# Correct synthesis and integration of compiler-generated function units

Thesis by Martin Ellis

In Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

University of Newcastle upon Tyne Newcastle upon Tyne, UK

#### Abstract

Computer architectures can use custom logic in addition to general purpose processors to improve performance for a variety of applications. The use of custom logic allows greater parallelism for some algorithms. While conventional CPUs typically operate on words, fine-grained custom logic can improve efficiency for many bit level operations. The commodification of field programmable devices, particularly FPGAs, has improved the viability of using custom logic in an architecture.

This thesis introduces an approach to reasoning about the correctness of compilers that generate custom logic that can be synthesized to provide hardware acceleration for a given application. Compiler intermediate representations (IRs) and transformations that are relevant to generation of custom logic are presented. Architectures may vary in the way that custom logic is incorporated, and suitable abstractions are used in order that the results apply to compilation for a variety of the design parameters that are introduced by the use of custom logic.

| 1 | Intro | oduction                                       |                                                                            |                 |

|---|-------|------------------------------------------------|----------------------------------------------------------------------------|-----------------|

|   | 1.1   | Hardware Acceleration for High-Level Languages |                                                                            |                 |

|   |       | 1.1.1                                          | Function Units                                                             | 3               |

|   |       | 1.1.2                                          | Reconfigurable Function Units                                              | 4               |

|   |       | 1.1.3                                          | Hardware/Software compilers for Function Units $\ . \ . \ .$               | 5               |

|   | 1.2   | Corr                                           | ectness of Hardware/Software Compilers                                     | 5               |

|   |       | 1.2.1                                          | Correctness for Hardware Acceleration                                      | 6               |

|   |       | 1.2.2                                          | Correctness for Conventional Compilers                                     | 8               |

|   |       | 1.2.3                                          | Inadequacy of Current Techniques                                           | 9               |

|   |       | 1.2.4                                          | Specific Problems in Hardware/Software Compilation $% \mathcal{S}^{(1)}$ . | 11              |

|   | 1.3   | Thes                                           | is Outline                                                                 | 13              |

|   |       | 1.3.1                                          | Scope                                                                      | 13              |

|   |       | 1.3.2                                          | Hardware/Software Interface                                                | 14              |

|   |       | 1.3.3                                          | Methodology and Thesis Structure                                           | 17              |

| 2 | Pac   | karoun                                         | d                                                                          | 19              |

| 2 |       |                                                |                                                                            |                 |

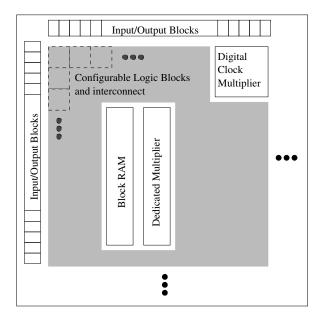

|   | 2.1   | 2.1.1                                          | A Structure and Design Flow                                                | 20<br>20        |

|   |       | 2.1.1<br>2.1.2                                 | FPGA Design Flow                                                           | 20<br>22        |

|   | 2.2   |                                                | ő                                                                          | 22              |

|   | 2.2   | 1                                              |                                                                            |                 |

|   | 2.3   | 2.3.1                                          | ware Acceleration using FPGAs          Types of RFU                        | $25 \\ 25$      |

|   | ை     | -                                              | • •                                                                        | $\frac{25}{27}$ |

|   | 2.4   | 2.4.1                                          | s, Meta-logics, and Logical Frameworks                                     | $\frac{21}{27}$ |

|   |       | 2.4.1<br>2.4.2                                 | Formal Systems                                                             | $\frac{27}{31}$ |

|   |       | 2.4.2                                          |                                                                            | 51              |

| 3 | Mac   | hine S                                         | upport for Reasoning                                                       | 33              |

|   | 3.1   | The .                                          | Isabelle System                                                            | 34              |

|   |       |                                                |                                                                            |                 |

|   |      | 3.1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Isabelle/Pure                                                            | 34 |

|---|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|----|

|   |      | 3.1.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Isabelle/HOL                                                             | 37 |

|   | 3.2  | Repr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | esentation of key concepts                                               | 42 |

|   |      | 3.2.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Memory representation                                                    | 42 |

|   |      | 3.2.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Number representation                                                    | 45 |

|   | 3.3  | Repr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | $esentation and Reasoning about Hardware \ldots \ldots$                  | 48 |

|   |      | 3.3.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Hardware Representations                                                 | 49 |

|   |      | 3.3.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Modelling Hardware in HOL                                                | 52 |

| 4 | Inte | rmedia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | te Representation                                                        | 57 |

|   | 4.1  | Requ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | $irements \ for \ a \ Hardware/Software \ IR \ \ldots \ \ldots \ \ldots$ | 58 |

|   |      | 4.1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Representation of Fine-Grained Parallelism                               | 58 |

|   |      | 4.1.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Flexibility for Hardware/Software Compilation $\ . \ . \ .$              | 59 |

|   | 4.2  | Anal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ysis of Existing Representations                                         | 59 |

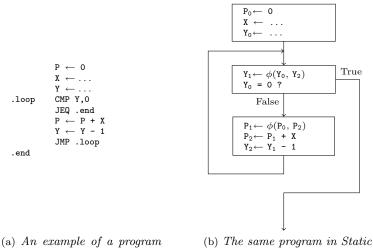

|   |      | 4.2.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Static Single Assignment Form                                            | 60 |

|   |      | 4.2.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SSA in Isabelle/HOL                                                      | 63 |

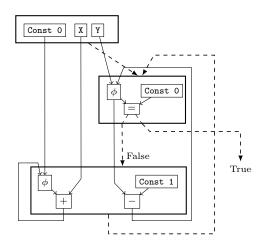

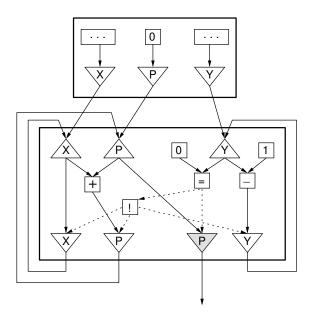

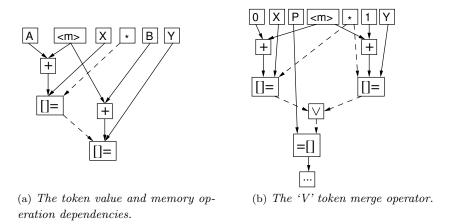

|   |      | 4.2.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Pegasus                                                                  | 67 |

|   | 4.3  | Form                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | al Definition of a Hardware/Software $IR$                                | 72 |

|   |      | 4.3.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Abstract Syntax                                                          | 72 |

|   |      | 4.3.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Semantics                                                                | 79 |

| 5 | ΑN   | etlist-L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | evel HDL                                                                 | 87 |

|   | 5.1  | Need                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | for a Netlist Language                                                   | 88 |

|   | 5.2  | Requ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | irements from a Netlist language                                         | 89 |

|   | 5.3  | Abstr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | $act \ Syntax$                                                           | 89 |

|   |      | 5.3.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | An abstract syntax for hardware                                          | 89 |

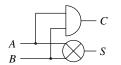

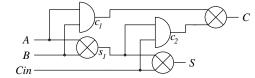

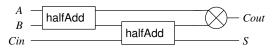

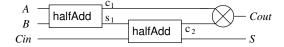

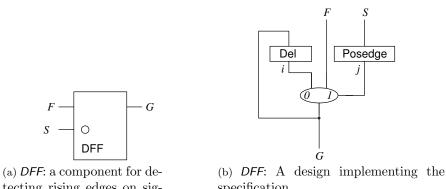

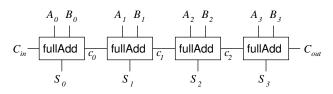

|   |      | 5.3.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | An example design of a Full Adder                                        | 91 |

|   | 5.4  | Netli                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | st Semantics                                                             | 92 |

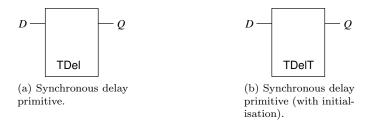

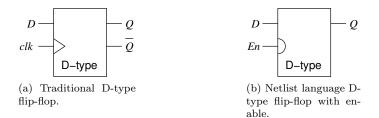

|   |      | 5.4.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Primitives                                                               | 92 |

|   |      | 5.4.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Abstraction and Instantiation Semantics                                  | 92 |

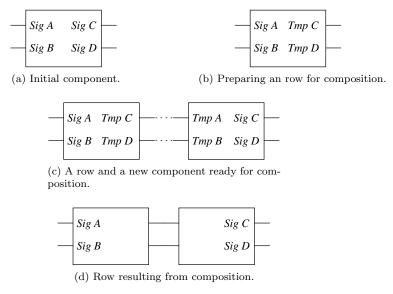

|   |      | 5.4.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Composition Semantics                                                    | 93 |

|   |      | 5.4.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Component Semantics                                                      | 94 |

|   | 5.5  | Sema                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | untics of a Full Adder design                                            | 95 |

|   |      | 5.5.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Half Adder Semantics                                                     | 96 |

|   |      | 5.5.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Full Adder Semantics                                                     | 97 |

|   | 5.6  | Correction Correctio | ectness of a Full Adder design                                           | 99 |