# Microsystems Research Group School of Engineering

# **Analysis and Design of Switched-Capacitor DC-DC Converters with Discrete Event Models**

#### Danhui Li

A thesis submitted for the degree of Doctor of Philosophy

# Content

| List of Figures                                           | V    |

|-----------------------------------------------------------|------|

| List of Tables                                            | ix   |

| Acronyms                                                  | X    |

| Abstract                                                  | xi   |

| Acknowledgement                                           | xiii |

| Chapter 1 Introduction                                    | 1    |

| 1.1 Motivations and objectives                            | 1    |

| 1.1 Contributions                                         | 5    |

| 1.2 Structure of the thesis                               | 6    |

| 1.3 Publications                                          | 8    |

| Chapter 2 Background                                      | 9    |

| 2.1 Switched-capacitor DC-DC converters                   | 10   |

| 2.1.1 Definition                                          | 10   |

| 2.1.2 Topologies of SCDDCs                                | 13   |

| 2.1.3 Reversion losses                                    | 17   |

| 2.2 Cross-coupled voltage doubler examples                | 19   |

| 2.2.1 Structure of the cross-coupled voltage doubler      | 19   |

| 2.2.2 Reversion losses in a cross-coupled voltage doubler | 22   |

| 2.2.3 Designs that eliminate reversion losses             | 25   |

| 2.3 Existing modelling methods                            | 31   |

| 2.3.1 Charge Flow Analysis                                | 31   |

| 2.3.2 Output Impedance Analysis                           | 32   |

| 2.4 Discrete event Models                                 | 35   |

| 2.4.1 Petri nets.                                                            | 35 |

|------------------------------------------------------------------------------|----|

| 2.4.2 Signal Transition Graphs (STGs)                                        | 37 |

| 2.4.3 Asynchronous circuits                                                  | 39 |

| 2.4.4 Tools for discrete event models                                        | 40 |

| 2.5 Summary                                                                  | 41 |

| Chapter 3 Modelling SCDDCs with Extended Signal Transition Graphs            | 42 |

| 3.1 Introduction                                                             | 42 |

| 3.2 Modelling Method                                                         | 43 |

| 3.3 Examples                                                                 | 47 |

| 3.4 STG for SCDDCs with different topologies                                 | 55 |

| 3.5 Summary                                                                  | 58 |

| Chapter 4 Modelling and Analysing Reversion Losses in SCDDCs with Petri Nets | 60 |

| 4.1 Introduction                                                             | 60 |

| 4.2 Modelling method                                                         | 62 |

| 4.3 Examples                                                                 | 67 |

| 4.4 Analysis and verification                                                | 74 |

| 4.5 Other cross-coupled voltage doubler studies with Petri nets              | 79 |

| 4.6 Summary                                                                  | 86 |

| Chapter 5 Designing Reversion-Loss-Free SCDDCs with Discrete Event Models    | 87 |

| 5.1 Introduction                                                             | 87 |

| 5.2 Design method                                                            | 88 |

| 5.3 Case study of a cross-coupled voltage doubler design                     | 90 |

| 5.3.1 Overview of the proposed cross-coupled voltage doubler                 | 91 |

| 5.3.2 Designing the proposed cross-coupled voltage doubler step by step      | 95 |

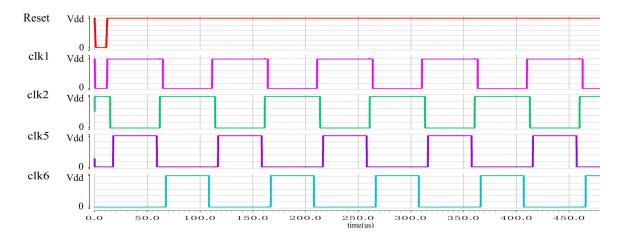

| 5.4 Simu     | ılation                                       | 102 |

|--------------|-----------------------------------------------|-----|

| 5.5 Sum      | mary                                          | 104 |

| Chapter 6 Co | nclusions                                     | 106 |

| 6.1 Sum      | mary of contributions                         | 106 |

| 6.2 Futu     | re work                                       | 108 |

| Appendix A   | Reachability analysis results for Case 1      | 111 |

| Appendix B   | System structure and design process of Case 2 | 114 |

| References   |                                               | 121 |

# **List of Figures**

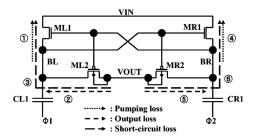

| Figure 1.1: Descriptions of reversion losses in a cross-coupled voltage doubler, (a) i         |

|------------------------------------------------------------------------------------------------|

| from [40]                                                                                      |

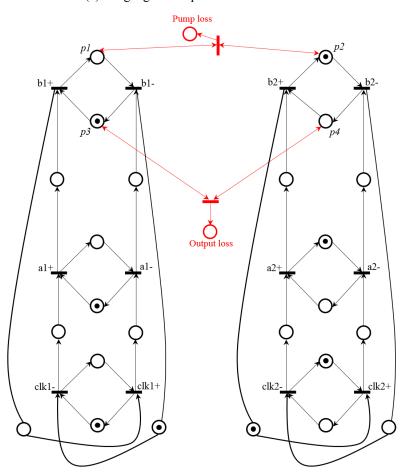

| Figure 1.2: Main structure of the thesis.                                                      |

| Figure 2.1: General structure for SCDDCs. 10                                                   |

| Figure 2.2: Basic voltage doubler and its sub-nets.                                            |

| Figure 2.3: Control signals (Clock signals).                                                   |

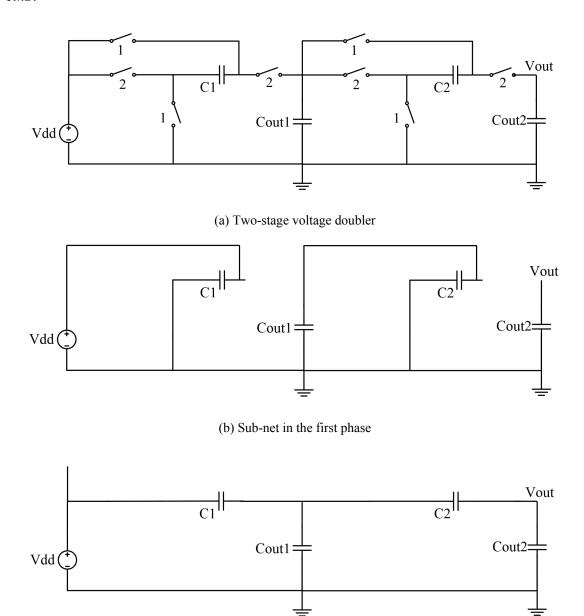

| Figure 2.4: Two-stage voltage doubler and its sub-nets.                                        |

| Figure 2.5: Ladder and its sub-nets.                                                           |

| Figure 2.6: Fibonacci multiplier and its sub-nets                                              |

| Figure 2.7: Reversion loss in PMOS and NMOS.                                                   |

| Figure 2.8: Shoot-through current                                                              |

| Figure 2.9: Cross-coupled voltage doubler, adapted from [18]                                   |

| Figure 2.10: Simulation result of Voltage Doubler 1                                            |

| Figure 2.11: Reversion loss paths in Voltage Doubler 1                                         |

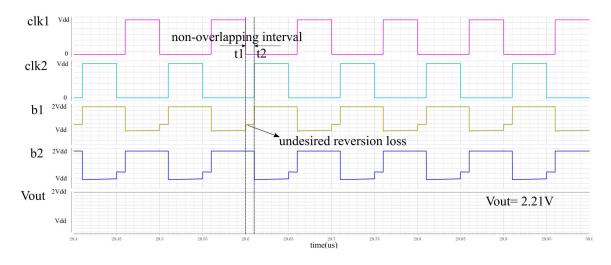

| Figure 2.12: Waveforms for Voltage Doubler 1 driven with different clock signals               |

|                                                                                                |

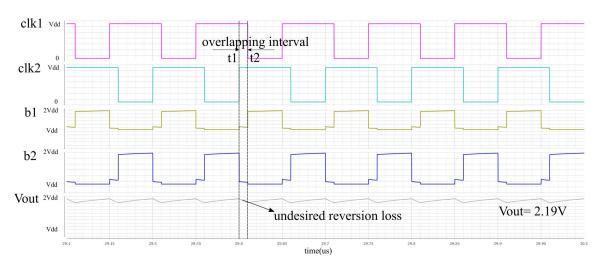

| Figure 2.13: VCRs for Voltage doubler 1 with different overlapping and non overlapping clocks. |

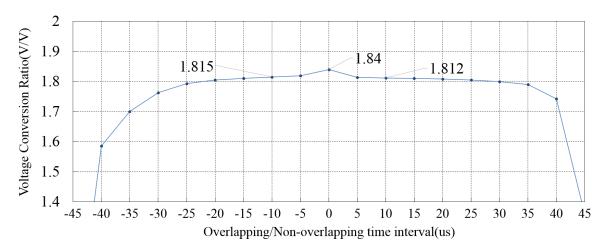

| Figure 2.14: Voltage Doubler 2 and its control signals, adapted from [18]20                    |

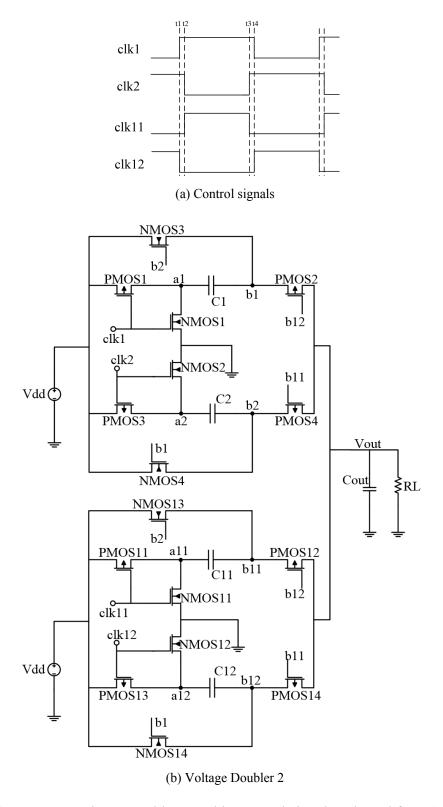

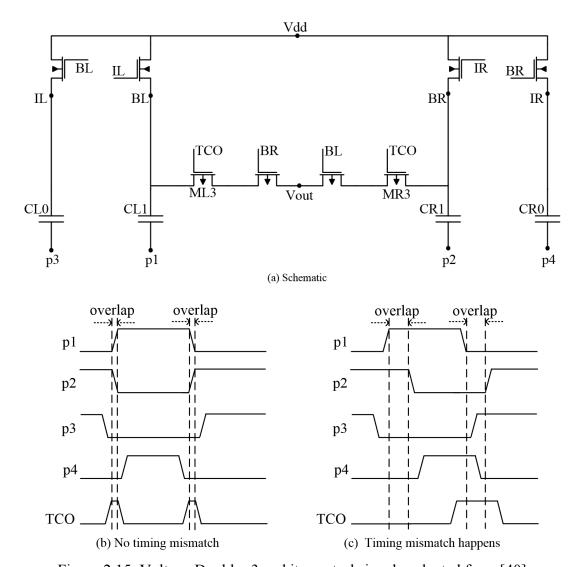

| Figure 2.15: Voltage Doubler 3 and its control signals, adapted from [40]                      |

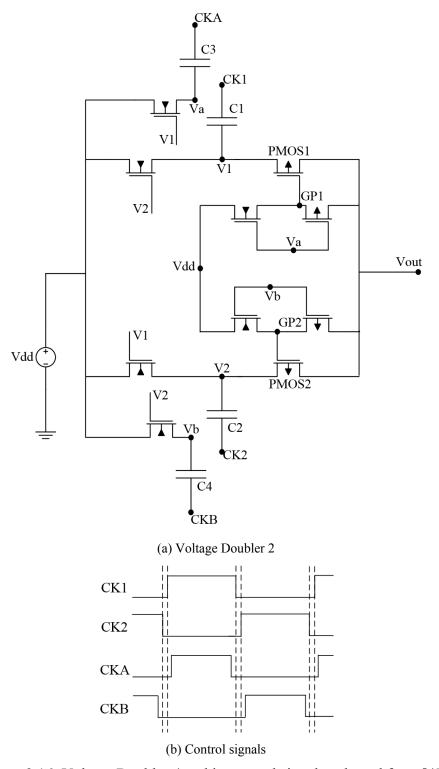

| Figure 2.16: Voltage Doubler 4 and its control signals, adapted from [47]29                    |

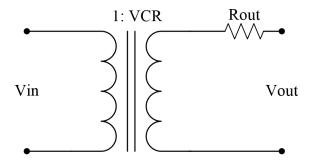

| Figure 2.17: Output Impedance Analysis Model for SCDDCs                                        |

| Figure 2.18: SSL and FSL impedance model for SCDDCs 3                                          |

| Figure 2.19: Elements of Petri nets.                                                                                                           | 36  |

|------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 2.20: Petri net example: Producer and Consumer problem.                                                                                 | 37  |

| Figure 2.21: Example of an STG modelling a system with featuring concurrency.                                                                  | 38  |

| Figure 2.22: Communication methods for synchronous circuit and asynchronic circuit.                                                            |     |

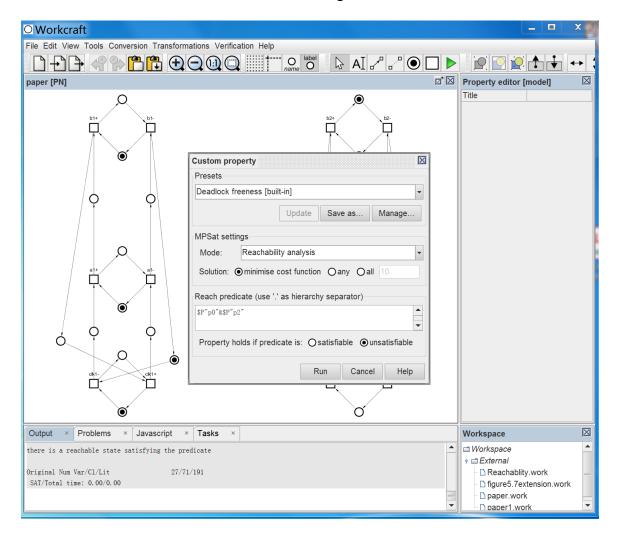

| Figure 2.23: UI of Workcraft.                                                                                                                  | 40  |

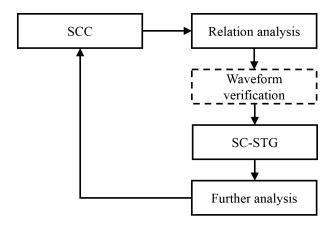

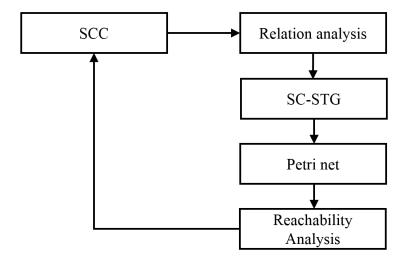

| Figure 3.1: Flow chart of modelling SCDDCs with SC-STGs.                                                                                       | 46  |

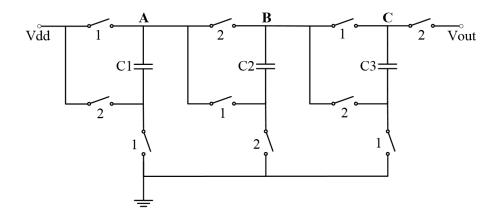

| Figure 3.2: Schematic of Voltage Double 1, adapted from [18]                                                                                   | 47  |

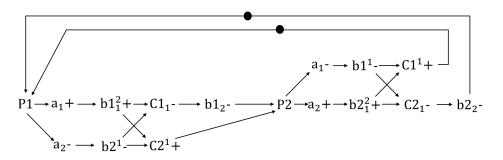

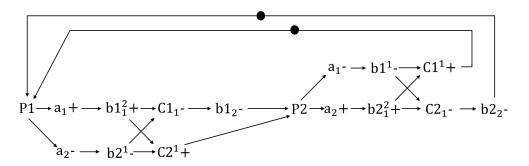

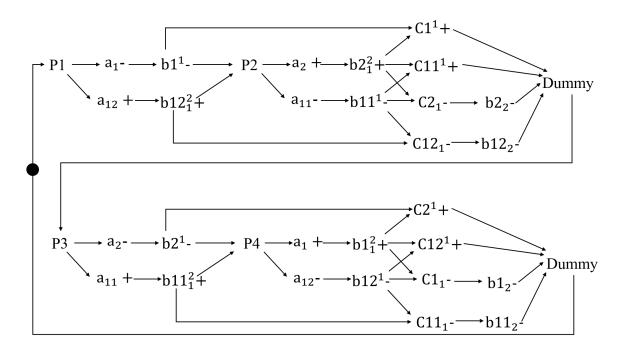

| Figure 3.3: Flow chart of events happening in Voltage Doubler 1. (All events in dashed box are caused by events with an arc to the dashed box) |     |

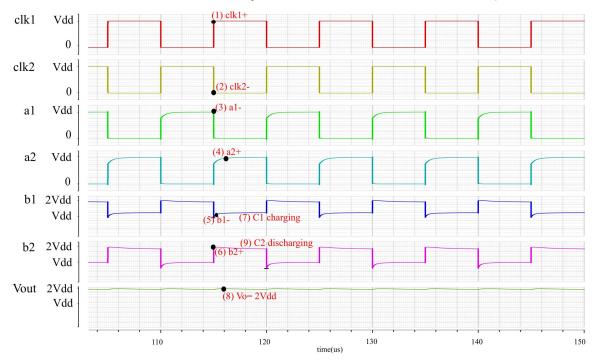

| Figure 3.4: Simulation waveform for Voltage Doubler 1 (RL=10K)                                                                                 | 48  |

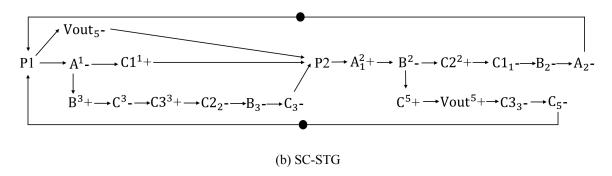

| Figure 3.5: SC-STG for Voltage Doubler 1.                                                                                                      | 49  |

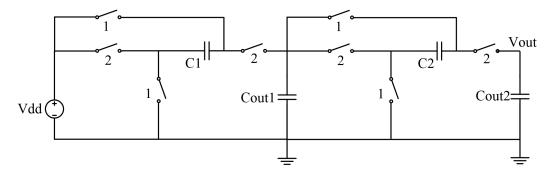

| Figure 3.6: Schematic of Voltage Doubler 2.                                                                                                    | 51  |

| Figure 3.7: Flow chart of events happening in Voltage Doubler 2                                                                                | 52  |

| Figure 3.8: SC-STG for Voltage Doubler 2.                                                                                                      | 52  |

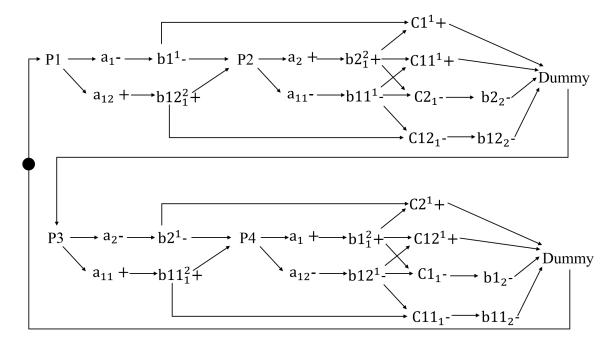

| Figure 3.9: Two-stage voltage doubler and its SC-STG model                                                                                     | 56  |

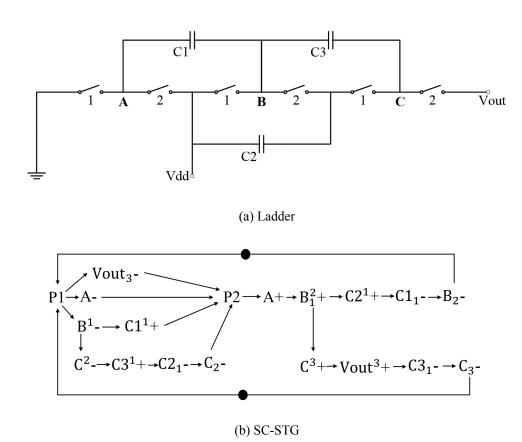

| Figure 3.10: Ladder with a VCR of 3 and its SC-STG model                                                                                       | 57  |

| Figure 3.11: Fibonacci Multiplier with a VCR of 5 and its SC-STG.                                                                              | 58  |

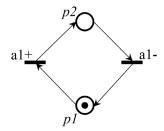

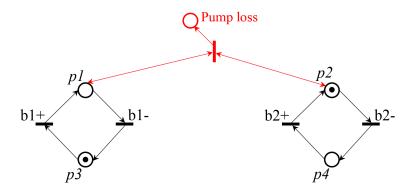

| Figure 4.1: Petri net modelling example of transitions $a1+$ and $a1-$                                                                         | 63  |

| Figure 4.2: Petri net modelling example of monitoring sub-nets for reversion loss                                                              | 364 |

| Figure 4.3: Flow chart of modelling reversion losses in SCDDCs                                                                                 | 65  |

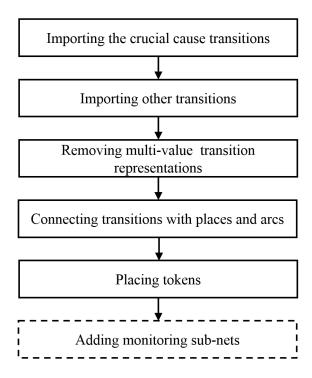

| Figure 4.4: Steps of developing a Petri net model based on SC-STG.                                                                             | 66  |

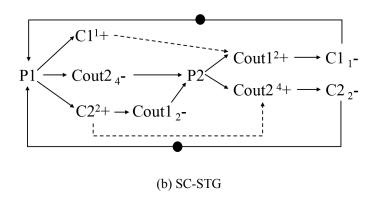

| Figure 4.5: SC-STG for Voltage Doubler 1                                                                                                       | 67  |

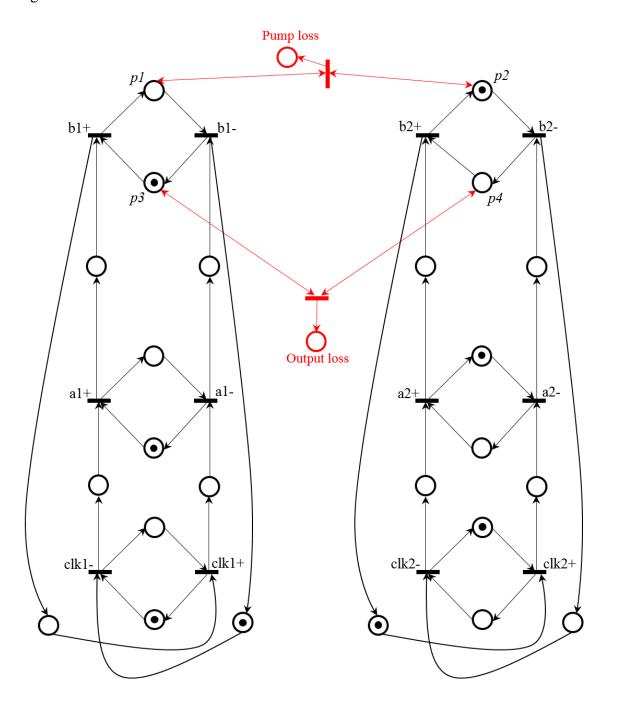

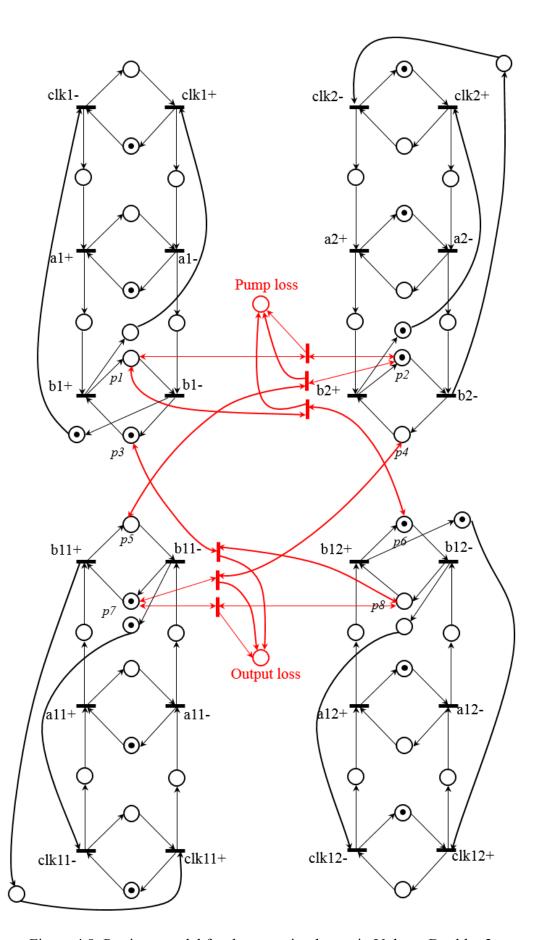

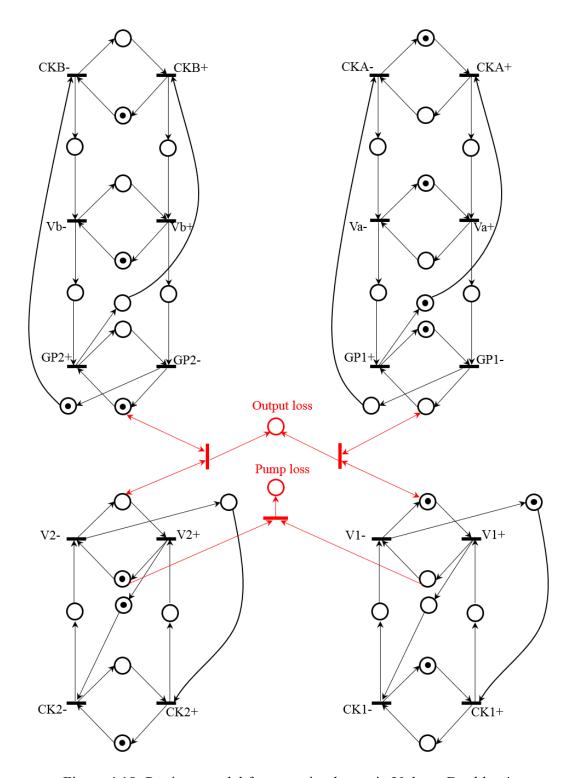

| Figure 4.6: Petri net model for reversion losses in Voltage Doubler 1                                                                          | 68  |

| Figure 4.7: SC-STG model for Voltage Doubler 2                                                                                                 | 70  |

| Figure 4.8: Petri net model for the reversion losses in Voltage Doubler 2                                  | 71 |

|------------------------------------------------------------------------------------------------------------|----|

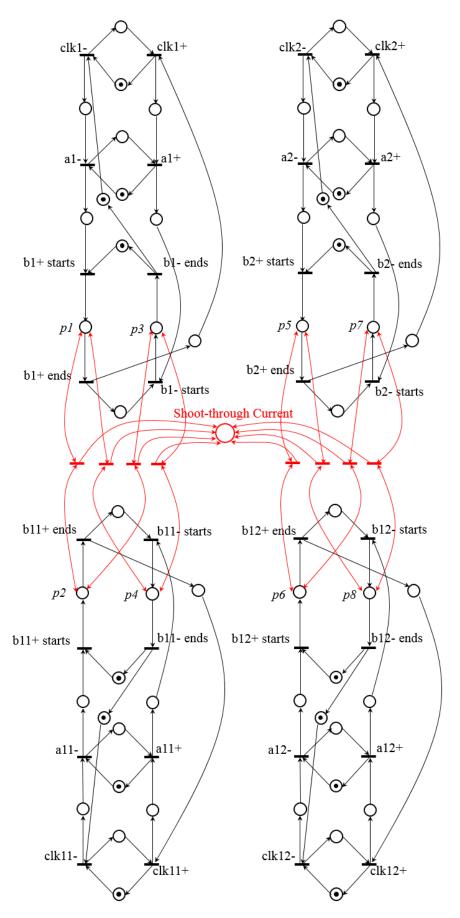

| Figure 4.9: Petri net model for shoot-through currents in Voltage Doubler 2                                | 72 |

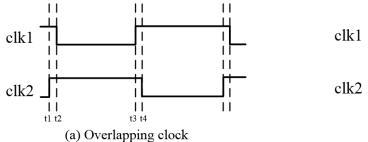

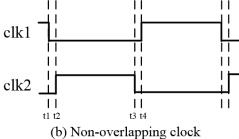

| Figure 4.10: Overlapping clock signals and non-overlapping clock signals                                   | 75 |

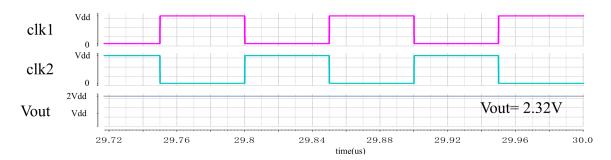

| Figure 4.11: Simulation result for Voltage Doubler 1 with the particular conscheme.                        |    |

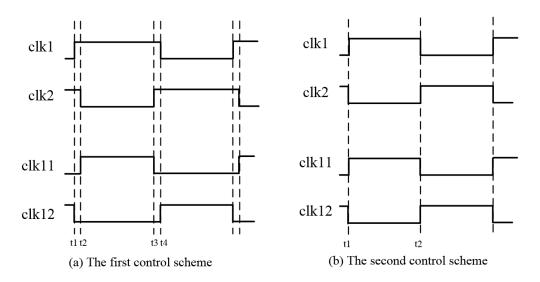

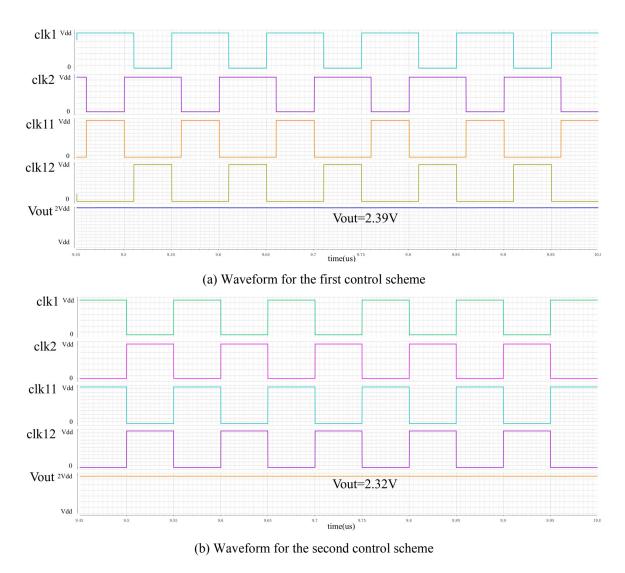

| Figure 4.12: Healthy control schemes determined from reachability analysis                                 | 77 |

| Figure 4.13: Simulation waveforms for Voltage Doubler 2 driven with the determined healthy control scheme. |    |

| Figure 4.14: Reversion losses caused by clock mismatches in Voltage Doubler 2.                             | 80 |

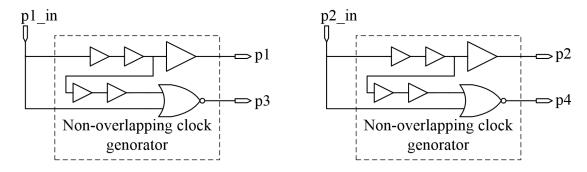

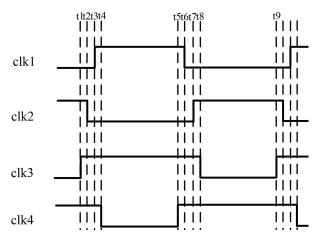

| Figure 4.15: Control signals of Voltage Doubler 3, adapted from [40]                                       | 81 |

| Figure 4.16: Control signals of Voltage Doubler 4, adapted from [47]                                       | 81 |

| Figure 4.17: Petri net model for reversion losses in Voltage Doubler 3                                     | 82 |

| Figure 4.18: Petri net model for reversion losses in Voltage Doubler 4                                     | 83 |

| Figure 4.19: Clock generators for Voltage Doubler 3 and Voltage Doubler 4, adaptrom [40] and [47]          | _  |

| Figure 5.1: Flow chart of the new design method.                                                           | 89 |

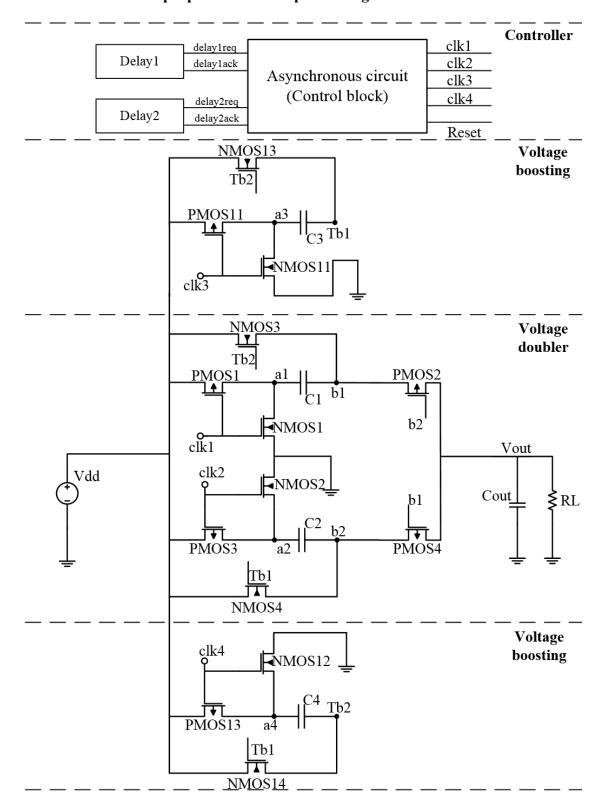

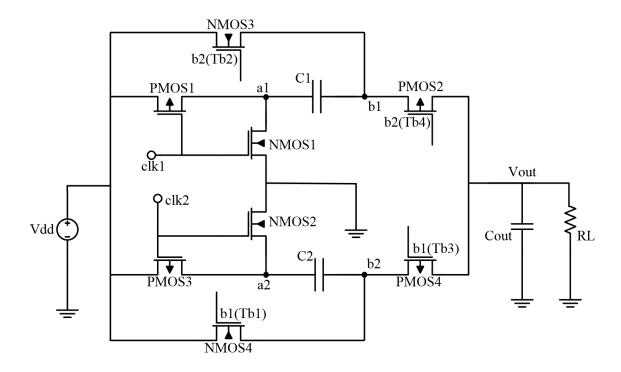

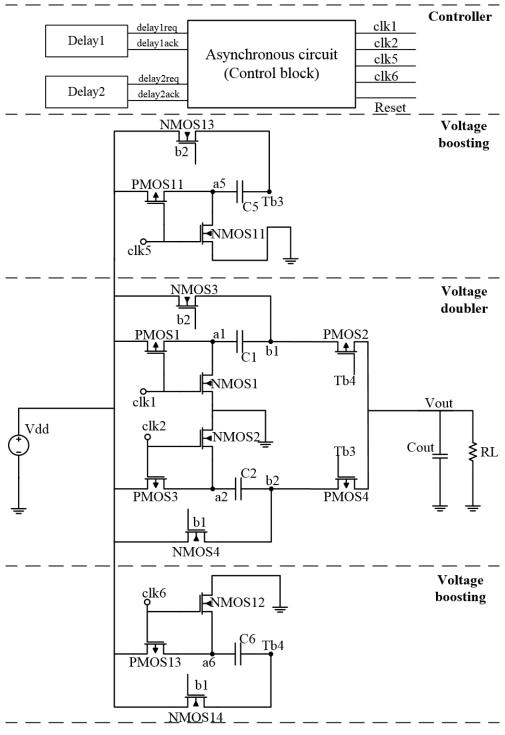

| Figure 5.2: Schematic of the proposed cross-coupled voltage doubler.                                       | 91 |

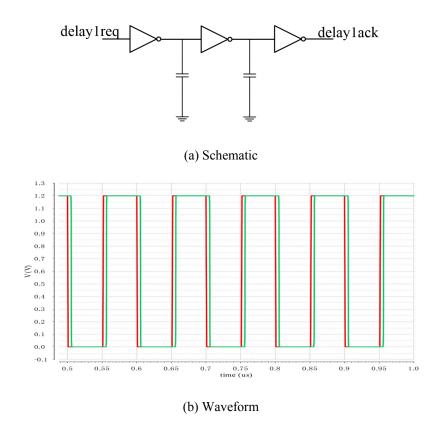

| Figure 5.3: Delay element Delay1 and its waveform.                                                         | 93 |

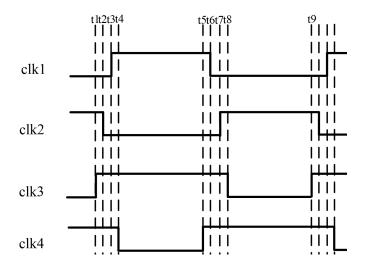

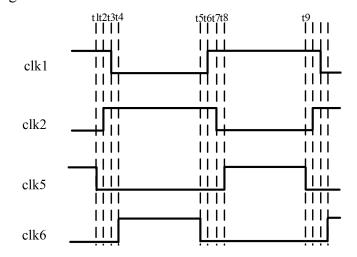

| Figure 5.4: The control scheme for the proposed cross-coupled voltage doubler                              | 94 |

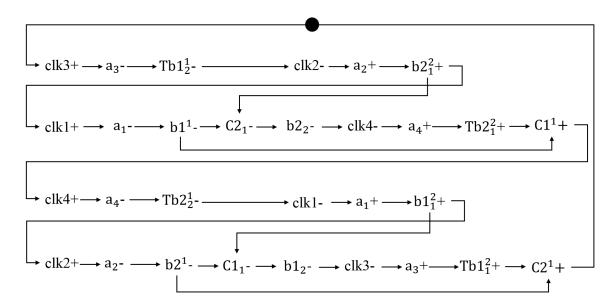

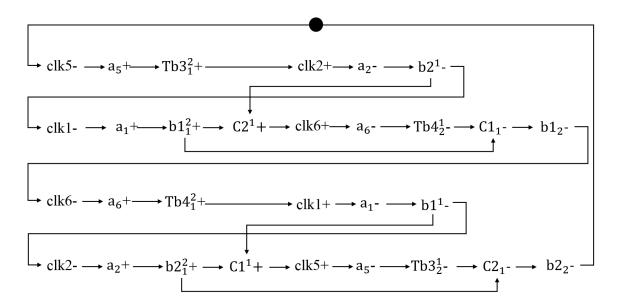

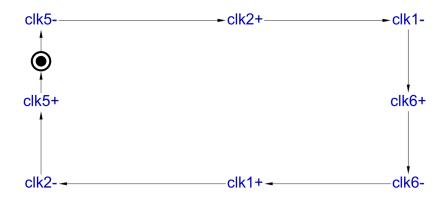

| Figure 5.5: SC-STG for the proposed cross-coupled voltage doubler                                          | 94 |

| Figure 5.6: Schematic of a cross-coupled voltage doubler with external controls.                           | 95 |

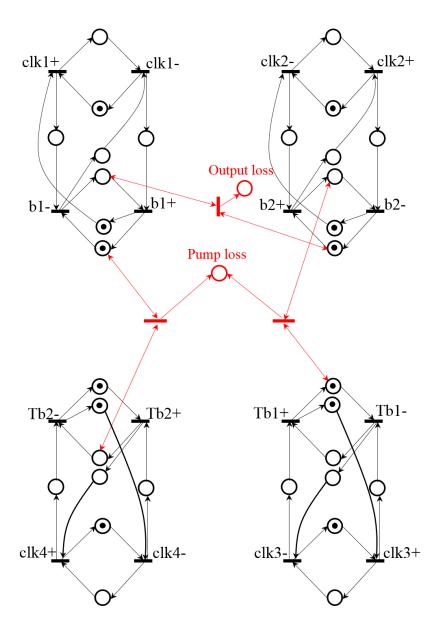

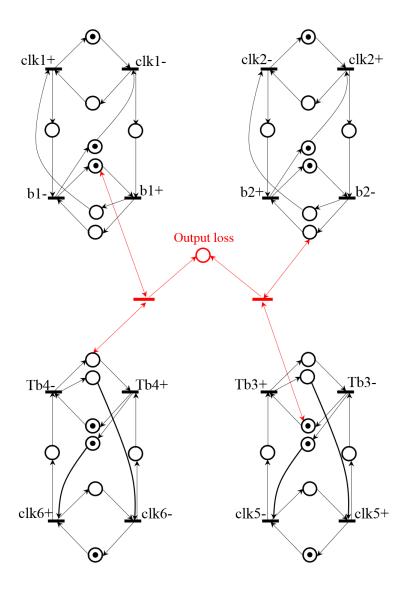

| Figure 5.7: Petri net model for reversion losses in Case 1                                                 | 97 |

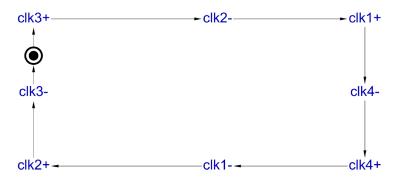

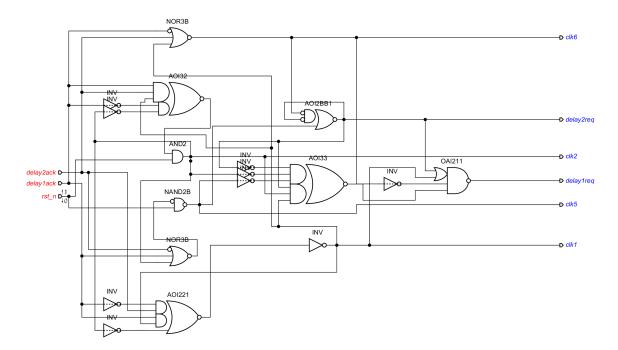

| Figure 5.8: Determined healthy control scheme for Case 1                                                   | 98 |

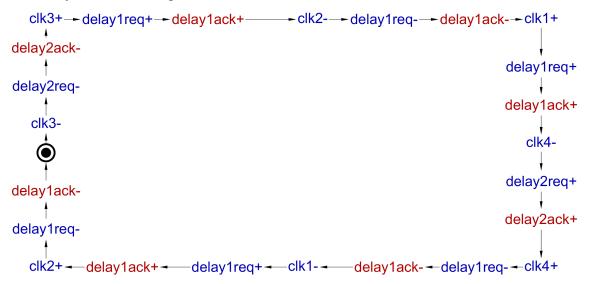

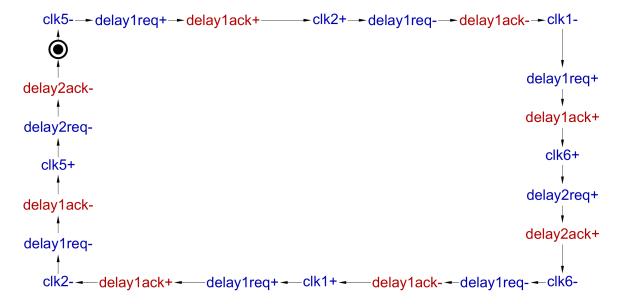

| Figure 5.9: STG model for the determined healthy control scheme (Case 1)                                   | 90 |

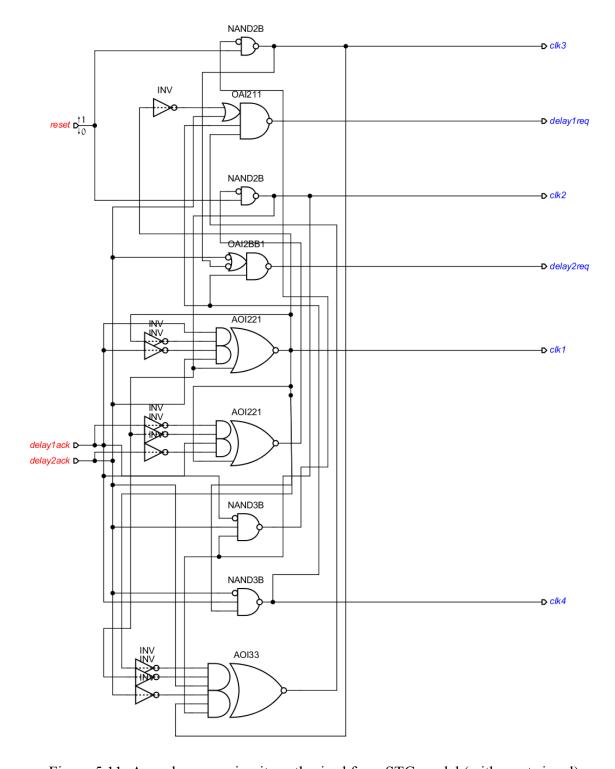

| Figure 5.10: Practical STG model for the determined healthy control scheme (Case 1).   |

|----------------------------------------------------------------------------------------|

| Figure 5.11: Asynchronous circuit synthesised from STG model (with reset signal).      |

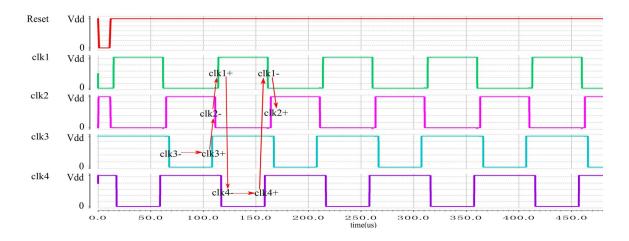

| Figure 5.12: Simulation waveform for the generated asynchronous circuit (Case 1).      |

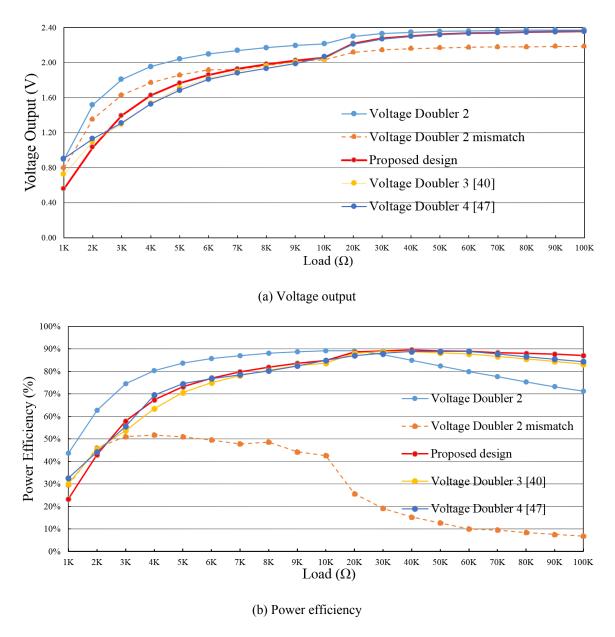

| Figure 5.13: Simulated output voltages and power efficiencies versus load resistances. |

| Figure A.1: Petri nets for Case 1 with extra monitoring sub-nets                       |

| Figure B.1: Schematic of a new cross-coupled voltage doubler based on Case 2114        |

| Figure B.2: SC-STG for the cross-coupled voltage doubler based on Case 2115            |

| Figure B.3: Petri net model for reversion losses in Case 2                             |

| Figure B.4: Determined healthy control scheme for Case 2                               |

| Figure B.5: STG model for the determined healthy control scheme (Case 2)118            |

| Figure B.6: Practical STG model for the determined healthy control scheme (Case 2).    |

| Figure B.7: Asynchronous circuit synthesised from STG model (with reset signal).       |

| Figure B.8: Simulation waveform for the generated asynchronous circuit (Case 2).       |

# **List of Tables**

| Table 3.1: Examples of representations in SC-STG.                  | 46  |

|--------------------------------------------------------------------|-----|

| Table 3.2: Representations in the SC-STG.                          | 50  |

| Table 3.3: Parts of representations in SC-STG of Voltage Doubler 2 | 53  |

| Table 4.1: Results of reachability analysis for Voltage Doubler 1  | 75  |

| Table A.1: Results of reachability analysis for Case 1 (method 1)  | 111 |

| Table A.2: Results of reachability analysis for Case 1 (method 2)  | 113 |

# Acronyms

SCDDC Switched-Capacitor DC-DC Converter

SC-STG Switched-Capacitor Signal Transition Graph

STG Signal Transition Graph

LPN Labelled Petri Nets

VCR Voltage Conversion Ratio

LCD Liquid-crystal Display

DRAM Dynamic Random Access Memory

SSL Slow Switching Limits

FSL Fast Switching Limits

CSC Complete State Coding

CAD Compute-Aid Design

### **Abstract**

Switched-capacitor DC-DC converters (SCDDCs) play a critical role in low power integrated systems. The analysis and design processes of an SCDDC impact the performance and power efficiency of the whole system. Conventionally, researchers carry out the analysis and design processes by viewing SCDDCs as analogue circuits. Analogue attributes of an SCDDC, such as the charge flow current or the equivalent output impedance, have been studied in considerable detail for performance enhancement. However, in most existing work, less attention is paid to the analysis of discrete events (e.g. digital signal transitions) and the relationships between discrete events in SCDDCs. These discrete events and the relationships between discrete events also affect the performance of SCDDCs. Certain negative effects of SCDDCs such as leakage current are introduced by unhealthy discrete states. For example, MOS devices in an SCDDC could conduct undesirably under certain combinations of signals, resulting in reversion losses (a type of leakage in SCDDCs). However, existing work only use verbal reasoning and waveform descriptions when studying these discrete events, which may cause confusion and result in an informal design process consisting of intuitive design and backed up merely by validation based on natural language discussions and simulations. There is therefore a need for formalised methods to describe and analyse these discrete events which may facilitate systematic design techniques.

This thesis presents a new method of analysing and designing SCDDCs using discrete event models. Discrete event models such as Petri nets and Signal Transition Graphs (STGs) are commonly used in asynchronous circuits to formally describe and analyse the relationships between discrete transitions. Modelling SCDDCs with discrete event models provides a formal way to describe the relations between discrete transitions in SCDDCs. These discrete event models can be used for analysis, verification and even design guidance for SCDDC design. The rich set of existing analysis methods and tools for discrete event models could be applied to SCDDCs, potentially improving the analysis and design flow for them. Moreover, since Petri nets and STGs are generally used to analyse and design asynchronous circuits, modelling and designing SCDDCs with STG models may additionally facilitate the incorporation of positive features of asynchronous circuits in SCDDCs (e.g. no clock skew).

In this thesis, the relations between discrete events in SCDDCs are formally described with SC-STG (an extended STG targeting multi-voltage systems, to which SCDDCs belong), which avoids the potential confusion due to natural language and waveform descriptions. Then the concurrency and causality relations described in SC-STG model are extended to Petri nets, with which the presence of reversion losses can be formally determined and verified. Finally, based on the STG and Petri net models, a new design method for reversion-loss-free SCDDCs is proposed. In SCDDCs designed with the new method, reversion losses are entirely removed by introducing asynchronous controls, synthesised with the help of a software synthesis toolkit "Workcraft".

To demonstrate the analysis capabilities of the method, several cross-coupled voltage doublers (a type of SCDDC) are analysed and studied with discrete event models as examples in this thesis. To demonstrate the design capabilities of the method, a new reversion-loss-free cross-coupled voltage doubler is designed. The cross-coupled voltage doubler is widely used in low power integrated systems such as flash memories, LCD drivers and wireless energy harvesting systems. The proposed modelling method is potentially used in both research and industrial area of those applications for a formal and high-efficiency design process.

# Acknowledgement

First of all, I would like to express my sincere gratitude to Prof. Alex Yakovlev for his patient guidance and consistent support throughout the duration of my study. His enthusiasm and attitude on research is admirable and has been a resource of inspiration for me.

I would also like to express my gratitude to my co-supervisor Dr. Fei Xia Dr. Delong Shang for their valuable support and continuous guidance. Fei also gave me lots of help in paper writing. Without him, it is hard to describe my research systematically and clearly.

I am also grateful to colleagues Junwen, Kaiyuan, Yuqing and Thomas for their assistance and inspiring discussion.

I would also to acknowledge that this work was partly supported by School of Engineering, Newcastle University.

Last but not least, my deepest thanks are given to my parents for their unrequited love.

## Chapter 1

### Introduction

#### 1.1 Motivations and objectives

Over the past few years, portable electronic devices such as smartphones and wearable devices have been proliferating in people's daily lives [1]. Portable devices such as smartphones are increasingly equipped with such components as face recognition modules, wireless charging modules, 5G communication modules, etc. [2]-[4]. As a portable device is typically powered by a battery with a fixed output (e.g. of 3.7V for smartphones) and the functional components are operated with different voltage supplies [5], DC-DC converters are utilised to convert the battery voltage into different supply voltages, ensuring that such components work in optimal modes. DC-DC converters play an essential role in these portable devices, and the performance of DC-DC converters impacts the device's battery life.

Switched-capacitor DC-DC Converters (SCDDC) are a subset of DC-DC converters, converting a voltage to another voltage with only switches and capacitors employed. Compared with the inductor based switched DC-DC converter, the SCDDC has advantages of small size and high-power density since the capacitor is more compatible with modern CMOS processes [6]. Although efforts have been made [7]-[9] to reduce the inductor size and to integrate the inductor on a chip, these usually require costly extra fabrication steps. The ease of integration has led to the extensive use of SCDDCs in low power technologies. The performance, especially power efficiency, of SCDDCs is therefore an important topic of study for low power integrated technologies [6].

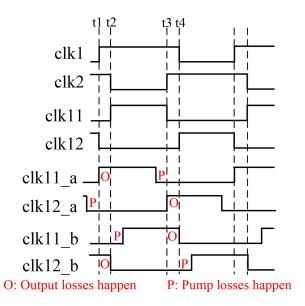

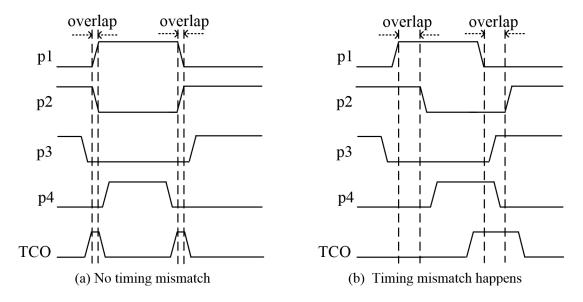

In this charge pump, the timing relationship between  $\Phi 1$ and  $\Phi 2$  is very important for minimizing the reversion loss because the loss closely depends on both the relative timing between clock phases and the transition slope of each clock [6]. To investigate this aspect, Fig. 2 shows two possible timing relationships between these control clocks. When  $\Phi 1$  and  $\Phi 2$ are matched to each other [see Fig. 2(a)], there is no overlap between clock levels, and only the transition periods are briefly overlapped. In this case, overlapping transition period,  $OV \mathcal{I}_R(OV \mathcal{I}_F)$ , refers to the period in which a rising (falling) transition of  $\Phi 1$  and a falling (rising) transition of  $\Phi 2$  are overlapped to each other. When there is a timing mismatch between  $\Phi 1$  and  $\Phi 2$  [see Fig. 2(b)], there are intervals in which their high and low levels are overlapped. In this case, overlapping period,  $OV\_H(OV\_L)$ , refers to the period in which both clock phases are identically high (low) [5]. Under the matched timing condition shown in Fig. 2(a), the charge pump has reversion loss during each transition period. That is, during  $OV \mathcal{I}_{R}$ , the pumping loss occurs since a boosting action on BL starts before ML1 becomes fully OFF [see ① in Fig. 1]. The output loss also occurs because the precharge action on BR starts before MR2 becomes fully OFF (see (5)). The short-circuit loss happens during the portion of the transition period in which ML1 and ML2 or MR1 and MR2 are simultaneously ON (see 3) and (6). The occurrence of reversion loss during  $OV_{-}T_{F}$  is similar to the previous case. Under the mismatched timing condition shown in Fig. 2(b), the conventional charge pump has far larger amount of reversion loss during overlapping periods. During  $OV\_L$ , BL driven by  $\Phi1$  goes low when ML2 is still ON. Then, some of the output charges are transferred to BL through ML2,

resulting in the output loss (see (2)). The pull-down of BL also allows MR2 to turn on, resulting in additional output loss (see ⑤). The charge injected into BL and BR by these output losses causes a pull-up of both nodes, which makes ML1 and MR1 turn on. Then, some charges can flow directly through ML1–ML2 or MR1–MR2, resulting in the short-circuit loss (see ③ and ⑥). During  $OV\_H$ , since BL goes high when ML1 is still ON, some of the charges stored in BL are transferred to the input supply node, resulting in the pumping loss (see ①). During the pull-up of BL, there is a period in which MR1 and MR2 are simultaneously ON, resulting in the short-circuit loss (see ⑥). In addition, since a high level on BL makes MR1 stay ON, the voltage of BR is somewhat lowered, turning ML2 on. Thus, short-circuit loss can happen during the period in which ML1 and ML2 are simultaneously ON (see ③).

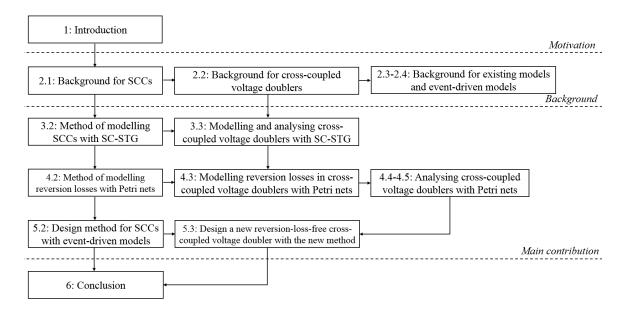

#### (a) Language description of reversion losses

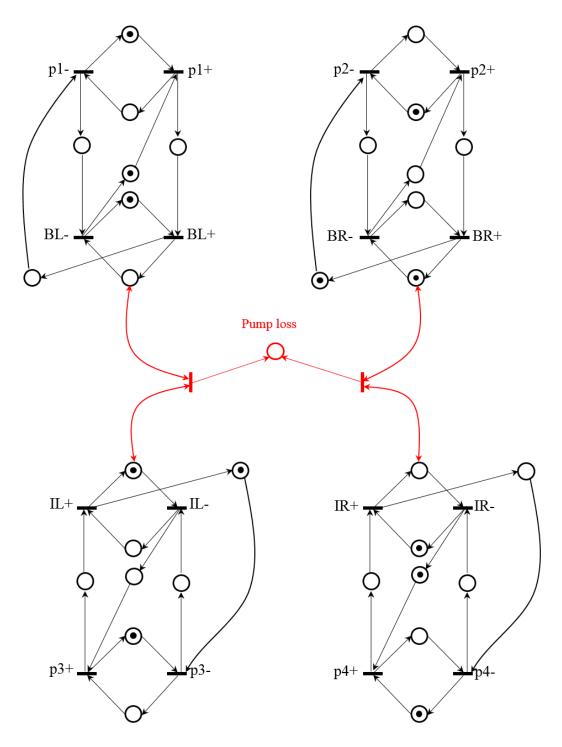

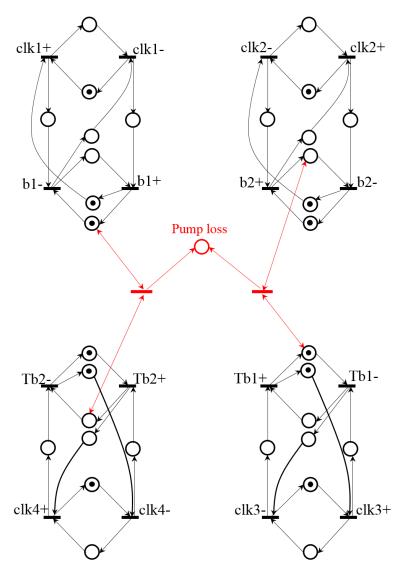

(b) Modelling reversion losses with Petri nets

Figure 1.1: Descriptions of reversion losses in a cross-coupled voltage doubler, (a) is from [40].

Traditionally, SCDDCs in are analysed and designed with modelling methods such as Charge Flow Analysis [10] and Output Impedance Analysis [11]-[13]. Charge Flow Analysis, studies the charges in a converter and can be used to estimate the equivalent output resistance based on the Output Impedance Analysis, with which an optimised working frequency or duty cycle can be obtained to improve the power conversion performance and power efficiency. Other modelling methods have also been proposed to help the analysis and design of SCDDC; [14] proposed a graph theory to predict the required number of capacitors for an SCDDC for any voltage conversion ratio; [15] and [16] modelled SCDDCs' output impedance with topology synthesis and [17] proposed a voltage-domain analysis that balances the trade-off between SCDDCs' properties for performance enhancement. However, these modelling methods focus more on the analogue attributes of SCDDCs and less attention is paid to discrete events (events that occur instantaneously, i.e. in discrete time, on signals that take discrete values, which are usually described using digital methods contrasted to continuous events which happen in continuous time on signals with continuous values and described using analogue methods) and the causality and concurrency relationships between discrete events, leading to the undernoted issues in the analysis and design of SCDDCs.

- There is no formal way to describe the causality and concurrency relations between the discrete events in SCDDCs. Existing literature titles typically describe the causalities of the signals in SCDDCs with natural language assisted by waveforms without any formal notations, researchers or engineers could potentially be confused about these relations in SCDDCs.

- There is no formal way to describe and verify certain negative effects, such as reversion loss, caused by discrete events in SCDDCs. Reversion losses are a type of leakage caused by undesirable conduction in MOS devices under certain combinations of signals. Without a formal method of modelling the discrete events and their relationships, works in the literature can only describe and analyse reversion losses with natural language intuition and waveforms, which also may cause confusion for researchers and engineers.

These problems become severe when an SCDDC gets larger in size and more complex in topology. Figure 1.1(a) shows descriptions of reversion losses that happen in a cross-

coupled voltage doubler [47] with dedicated combinations of internal signals. Although readers can understand what happened in the voltage doubler from the above descriptions, the descriptions are likely to cause confusion and inconvenience in case of the need for further analysis and verification.

At the same time, there are several SCDDC topologies that can achieve the same conversion rate with different charging and discharging principles. Behaviours such as signal transitions and charging/discharging processes in those SCDDCs are different, where the conventional intuitive descriptions for these also may cause a certain degree of confusion.

To formally describe and analyse those discrete events in SCDDCs, new modelling methods for SCDDCs based on discrete event models are proposed in this thesis. In this thesis, the main discrete event models adopted to model SCDDCs are Petri nets [19] and Signal Transition Graphs (STGs) [20]. The Petri net language was first introduced in the early 1960s, which has been used widely in the area of concurrent systems, distributed control systems, manufacturing, etc. [21]-[24]. STG is a particular version of Petri nets, which was initially introduced in [20], [25] to describe and formalise discrete events in asynchronous digital circuits. These discrete event models have been utilised to analyse and design DC-DC converters in some literature titles [26]-[30]. [26]-[28] propose a new design flow for a mixed-signal circuit based on STG and LPN (a type of extended Petri nets) where an example of an inductor based buck converter is designed with STG and LPN. [29] and [30] propose self-timed two-phase and multi-phase SCDDCs based on the STG model.

Based on these existing works, this thesis presents new modelling methods for SCDDCs in low power integrated systems by using discrete event models. With such modelling methods, the causality and concurrency relations between discrete events in SCDDCs can be formally described and reversion losses can be associated with certain events and therefore formally described and verified. Figure 1.1(b) shows the Petri net model that describes reversion losses in a cross-coupled voltage doubler, which is formal, simpler and more straightforward compared with the traditional descriptions in Figure 1.1(a). Most importantly, it can be used for analysis, verification and even design guidance for SCDDC designs such as cross-coupled voltage doublers. Moreover, modelling SCDDCs with discrete models will provide designers with a new perspective for SCDDC's analysis and design. Large sets of analysis methods and tools for discrete models could be applied to

SCDDCs, potentially improving the analysis and design flow for them. The automation tools for discrete event models such as Workcraft [71] may promote design efficiency for SCDDCs, especially for large-sized systems. In addition, since Petri nets and STGs are generally used to analyse and design asynchronous circuits, modelling and designing SCDDCs with STG models may additionally facilitate the incorporation of positive features of asynchronous circuits to SCDDCs. These include no global clock distribution & clock skew problems, low power and high speed. These features for asynchronous circuits will provide SCDDCs with extra benefits for power conversion performance and power efficiency.

#### 1.1 Contributions

This thesis aims to present new modelling and design methods for SCDDCs in low power integrated systems with discrete event models. The following contributions have been made as a result of this research:

- A new modelling method that represents SCDDC with SC-STG (an extended STG) is proposed. With this new modelling method, the causality and concurrency relations between discrete events in SCDDCs can be described formally. A modified definition of multi-value transition enables analogue variation processes such as capacitor charging and discharging processes to be described with SC-STG. This method prevents the potential confusion in describing these relations with natural language and waveforms and facilitates the use of the rich set of tools available for SCDDC design and investigation.

- A new modelling approach that models reversion losses in SCDDCs with Petri nets is proposed. With the appropriate representation of events in SCDDCs with places and transitions, qualitative verification for reversion losses can be obtained by reachability analysis, by means of which all possible states of an SCDDC can be explored and investigated. Consequently, the related control scheme leading to a reversion loss can be detected and healthy controls that do not cause these events can be determined. In addition, the Petri net model also can be utilised to detect the reversion losses because of clock skew and clock jitter.

- A new reversion-loss-free SCDDC design method based on Petri nets and STGs is proposed. In this method, a healthy control scheme that avoids reversion losses can be determined at first based on the reachability analysis of the Petri net model. Then the healthy control scheme is modelled with STGs and the asynchronous control circuit producing such a control scheme can be obtained using tools such as Workcraft [71] and Petrify [72]. In the SCDDCs obtained with this new design method, there will be no reversion losses or clock mismatch problems (correct by the design). In addition, the new method is flexible, so that the obtained circuit synthesised by STG is able to produce control signals that are closed-loop with the target SCDDC.

- As a demonstration case study, a reversion-loss-free cross-coupled voltage doubler

is obtained using the new design method. By using a formalised method and less

design effort, the design achieves the same level of power efficiency as the best

existing designs. This new cross-coupled voltage doubler example is a good

demonstration for the validity of using the modelling methods presented in this

thesis for SCDDCs.

#### 1.2 Structure of the thesis

This thesis is organised as follows

- Chapter 1: This chapter briefly outlines the motivations and contributions of the thesis.

- Chapter 2: This chapter provides background information on SCDDCs and crosscoupled voltage doublers. It also introduces the basic definitions and properties of the Petri net model and the STG model. In addition, some existing modelling methods for SCDDCs are reviewed.

- Chapter 3: This chapter presents a new modelling method that models SCDDCs with SC-STGs. Examples of two different cross-coupled voltage doubler designs

are analysed with this new method. Subsequently, other SCDDCs with different topologies are also modelled with SC-STG.

- Chapter 4: This chapter presents a new modelling method that captures the reversion losses in SCDDCs with Petri nets. This concurrency and causality relations in Petri nets can be obtained from the SC-STG model. Several examples of existing cross-coupled voltage doubler designs are studied to demonstrate the modelling approach. Healthy control schemes that do not lead to reversion losses for these designs are determined and verified with reachability analysis of the Petri net models. In addition, further analysis of clock mismatch problems of these cross-coupled voltage doublers is also undertaken using the Petri net model.

- Chapter 5: This chapter presents a new design method for SCDDCs with Petri nets and STGs. This design method is extended from the Petri net model for reversion losses. A reversion-loss-free cross-coupled voltage doubler is designed with this new method in which reversion losses and timing mismatch problems are avoided. This new cross-coupled voltage doubler is implemented in UMC 65nm technology, and the analogue simulation results show high power efficiency and high performance.

- Chapter 6: This chapter summarises the modelling and design methods in this thesis.

Possible areas for future work also are discussed.

Figure 1.2: Main structure of the thesis.

Figure 1.2 depicts the relationships between the chapters. Apart from the modelling methods proposed, other critical contents of this thesis include analysing different cross-coupled voltage doublers with discrete event models and finally designing a new cross-coupled voltage doubler with discrete event models.

#### 1.3 Publications

The following is a list of publications and paper(s) to be submitted for review as a result of this research work.

- D. Li, D. Shang, F. Xia and A. Yakovlev, "Modelling Switched-Capacitor DC-DC Converters with Signal Transition Graphs," 2018 15th International Conference on Synthesis, Modelling, Analysis and Simulation Methods and Applications to Circuit Design (SMACD), Prague.

- D. Li, F. Xia, J. Luo and A. Yakovlev, "Modelling Reversion Loss and Shoot-through Current in Switched-Capacitor DC-DC Converters with Petri Nets," 2019 29th International Workshop on Power and Timing Modelling, Optimisation and Simulation (PATMOS), Rhodes.

- D. Li, F. Xia, D. Shang, J. Luo and A. Yakovlev, "Analyse and Design Reversion-loss-free Switched-Capacitor DC-DC Converters with Petri Nets," Journal paper (ready to submit).

## Chapter 2

## **Background**

The primary background information for this thesis is introduced in this chapter, which includes:

- SCDDCs

- Cross-coupled voltage doublers

- Existing modelling methods for SCDDCs

- Discrete event models

Basic knowledge of SCDDCs related to this thesis, including definition, topologies and reversion losses, is introduced in Section 2.1. Several cross-coupled voltage doublers, which are a specific type of SCDDCs and which are modelled and analysed with discrete event models in the following chapters, are preliminarily introduced and analysed in Section 2.2. Existing modelling methods for SCDDCs are reviewed in Section 2.3. Finally, an overview of discrete event models including Petri nets and STG, tools for discrete event models and asynchronous circuit design flow with discrete event models is provided in Section 2.4. Sections 2.1 – 2.3 pertain to the baseline of this research and Section 2.4 presents the modelling techniques used in this research.

#### 2.1 Switched-capacitor DC-DC converters

#### 2.1.1 Definition

A DC-DC converter is a power converter with a feature of converting a DC voltage at the input terminal to a different DC voltage at the output terminal [31]. Generally, there are three types of DC-DC converters in low power systems, including inductive, capacitive and inductive-capacitive DC-DC converters [32]. SCDDCs are capacitive DC-DC converters whose voltage-conversion activities rely only on switches and capacitors.

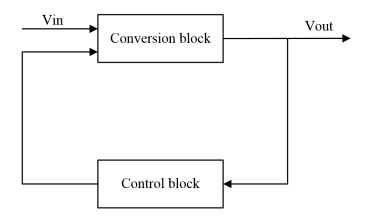

Figure 2.1: General structure for SCDDCs.

As shown in Figure 2.1, an SCDDC circuit includes a conversion block and a control block. The conversion block consists of switches and capacitors that implement the actual voltage conversion, whereas the control block manipulates events in the conversion block such as turning on and turning off switches based on the system requirements. The conversion block includes only switches and capacitors. Generally, control signals are clock signals, which control one or more switches in the conversion blocks. In an integrated SCDDC system, switches are realised by NMOS or PMOS devices. The capacitor employed in the conversion block to transfer the energy is called flying capacitor [32]. The word 'flying' denotes that neither of its two terminals is fixed at a specific voltage.

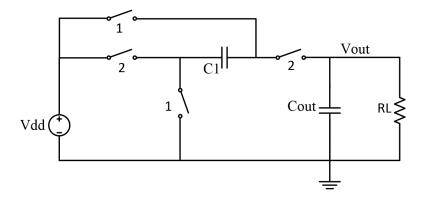

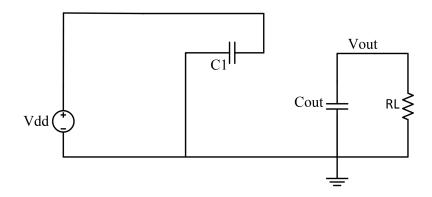

Each switching period of switches may be divided into several phases. With individual switches turned on and off in different phases, the conversion block can be configured into different SCDDC sub-nets. An SCDDC might implement two or more SCDDC sub-nets in different phases. Figure 2.2(a) shows a voltage doubler, which is configured into two different sub-nets during two phases.

#### (a) Voltage doubler

#### (b) Sub-net in the first phase

(c) Subnet in the second phase

Figure 2.2: Basic voltage doubler and its sub-nets.

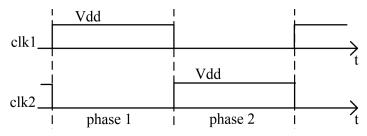

Figure 2.3: Control signals (Clock signals).

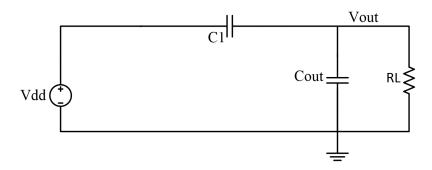

This voltage doubler consists of a flying capacitor C1 and four switches. This voltage doubler is controlled by control signals shown in Figure 2.3, Switches marked 1 are controlled by clock signal *clk1*, while switches marked 2 are controlled by *clk2*. The voltage input Vin is connected to a voltage source Vdd (Vin in all example SCDDCs in this thesis is connected to Vdd). This voltage doubler is configured into two sub-nets in two phases. In the first phase, switches marked 1 are turned on and switches marked 2 are turned off. The sub-net of the voltage doubler is shown in Figure 2.2(b). In this phase, capacitor C1 is charged to Vdd. In the second phase, with switches marked 2 turned on and switches marked 1 turned off, the voltage doubler is configured into a sub-net, as shown in Figure 2.2(c). In this phase, as C1 was charged to Vdd in the previous phase, the output voltage gets boosted to 2Vdd. According to [54], two nodes are capacitor coupling if they are connected with a capacitor, where a sudden change of voltage at one will cause a sudden change of voltage at the other. In this thesis, the voltage boost because of a pre-charged capacitor is called *capacitor coupling effect*.

The voltage doubler achieves a voltage output of 2Vdd with an input of Vdd. Therefore, the Voltage Conversion Ratio (VCR) for the voltage doubler is 2. The VCR of an SCDDC is defined as:

$$VCR = \frac{V_{out}}{V_{in}}$$

where  $V_{out}$  is the output voltage of an SCDDC and  $V_{in}$  is the input voltage of an SCDDC.

An SCDDC with VCR larger than 1 is called a step-up converter while the step-down converter has a VCR smaller than 1. Different VCRs can be achieved by different topologies which correspond to different configurations of switches and capacitors. Step-up converters can be implemented by topologies such as Ladder [33], Fibonacci multiplier [34], Parallel-Series Converter [35] and Multi-stage converter [36]. The step-down converter can be implemented by topologies such as Fractional Converter [37], Series-Parallel Converter [38] and Ladder [33].

All SCDDC examples analysed in this thesis are step-up converters for low power integrated systems. These SCDDCs are widely used in flash memories [32], LCD panels [33] and wireless energy harvesting systems [52].

#### 2.1.2 Topologies of SCDDCs

For SCDDCs, different VCRs can be achieved by different topologies. In this subsection, several topologies of step-up converters are introduced, which are then modelled and analysed in Chapter 3. All these SCDDCs are two-phase and controlled by two inverted clock signals, which are similar to the control signals shown in Figure 2.3. At the same time, switches marked 1 are controlled by *clk1* and switches marked 2 are controlled by *clk2*.

(c) Sub-net in the second phase Figure 2.4: Two-stage voltage doubler and its sub-nets.

The SCDDC shown in Figure 2.4(a) is a step-up converter. It is a two-stage voltage doubler where the output of the first stage acts as an input for the second stage, achieving a VCR

of 4. The clock signals for this two-stage voltage doubler are shown in Figure 2.3, which are also control signals for other SCDDCs in this subsection.

Like the voltage doubler shown in Subsection 2.1.1, the two-stage converter also has two phases. In the first phase, the converter is configured into the sub-net shown in Figure 2.4(b) and in the second phase it is configured into the sub-net shown in Figure 2.4(c). In the first phase, C1 and C2 are charged to Vdd and 2Vdd respectively. Then the output of the converter goes to 4Vdd in the second phase due to a capacitor coupling effect. Obviously, with the number of stages increased, the output voltage increases. For a k-stage doubler-type SCDDC, the VCR can be expressed as  $2^k$ .

(c) Sub-net in the second phase

Figure 2.5: Ladder and its sub-nets.

Figure 2.5(a) shows an SCDDC with a Ladder-type topology. This type of SCDDC can implement both step-up and step-down conversion. The ladder shown above is a step-up version, achieving a VCR of 3. For the step-up Ladder, the VCR equals to the number of flying capacitors.

This Ladder is controlled by two clock signals *clk1* and *clk2* as shown in Figure 2.3. In the first phase, switches controlled by *clk1* are turned on and switches controlled by *clk2* are turned off, and the Ladder circuit is configured into a sub-net as shown in Figure 2.5(b). The voltages at nodes *A* and *B* are 0 and Vdd, since they are connected to ground and Vdd respectively. As a result, C1 is charged to Vdd. Since C2 was charged to Vdd previously, the voltage at node *C* is 2Vdd, which charges C3 to Vdd. In the second phase, as switches controlled by *clk1* are turned off and switches controlled by *clk2* are turned on, the Ladder circuit is configured into a sub-net as shown in Figure 2.5(c). As in the previous phase, C1 and C3 were charged to Vdd, the voltages at node *B* and *C* are 2Vdd and 3Vdd respectively. Finally, the output voltage of the Ladder is 3Vdd.

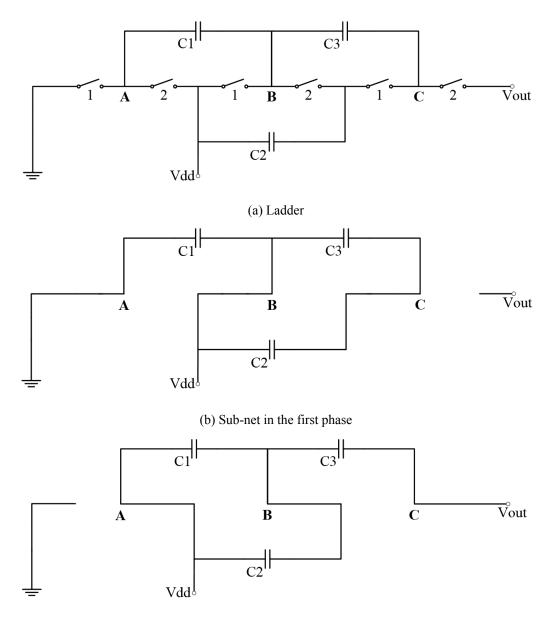

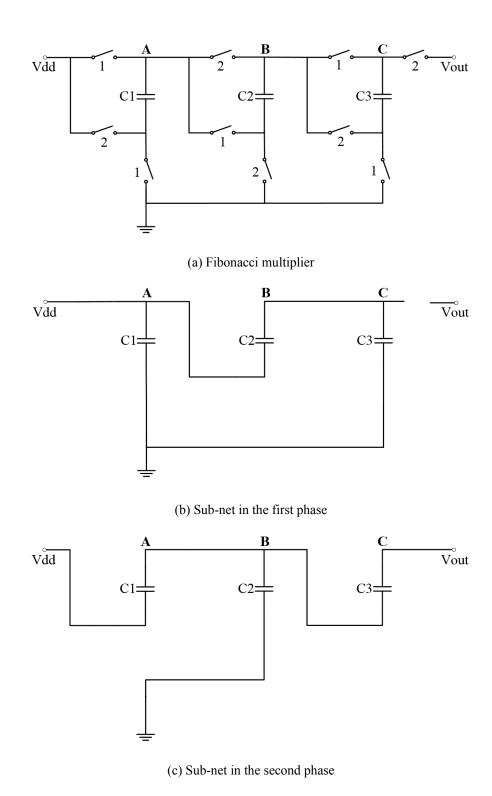

Figure 2.6(a) shows an SCDDC with a Fibonacci topology. A Fibonacci multiplier with n capacitors has a VCR of  $F_{n+2}$ , where  $F_{n+2}$  represents the  $(n+2)^{th}$  Fibonacci number. Fibonacci series is a set of numbers  $1, 1, 2, 3, 5, ..., F_{n-1}, F_n, F_{n+1}$ , where  $F_{n+1} = F_n + F_{n-1}$  and the value of the next number is the sum of the previous two numbers. Therefore, the three-capacitor Fibonacci multiplier shown above has a VCR of 5. A Fibonacci converter has the highest VCR for a given number of flying capacitors, among all two-phase topologies [11].

Figure 2.6: Fibonacci multiplier and its sub-nets.

This Fibonacci multiplier is also controlled by clock signals clk1 and clk2 shown in Figure 2.3. In the first phase, the converter is configured into a sub-net shown in Figure 2.6(b), since switches controlled by clk1 are on and switches controlled by clk2 are off. The node A is connected to Vdd, charging C1 to Vdd. As C2 was charged to 2Vdd previously, the voltages at node B and C are both 3Vdd. As a result, C3 is charged to 3Vdd.

In the second phase, the converter is configured into a sub-net shown in Figure 2.6(c). Because C1 and C3 were charged to Vdd and 3Vdd in the previous phase, the voltages at nodes *A*, *B* and *C* are 2Vdd, 2Vdd and 5Vdd respectively. As a result, the output voltage for this Fibonacci multiplier is 5Vdd.

The two-stage voltage doubler employs two flying capacitors while both the Ladder and Fibonacci multiplier employ three flying capacitors. Their VCRs are different; the Ladder has the lowest VCR of 3, the VCR of the two-stage doubler is 4 and the Fibonacci Multiplier has the highest VCR of 5. Because of the different topology configurations, the charging and discharging events among these converters are different. It is important to study why and how the VCRs of these converters have changed. Modelling these charging and discharging behaviours with discrete event models potentially helps us to do this analysis systematically, while the conventional methods presented here rely on verbal reasoning or other types of description that may cause confusion.

#### 2.1.3 Reversion losses

NMOS or PMOS devices are used as switches in an integrated SCDDC. However, the utilisation of MOS devices may bring about reversion losses in an SCDDC, leading to undesirable power and energy loss.

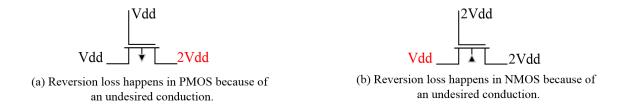

Reversion loss [39], which is also known as undesired charge loss or undesired charge transfer, is generated in an SCDDC with NMOS or PMOS switches under certain signal combinations. Three types of reversion loss happen on MOS switches, as introduced below.

Figure 2.7: Reversion loss in PMOS and NMOS.

For a PMOS switch as shown in Figure 2.7(a), when the gate and source terminals are connected to Vdd, it is on a turned-off state for a typical circuit whatever the drain terminal is connected to 0 or Vdd. However, in an SCDDC, the drain terminal of the PMOS switch may be connected to a voltage larger than Vdd, e. g. 2Vdd (Vdd > Vth). Consequently, this PMOS switch is conducting undesirably, causing a reversion loss from the output to the source terminal.

For an NMOS switch as shown in Figure 2.7(b), a reversion loss appears when the gate and drain terminals are connected to a voltage larger than Vdd, e.g. 2Vdd (Vdd > Vth), while the source terminal is connected to the voltage source of Vdd.

In an SCDDC, when such undesired conductions happen, undesired charges may flow back from the load to the flying capacitor, or from the flying capacitor to the power supply. In principle, the energy flow through an SCDDC should be from the energy source to the SCDDC, then from the SCDDC to the load. If energy flows in the opposite direction, e.g. from the load back to the SCDDC or directly to the source, or from the SCDDC to the source, a reversion loss event happens. A reversal of the energy flow reduces the efficiency of the SCDDC and causes its output voltage to drop. As a result, these types of events are known as energy and power 'losses'. In other words, energy/power that has already been delivered in the forward direction flows backwards and is 'lost' from the point of view of the load or SCDDC.

Figure 2.8: Shoot-through current.

Shoot-through current is also conventionally viewed as a type of reversion loss in an SCDDC [40]-[50], even though strictly speaking this is only partially the case. This thesis takes this convention and regards shoot-through current as a type of reversion loss. The effect of shoot-through current is the same as other types of reversion losses, i.e. reduced energy efficiency and output voltage drops.

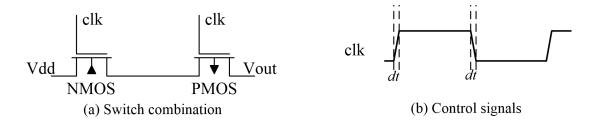

For example, in the MOS switch combination as shown in Figure 2.8(a) controlled by *clk* shown in Figure 2.8(b), shoot-through currents may happen from the output Vout to the voltage source Vdd if Vout > Vdd. When *clk* is in transition, because this transition does not happen instantaneously and there may be a time interval *dt* when both the NMOS and PMOS switches are conducting simultaneously, causing a charge from Vout to Vdd [45]. Shoot-through current in voltage doubler designs occurs from Vout (2Vdd) to Vdd rather than from Vdd to the ground in conventional circuits such as an inverter. Therefore, one part of the energy loss of shoot-through current is lost due to the reverse charge and the rest is lost locally that is similar as in conventional circuits.

Above all, MOS switches in SCDDCs are all gated by control signals or connected to the internal node in an SCDDC, so that the generation of these reversion losses are corresponding to the control signals and the voltage at the internal nodes. Chapter 4 presents the model and analysis of these reversion losses in SCDDCs with the help of Petri net models.

Since reversion losses are associated with combinations of certain signal combinations in SCDDCs, the usual method of eliminating them is to remove these signal combinations and then test again for the existence of reversion losses.

#### 2.2 Cross-coupled voltage doubler examples

Four cross-coupled voltage doublers are reviewed in this section. These voltage doublers are analysed using discrete event models such as extended STG model and Petri net model in Chapter 3 and Chapter 4. Based on these modelling works with discrete event models, a new design method and a new design of cross-coupled voltage doubler are presented in Chapter 5.

#### 2.2.1 Structure of the cross-coupled voltage doubler

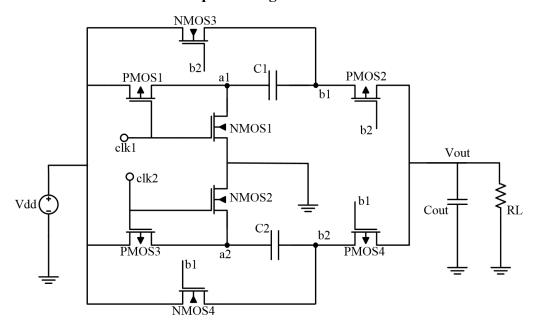

The cross-coupled voltage doubler is a common type of SCDDC, which is also named cross-coupled charge pump [40]. Compared with conventional MOS-device SCDDCs, the cross-coupled voltage doubler has advantages of higher output value and lower output ripple [18]. These features make it widely used in on-chip applications such as mixed-signal integrated systems [18], LCD drivers [41], DRAMs [45], ultrasonic transducer drivers [47] and wireless energy harvesting systems [52]. The schematic of a typical integrated cross-coupled voltage doubler is shown in Figure 2.9, referring as Voltage Doubler 1 in this thesis.

Figure 2.9: Cross-coupled voltage doubler, adapted from [18].

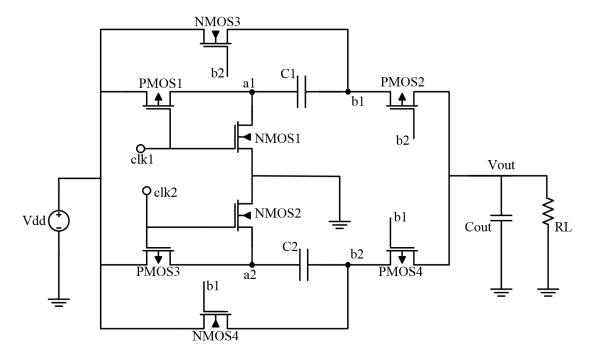

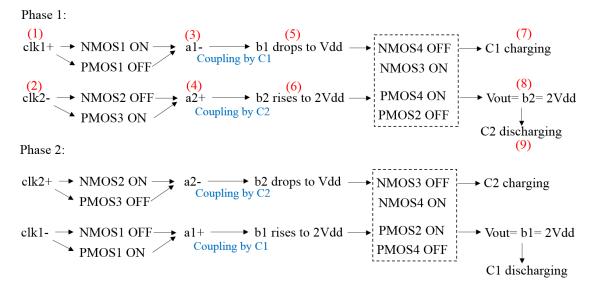

Voltage Doubler 1 includes two MOS-switch versions of the voltage doubler shown in Figure 2.2, with cross-coupled signals and MOS switch devices. Switches PMOS1, PMOS2, NMOS1, NMOS3 and flying capacitor C1 constitute the first voltage doubler while the second consists of PMOS3, PMOS4, NMOS2, NMOS4 and the flying capacitor C2. These two voltage doublers have a common input signal Vdd and output capacitor Cout. The MOS switch pair PMOS2 and PMOS4 is cross-coupled that each one is controlled by an internal signal from the other [53]. Also, NMOS3 is cross-coupled to the NMOS4. A simulated waveform of this voltage doubler is shown in Figure 2.10, where it is controlled by inverted control signals *clk1* and *clk2* (similar to controls shown in Figure 2.3).

Figure 2.10: Simulation result of Voltage Doubler 1.

In the phase that clkl = Vdd, clk2 = 0, NMOS1 is turned on and PMOS1 is turned off, making the internal node al 0V. Meanwhile, the voltage at the node al is Vdd since switch PMOS3 is on and NMOS2 is off, boosting the voltage at the node bl up to 2Vdd due to a capacitor coupling effect, as the flying capacitor C2 was charged to Vdd in the previous phase. Subsequently, switch NMOS3 that was controlled by the bl is turned on. As a result, the flying capacitor C1 is charged to Vdd in this phase through NMOS1 and NMOS3, which will bring bl up to 2Vdd in the next phase. At the same time, switch PMOS4 is turned on as bl is Vdd and bl is 2Vdd, charging the output to 2Vdd. In the next phase that clkl = 0, clkl = Vdd, the flying capacitor C2 is charged to Vdd and the output is charged to 2Vdd in a similar way. In other words, the output Vout is connected to either bl or bl, whichever is 2Vdd in any particular phase.

Compared with a single voltage doubler shown in Figure 2.2, the charging and discharging period of the flying capacitors is reduced by half, which indeed leads to a decrease of almost half of the output voltage ripple. At the same time, because each cross-coupled MOS switch is controlled by a signal from the other branch instead of its own source terminal, the turn-on voltage drop is reduced to a small drain-to-source voltage that is much smaller than the threshold voltage of Vth. Consequently, the output voltage of Voltage Doubler 1 is higher than the output voltages of other conventional MOS voltage doubler designs. Notably, there are a couple of internal signals including a1, a2, b1, b2 in Voltage Doubler 1, which affect

the turn-on and turn-off state of MOS switches and the charging and discharging of flying capacitors.

#### 2.2.2 Reversion losses in a cross-coupled voltage doubler

There are reversion-loss problems in cross-coupled voltage doublers. The reversion loss in Voltage Doubler 1 appears due to overlapped clock signals or clock signals with timing mismatches [18]. This subsection describes two types of reversion loss in Voltage Doubler 1 because of overlapped clock signals.

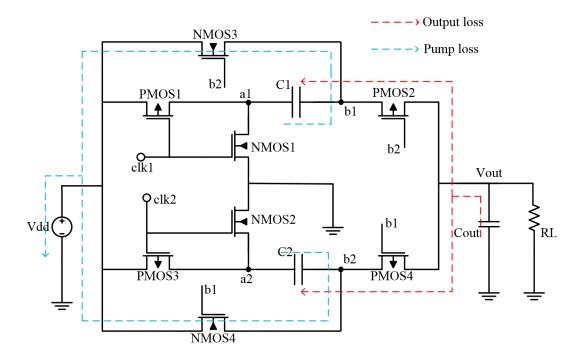

Figure 2.11: Reversion loss paths in Voltage Doubler 1.

# (a) Driven with non-overlapping signals

(b) Driven with overlapping signals

Figure 2.12: Waveforms for Voltage Doubler 1 driven with different clock signals.

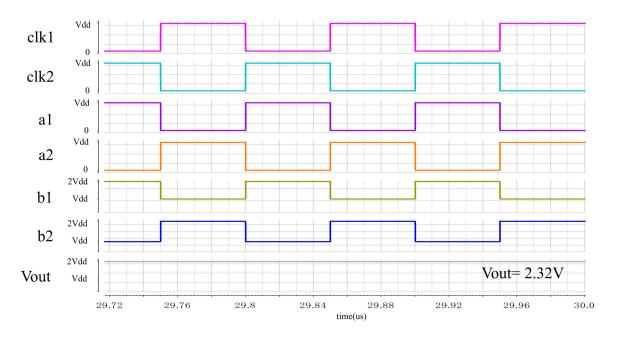

When Voltage Doubler 1 is driven by non-overlapping clock signals as shown in Figure 2.12(a), reversion losses happen during the non-overlapping interval between t1 and t2. Specifically, since both clk1 and clk2 are at the ground during this interval, a1 and a2 are both connected to Vdd and thus both b1 and b2 are at 2Vdd. In this situation, as switches NMOS3 and NMOS4 are turned on undesirably at the same time, reversion losses may exist. These undesired conductions cause reverse charges from C1 and C2 to Vdd, the paths of which are shown in Figure 2.11. This type of reversion loss from flying capacitors is called pump loss in the literature [40], as the flying capacitor in a Charge Pump [32] (the cross-coupled voltage doubler is also called a cross-coupled charge pump) is also called pump capacitor. As shown in the simulation waveform in Figure 2.12(a), there is a clear voltage drop during the time interval when both clk1 and clk2 are at 0. The output voltage

here drops compared with the voltage doubler driven with inverted clock signals due to the undesirable reverse charge. The reverse charge leads to additional power loss, thus reducing the power efficiency of the voltage doubler.

When the Voltage Doubler 1 is driven by overlapping signals as shown in Figure 2.12(b), reversion losses happen during the overlapping interval between t1 and t2. During this time interval, as both clk1 and clk2 are at Vdd, a1 and a2 are connected to ground, making b1 and b2 connected to Vdd. In this situation, PMOS2 and PMOS4 are turned on undesirably at the same time. As a result, reversion losses happen. These undesired conductions cause reverse charge from the output to flying capacitors C1 and C2, the paths of which are shown in Figure 2.11. This type of reversion loss from the output to flying capacitors is called output loss in the literature [40]. A noticeable voltage drop can also be seen during the overlapping interval in the waveform. Similarly, the output voltage drops and the power efficiency decreases due to these output losses.

Figure 2.13: VCRs for Voltage doubler 1 with different overlapping and non-overlapping clocks.

The level of the reversion loss is associated with the time of the non-overlapping or overlapping time gap. Figure 2.13 shows VCR of Voltage Doubler 1 is controlled by clocks with different scale of overlapping and non-overlapping time (with 10K loads). The VCR of the Voltage Doubler 1 drops with increase in the overlapping or non-overlapping time from 0 to 30us. When the time gap is over 35us, the reversion loss leads to failure of Voltage Doubler 1 to behave reasonably as a voltage doubler.

In summary, the nature of the pump losses and output losses are reverse charges due to the undesired conduction of MOS switches. The direct cause of these reversion losses are specific combinations of signals connected to the MOS switches.

# 2.2.3 Designs that eliminate reversion losses

A new cross-coupled voltage doubler design attempting to eliminate reversion losses is proposed in [18], which is referred to as Voltage Doubler 2 in this thesis. The schematics of Voltage Doubler 2 and its control signals are shown in Figure 2.14.

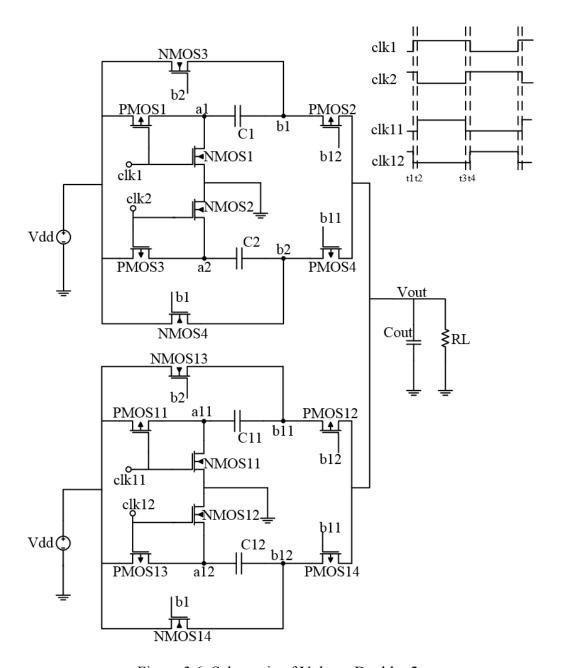

Figure 2.14: Voltage Doubler 2 and its control signals, adapted from [18]. As can be seen from the schematic in Figure 2.14(b), it has two copies of the Voltage Doubler 1 shown in Figure 2.9, with a further level of cross-coupled signals. Consequently,

the number of control signals and internal signals are doubled compared to Voltage Doubler 1.

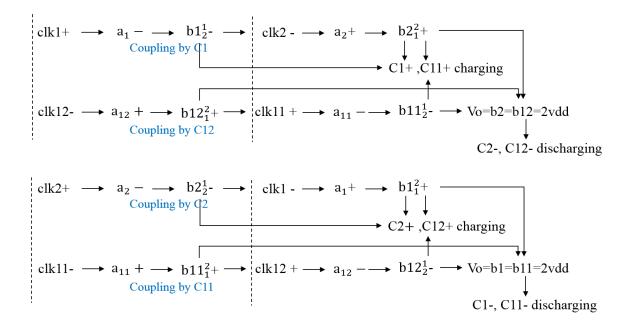

In Voltage Doubler 2, switches PMOS2 and PMOS4 of the upper doubler are controlled by internal signals *b12* and *b11* from the lower doubler instead of *b2* and *b1* from their own block. Similarly, switches NMOS13 and NMOS14 of the lower doubler are controlled by internal signals from the upper one. At the same time, the upper voltage doubler is controlled by overlapping clocks and the lower one is controlled by non-overlapping clocks, where the transitions of these clocks need to be synchronised strictly as shown in the Figure 2.14(a).

In this design, the reversion losses in one copy of the voltage doubler are eliminated by external controls from the other copy. During the time interval t1 to t2, b1 and b2 are both connected to Vdd and b11 and b12 are both at 2Vdd. For the upper one, there is no output loss from the output Vout to flying capacitors C1 and C2 as PMOS2 and PMOS4 are switched off by signals b12 and b11. Similarly, for the one below, there is no pump loss from C11 and C12 to Vdd since NMOS13 and NMOS14 are turned off by signals b2 and b1. Besides, this cross-coupled voltage doubler design is able to eliminate the shoot-through current compared with Voltage Doubler 1. This aspect is verified in Chapter 4 with Petri net model.

However, in this design, the control signals (clock signals) need to be strictly synchronised. There may be reversion losses when there is any timing mismatch of the control signals. Reversion losses due to timing mismatch of the control signals are also analysed with the Petri net model in Chapter 4.

To eliminate reversion loss problems as well as control signal synchronisation problems, a few newer cross-coupled voltage doubler designs are proposed [40]-[58]. The methods of these reversion-loss-free designs can be divided into two types. The first type of design eliminates the reversion loss by extra blocking transistors that switch off the path of the reversion loss when it happens. The second type of design cancels the reversion loss by introducing extra external control for the MOS switches that have the reversion loss problem. Two classical designs with these two types of techniques are introduced as follows. These designs are further analysed with Petri nets in Chapter 4.

Figure 2.15: Voltage Doubler 3 and its control signals, adapted from [40].

Figure 2.15 shows a classical design [40] with the first type of reversion loss elimination method, referred to as Voltage Doubler 3 in this thesis. Voltage Doubler 3 is controlled by control signals p1, p2, p3 and p4. Its MOS switches are controlled by internal signals BL, BR, IL, IR, which are indeed impacted by control signals p1, p2, p3 and p4 with capacitor coupling effects. There are two extra blocking MOS switches ML3 and ML4 controlled by signal TCO. TCO is a signal from the overlapping detector (the schematic can be seen in [40]).

In theory, there will be output losses from the output Vout to the flying capacitors during the overlapping interval of the clock pair (p1, p2). However, output losses in Voltage Doubler 3 have been blocked by extra MOS switches. Two extra MOS switchers ML3 and MR3 controlled by TCO are utilised to block the path of the reversion loss. TCO signal will be activated by the extra overlapping detector when p1 and p2 are both in transition as

shown in Figure 2.15(b) or a timing mismatch happens as shown in Figure 2.15(c). Switches ML3 and MR3 will be turned off when TCO is activated, blocking the path of the reversion loss from the output. In addition, clock signal pairs (p1, p3) and (p2, p4) are non-overlapping, so that neither signal pairs (IL, BL) nor (IR, BR) will be at 2Vdd at the same time. Consequently, there is no pump loss from flying capacitors to Vdd.

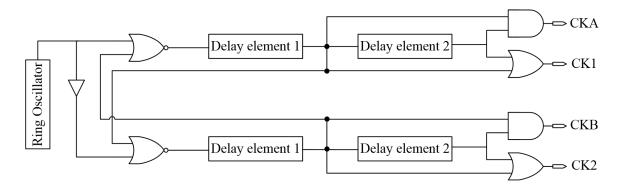

Figure 2.16: Voltage Doubler 4 and its control signals, adapted from [47].

Compared with Voltage Doubler 2, this type of voltage design has a further capability of eliminating the reversion loss due to the control signal mismatch. However, the trade-off is introducing extra MOS devices and extra overlapping detector circuit. Notably, similar to Voltage Doubler 2, there are also some internal signals introduced in Voltage Doubler 3, including *IL*, *BL*, *IR*, *BR*.

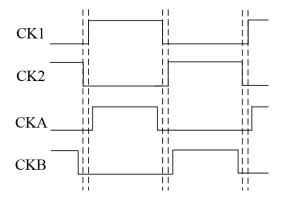

Figure 2.16(a) shows a cross-coupled voltage doubler design [47] which eliminates reversion losses by employing the second type of elimination method, and this is referred to as Voltage Doubler 4 in this thesis. Voltage Doubler 4 also has four control signals *CK1*, *CK2*, *CKA* and *CKB*. The MOS switches are controlled by internal signals *V1*, *V2*, *Va*, *Vb*, which are indeed impacted by control signals *CK1*, *CK2*, *CKA* and *CKB* with capacitor coupling effects. In addition, another two extra signals *GP1* and *GP2* are introduced to control the PMOS1 and PMOS2.

In theory, there will be output losses from the output Vout to the flying capacitors during the overlapping interval of the clock pair (*CK1*, *CK2*) if PMOS1 and PMOS2 are controlled by *V2* and *V1*. However, such reversion losses for PMOS1 and PMOS2 are eliminated by introducing external controls of *GP1* and *GP2*. The value of external controls *GP1* and *GP2* are affected by internal signals *Va* and *Vb* with two extra pairs of MOS switches. *GP1* and *GP2* are indeed controlled by *CKA* and *CKB*, as *CKA* and *CKB* are capacitor coupling with *Va* and *Vb*. Then [47] develops a control scheme that avoids the reversion loss problem based on conventional waveform analysis, which is shown in Figure 2.16(b). During the overlapping interval of (*CK1*, *CK2*), *CKA* and *CKB* are both at 0, *Va* and *Vb* are then both at Vdd because of capacitor coupling effects and *GP1* and *GP2* are both connected to 2Vdd. As a result, *GP1* and *GP2* will turn off PMOS1 and PMOS2 during the overlapping interval so that the output losses are avoided. Meanwhile, it is also claimed that there are no pump losses as *CK1* and *CK2* are non-overlapping that *V1* and *V2* will not be at 2Vdd at the same time.

Compared with the Voltage Doubler 2, transitions of control signals do not need to be synchronised. Compared with the Voltage Doubler 3, this design does not need an extra blocking transistor and overlapping detector. However, the scheme of the control signals that will not lead to a reversion loss for Voltage Doubler 4 or other cross-coupled voltage doublers adopting similar reversion loss eliminating techniques requires careful analysis, as signals in such designs are complicated. As the complexity increases, the conventional

methods of verbal reasoning and waveform analysis become cumbersome and less trustworthy.

A common phenomenon existing in the cross-coupled voltage designs introduced in this subsection is that there are a couple of control signals and internal signals. These signals control the MOS switches directly or indirectly, which may further affect the working principle of these designs. However, the conventional modelling methods for SCDDCs seem to overlook these signals and the relationship between these signals, which may cause confusion for the reader in understanding these designs. At the same time, some states of these signals may also cause a reversion loss problem. These designs propose different techniques to avoid reversion losses, and there is no formal way to describe and analyse the reversion loss that can be used for formal verification. The design methods also depend heavily on intuition, as formal discrete state models for design did not exist until the work reported in this thesis. In addition, the design methods adopted in these designs are not flexible (being dependent on dedicated clock generators), as demonstrated and analysed with Petri nets in Chapter 4.

# 2.3 Existing modelling methods

In this section, the modelling methods of Charge Flow Analysis and Output Impedance Analysis are introduced. Using these modelling methods for an SCDDC, an optimal value for the flying capacitor and the working frequency of control signals can be selected to achieve a higher power conversion performance and power efficiency.

# 2.3.1 Charge Flow Analysis

In Charge Flow Analysis [10] for SCDDCs, a set of vectors is defined to describe the topologies and to identify the sub-net configurations in different phases based on the charge flow through switches and capacitors. Charge Flow Analysis quantifies SCDDCs' performance and enables objective comparison of SCDDCs' topologies, playing an essential role in the conventional modelling methods of SCDDCs.

The charge flow through the capacitors is defined as:

$$a_c^{(1)} = \left[ q_{out}^{(1)} \, q_1^{(1)} \dots \, q_n^{(1)} \, q_{in}^{(1)} \right] / \, q_{out}$$

$$a_c^{(2)} \, = \, \left[ q_{out}^{(2)} \, q_1^{(2)} \, ... \, q_n^{(2)} \, q_{in}^{(2)} \right] / \, \, q_{out}$$

...

$$a_c^{(m)} = \left[ q_{out}^{(m)} \, q_1^{(m)} \dots \, q_n^{(m)} \, q_{in}^{(m)} \right] / \, q_{out}$$

Where  $q_i^{(m)}$  denotes the amount of charge transferred to flying capacitor i during phase m, and  $q_{out}$  represents the total amount of charge that is transferred to the output during a switching period T.

The values of each vector element follow the undernoted principles:

- Kirchhoff's current law. The sum of charge flow elements at every circuit node equals to zero.

- For every capacitor, the sum of charge flow elements of all phases equals zero.

For example, the charge flow vectors for the voltage doubler shown in Figure 2.1 are shown in below:

$$a^1 = [0 \quad -1 \quad 1]$$

$$a^2 = [1 \ 1 \ 1]$$

As can be seen clearly from the vectors, the vector elements of the flying capacitors in two phases have opposite signs. More details about Charge Flow Analysis can be reviewed in [10] and [32].

Output Impedance Analysis and related calculations introduced in Subsection 2.3.2 are based on Charge Flow Analysis.

# 2.3.2 Output Impedance Analysis

In the Output Impedance Analysis model, SCDDCs are modelled as a combination of an ideal DC-transformer with a fixed VCR and a finite output resistance [59], which is shown in Figure 2.17.

Figure 2.17: Output Impedance Analysis Model for SCDDCs.

Figure 2.18: SSL and FSL impedance model for SCDDCs.

There are two distinct asymptotic limits to the output impedance: Slow Switching Limits (SSL) and the Fast Switching Limits (FSL). These two impedance models are related to the switching frequency, as shown in Figure 2.18.

# **Slow Switching Limits (SSL)**

SSL is an analysis based on the effect of the switched-capacitor nature of the converter, assuming that the resistances of switches and other interconnects are ideal [57]. The SSL impedance is a function of the switching frequency and the amount of flying capacitance. For an SCDDC with i flying capacitors and m phases, the SSL impedance is described as follows:

$$R_{SSL} = \sum_{cap,i} \sum_{phases,m} \frac{(a_{c,i}^m)^2}{2f_{sw}C_i}$$

where  $a_{c,i}^m$  is the charge flow vector element of the capacitor i in the  $m^{th}$  phase.

For a two-phase SCDDC, the SSL impedance is described as:

$$R_{SSL} = \sum_{\substack{cap,i \\ 33}} \frac{a_{c,i}^2}{f_{sw}C_i}$$

The SSL impedance models the power loss due to the charging and discharging of the flying capacitors, ignoring the parasitic resistance in an SCDDC. This impedance can be obtained by only examining the charge flow in SCDDCs, without complex network analysis or simulations.

# **Fast Switching Limits (FSL)**

FSL is an analysis based on the resistive nature of the converter, assuming capacitors as a fixed voltage source [57]. The FSL impedance is frequency independent. For an SCDDC with n switches and m phases, the FSL impedance is described as follows:

$$R_{FSL} = \sum_{\text{switchers, i phases, m}} \frac{(a_{R,i}^m)^2}{G_i D_m}$$

where  $a_{R,i}^m$  is the charge flow vector element of the switch i in the  $m^{th}$  phase,  $G_i$  is the conductance of the switch i and  $D_i$  is the duty cycle of the phase m.

For an SCDDC with *n* switches and *m* phases with a 50% duty cycle, the FSL impedance is described as follows:

$$R_{FSL} = 2 \sum_{switchers.i} \frac{(a_{R,i})^2}{G_i}$$

Analogous to the SSL impedance, the FSL impedance is determined by the component parameters and charge flow vectors of the switches.

# Practical output impedance

Both the SSL and the FSL impedance only model the output impedance of SCDDCs in extreme cases. In practice, an SCDDC is subject to both capacitive and resistive power losses. In [11], the practical output impedance *Rout* is described as a combination of SSL and FSL impedance, which is expressed as follows.

$$Rout = \sqrt{{R_{SSL}}^2 + {R_{FSL}}^2}$$

The practice output impedance can be used to improve the power efficiency of an SCDDC. Generally, the power efficiency  $\eta$  [32] of an SCDDC is defined as:

$$\eta = \frac{P_{out}}{P_{out} + P_{loss}} \times 100\%$$

Where  $P_{out}$  is the output power and  $P_{loss}$  is the total power loss in an SCDDC. The power loss due to the practical output impedance Rout is a significant part of the total power loss.

Therefore, Output Impedance Analysis gives the designer a simple way to estimate the power loss due to both charging and discharging of the capacitors and the resistance of the switches without complex analysis and simulations. At the same time, the total power loss can be reduced by optimising the parameters of SCDDCs such as switching frequency and flying capacitance, enabling an SCDDC design with higher power efficiency.

In summary, the existing modelling methods overviewed in this section concentrate on the analogue attributes such as charge flow and equivalent output impedance of SCDDCs. Generally, these conventional modelling methods overlook discrete attributes such as signal transition and relations between transitions of SCDDC. They do not, consequently, shed light on the qualitative question of the existence or absence of reversion loss. There are only natural language descriptions with assisted waveform employed to describe these discrete events in the literature, which are not easy to understand and cause confusion.

# 2.4 Discrete event Models

In this thesis, discrete event models such as Petri nets and Signal Transition Graph (STG) are utilised to model and analyse discrete events and their relationships in SCDDCs. Furthermore, asynchronous control design based on STG for SCDDCs is included in Chapter 5. This section presents the background for these discrete event models and then provides a fundamental review of asynchronous circuit design flow and the related CAD tools.

### 2.4.1 Petri nets

Petri nets were first introduced in the early 1960s, which are graphical and mathematical representations of distributed systems [60]. Petri nets are widely used to describe and analyse distributed, concurrent and non-deterministic systems. The Petri net model shows possible behaviours of discrete systems using a simple graphical description of the system.

# **Definitions**

A Petri net model *PN* is a tuple  $C = \langle P, T, F, M_0 \rangle$  where  $P = \{p_1, p_2, p_3, ..., p_n\}$  is a finite non-empty set of places,

$T = \{t_1, t_2, t_3, ..., t_n\}$  is a finite non-empty set of transitions such that  $P \cap T = \phi$ ,

$F \subseteq P \times T \cup T \times P$  is a flow relation between place P and transition T,

$M_0 \in [P \to N]$  is the initial marking.

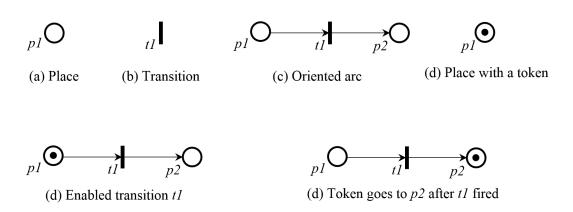

Figure 2.19: Elements of Petri nets.

Figure 2.19 shows some elements of a Petri net graph, where places are represented by circles (Figure 2.19(a)), rectangles represent transitions (Figure 2.19(b)) and oriented arcs indicate flow relations between places and transitions (Figure 2.19(c)). A marking is represented by a set of tokens (solid disks) inside the places of a Petri net (Figure 2.19(d)). The Petri net marking represents its current state. The Petri net state changes with firings of its enabled transitions. A transition is enabled if all of its input places (A place with an arc from itself to a transition is an input place of the transition) have tokens and an enabled transition may fire (Figure 2.19(e)). The firing of a transition decreases the number of tokens in every one of its input places by one and increases the number of tokens in every one of its output places (a place with an arc from a transition to itself is an output place of the transition.) by one (Figure 2.19(f)).

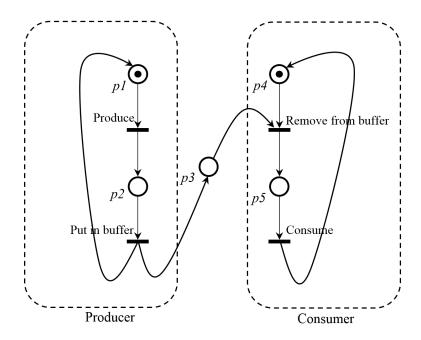

Figure 2.20: Petri net example: Producer and Consumer problem.

Figure 2.20 shows a simple Petri net example of the Producer and Consumer problem. This Petri net model contains five places and four transitions, with places *p1* and *p4* each holding a token, which describes that as long as the producer produces an object and puts it into the buffer, the consumer can remove it from the buffer and consume it.

# Reachability analysis

Reachability analysis investigates whether a target state is reachable from a specific initial marking in a Petri net model. It plays a critical role in Petri net theory, since other problems such as liveness analysis and deadlock verification can be reduced to reachability analysis [60]. In actual Petri net applications, it is commonly used to detect fault or hazard problems [61]-[64].

# 2.4.2 Signal Transition Graphs (STGs)

The Signal Transition Graph (STG) model was first introduced in [20] and [25] to formally model the behaviour of asynchronous circuits and their environments. STG is a domain-specific Petri net for specifying asynchronous circuits. An STG has two types of transitions, positive transition and negative transition, to represent the signal behaviours (rising and falling voltages) in a circuit. With directed arcs indicating the relations between these signal transition behaviours, STG clearly defines the causality and concurrent relationship for a circuit.

### **Definition**

An STG is a tuple  $G = \langle PN, I, O, L \rangle$  where

$S \in [I \cup O]$  is a set of all input and output signals,

$L: T \to S \times \{+, -\}$  is the labelling function,

$S \times \{+, -\}$  is the set of transitions of input and output signals.

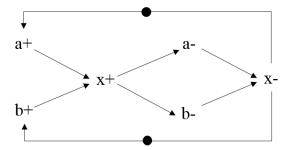

Figure 2.21: Example of an STG modelling a system with featuring concurrency.

As STGs are derived from Petri nets, the graphic representations of STGs are similar to Petri nets. An STG example of a system featuring concurrency is shown in Figure 2.21. In this STG, all places are hidden, which allows transitions to be connected with an arc directly, e.g. on the arc between a+ and X+, there is assumed to be a place which is removed in the representation. This STG describes the concurrency and causality relationships between signal transitions in this concurrent system. Tokens on the arcs between X- and A+ and A+ indicate the initial state of this system.

### Formal verification methods

STGs provide asynchronous circuits with a convenient theoretical background for specifications and verifications. The property verifications for STGs include:

- Deadlock-freeness: There is no state where all signals are disabled.

- Consistency: In any firing sequences starting from  $M_0$ , the positive and negative transitions of every signal must alternate.

- Output-persistence: An enabled transition of an output signal must not be disabled by a transition of any other signal.

- Complete State Coding (CSC): if there are two markings with the same binary code, the output signals enabled at those markings should be the same.

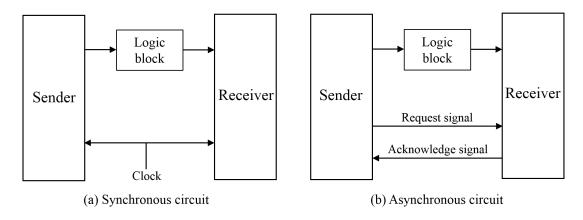

# 2.4.3 Asynchronous circuits