# INVESTIGATION INTO SCALABLE ENERGY AND PERFORMANCE MODELS FOR MANY-CORE SYSTEMS

Mohammed A. Noaman Al-hayanni

A Thesis Submitted for the Degree of Doctor of Philosophy at Newcastle University

School of Engineering

Faculty of Science, Agriculture and Engineering

May 2019

# **DECLARATION**

I hereby declare that this thesis is my own work and effort and that it has not been submitted anywhere for any award. Where other sources of information have been used, they have been acknowledged.

Newcastle upon Tyne - May 2019

Mohammed A. Noaman Al-hayanni

# CERTIFICATE OF APPROVAL

I confirm that, to the best of my knowledge, this thesis is from the student's own work and effort, and all other sources of information used have been acknowledged. This thesis has been submitted with my approval at the School of Engineering / Newcastle University for the degree of PhD in Electrical and Electronic Engineering / Computer Engineering.

| Alex Yakovlev |

|---------------|

|               |

|               |

|               |

| D: 1 101 (1   |

| Rishad Shafik |

|               |

|               |

| Fei Xia       |

# To my lovely family. — Mohammed Al-hayanni

I would like to express my sincere gratitude to my supervisors Prof. Alex Yakovlev, Dr. Rishad Shafik and Dr. Fei Xia for their support and guidance through my Ph.D. journey. They have always been a source of motivation and my inspirational model as a researcher.

I am grateful to my sponsor Higher Committee of Education Development (HCED) in Iraq for funding my Ph.D. study through their scholarship program. Furthermore, I am thankful to the University of Technology-Iraq for giving the opportunity to join the scholarship and also would like to express my sincere gratitude to the Iraqi Cultural Attache in London.

I would like to express my great thanks to (PRiME) project members for their support and useful discussions.

I am thankful to Dr. Ashur Rafiev for his supporting through continues discussions, experimental works, and preparing synthetic benchmark programs.

I am also grateful to Dr. Waleed Fawwaz for his advice and suggestions for preparing some Matlab codes.

I would also like to express my gratefulness and appreciation to my colleagues and friends in the School of Engineering, particularly those in  $\mu$ Systems Research Group at Newcastle University for their assistance through my study.

I would like to offer my special regards to all the staff of the Electrical and Electronic Engineering in the School of Engineering at Newcastle University.

Last but not least, I would like to thank my beautiful family for their continuous support and motivation throughout my Ph.D. journey.

Recite in the name of your Lord who created - Created man from a clinging substance. Recite, and your Lord is the most Generous - Who taught by the pen -Taught man that which he knew not.

The holy Quran - Chapter 30 - Verse 96 - (1-5).

It is likely that many-core processor systems will continue to penetrate emerging embedded and high-performance applications. Scalable energy and performance models are two critical aspects that provide insights into the conflicting trade-offs between them with growing hardware and software complexity. Traditional performance models, such as Amdahl's Law, Gustafson's and Sun-Ni's, have helped the research community and industry to better understand the system performance bounds with given processing resources, which is otherwise known as speedup. However, these models and their existing extensions have limited applicability for energy and/or performance-driven system optimization in practical systems. For instance, these are typically based on software characteristics, assuming ideal and homogeneous hardware platforms or limited forms of processor heterogeneity. In addition, the measurement of speedup and parallelization factors of an application running on a specific hardware platform require instrumenting the original software codes. Indeed, practical speedup and parallelizability models of application workloads running on modern heterogeneous hardware are critical for energy and performance models, as they can be used to inform design and control decisions with an aim to improve system throughput and energy efficiency.

This thesis addresses the limitations by firstly developing novel and scalable speedup and energy consumption models based on a more general representation of heterogeneity, referred to as the normal form heterogeneity. A method is developed whereby standard performance counters found in modern many-core platforms can be used to derive speedup, and therefore the parallelizability of the software, without instrumenting applications. This extends the usability of the new models to scenarios where the parallelizability of software is unknown, leading to potentially Run-Time Management (RTM) speedup and/or energy efficiency optimization. The models and optimization methods presented in this thesis are validated through extensive experimentation, by running a number of different applications in wide-ranging concurrency scenarios on a number of different homogeneous and heterogeneous Multi/Many Core Processor (M/MCP) systems. These include homogeneous and heterogeneous architectures and

range from existing off-the-shelf platforms to potential future system extensions. The practical use of these models and methods is demonstrated through real examples such as studying the effectiveness of the system load balancer.

The models and methodologies proposed in this thesis provide guidance to a new opportunities for improving the energy efficiency of M/MCP systems.

The contributions in this thesis have supported by diverse publications which include a large amount of work during the journey of my study. They are published in different papers including journal, magazine, conferences and technical reports. The materials are covered in separate chapters. The publications which include the *contributions* of this thesis are listed as follows:

## Journals and Magazines Publications:

1. Ashur Rafiev; **Mohammed A. N. Al-hayanni**; Fei Xia; Rishad Shafik; Alexander Romanovsky; Alex Yakovlev, *Speedup and Power Scaling Models for Heterogeneous Many-Core Systems*, Transactions on Multi-Scale Computing Systems (TMSCS), 12 January 2018, Page(s): 436 - 449, DOI: 10.1109/TMSCS.2018.2791531, Publisher: IEEE, Electronic ISSN: 2332-7766.

The underpinning studies of this paper can be found in Chapter 3 and Chapter 4. It includes the essential *contributions* of this literary work which represented by extending the assumption of system heterogeneity to cover such modern Multi/Many-Core Processors (M/MCP) configurations. It presents the attempt to extend the classical speedup models (Amdahl, Gustafson, and Sun-Ni) to estimate power and energy normalized speedup metrics. Thus, it studies the power/performance trade-offs of the extended models for energy-efficient computing in diverse M/MCP configurations. Further, This literature considers the effect of Dynamic Voltage Frequency Scaling (DVFS) techniques on all power and energy models. Moreover, it clarifies the limitations of the Amdahl-like heterogeneous models and outlining further challenges of heterogeneous speedup and power modeling.

On the other hand, this paper performs intensive validations experiments. It validates the extended models on real heterogeneous platforms on the Odroid XU<sub>3</sub> platform and dual-GPU laptop under a set of carefully controlled model parameters. Furthermore, it uses these

models to evaluate the efficiency of the Linux scheduler's load balancing while running realistic workloads.

In addition, the synthetic benchmark used in this paper has been included in Appendix A, the source code for Open Computing Language (OpenCL) version is also available in [1], and the full data set have included in Appendix B.

# Conference Publications:

1. **Mohammed A. N. Al-hayanni**; Ashur Rafiev; Rishad Shafik; Fei Xia, *Power and Energy Normalized Speedup Models for Heterogeneous Many-Core Computing*, 16th International Conference on Application of Concurrency to System Design (ACSD), 19-24 June 2016, pp 84 - 93, DOI: 10.1109/ACSD.2016.16, Publisher: IEEE.

The underpinning studies of this paper can be found in Chapters 3, 4 and 5. This paper demonstrates the first attempt to extend the classical speedup models (Amdahl, Gustafson, and Sun-Ni) for energy efficient computing. It demonstrates the theoretical calculations for all extended speedup models. In addition, it explains the first set of experimental work.

2. **Mohammed A. N. Al-hayanni**; Rishad Shafik; Ashur Rafiev; Fei Xia; Alex Yakovlev, *Speedup and Parallelization Models for Energy-Efficient Many-Core Systems Using Performance Counters*, International Conference on High-Performance Computing and Simulation (HPCS), 17-21 July 2017, PP: 410 - 417, DOI: 10.1109/HPCS.2017.68, Publisher: IEEE.

The underpinning studies of this paper can be found in Chapter 5. It extends the Amdahl's speedup model considering applications and system software related overhead separately. Moreover, It proposes a novel method to model the parallelization ratio for executed applications. This paper performs intensive validations experiments to validate the proposed models. Furthermore, it demonstrates the effectiveness of our method for identifying parallelization-aware energy-efficient system configurations using power/energy metrics.

## Technical Reports and Memos:

1. **Mohammed A. N. Al-hayanni**; Ashur Rafiev; Rishad Shafik; Fei Xia; Alex Yakovlev, *Extended Power and Energy Normalized Performance Models for Many-Core Systems*, Technical Report Series, NCL-EEE-MICRO-TR-2016-198, Year: 2016, Newcastle University, μSystems Research Group, School of Engineering. Available at http://async.org.uk/tech-reports/NCL-EEE-MICRO-TR-2016-198.pdf.

The underpinning studies of this paper can be found in Chapters 3, 4 and 5. It attempts to extend the assumption of heterogeneity for classical speedup models. It includes the theoretical modeling and calculations of all performance and power models. Also, it contains the first set of experimental works.

2. **Mohammed A. N. Al-hayanni**; Rishad Shafik; Ashur Rafiev; Fei Xia; Alex Yakovlev, *Speedup and Parallelization Models for Energy-Efficient Many-Core Systems Using Performance Counters*, Technical Report Series, NCL-EEE-MICRO-TR-2017-205, Year: 2017, Newcastle University, μSystems Research Group, School of Engineering UK. Available at http://async.org.uk/tech-reports/NCL-EEE-MICRO-TR-2017-205.pdf.

The underpinning studies of this paper can be found in Chapter 5. It attempts to extend the Amdahl speedup model and system software separately. It uses hardware performance counter to avoid the need for instrumenting applications. In addition, This paper proposes a new method to model the parallelization ratio for different applications. Furthermore, it performs extensive synthetic and real benchmarks experiments to validate all models. The full data set of performance and power of the Princeton Application Repository for Shared-Memory Computers (PARSEC) benchmarks of this paper included in AppendixC

#### **Other Contributions:**

I also contributed in the following work:

1. Fei Xia; Ashur Rafiev; Ali Aalsaud; **Mohammed A. N. Al-hayanni**; James Davis; Joshua Levine; Andrey Mokhov; Alexander Romanovsky;

Rishad Shafik; Alex Yakovlev; Sheng Yang, *Voltage, Throughput, Power, Reliability, and Multicore Scaling*, Journal: Computer, Year: 2017, Volume: 50, Issue: 8, pp: 34 - 45, DOI: 10.1109/MC.2017.3001246, ISSN: 0018-9162.

# CONTENTS

| I | Τŀ  | nesis ( | Chapte    | rs                                           | 1  |

|---|-----|---------|-----------|----------------------------------------------|----|

| 1 | INT | RODUC   | CTION     |                                              | 3  |

|   | 1.1 | Motiv   | ation and | d Challenges                                 | 3  |

|   | 1.2 | Aim a   | nd Objec  | ctives                                       | 6  |

|   | 1.3 | Thesis  | s Organiz | ration and Key Findings                      | 7  |

| 2 | ВАС | KGROU   | JND AND   | LITERATURE REVIEW                            | 9  |

|   | 2.1 | Introd  | luction . |                                              | 9  |

|   | 2.2 | Micro   | /Nano E   | lectronic Technology Scaling                 | 10 |

|   | 2.3 | From    | Single-Co | ore to Multi/Many-Core (M/MCP)               | 11 |

|   | 2.4 | M/M     | CP Archi  | tecture                                      | 13 |

|   |     | 2.4.1   | Homog     | eneous M/MCP                                 | 14 |

|   |     | 2.4.2   | Heterog   | geneous M/MCP                                | 14 |

|   |     | 2.4.3   | Dynami    | ic M/MCP                                     | 16 |

|   | 2.5 | The M   | 1ethods o | of Energy Efficiency                         | 16 |

|   |     | 2.5.1   | Dynami    | ic Voltage Frequency Scaling (DVFS)          | 17 |

|   |     | 2.5.2   | Thread    | to Core Affinity Managements                 | 17 |

|   |     | 2.5.3   | Energy    | Efficient Load Balancing, Task Migration and |    |

|   |     |         | Task Sc   | heduling Over M/MCP                          | 18 |

|   | 2.6 | Speed   | lup Mode  | els                                          | 19 |

|   |     | 2.6.1   | Extende   | ed Speedup Models in M/MCP                   | 21 |

|   |     |         | 2.6.1.1   | Extended Speedup Models for Performance      |    |

|   |     |         |           | Calculations in M/MCP (Hill-Marty Models) .  | 21 |

|   |     |         | 2.6.1.2   | M/MCP Overheads                              | 23 |

|   |     |         | 2.6.1.3   | Parallelization Factor (p)                   | 25 |

|   |     |         | 2.6.1.4   | Extended Speedup Models in Networks          | 25 |

|   |     |         | 2.6.1.5   | Extended Speedup Models in Run-Time          |    |

|   |     |         |           | Management (RTM) System                      | 26 |

|   |     |         | 2.6.1.6   | Extended Speedup Models for Energy           |    |

|   |     |         |           | Efficiency in M/MCP                          | 27 |

|   |     |         | 2.6.1.7   | -                                            | 29 |

|   |     | 2.6.2   | Multi-A   | mdahl Model                                  | 30 |

|   | 2.7 | Discu  | ssions and Conclusions                           | 31 |

|---|-----|--------|--------------------------------------------------|----|

| 3 | SPE | EDUP A | AND POWER SCALING MODELS                         | 35 |

|   | 3.1 | Introd | luction                                          | 35 |

|   | 3.2 | Existi | ng Speedup Models                                | 38 |

|   |     | 3.2.1  | Amdahl's Law (Fixed Workload)                    | 38 |

|   |     | 3.2.2  | Gustafson's Model (Fixed Time)                   | 39 |

|   |     | 3.2.3  | Sun-Ni's Model (Memory Bounded)                  | 40 |

|   |     | 3.2.4  | Hill-Marty's Heterogeneous Models                | 41 |

|   | 3.3 | Heter  | ogeneous System                                  | 41 |

|   |     | 3.3.1  | The Challenges of Heterogeneous Modeling         | 41 |

|   |     |        | 3.3.1.1 Hardware-dependent parallelizability     | 42 |

|   |     |        | 3.3.1.2 Workload equivalence and performance     |    |

|   |     |        | comparison                                       | 42 |

|   |     | 3.3.2  | Platform Assumptions                             | 43 |

|   |     | 3.3.3  | Normal Form Representation of Heterogeneity      | 44 |

|   | 3.4 | Propo  | sed Heterogeneous Speedup Models                 | 44 |

|   |     | 3.4.1  | Workload Distribution                            | 45 |

|   |     |        | 3.4.1.1 Equal-share workload distribution        | 46 |

|   |     |        | 3.4.1.2 Balanced workload distribution           | 47 |

|   |     | 3.4.2  | Heterogeneous Amdahl's Law                       | 47 |

|   |     | 3.4.3  | Workload Scaling                                 | 48 |

|   |     | 3.4.4  | Heterogeneous Gustafson's Model                  | 48 |

|   |     |        | 3.4.4.1 Purely parallel scaling mode             | 49 |

|   |     |        | 3.4.4.2 Classical scaling mode                   | 49 |

|   | 3.5 | Propo  | sed Heterogeneous Power Models                   | 50 |

|   |     | 3.5.1  | Power Modeling Basics                            | 51 |

|   |     | 3.5.2  | Power Distribution and Scaling Models            | 52 |

|   |     | 3.5.3  | Energy and Power-Normalized Performance          | 53 |

|   | 3.6 | Discu  | ssion and Conclusion                             | 54 |

| 4 | EXP | ERIME  | NTAL VALIDATION OF SPEEDUP AND POWER             |    |

|   | SCA | LING   | MODELS                                           | 57 |

|   | 4.1 | Introd | luction                                          | 57 |

|   | 4.2 | CPU-   | only Experimental Validations                    | 57 |

|   |     | 4.2.1  | Platform Description                             |    |

|   |     |        | Benchmark Description and Model Characterization | 58 |

|   |     |        | 4.2.2.1 Controlled parameters                    |    |

|   |     |        |                                                  |    |

|   |     |        | 4.2.2.2 Relative performances of cores 6    | 0       |

|---|-----|--------|---------------------------------------------|---------|

|   |     |        | 4.2.2.3 Core idle and active powers 6       | 1       |

|   |     | 4.2.3  | Amdahl's Workload Outcomes 6                | 2       |

|   |     | 4.2.4  | Gustafson's Workload Outcomes 6             | 3       |

|   |     | 4.2.5  | Balanced Execution 6                        | 4       |

|   | 4.3 | CPU-0  | GPU Experimental Validations 6              | 5       |

|   |     | 4.3.1  | Platform Description and Characterization 6 | 6       |

|   |     | 4.3.2  | Speedup Validation Outcomes 6               | 8       |

|   | 4.4 | Realis | tic Application Workloads                   | O'      |

|   |     | 4.4.1  | Model Characterization                      | 1       |

|   |     | 4.4.2  | Quality of Load Balancer                    | 2       |

|   | 4.5 | Discus | ssion and Conclusion                        | 4       |

|   |     |        |                                             |         |

| 5 |     |        | AND PARALLELIZATION MODELS USING            |         |

|   |     |        |                                             | 7       |

|   | 5.1 |        |                                             | 7       |

|   | 5.2 |        |                                             | 8       |

|   |     | 5.2.1  | -                                           | 8       |

|   |     | 5.2.2  |                                             | 9       |

|   | 5.3 |        | 1 1                                         | O       |

|   |     | 5.3.1  | O .                                         | O       |

|   |     | 5.3.2  | 1 1                                         | 2       |

|   |     | 5.3.3  |                                             | 4       |

|   |     | 5.3.4  |                                             | 4       |

|   |     | 5.3.5  |                                             | 4       |

|   |     | 5.3.6  | 11                                          | 6       |

|   | 5.4 | Result |                                             | 6       |

|   |     | 5.4.1  | ,                                           | 6       |

|   |     | 5.4.2  | 1 1                                         | 9       |

|   |     | 5.4.3  | ,                                           | 2       |

|   | 5.5 | Parall |                                             | 4       |

|   |     | 5.5.1  |                                             | 4       |

|   |     | 5.5.2  | Power Normalized Performance (PNP) and      |         |

|   |     |        |                                             | 9       |

|   | 5.6 | Concl  | usions and Discussions                      | 2       |

| 6 | CON | CLUST  | ONS AND FUTURE WORK 10                      | <u></u> |

| J | 6.1 |        | nary and Conclusion                         |         |

|   | 0.1 | Junin  | miy and Concident                           | 9       |

|     | 6.2  | Future Work            | <br>10 | 09         |

|-----|------|------------------------|--------|------------|

| 11  | ΤI   | hesis Appendices       | 11     | .1         |

| A   |      | NCHMARK APPLICATION    |        | 13         |

|     | A.1  | Synthetic Benchmark    | <br>13 | 13         |

| В   | DAT  | TA SET                 | 1:     | 17         |

|     | B.1  | Odroid XU <sub>3</sub> | <br>1: | 17         |

|     | B.2  | OpenCL                 | <br>1: | 18         |

|     | в.3  | PARSEC                 | <br>13 | 19         |

| C   | PAR  | RSEC RESULTS           | 12     | <b>2</b> 9 |

| 111 | Τŀ   | hesis Bibliography     | 13     | 5          |

| BI  | BLIO | OGRAPHY                | 1      | 37         |

# LIST OF FIGURES

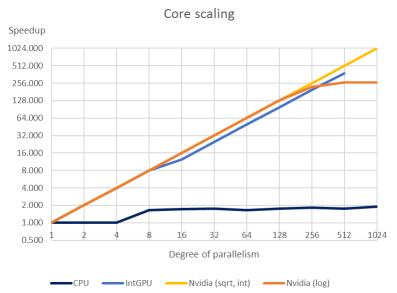

| Figure 1.1 | Micro/nanoelectronic scaling over time [2]                | 3  |

|------------|-----------------------------------------------------------|----|

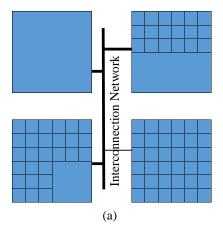

| Figure 2.1 | M/MCP architecture                                        | 13 |

| Figure 2.2 | Diversity of M/MCP                                        | 13 |

| Figure 2.3 | Distributed M/MCP                                         | 15 |

| Figure 2.4 | Architecture of a Central Processing Unit-Graphics        |    |

|            | Processing Unit (CPU – GPU) chip                          | 15 |

| Figure 2.5 | homogeneous speedup $(S(n))$ vs number of cores $(n)$ for |    |

|            | (a) Amdahl's law (b) Gustafson's model and (c) Sun-Ni's   |    |

|            | model                                                     | 20 |

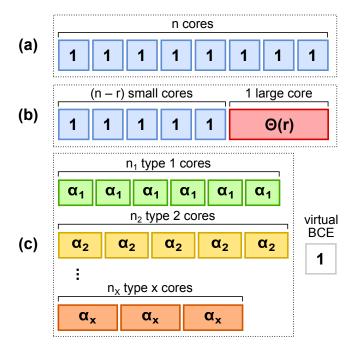

| Figure 2.6 | M/MCP diversity. (a) Symmetric Multi-Core                 |    |

|            | Processor (SMCP) with 16 one-Base Core                    |    |

|            | Equivalent (BCE) cores, (b) Asymmetric Multi-Core         |    |

|            | Processor (AMCP) with 4 four-BCE cores, and (c) AMCP      |    |

|            | with 1 four-BCE core and 12 one-BCE cores. These          |    |

|            | figures eliminate important structures such as memory     |    |

|            | interfaces, shared caches, and interconnects. They        |    |

|            | assume that area, not power, is a chip's limiting         |    |

|            | resource. [3]                                             | 22 |

| Figure 3.1 | The proposed extended structure of a heterogeneous        |    |

|            | system (c) compared to a homogeneous system (a) and       |    |

|            | the previous assumption [3] on heterogeneity (b). The     |    |

|            | numbers in the core boxes denote the equivalent number    |    |

|            | of Base Core Equivalents (BCEs)                           | 44 |

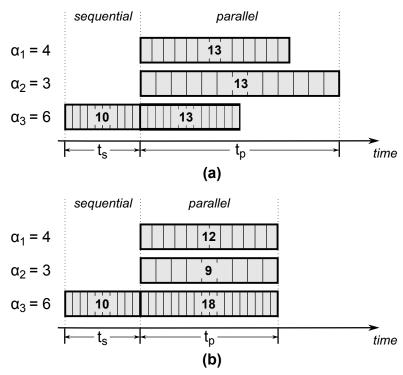

| Figure 3.2 | Workload distribution examples following                  |    |

|            | (a) equal-share model and (b) balanced model              | 46 |

| Figure 4.1 | Experimental big.LITTLE platform description              | 58 |

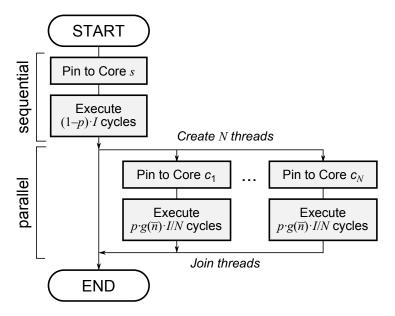

| Figure 4.2  | Synthetic application with controllable parallelization                |    |

|-------------|------------------------------------------------------------------------|----|

|             | factor and equal-share workload distribution. Parameter                |    |

|             | parallelization factor (p), unscaled workload size (I),                |    |

|             | parallel workload scaling factor $(g(\overline{n}))$ , total number of |    |

|             | heterogeneous cores (N), type of core executing                        |    |

|             | sequential workload (s) and set of core                                |    |

|             | allocations $(\bar{c})=(c_1,\ldots,c_N)$ are specified as the          |    |

|             | program arguments                                                      | 60 |

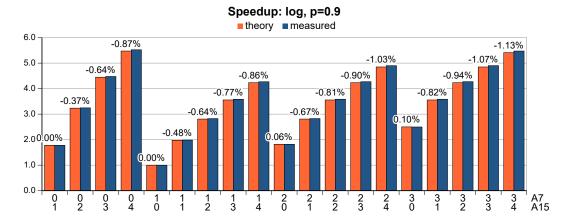

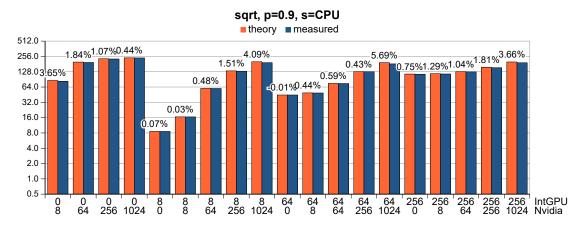

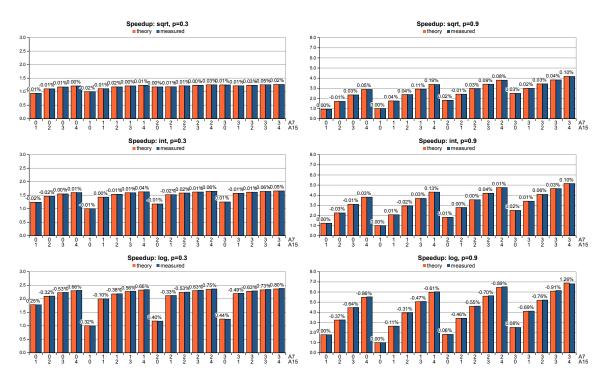

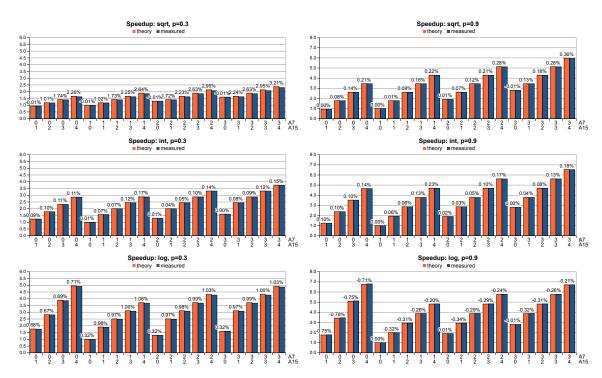

| Figure 4.3  | Speedup validation results for the heterogeneous                       |    |

|             | Amdahl's law showing percentage error of the                           |    |

|             | theoretical model in relation to the measured speedup                  | 62 |

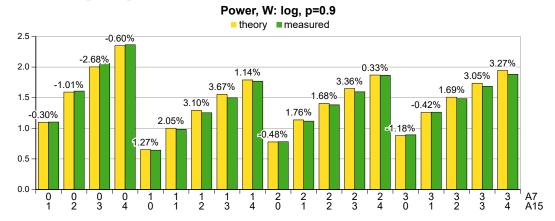

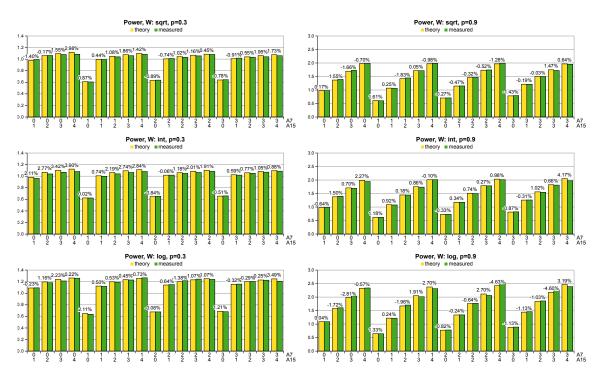

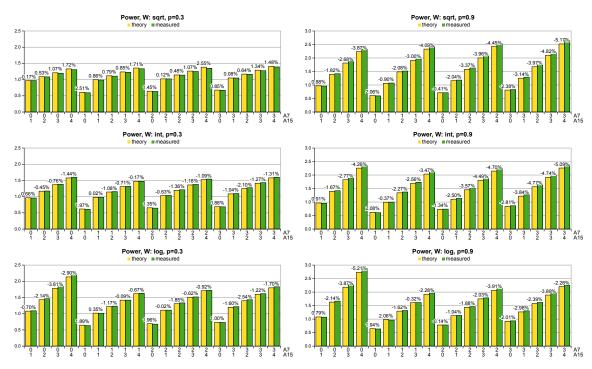

| Figure 4.4  | Total power dissipation results for the heterogeneous                  |    |

|             | Amdahl's law showing percentage error of the theoretical               |    |

|             | model in relation to the measured power                                | 62 |

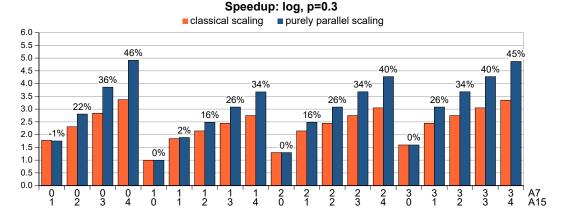

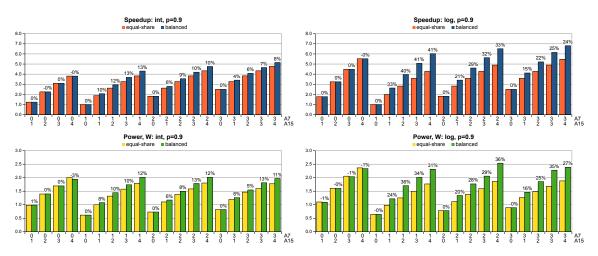

| Figure 4.5  | Gustafson's model outcomes showing the measured                        |    |

|             | speedup gain from using the purely parallel workload                   |    |

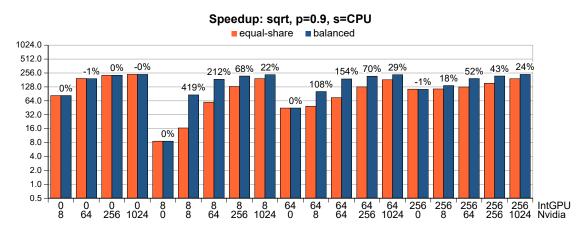

|             | scaling compared to the classical scaling                              | 64 |

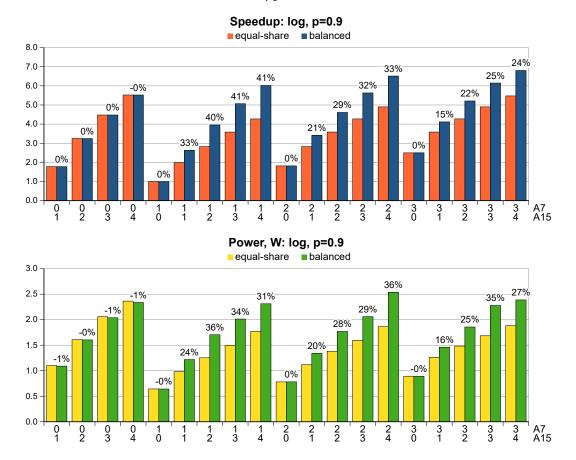

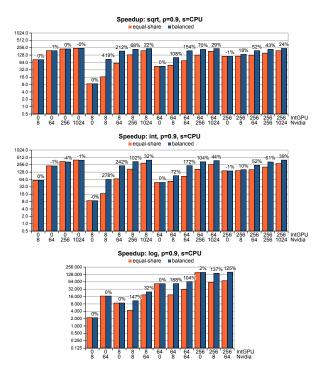

| Figure 4.6  | Comparison of the measured speedup, power, and                         |    |

|             | energy between equal-share and balanced execution                      | 65 |

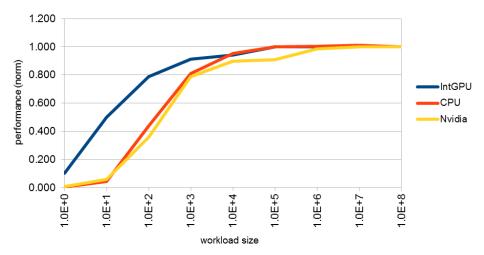

| Figure 4.7  | The effect of Open Computing Language (OpenCL)                         |    |

|             | overheads on performance, can be ignored for                           |    |

|             | sufficiently large workload sizes                                      | 67 |

| Figure 4.8  | Investigating the scalability potential for the requested p            |    |

|             | = 1                                                                    | 68 |

| Figure 4.9  | Speedup validation results for the heterogeneous                       |    |

|             | Amdahl's law in the OpenCL platform                                    | 69 |

| Figure 4.10 | Comparison of the measured speedups between equal-                     |    |

|             | share and balanced execution in the OpenCL platform                    | 69 |

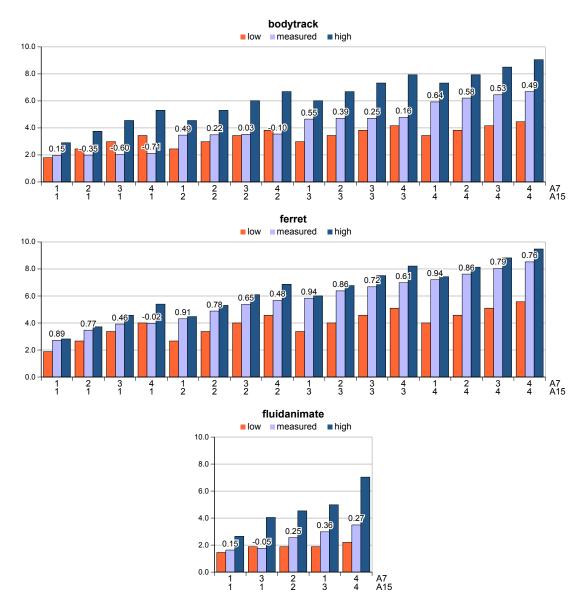

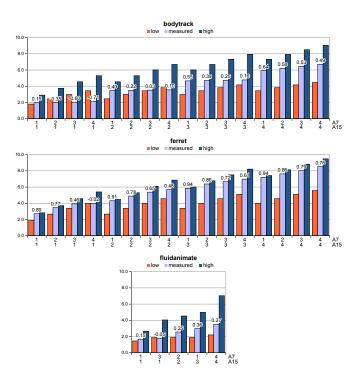

| Figure 4.11 | Princeton Application Respository for Shared-Memory                    |    |

|             | Computers (PARSEC) speedup range results from                          |    |

|             | heterogeneous system setup determining quality metric                  |    |

|             | of load balancimg algorithm (q). $\dots$                               | 73 |

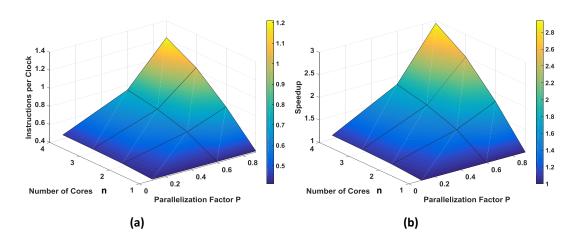

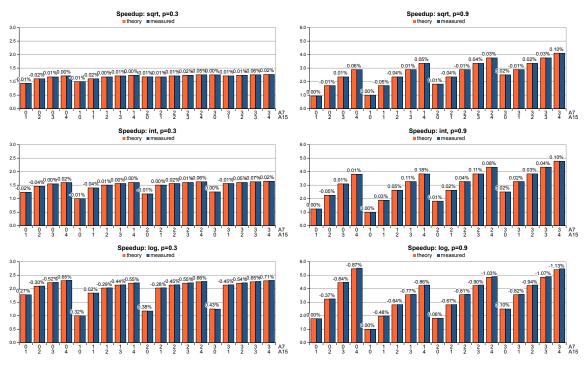

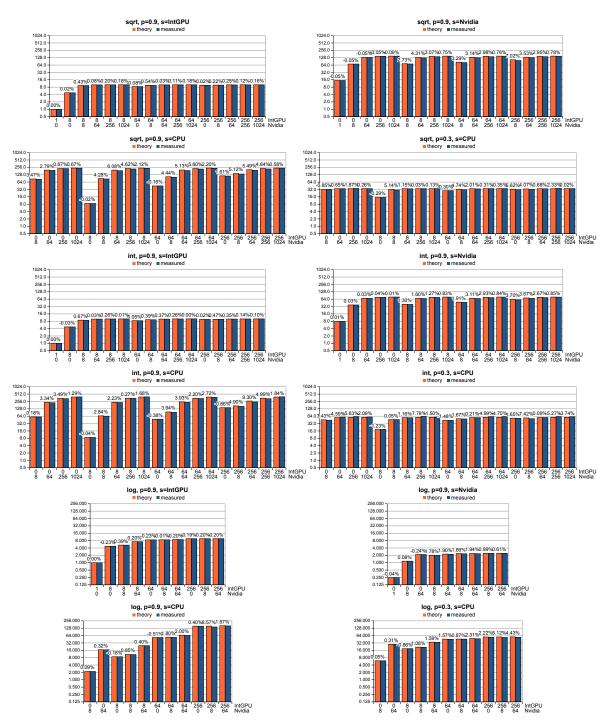

| Figure 5.1  | Synthetic benchmark using variable n and p for                         |    |

|             | Amdahl's model (a) Application instructions per clock.                 |    |

|             | (b) Performance counter based speedup                                  | 87 |

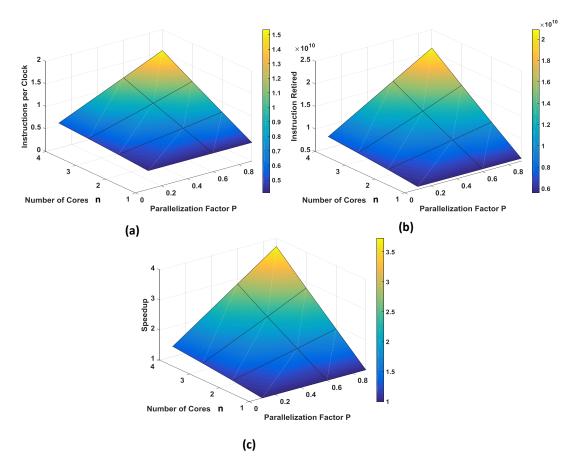

| Figure 5.2  | Synthetic benchmark using variable n and p for                |    |

|-------------|---------------------------------------------------------------|----|

|             | Gustafson's model (a) Application instructions per            |    |

|             | clock. (b) scaled workload size (I'). (c) Performance         |    |

|             | 1 1                                                           | 38 |

| Figure 5.3  | Performance counter based speedup for PARSEC                  |    |

|             |                                                               | )1 |

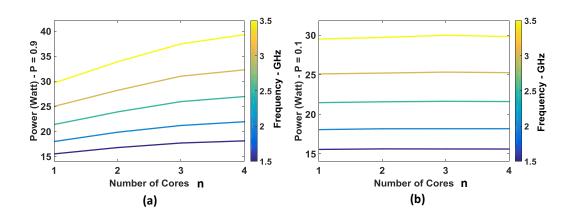

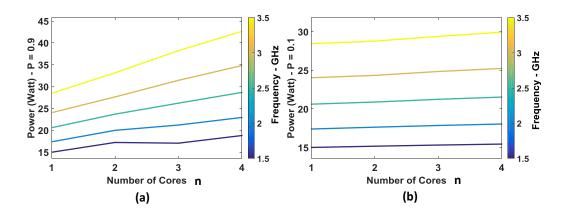

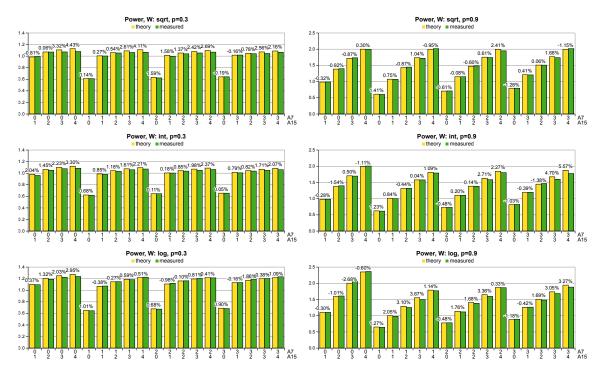

| Figure 5.4  | Power consumption for synthetic application of extended       |    |

|             | Amdahl's power model using: a) high $p = 0.9$ , b) low $p =$  |    |

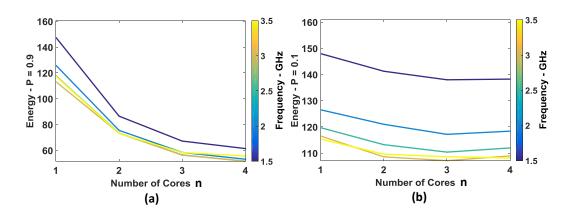

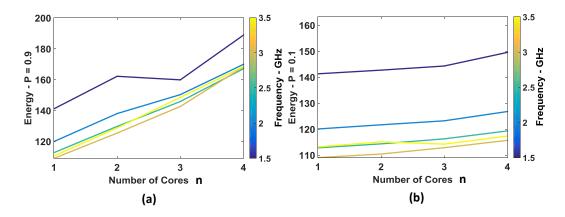

|             | -                                                             | 97 |

| Figure 5.5  | Power consumption for synthetic application of extended       |    |

|             | Gustafson's power model using: a) high $p = 0.9$ , b) low $p$ |    |

|             | = 0.1                                                         | 98 |

| Figure 5.6  | Energy consumption for synthetic application of               |    |

|             | extended Amdahl's energy model using: a) high $p = 0.9$ ,     |    |

|             | b) low p = 0.1                                                | 98 |

| Figure 5.7  | Energy consumption for synthetic application of               |    |

|             | extended Gustafson's energy model using: a) high $p =$        |    |

|             | o.9, b) low p = 0.1                                           | 99 |

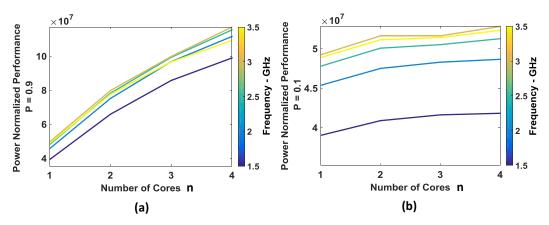

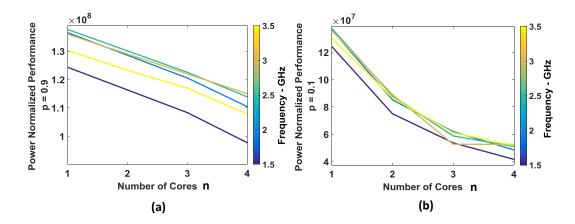

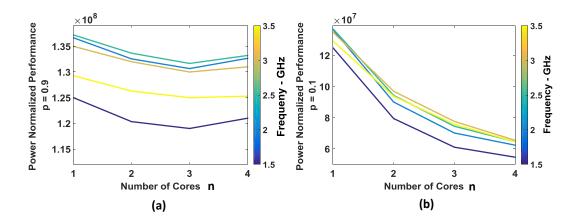

| Figure 5.8  | Power Normalized Performance (PNP) results in full-           |    |

|             | domain Dynamic Voltage Frequency Scaling (DVFS) for           |    |

|             | synthetic application of extended Amdahl's speedup            |    |

|             | model using: a) high $p = 0.9$ , b) low $p = 0.1$             | )9 |

| Figure 5.9  | PNP results in full-domain DVFS for synthetic application     |    |

| _           | of extended Gustafson's speedup model using: a) high p        |    |

|             | = 0.9, b) low p = 0.1                                         | C  |

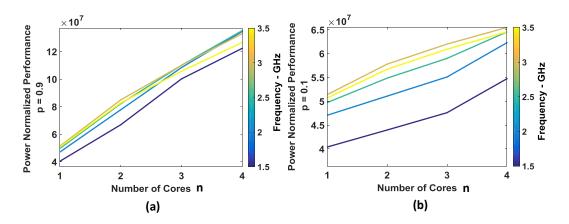

| Figure 5.10 | PNP results in per-core DVFS for synthetic application of     |    |

| 0 1         | extended Amdahl's speedup model using: a) high $p =$          |    |

|             | o.9, b) low p = 0.1                                           | C  |

| Figure 5.11 | PNP results in per-core DVFS for synthetic application of     |    |

| 0           | extended Gustafson's speedup model using: a) high $p =$       |    |

|             | o.9, b) low p = 0.1                                           | )C |

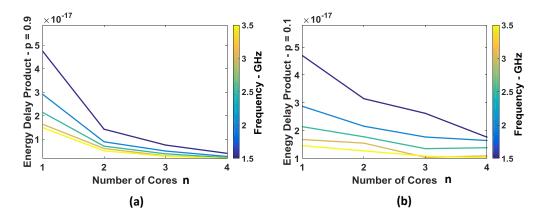

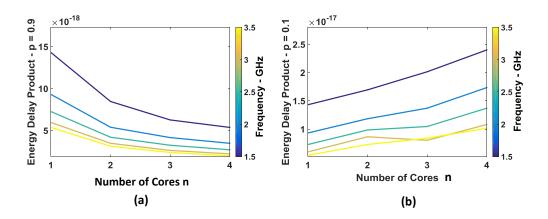

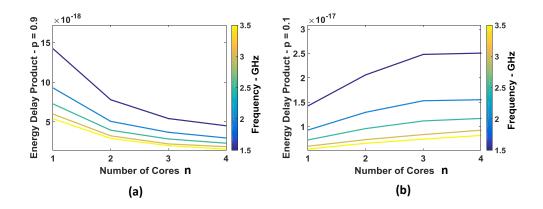

| Figure 5.12 | Energy-Delay Product (EDP) results in full-domain DVFS        |    |

| 0 9         | for synthetic application of extended Amdahl's speedup        |    |

|             | model using: a) high $p = 0.9$ , b) low $p = 0.1$             | )1 |

| Figure 5.13 | EDP results in full-domain DVFS for synthetic application     |    |

| 0 5 - 5     | of extended Gustafson's speedup model using: a) high p        |    |

|             | = 0.9, b) low p = 0.1                                         | )1 |

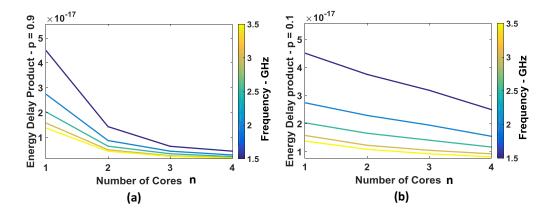

|             |                                                               |    |

| Figure 5.14 | EDP results in per-core DVFS for synthetic application of extended Amdahl's speedup model using: a) high $p =$                |

|-------------|-------------------------------------------------------------------------------------------------------------------------------|

|             | o.9, b) low $p = 0.1$                                                                                                         |

| Figure 5.15 | EDP results in per-core DVFS for synthetic application of extended Gustafson's speedup model using: a) high $p = \frac{1}{2}$ |

|             | o.9, b) low p = 0.1                                                                                                           |

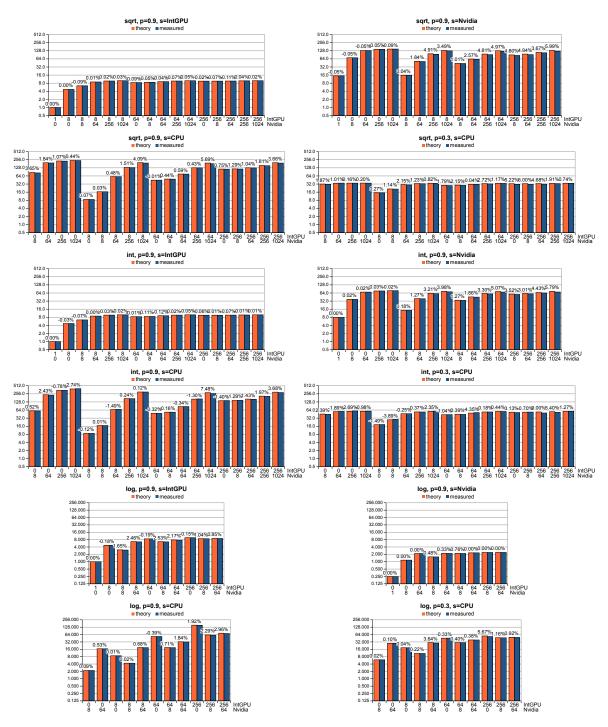

| Figure B.1  | Speedup validation results for the heterogeneous<br>Amdahl's law showing percentage error of the                              |

|             | theoretical model in relation to the measured speedup 119                                                                     |

| Figure B.2  | Total power dissipation results for the heterogeneous Amdahl's law showing percentage error of the theoretical                |

|             | model in relation to the measured speedup 120                                                                                 |

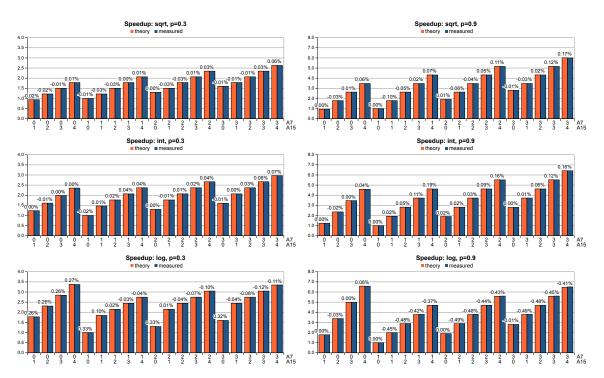

| Figure B.3  | Speedup validation results for the heterogeneous                                                                              |

|             | Amdahl's law with balanced workload showing                                                                                   |

|             | percentage error of the theoretical model in relation to                                                                      |

|             | the measured speedup                                                                                                          |

| Figure B.4  | Total power dissipation results for the heterogeneous                                                                         |

|             | Amdahl's law with balanced workload showing                                                                                   |

|             | percentage error of the theoretical model in relation to                                                                      |

|             | the measured speedup                                                                                                          |

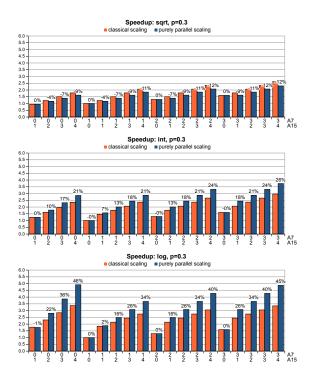

| Figure B.5  | Speedup validation results for the heterogeneous                                                                              |

|             | Gustafson's model with classical scaling showing                                                                              |

|             | percentage error of the theoretical model in relation to                                                                      |

|             | the measured speedup                                                                                                          |

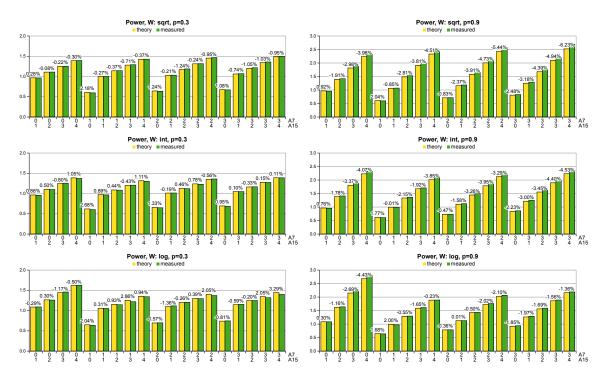

| Figure B.6  | Total power dissipation results for the heterogeneous                                                                         |

|             | Gustafson's model with classical scaling showing                                                                              |

|             | percentage error of the theoretical model in relation to                                                                      |

| E. D        | the measured speedup                                                                                                          |

| Figure B.7  | Speedup validation results for the heterogeneous                                                                              |

|             | Gustafson's model with purely parallel scaling showing                                                                        |

|             | percentage error of the theoretical model in relation to                                                                      |

| F. D.       | the measured speedup                                                                                                          |

| Figure B.8  | Total power dissipation results for the heterogeneous                                                                         |

|             | Gustafson's model with purely parallel scaling showing                                                                        |

|             | percentage error of the theoretical model in relation to                                                                      |

| Tr D        | the measured speedup                                                                                                          |

| Figure B.9  | Comparison of the measured speedup, power and energy                                                                          |

|             | between equal-share and balanced execution 123                                                                                |

| Figure B.10 | Gustafson's model outcomes showing the measured          |

|-------------|----------------------------------------------------------|

| O           | speedup gain from using the purely parallel workload     |

|             | scaling compared to the classical scaling 124            |

| Figure B.11 | OpenCL speedup validation results for the heterogeneous  |

|             | Amdahl's law showing percentage error of the theoretical |

|             | model in relation to the measured speedup 125            |

| Figure B.12 | OpenCL speedup validation results for the                |

| Ü           | heterogeneous Amdahl's law with balanced workload        |

|             | showing percentage error of the theoretical model in     |

|             | relation to the measured speedup                         |

| Figure B.13 | Comparison of the measured OpenCL speedup between        |

|             | equal-share and balanced execution                       |

| Figure B.14 | PARSEC speedup range results from heterogeneous          |

| ,           | system setup determining q – the quality of the system   |

|             | load balancer                                            |

# LIST OF TABLES

| Table 2.1 | Literature summary                                               |

|-----------|------------------------------------------------------------------|

| Table 3.1 | Summary of the existing speedup models and the                   |

|           | proposed model 37                                                |

| Table 4.1 | Characterization experiments: single core execution 61           |

| Table 4.2 | OpenCL device capabilities                                       |

| Table 4.3 | OpenCL characterization experiments                              |

| Table 4.4 | Characterization of PARSEC benchmark parallelizability           |

|           | from homogeneous system setup                                    |

| Table 5.1 | Experimental platforms used in this work                         |

| Table 5.2 | System software workloads over execution time for                |

|           | different PARSEC applications 89                                 |

| Table 5.3 | Cross-validation results for I using synthetic benchmark [4]. 90 |

| Table 5.4 | Cross-validation results for fixed time using synthetic          |

|           | benchmark                                                        |

| Table 5.5 | p calculations for synthetic benchmark using Amdahl's            |

|           | speedup model [4]                                                |

| Table 5.6 | p calculations for synthetic benchmark using Gustafson's         |

|           | speedup model                                                    |

| Table 5.7 | p calculations of PARSEC benchmarks                              |

| Table 5.8 | Voltage Frequency Scaling Readings                               |

| Table C.1 | Performance and power calculations of Bodytrack 129              |

| Table C.2 | Performance and power calculations of Blackscholes 130           |

| Table C.3 | Performance and power calculations of Facesim 130                |

| Table C.4 | Performance and power calculations of Fluidanimate 131           |

| Table C.5 | Performance and power calculations of Frequine 131               |

| Table C.6 | Performance and power calculations of Swaptions 132              |

| Table C.7 | Performance and power calculations of Streamcluster 132          |

| Table C.8 | Performance and power calculations of Canneal 133                |

| Table C.9 | Performance and power calculations of Dedup 133                  |

### LIST OF ACRONYMS

ALU Arithmetic Logic Unit

AMCP Asymmetric Multi-Core Processor

**BCE** Base Core Equivalent

**BCEs Base Core Equivalents**

CMOS Complementary Metal-Oxide-Semiconductor

CPU Central Processing Unit

CPU – GPU Central Processing Unit-Graphics Processing Unit

**CUDA Compute Unified Device Architecture**

**DMCP** Dynamic Multi-Core Processor

**DVFS Dynamic Voltage Frequency Scaling**

**EDP** Energy-Delay Product

**ENP Energy Normalized Performance**

**EPI** Energy per Instruction

FPGA Field-Programmable Gate Array

**GPU** Graphics Processing Unit

HeMCP Heterogeneous Multi-Core Processor

HoMCP Homogeneous Multi-Core Processor

**HPC** High Performance Computing

IPC Instructions per Clock

IPS Instructions per Second

ISA Instruction Set Architecture

ISSCC International Solid-State Circuits Conference

ITRS International Technology Roadmap for Semiconductors

M/MCP Multi/Many Core Processor

MIDs Mobile Internet Devices

MSR Model-Specific Register

MOSFET Metal Oxide Semiconductor Field Effect Transistor

NoC Networks-on-Chip

OpenMP Open Multi-Processing

OpenCL Open Computing Language

OS Operating System

PNP Power Normalized Performance

PARSEC Princeton Application Respository for Shared-Memory Computers

POSIX Portable Operating System Interface for Unix

RTM Run-Time Management

SoC System-on-Chip

SIMD Single Instruction, Multiple Data

SMCP Symmetric Multi-Core Processor

TSC Time Stamp Counter

# LIST OF SYMBOLS

- $\alpha$  performance factor for the core

- $\alpha_i$  performance factor for the core type i

- $\alpha_s$  performance factor of sequential execution

- $\bar{\alpha}$  vector of the core performance factors

- β power factor of core

- $\beta_i$  power factors of core type i

- $\beta_s$  power factor of sequential execution

- $\overline{\beta}$  vector of core power factors

- θ base core equivalent performance

- $\Theta(n)$  homogeneous system performance on number of cores

- $\Theta(r)$  relative performance of Hill-Marty assumption

- e number of clock cycle

- ΔI system software instructions

- a activity factor

- A<sub>0</sub> product of activity factor by capacitance for idle power consumption

- A<sub>n</sub> product of activity factor by capacitance for effective power

- C switch capacitance

- $\bar{c}$  set of core allocations

- $D_{w}(\overline{n})$  power distribution characteristic function

- $D_w(n)$  power distribution function for homogeneous system

- e effective energy

- E total energy consumption

- $E_0$  idle energy

- F clock frequency

- $g(\overline{n})$  parallel workload scaling factor

- g(n) workload/memory scaling

- $h(\overline{n})$  proportional workload scaling factor

- I unscaled workload size

- I' scaled workload size

- I<sub>Amd</sub> total number of instructions for Amdahl's model

- I<sub>Gus</sub> total number of instructions for Gustafson's model

- n number of cores

- $n_i$  number of cores of type i

- $\overline{n}$  vector of core numbers

- N total number of heterogeneous cores

- $N_{\alpha}$  performance-equivalent number of Base Core Equivalents

- $N_{\beta}$  power-equivalent number of Base Core Equivalents

- p parallelization factor

- p<sub>Amd</sub> Amdahl's parallelization factor

- p<sub>Gus</sub> Gustafson's parallelization factor

- q quality metric of load balancimg algorithm

- s type of core executing sequential workload

- $S(\overline{n})$  heterogeneous speedup

- S(n) homogeneous speedup

- $S_{low}(\overline{n})$  lower speedup limit

- $S_{high}(\overline{n})$  higher speedup limit

- $t(\overline{n})$  unscaled workload execution time

- $t'(\overline{n})$  scaled workload execution time

- t(1) workload execution time in a single core

- t(n) workload execution time in the number of cores

- t'(n) extended workload execution time

- $t_p'(\overline{n})$  parallel execution time

- $t'_s(\overline{n})$  sequential execution time

- $t_{p}^{\prime}\left( \mathfrak{n}\right) \ speedup-dependent parallel execution time$

- $t_{s}'(n)$  speedup-dependent sequential execution time

- V supply voltage

- $w_0$  idle power of a core

- w effective power of Base Core Equivalent

- $w_{\alpha}$  active power of a core

- $W_0$  total background power

- $W(\overline{n})$  total effective power

- W(n) total effective power of homogeneous system

- $W_{\text{total}}$  total power of the system

- $w_s$  sequential effective execution power

- $w_p$  parallel effective execution power

- $W_{Amd}$  Amdahl's total power consumption

- W<sub>Gus</sub> Gustafson's total power consumption

- $W_{l}$  leakage power

- x clusters (types) of homogeneous cores

# Part I Thesis Chapters

#### 1.1 MOTIVATION AND CHALLENGES

Micro/nanoelectronic scaling technology has facilitated significant performance improvements with reduced power consumption in microprocessor system design through increased operating frequency and smaller device geometries [5]. Furthermore, the number of transistors per unit area is also increasing substantially, which also conforms to Moore's [6] and Koomey's laws [7]. It is further stated that performance per watt is growing exponentially and the number of electronic components is doubling every 1.5 years [6].

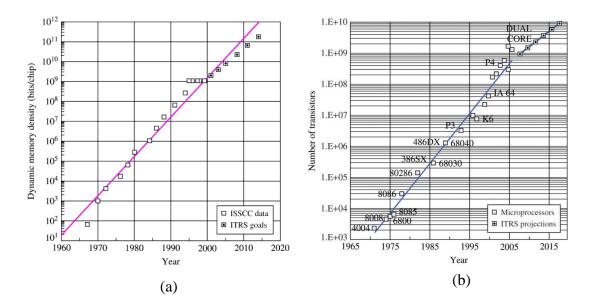

Figure 1.1: Micro/nanoelectronic scaling over time [2]

In order to predict the future of component scalability, some additional studies and research groups have proposed the future roadmaps, such as the International Technology Roadmap for Semiconductors (ITRS) [8] and the International Solid-State Circuits Conference (ISSCC) [9]. Figure 1.1 explains the goals and projections of the ITRS [8] and ISSCC [9] for the growth in

the number of microelectronics components over time for dynamic memory density in Figure 1.1(a) and the number of transistors in chips in Figure 1.1(b).

Over the years, significant research has been carried out to understand the trends of growth in performance in single and many interconnected cores. An example of these models is Pollack's Rule, which suggests that an increase in performance are approximately proportional to the square root of complexity [10]. Following this rule, a doubling of the number of components in a double processor will provide twice the performance in contrast to a single processor [5]. Therefore, several-core systems will deliver further improvements in throughput and latency for the same die area. Many studies have demonstrated the necessity of the evolution from single to Multi/Many Core Processor (M/MCP) to achieve performance improvements in the whole system alongside reducing in power consumption [5].

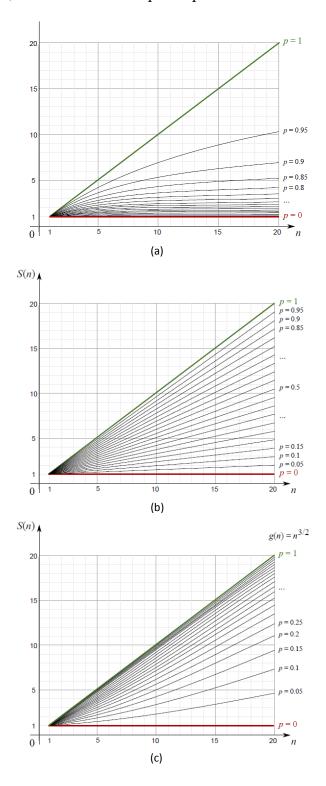

The calculation of performance is essential to the growth of M/MCP. One of the most appropriate methods to discover the suitable performance in M/MCP is speedup. Several recent studies have explained the ideas behind speedup calculations; however, the most familiar classical speedup models are considered by most of these studies. The first scalable and familiar model in relation to M/MCP is explained in Amdahl's law [11]. Amdahl assumed that the speedup model for a fixed workload can be calculated by comparing the performance of the workload executed in a single core with the performance of the same workload executed in the number of cores (n). The model shows the limitations in speedup with increasing n. In 1988, Gustafson introduced the principle of scalable computing in M/MCP pertaining to a fixed time model. Gustafson proposed a linear speedup model where increases in workload are proportional to increasing machine scalability, while execution time remains fixed [12]. In 1990, Sun and Ni suggested a new model which includes extended workload calculations by increasing the capability of memory. It is important to note that the executed workload and time should change based on the capability of the system, whereas the performance calculations appear to be super-linear within the cores increasing [13, 14].

On the other hand, power consumption management is a significant issue which should be considered in calculations of scalable systems and M/MCP. Several techniques have been designed to manage power consumption. For instance, Dynamic Voltage Frequency Scaling (DVFS), clock, and power gating techniques and fine grain power management. [15, 16, 17, 18] are some of the scaling techniques used to decrease power consumption.

Currently, most consumer devices and embedded systems make use of the computational performance and power of M/MCP. The number of cores is growing constantly, and hence speedup models remain very important. Amdahl's law and models derived from it do not require complex modeling and the simulation of individual inter-process communication. Instead, they operate according to average platform and application characteristics and provide simple analytical solutions that project the system's capabilities in a clear and understandable way. However, it is crucial to keep the models up to date to make sure that they remain relevant and correctly represent novel aspects of platform design.

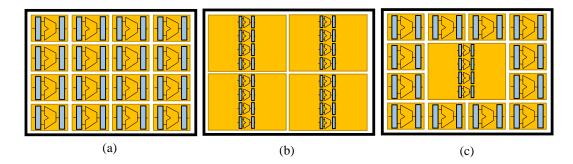

The classical speedup models of Amdahl, Gustafson, and Sun-Ni have been investigated in several studies to gain an understanding of M/MCP modeling. Hill and Marty extended Amdahl's model to simple homogeneous and heterogeneous configurations [3]. Other studies [19, 20] have extended all three major speedup models following the principle of the Hill-Marty models. Meanwhile, researchers in [21, 22] have extended Hill-Marty's models to consider the problem of energy efficiency in simple homogeneous and heterogeneous configurations.

The concept of heterogeneity has emerged within the study of the increase in system complexity and integration. Basically, this phenomenon appears in specialized accelerator forms such as Graphics Processing Unit (GPU). Recently, several types of Central Processing Unit (CPU) cores integrated into a single processor have also been made popular, such as the ARM big.LITTLE processor which has found wide use in mobile devices [23]. Heterogeneous systems have added more research and engineering challenges. From the perspective of the trade-offs between performance and power, the goal is to achieve better performance with the available power. From the perspective of load balancing and scheduling, the goal is to improve the core utilization to more efficiently use the performance available.

The Hill-Marty models and related studies have considered simple heterogeneous configurations consisting of a single big core and many smaller ones of exactly the same type [3, 19, 20], which relates to the Central Processing Unit-Graphics Processing Unit (CPU – GPU) type of heterogeneity. In addition, the problem of energy efficiency has been addressed in [21] for simple homogeneous and heterogeneous Hill-Marty models.

Parallel programming and its effects on power/energy management techniques are one of the vital issues in M/MCP. It may be facing some obstacles within the developments in hardware and software complexity [24].

Parallel programming is represented in many recent studies by workload parallelism in a different level of software design [25, 26, 26]. The classical and related speedup models [11, 12, 13, 14] consider workload parallelism by a fixed controlled parameter called parallelization factor (p). On the other hand, the parallelization factor has also been modeled based on the average of a program's parallelism and its variance in parallelism [27]. In addition, the implications of the parallelization factor modeling according to Amdahl's law in M/MCP has been considered [28] describing the level of parallelism achieved in different parts of the calculation. The effects of p on calculations for performance, power and energy metrics has described by [21] for a simple different architecture of M/MCP. This leads to focus more on the study of parallelization in Run-Time Management (RTM)[29, 30].

#### 1.2 AIM AND OBJECTIVES

This thesis describes research which seeks to extend existing classical speedup models in the context of contemporary M/MCP architectures, which are not covered by existing models. In addition, it includes power and energy models in the same context. The investigations extend to making these models more practically applicable for such goals as the RTM optimization of M/MCP systems. Experimental investigations using real off the shelf systems support the research at all points. The objectives of this thesis can be summarized as follows:

- 1. This thesis seeks to extend the classical theoretical M/MCP speedup models to cover modern system homogeneity and heterogeneity. The models can capture the interplay between energy and performance. Furthermore, these models are expected to be used for analyzing workload balancing methods.

- 2. This thesis sets out to propose a novel method to model p based on the extended speedup models. It should explain the effect of different application parallelizability on energy efficient computation for M/MCP.

- 3. This thesis seeks to validate all models by extensive experiments on different homogeneous and heterogeneous M/MCP by using designed synthetic and real Princeton Application Respository for Shared-Memory Computers (PARSEC) benchmarks.

4. This thesis seeks to establish M/MCP power , energy, and other efficiency models considering full-domain DVFS and per-core DVFS.

#### 1.3 THESIS ORGANIZATION AND KEY FINDINGS

This thesis is organized into six chapter. The major contributions of this thesis are described in 2 parts. The extended speedup, power models and the validations experiments of M/MCP are covered in Chapter 3 and Chapter 4. The p modeling, full-domain DVFS and per-core DVFS power modeling with all their experimental work are covered in Chapter 5. The chapters are summarized as follows:

*Chapter* 1 "*Introduction*". Introduces the motivations and challenges, aim and objectives, and the layout of the thesis.

Chapter 2 "Background and Literature Review". Provides a background literature survey establishing the environment and baseline of this research. The survey takes an in-depth look at the trend of integration of digital electronics, the development and significance of parallelization in M/MCP systems, and the modeling of speedup, power and energy in parallel processing systems. The chapter summarizes existing related work to illustrate the gaps this research sets out to fill and gaps for potential future work to fill.

Chapter 3 "Speedup and Power Scaling Models". Extends the assumption of system core heterogeneity in order to cover modern configurations such as big.LITTLE. The assumption establishes by extending the classical speedup models (Amdahl, Gustafson, and Sun-Ni) [11, 12, 13] in order to cover modern system heterogeneity. Furthermore, It extend the speedup models to estimate power and energy normalized speedup metrics. It incorporates the representations of the power and energy optimization effects techniques such as DVFS in the extended power models. In addition, it incorporates the calculations of workload balancing methods within extended performance and power modeling.

Chapter 4 "Experimental Validation of Speedup and Power Scaling Models". Validates the extended models from Chapter 3 on real heterogeneous

platforms including big.LITTLE and CPU-GPU through extensive experimentation. Moreover, this chapter uses these models to evaluate the efficiency of Linux scheduler's load balancing while running realistic workloads in a heterogeneous system.

Chapter 5 "Speedup and Parallelization Models Using Performance Counters". Presents a new method of p modeling from the extended speedup models. Furthermore, extensive experiments and analysis of synthetic and real PARSEC benchmarks have been applied. In addition, it presents novel full-domain DVFS and per-core DVFS power models for M/MCP.

*Chapter* 6 "*Conclusions and Future Work*". Summarizes the work and contributions of this thesis and identifies promising directions for future work.

#### 2.1 INTRODUCTION

There is a growing body of literature that recognizes the importance of micro/nano electronic in computer system development. The principles of electronic scaling permit to double the electronic components in the same die area every two years [6, 7]. Furthermore, the trend toward processors fabrication from single core to Multi/Many Core Processor (M/MCP) became necessary to improving performance and produce energy-efficient processors [5]. In general, M/MCP may be configured into Homogeneous Multi-Core Processor (HoMCP), where all the cores have a similar architecture such as Intel core i7-4820k and Intel Xeon Phi 7120X, or Heterogeneous Multi-Core Processor (HeMCP), where the cores have different architectures such as ARM big.LITTLE [31, 32, 3]. The HeMCP may incorporate diverse architectures of processing units such as, Central Processing Unit (CPU)s, Graphics Processing Unit (GPU) and embedded Field-Programmable Gate Array (FPGA) [33, 34].

Along the exploitation of micro/nano electronics component scaling to produce high performance and energy efficient M/MCP, additional techniques have been developed for dealing with same issues. For instance, Dynamic Voltage Frequency Scaling (DVFS) is a technique has developed to manage power consumption within processor clusters or individual cores [35, 36], the CPU affinity allows a task to core mapping, which may be used to reduce energy consumption. Other techniques targeting the same concerns include the energy efficient load balancing, task migration, and scheduling have invented for the same issues [37, 38, 39, 40].

This chapter reviews the literature on M/MCP, particularly those related to speedup models such as Amdahl [11], Gustafson [12] and Sun-Ni [13, 14]. It studies the background of the speedup models. Extended speedup models for M/MCP for improving performance and energy will also be discussed. The survey will also deal with theoretical models and practical validation methods found in the literature. In addition, it discusses the overheads that can affect performance and power consumption, explain the parallelization calculation,

and consider dark silicon calculation in extended speedup models. Finally, it summarises the discussed studies by the Table 2.1. The *contributions* of this chapter can be addressed as follows:

- 1. Provides basic concepts and theory of micro/nano electronic scalability, the trend from single to M/MCP, M/MCP architecture, the methods of performance improvements and power/energy consumption reduction in M/MCP (Section 2.2 to 2.5).

- Gives a brief survey including the concepts of classical speedup models Amdahl, Gustafson, and Sun-Ni and related speedup models such as, (Downey), the extended speedup models in M/MCP such as Hill-Marty (Section 2.6).

- 3. Provides an extensive survey of the overhead calculations in speedup models, the parallelization factor, the useful utilization of speedup models in networking, Run-Time Management (RTM), dark silicon, and power/energy normalized extended models (Section 2.6).

- 4. Summarizes all literature in this chapter in Table 2.1 to clarify the contributions of each study.

### 2.2 MICRO/NANO ELECTRONIC TECHNOLOGY SCALING

The evolution of electronics components has been continuing since the transistor was invented. Technology scaling, traditionally a good method of improving energy efficiency, has been facing challenges [41]. Dennard presented the Metal Oxide Semiconductor Field Effect Transistor (MOSFET) scaling law. The study considers the design, fabrication, and characterization of very small MOSFET switching devices appropriate for digital integrated circuits [42]. Consequently, The Dennard law states that approximately, if transistors get smaller their power density stays constant. Thus, the power calculations remain in proportion to the die area. Dennard scaling relates to Moore's Law [6] which explains that a reduction in the transistor's size leading to more transistors per chip at the same cost. Furthermore, Moore's law states that the performance per watt is growing exponentially at the same rate. This claim is related to Koomey's law [7] which elucidates that electrical efficiency performance has double roughly every 1.5 years. This leads to the efficiency improvements that enables many devices creations, such as mobile smartphone and wireless sensors.

Recently, Dennard scaling starts facing challenges. The study in [43] explains the collapse of Dennard scaling even though Moore's law continued. The essential reason is that at a small size, current leakage presents greater challenges related to power increases and a threat of thermal dissipation. Thus, the energy cost should increase. Based on these challenges, numerous researchers and architects have switched to focusing on developing microprocessors fabrication to M/MCP scaling [5].

The Pollack rule simplifies the explanation of the scaling trends [10]. It demonstrates the changes with each technology generation, frequency increases by 50%, transistor density doubles, and the voltage is lowered. Moreover, the study explains the improvement in manufacturing technology that allowed to increase die size without cost increases. Generally, the die size still limited by power, because of the increase in power dissipation which leads to several new challenges.

In the same field of Complementary Metal-Oxide-Semiconductor (CMOS) scalability, the study in [44] explains the next generations of CMOS scaling by using different data of Intel microprocessors. However, the analysis correspondingly applicable to other types of logic designs that meet the goals forecast by scaling theory introduced in this study [44]. The main consequences of scaling theory analyzed microprocessor performance by increasing the operating frequency and reducing gate delay, double the transistor density, and reduce power consumption.

The scaling aims to find the solutions for all challenges and predict the future of the next generation of technology. For instance, the study in [45] describes the possibility of exascale performance via voltage scaling for logic and memory, managing hierarchical interconnects concurrency and system level resilience. Generally, International Technology Roadmap for Semiconductors (ITRS) provides a set of up-to-date reference documents defining the requirements of the semiconductor technology advancements which takes into consideration the past, present and future related to both industry and academic fields [8].

# 2.3 FROM SINGLE-CORE TO MULTI/MANY-CORE (M/MCP)

The continuity of microelectronics scaling gives a chance to integrate billions of transistors in a single chip, and this has been expected to double every 18 months [6, 7].

The demand for increased performance in the field of a computer is continuing with every new improvement in processors, which leads to a higher level of requirements from users and businesses. More recently, the performance progress no longer relates to speed improvement solely, it does include smaller portable devices with higher efficiency, long battery life and better price per performance for one watt and lowest cooling costs [46, 23].

Formerly, performance improvements of the processors were achieved by increasing microelectronics technology scaling. Increasing clock speeds and power dissipation. Recently, the clock speeds have stagnated, and the power dissipation remained flat [47]. Thus, the principle of M/MCP has established as one of the new methods to improve processors performance. To explain this principle clearly, consider a logic block with an operating voltage of 1 unit, a frequency of 1, a throughput of 1, and a power of 1. If the designer reduced the voltage to 0.7, then the frequency must also reduce to 0.7 by considering DVFS technique. Thus, the throughput reduces to 0.7, and the power reduces to 0.35. The power can be calculated by 2.1 [48] with a hypothesis that constant C equal to 1, V is voltage, F is operating frequency and P<sub>Dyn</sub> is the dynamic power.

$$P_{Dyn} = C \cdot V^2 \cdot F. \tag{2.1}$$

If the logic block is then replicated and two blocks operate in parallel. The total power for the two blocks is 0.7, and the throughput is 1.4. This illustrates how parallel processing can increase performance while cutting power consumption.

Continuing the process of doubling the logic in a single processor core is not the unique method to improve processor performance within the same power envelope. This leads to using additional techniques, such as M/MCP and Multi-thread technology. Pollack assumed that a single thread processor would provide a diminishing return in performance versus power [10].

On the other hand, M/MCP has several benefits related to power consumption reduction [5] such as:

- 1. The cores can be individually turned on or off, thus saving power when a core is not needed.

- 2. Each processor core may have its own supply voltage and frequency, providing flexibility.

- 3. Easier distribute heat across the die with core work matching.

- 4. It can potentially produce lower die temperatures, improving reliability and leakage.

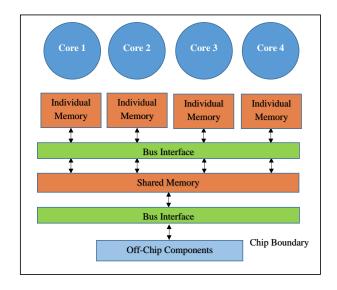

Figure 2.1 demonstrates the simple architecture of M/MCP.

Figure 2.1: M/MCP architecture.

### 2.4 M/MCP ARCHITECTURE

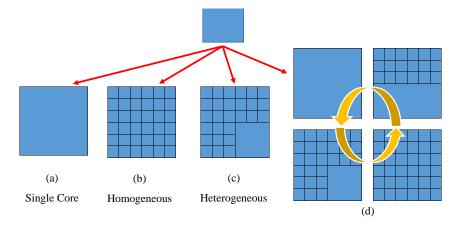

The continued increase in the number of microelectronic components allowed the development of M/MCP in the number of architectures. In general, it has been proposed to classify the M/MCP architectures into homogeneous, heterogeneous and dynamic as shown in Figure 2.2 [32, 3, 49].

Figure 2.2: Diversity of M/MCP.

### 2.4.1 Homogeneous M/MCP

HoMCP integrates M/MCP that have the same architecture of Symmetric Multi-Core Processor (SMCP) as shown in Figure 2.2 (a) [31, 32, 3]. In this type all the cores have identical performance and Instruction Set Architecture (ISA) [50, 51]. HoMCP has several benefits such as the flexibility to run different processes

HoMCP has several benefits such as the flexibility to run different processes simultaneously. They may also execute independent threads spawned from a single process to improve the performance of a single application.

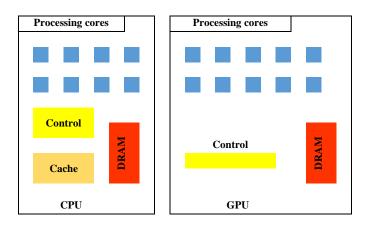

One of the specific types of HoMCP is GPU which are designed as special purpose processors for visual processing [52]. Modern GPUs may incorporate hundreds of cores to achieve parallel processing by handling thousands of threads simultaneously [53]. Generally, GPU is similar to CPU. However, it includes many smaller cores in comparison with multi bigger cores in CPU and has some differences such as CPU may be designed for speedup including (latency/throughput) improvements while GPU tend to be designed generally to improve throughput [54].

# 2.4.2 Heterogeneous M/MCP

HeMCP incorporates the large number of different computational units that may have different architecture. These include full-blown latency oriented cores for sequential processing, massively parallel Single Instruction, Multiple Data (SIMD) accelerators such as GPU, embedded FPGA and media accelerators [33, 34].

The Asymmetric Multi-Core Processor (AMCP) is a special case of heterogeneity when the processor includes two types of different cores) as shown in Figure 2.2 (b) [31, 32, 3]. In this type, not all the cores have the same performance and may have a single ISA [50, 55] or more than one ISA [56].

The HeMCP suffer from challenges brought by the flexibility to run different processes simultaneously. However, one advantage of heterogeneity is the high ability to manage performance/power trade-off to improve system performance and reduce power consumption. For instance, the big.LITTLE technology from ARM is HeMCP incorporating a cluster of 'big' cores for high performance and a cluster of 'LITTLE' cores for low power consumption. Further, some studies interested to study the software model design to manipulate the executed workload in HeMCP [23, 57].

Distributed Multi-Core Chips

Figure 2.3: Distributed M/MCP.

M/MCP architectures may feature in single chips or form distributed structures with multiple cores connected through communications facilities such as networks [58]. Figure 2.3 shows a simple architecture of distributed M/MCP.

HeMCP could include CPUs or Central Processing Unit-Graphics Processing Unit (CPU – GPU) in single chip as shown in Figure 2.4. The CPU – GPU integration in single chip offer performance imrovements [59, 60]. Further advantages include reduced communication overheads and costs, specially designed shared memory for avoiding explicit data copying [61]. They may also deliver more power and energy efficient computations [62, 59, 60].

Figure 2.4: Architecture of a CPU – GPU chip.

Recently, it has been claimed in the literature that optimization targeting certain applications have resulted in performance speedup from 25x to 100x or more utilizing GPU instead of CPU [63]. The main reason for this comes

from the differences in the architecture of each unit. CPU and GPU are designed in order to execute different types of applications [64, 65]. These differences cause CPU achieve better performance on latency-sensitive applications which need to respond rapidly to specific events and partially parallel applications [66, 64, 65]. On the other hand, GPU achieves better performance with latency-tolerant applications, and the processor utilization may be high due to multithreading [67, 68], highly parallel applications and independent applications [63]. Thus, the overall performance on CPU and GPU depends on the application characteristics. Moreover, other works have focused on heterogeneous architecture to combine unconventional cores such as custom logic or FPGA in the traditional M/MCP to achieve superior energy efficiency and performance improvements [59, 65]. This new paradigm considers the relationships between a conventional processor and a various set of unconventional cores. It forecasts future architecture from scaling developments predicted by ITRS [8].

# 2.4.3 Dynamic M/MCP

The Dynamic Multi-Core Processor (DMCP) has the ability to configure cores dynamically to adjust their computational resources through execution. Thus, it can provide superior system performance and lowest power consumption. It tackles the problem of performance/power trade-off which faces M/MCP architecture [32]. Figure 2.2(d) shows the simple idea of DMCP architecture, it can dynamically configure the number and the size of cores. For instance, if the executing program is easy to parallelize, the system may be configured into an increasing the number of cores. Whereas, it can combine several cores into one large one to improve the M/MCP performance for the sequential portion of a program. The overall aim of this type of dynamic configuration is to improve system performance.

### 2.5 THE METHODS OF ENERGY EFFICIENCY

In parallel with the development from single to M/MCP, methods have been developed to improve these issues. This section provides an overview of some important techniques which relate to this study.

# 2.5.1 Dynamic Voltage Frequency Scaling (DVFS)

DVFS is a technique designed to manage power and energy consumption in M/MCP [35]. Essentially, a controller can scale the voltage and frequency up and down in order to save the power. This technique can be found in a wide range of commercial M/MCP from embedded systems and mobile devices to servers [16]. [36, 69, 5] claim that the modern M/MCP have supported per-core DVFS, for instance, Intel and ARM's big.LITTLE. [5] suggests fine grain power management design, particularly with the power management for idle cores. The study considers two frequency operations for each Microprocessor core, with maximum frequency for fast processing and 1/2 of maximum frequency for idle cores. When a core operates at f/2, it uses lower voltage, subsequently consuming only a few of the maximum dynamic power. Furthermore, when there is support for DVFS for each core individually, each have specific performance and power consumption calculations [17, 18, 70]. It is possible to control technique by use dynamic sleep transistor and body biasing in conjunction with clock gating in CMOS technology to reduce power for idle cores [15]. Certain systems even provide capability scale voltage and frequency up-and-down the to independently [36]. Recently, M/MCP systems extended mechanisms to control cores and uncore components which include the components out of cores but connected to the core closely, such as Arithmetic Logic Unit (ALU), L1 and L2 cache [71, 72, 73, 74].

### 2.5.2 Thread to Core Affinity Managements

Modern processors lose a significant amount of time and energy when moving data. With the increase of core numbers, the importance of energy expenditure will increase with time. Thread-to-core affinity may also be used as a technique to enhance performance and/or reduce power.

CPU affinity or pinning is a technique that can enable the binding and unbind of tasks (thread or process) to specific cores in M/MCP. As a result, the tasks execute on the particular core or cores rather than any random core [75]. Generally, there are two types of CPU affinity, software, and hardware. The software affinity is used by an Operating System (OS) or specific application's scheduler to keep tasks on a CPU. Hardware itself may also provide affinity capabilities which makes particular threads execute on specific hardware.

The affinity technique has several trends to utilize the tasks in an efficient method. One area where affinity may help improve energy efficiency is in cache memory use. If shared cache between different cores needs to be used, all cores involved must validate the data, which is a costly procedure. Bouncing the same thread between different cores can also cause increased cache misses and increasing demands on cache validation [76].

Further, the performance of multi-thread applications can be improved when they are accessing the same data. It is better to bind them to the same CPU or core in M/MCP. Thus, the threads do not contend over data and increase cache misses [76]. Besides performance, thread-to-core affinity can also improve the performance to power consumption ratio. For instance, High Performance Computing (HPC) employ different thread to core affinity strategies to maximize the performance-power ratio. [75] demonstrates these improvements through extensive experimenting with HPC benchmarks.

The management of real-time and time-sensitive applications can also be improved based on this technique. Usually, the processors spend a significant amount of time, power and energy to move data. The system processes can be bound to a subset of cores in M/MCP, while other applications can be bound to the remaining cores [76]. Moreover, the core affinity relates to scheduling of real-time tasks on M/MCP. Thus, the unscheduled tasks can be pinned to a single core while the scheduled tasks can be pinned to multiple cores [77]. Furthermore, the impact of threads and data mapping mechanism on the communication traffic of Networks-on-Chip (NoC) is an important issue in relation to execution time in M/MCP. Following a mechanism to approach the lowest communication traffic through threads affinity with data results in significant communication traffic reduction and energy saving [78].

Usually, each application has a parallelization ratio, splitting sequential and parallel sections to schedule the parallel code to run on multiple cores can improve performance and decrease power consumption [79].

2.5.3 Energy Efficient Load Balancing, Task Migration and Task Scheduling Over M/MCP

Workload task manipulation is a significant and necessary consideration when aiming to improve M/MCP and embedded system performance and energy-efficient computations trough resources optimization, maximize throughput

and minimize response time. The techniques of task manipulation include load balancing, task migration and task scheduling [37, 38, 39, 40].

Load balancing is a technique used to improve the distribution of workload across multiple cores [37, 38, 39]. Diverse types of load balancing algorithms may be employed to improve performance and reduce energy consumption, particularly during task migration [39]. The algorithms should consider the task behavior and M/MCP architecture to achieve system optimization.

Task migration is the transfer technique of partially executed tasks from a core or cluster of cores to another core or cluster of cores in M/MCP [37, 38, 40, 39]. Task migration may be used to migrate a task from heavily loaded cores to lightly loaded or idle cores in M/MCP particularly HeMCP to balance the load across all cores. Thus, the average response time will be reduced to improve performance and decrease energy consumption [37, 40].

Task scheduling is the technique used to assign the start and end times to a set of tasks [80, 40]. The main challenges in real-time systems are how to satisfy better performance and minimize energy consumption [81], particularly in embedded real-time system and mobile devices. Task scheduling can be implemented by task scheduler software or OS process schedulers [80].

#### 2.6 SPEEDUP MODELS

Speedup is a number comparing the performance of using multiple computation units (cores) to solve a particular problem to the performance of solving the same problem with a single unit (core). One of the most important speedup models was presented in 1967 by Amdahl [11]. Amdahl's law pertains to fixed workloads. It compares the latency/performance of a fixed workload executed on a single core with the performance of the same workload executed in a number of cores (n).