# Self-Diagnosis Implantable Optrode for Optogenetic Stimulation

#### **Hubin Zhao**

A thesis submitted in partial fulfilment for the degree of Doctor of Philosophy

in the

School of Electrical and Electronic Engineering Faulty of Science, Agriculture and Engineering

January 2017

### Acknowledgements

First of all, I would like to express my deepest gratitude to my supervisor, Dr Patrick Degenaar. He has provided valuable opportunities and resources for me to explore the exciting bio-electronic technology from scratch. During these four years, he has given me very patient supervision, and has helped me to build a solid first step for my academic career. His sharp insight and helpful advices always benefits me a lot, and he always gives me all-out support and trust when I meet any difficulty and challenge. It is my honour to be your student during these years. I would also like to thank his wife, Dr Ying Hong, for proofreading my master thesis prior to the start of my PhD and her hospitalities for laboratory parties. I deeply appreciate the warm and help that Patrick and Ying have given to me since I arrived at UK.

I would like to give sincere thanks to my co-supervisor, Dr Danil Sokolov. Danil has given me numerous suggestions for my research and career, and he has consistently given me support and encouragement during my PhD. He continuously supplies positive energy for me when I lose confidence and even do not believe myself. And I am also grateful to his help for reviewing my research papers and thesis draft. It is my great luck to pursue my PhD under your supervision.

I wish to express my special thanks to Prof Alex Yakovlev. It is my great pleasure to be the chair of IEEE Newcastle University Student Branch in 2014-2016 under his mentoring. Besides, He has provided me very helpful advices and important support for both research and career development. In addition, I thank him and his wife for hosting warm Christmas parties for the group. I also thank Alex for his acceptance of my examiner invitation. It is my great honour to conduct my viva under your examination.

I also wish to give thanks to Prof Wouter Serdijn at Delft University of Technology. I met him at BioCAS 2015, and he gave me valuable feedback and encouragement for my work. He is a well-known and highly respectable scholar in bio-electronics area, and I do appreciate that he has accepted my invitation for being my external examiner. In addition, I also thank Vasiliki for her helpful feedback for my work and her very useful recommendation for the choice of my external examiner.

I am grateful to Prof Wai-Chi Fang (National Chiao Tung University), Prof Jie Chen (University of Alberta, Canada), and Prof Liudi Jiang (University of Southampton, UK), for their meaningful advices, help and encouragement. Your support have strengthen my faith for academics, and it is my great luck to know you.

A special thank for Yan, I do appreciate his help and support for my PhD and life at UK. I have learned much from his outstanding technical skills and excellent professionalism. I also appreciate his kind and helpful career advices. It is my great pleasure to become your friend. I am also thankful for Bo for his kind support for my career development. His valuable advices have made me obtain a deeper understanding for academic career and have strengthen my confidence and persistence to pursue my academic goals. It is my great luck to be your friend.

To Hock, my best friend at Newcastle. He has always taken me as his younger brother for these years, and has given me uncountable help for research and life. Besides, a special thank for his wife, Yingzhi, thanks a lot for her help in these years. Hock and Yingzhi, you are and will be always my family.

I sincerely thank Austin, Graeme, Musa, Michael, Ahmed, Ammar, Haider, Max, Nizar, Xuefu, Hang, and other colleagues at Neuroprosthesis lab and μSystem group, for their help and encouragement. I also thank Yang, Chen, Kuang, Yuqing, Ruisheng, Chloe, and Prof Nick Wright in NCL IEEE Branch, for their efforts and assistances. I am thankful for my friends in China, Xin, Xing, Kai, He, Xinsheng, Qiaojun, Haiyi, Mengxue, Mengliu, and Kang, for their continuous support.

I would thank Geraint and Steve for their advices for both patent filings. I thank the support from OptoNeuro and CANDO projects. I am thankful for Dr Timothy Constandinou for hosting me as a visiting student at Imperial College London.

At last, my deepest thanks and gratitude are given to my family. They always give me invaluable and unrequited love, which I cannot express it in both Chinese and English. No matter what I can do, I cannot pay back the love they have given to me. This thesis is dedicated to them. Most of all, to Sun, my girl, my dear fiancée, I deeply appreciate your accompany along this four-year journey. It is impossible for me complete it without your unrequited sacrifice and support. It is my greatest luck and happiness to being with you along the way. And best wishes for your PhD!

### **Abstract**

As a cell type-specific neuromodulation method, optogenetic technique holds remarkable potential for the realisation of advanced neuroprostheses. By genetically expressing light-sensitive proteins such as channelrhodopsin-2 (ChR2) in cell membranes, targeted neurons could be controlled by blue light. This new neuromodulation technique could then be applied into extensive brain networks and be utilised to provide effective therapies for neurological disorders.

However, the development of novel optogenetic implants is still a key challenge in the field. The major requirements include small device dimensions, suitable spatial resolution, high safety, and strong controllability. In particular, appropriate implantable electronics are expected to be built into the device, accomplishing a new-generation intelligent optogenetic implant. To date, different microfabrication techniques, such as wave-guided laser/light-emitting diode (LED) structure and µLED-on-optrode structure, have been widely explored to create and miniaturise optogenetic implants. However, although these existing devices meet the requirements to some extent, there is still considerable room for improvement.

In this thesis, a Complementary Metal-Oxide-Semiconductor (CMOS)-driven μLED approach is proposed to develop an advanced implantable optrode. This design is based on the μLED-on-optrode structure, where Gallium Nitride (GaN) μLEDs can be directly bonded to provide precise local light delivery and multi-layer stimulation. Moreover, an in-built diagnostic sensing circuitry is designed to monitor optrode integrity and degradation. This self-diagnosis function greatly improves system reliability and safety. Furthermore, in-situ temperature sensors are incorporated to monitor the local thermal effects of light emitters. This ensures both circuitry stability and tissue health. More importantly, external neural recording circuitry is integrated into the implant, which could observe local neural signals in the vicinity of the stimulation sites. Therefore, a CMOS-based multi-sensor optogenetic implant is achieved, and this closed-loop neural interface is capable of performing multichannel optical neural stimulation and electrical neural recording simultaneously. This optrode is expected to represent a promising neural interface for broad neuroprosthesis applications.

### **Publications**

#### **Patents**

- 1. Degenaar P and **Zhao H**, "Implantable Optrode", Application No.: GB1410886.4, Filed by Intellectual Property Office, UK, Filing Date: 18 June 2014.

- Degenaar P and Zhao H, "Optical Stimulation Arrangement", Application No.: GB1616725.6, Filed by Intellectual Property Office, UK, Filing Date: 30 Sep 2016.

### **On-going Journal Papers**

- 3. **Zhao H**, Sokolov D, Degenaar P, "A CMOS-based Implantable Optogenetic Stimulator with Self-Diagnosis Function", *IEEE Transactions on Circuits and Systems I: Regular Papers*, (ready to submit), Jan 2017.

- 4. "An Integrated Optogenetic Implant for Closed-Loop Neural Optical Stimulation and Electrical Recording", *IEEE Transactions on Biomedical Circuits and Systems*, (finalising draft), Jan 2017.

### **Published International Conference Papers**

- 5. **Zhao H**, Sokolov D, Degenaar P, "An Implantable Optrode with Self-Diagnostic Function in 0.35µm CMOS for Optical Neural Stimulation", *IEEE Biomedical Circuits and Systems Conference (BioCAS)*, 2014 (*Best Paper*).

- Zhao H, Liu Y, Constandinou TG et al., "A CMOS-based Neural Implantable Optrode for Optogenetic Stimulation and Electrical Recording", *IEEE BioCAS*, 2015.

- Soltan A, Zhao H, Chaudet L, et al., "An 8100 Pixel Optoelectronic Array for Optogenetic Retinal Prosthesis", *IEEE BioCAS*, 2014.

### **Local Conference Papers**

- 8. **Zhao H**, Sokolov D, Degenaar P, "An Integrated Closed-loop Neural Interface for Focal Epilepsy", *UK Sensory Motor Conference*, 2016.

- 9. **Zhao H**, Sokolov D, Degenaar P, "Design and Implementation of a CMOS-based Brain Implant for Neuroprosthesis", *Newcastle Annual Research Conference*, 2015 (*Best Paper*).

- 10. **Zhao H**, Sokolov D, Degenaar P, "A CMOS-MEMS based Feedback-loop Microsystem for Implantable Biomedical Applications", *North East Epilepsy Research Network Meeting*, 2013.

# **Contents**

| 1 | Introduc | etion                                   | 32 |

|---|----------|-----------------------------------------|----|

|   | 1.1 Mo   | otivation                               | 32 |

|   | 1.2 Re   | search Aim and Objectives               | 34 |

|   | 1.3 Th   | esis Outline                            | 35 |

| 2 | Backgro  | und and Literature Review               | 37 |

|   | 2.1 Int  | roduction                               | 37 |

|   | 2.2 Ba   | ckground on Neuroprosthetics            | 37 |

|   | 2.2.1    | Concept                                 | 37 |

|   | 2.2.2    | Applications                            | 38 |

|   | 2.2.3    | Summary                                 | 43 |

|   | 2.3 Ba   | ckground on Optogenetics                | 43 |

|   | 2.3.1    | Concept                                 | 43 |

|   | 2.3.2    | Applications                            | 44 |

|   | 2.3.3    | Summary                                 | 46 |

|   | 2.4 Lit  | terature Review of Optogenetic Implants | 47 |

|   | 2.4.1    | Introduction                            | 47 |

|   | 2.4.2    | Wave-Guiding Structure                  | 48 |

|   | 2.4.3    | μLED-on-Optrode Structure               | 55 |

|   | 2.4.4    | Summary                                 | 65 |

|   | 2.5 Co   | onclusion                               | 68 |

| 3 | Design C | Concept and Specifications              | 69 |

|   | 3.1 Int  | roduction                               | 69 |

|   | 3.2 Co   | oncentual Design                        | 69 |

|   | 3.2.1     | Potential Applications                        | 70  |

|---|-----------|-----------------------------------------------|-----|

|   | 3.2.2     | System Architecture                           | 72  |

|   | 3.3 Int   | elligent Implantable Electronics              | 75  |

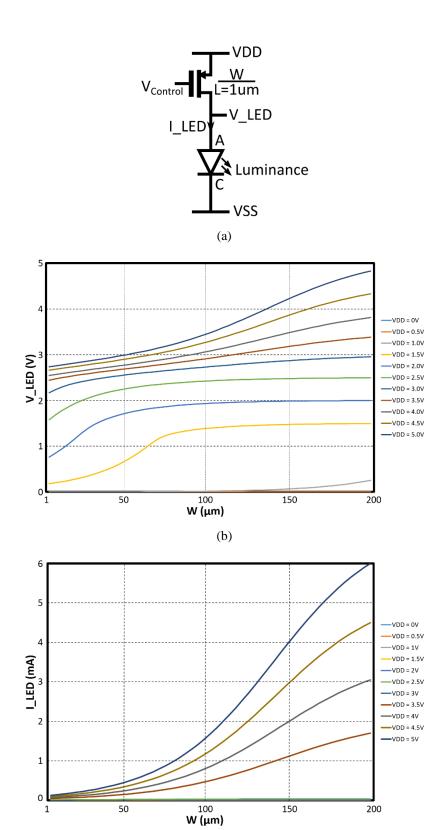

|   | 3.4 Fal   | brication Technology                          | 75  |

|   | 3.5 Mu    | ulti-site Optical Stimulation                 | 76  |

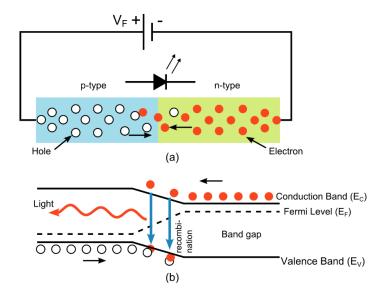

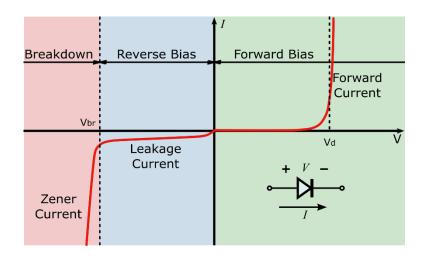

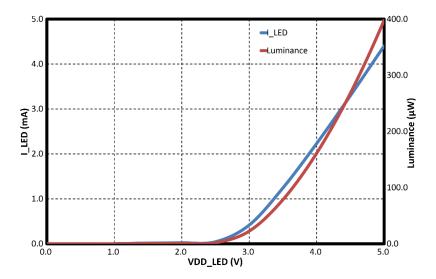

|   | 3.5.1     | Fundamentals of LEDs                          | 77  |

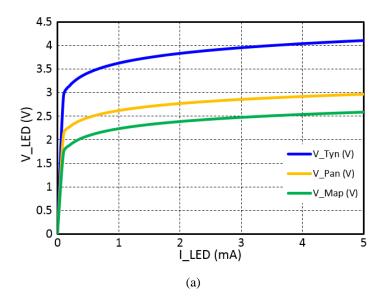

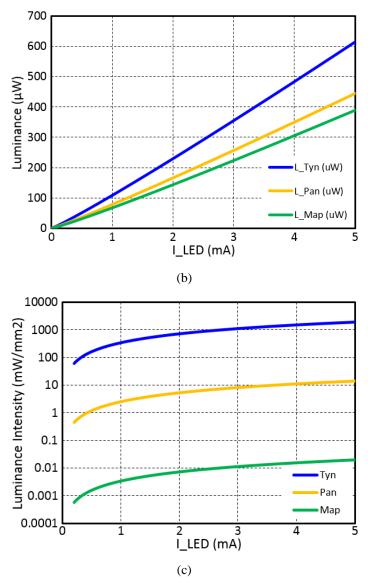

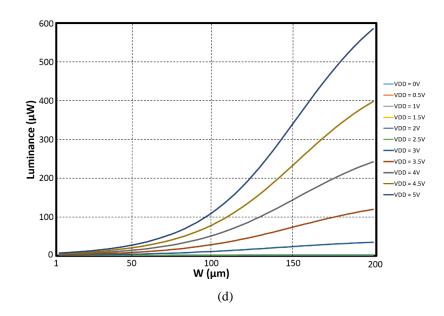

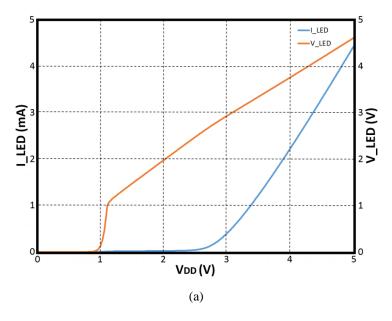

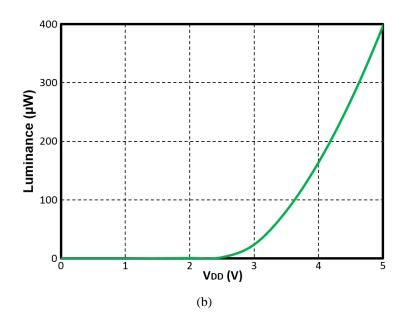

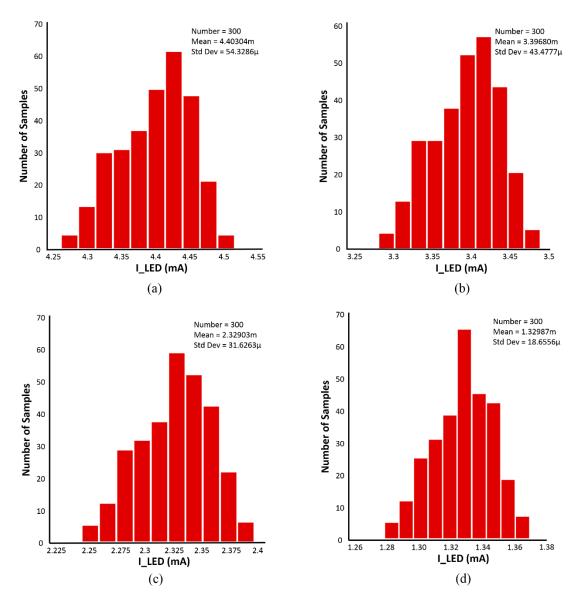

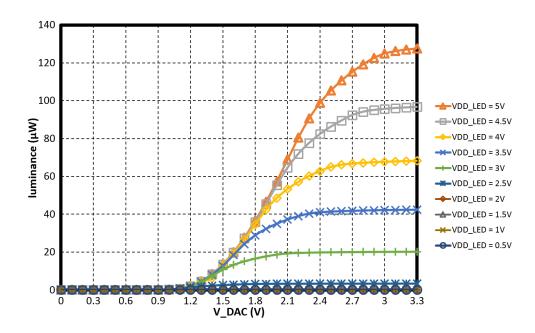

|   | 3.5.2     | Luminance Driving Ability and Controllability | 82  |

|   | 3.5.3     | Spatiotemporal Resolution                     | 84  |

|   | 3.5.4     | Biphasic Stimulation                          | 84  |

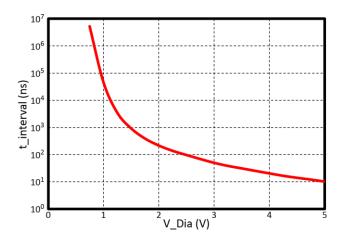

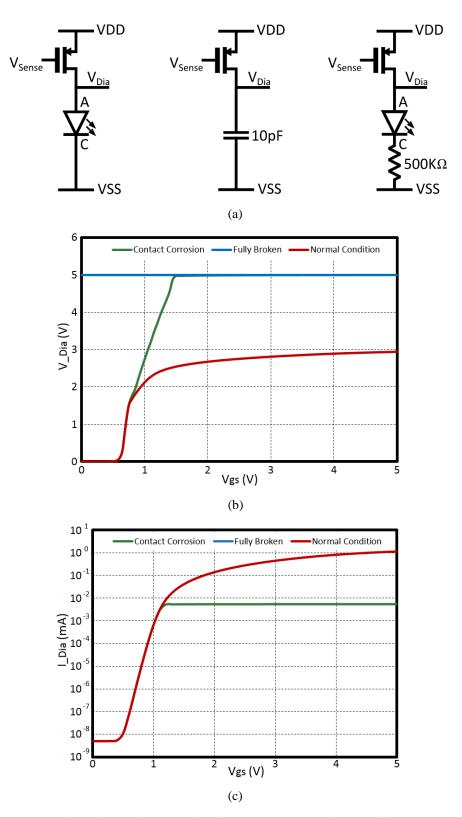

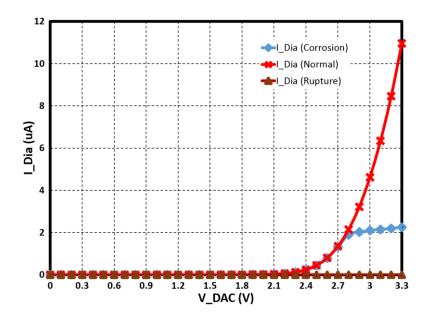

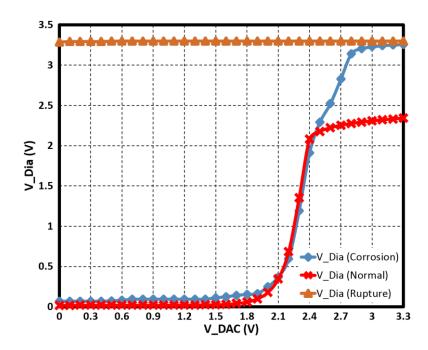

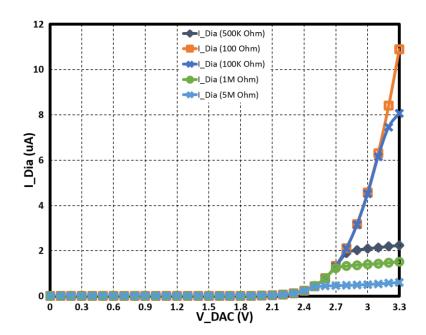

|   | 3.6 Sel   | If-Diagnostic Function                        | 85  |

|   | 3.7 Th    | ermal Analysis and Sensing                    | 89  |

|   | 3.8 Ele   | ectrical Neural Recording                     | 91  |

|   | 3.9 Po    | wer Budget                                    | 92  |

|   | 3.10 Co   | nclusion                                      | 92  |

| 4 | Circuit I | Design                                        | 96  |

|   | 4.1 Int   | roduction                                     | 96  |

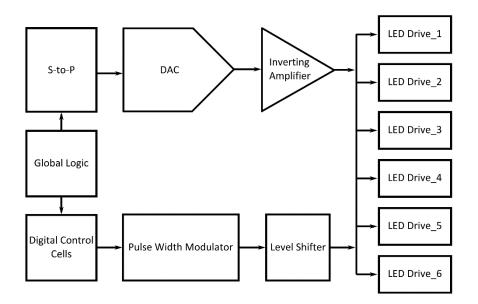

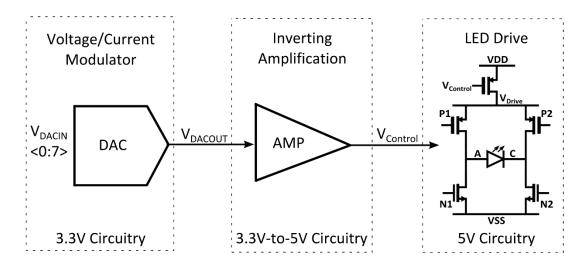

|   | 4.2 Op    | tical Stimulation Circuitry                   | 98  |

|   | 4.2.1     | Introduction                                  | 98  |

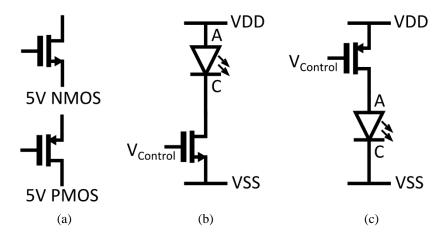

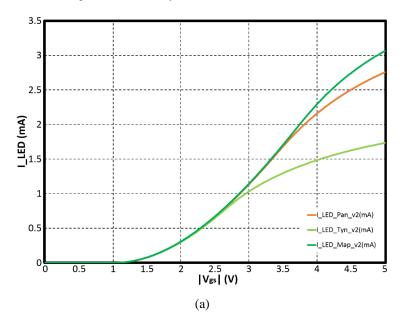

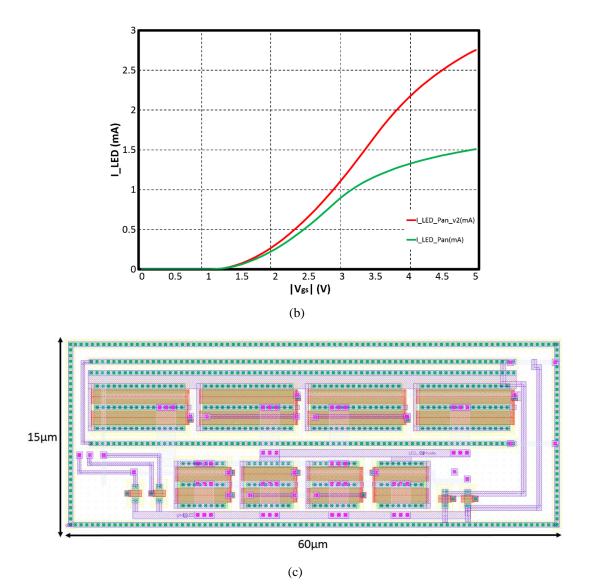

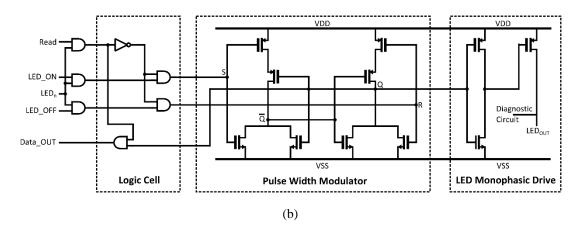

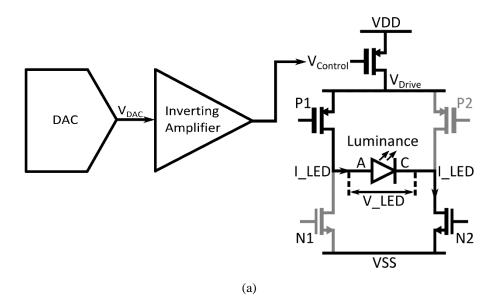

|   | 4.2.2     | μLED Drive Circuit                            | 99  |

|   | 4.2.      | 2.1 PMOS and NMOS                             | 99  |

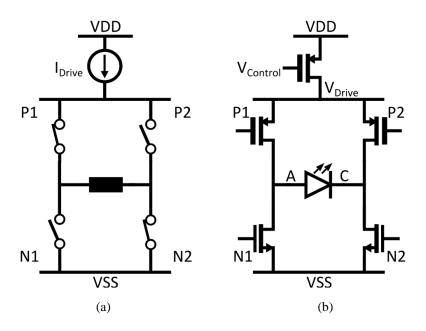

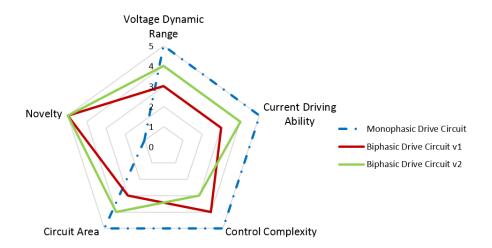

|   | 4.2.      | 2.2 Monophasic Drive Circuit                  | 100 |

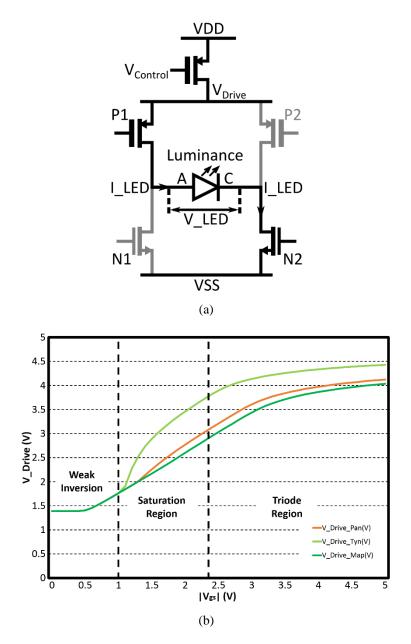

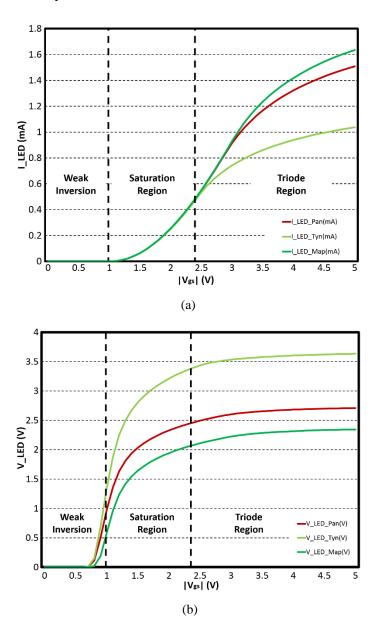

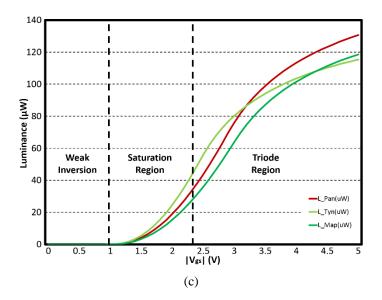

|   | 4.2.      | 2.3 Biphasic Drive Circuit                    | 104 |

|   | 4.2.      | 2.4 Summary                                   | 113 |

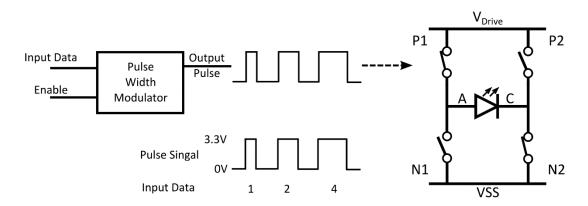

|   | 4.2.3     | Intensity Modulation Mechanism                | 114 |

|   | 4.2.      | 3.1 Pulse Width Modulation Control            | 115 |

|   | 4.2.      | 3.2 Intensity Magnitude Control               | 115 |

|   | 4.2.4 P    | ulse Width Modulator              | 116 |

|---|------------|-----------------------------------|-----|

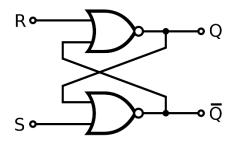

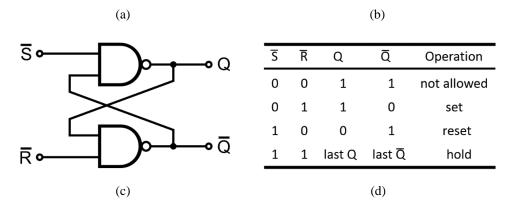

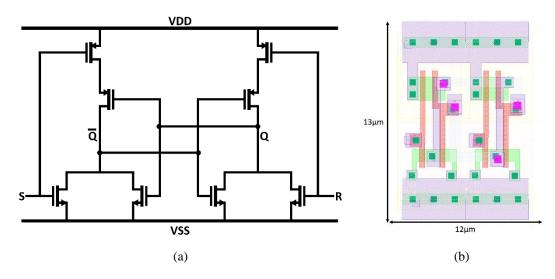

|   | 4.2.4.1    | SR Latch                          | 116 |

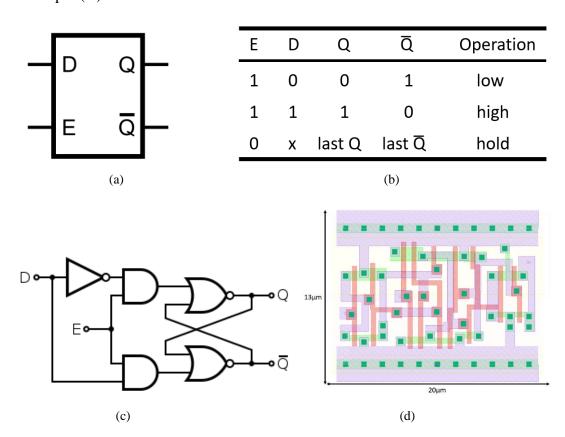

|   | 4.2.4.2    | D Latch                           | 118 |

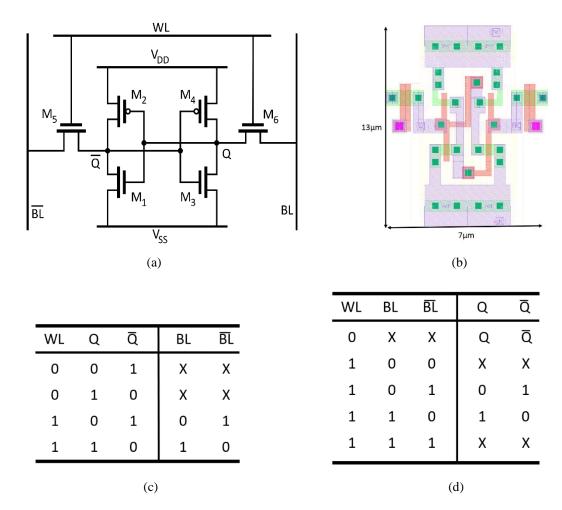

|   | 4.2.4.3    | SRAM                              | 120 |

|   | 4.2.4.4    | Summary                           | 122 |

|   | 4.2.5 In   | verting Voltage Amplifier         | 123 |

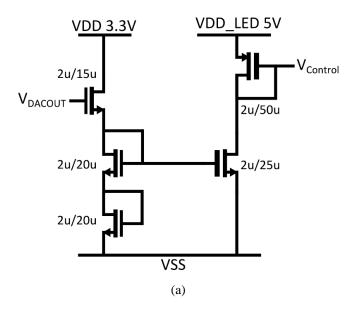

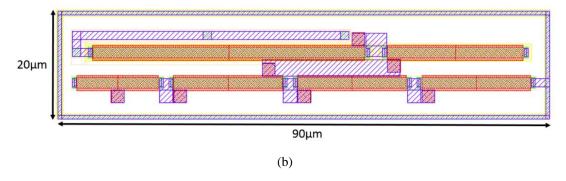

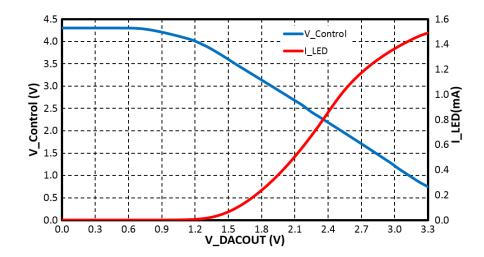

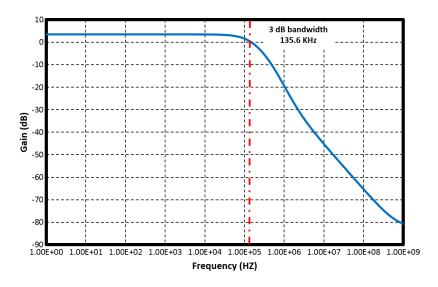

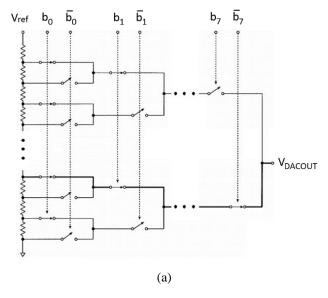

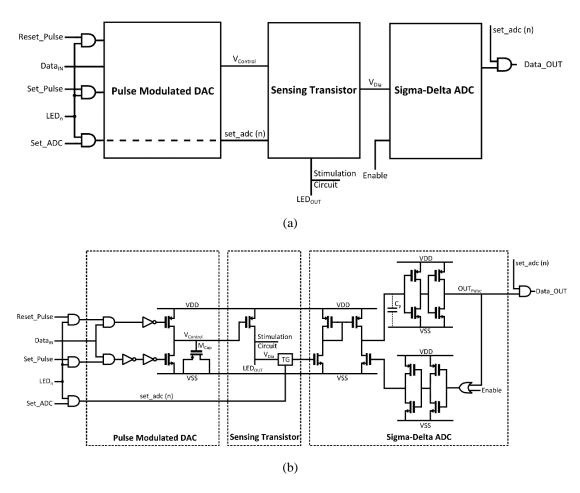

|   | 4.2.6 D    | rigital to Analogue Converter     | 126 |

|   | 4.2.6.1    | Resistor String DAC               | 126 |

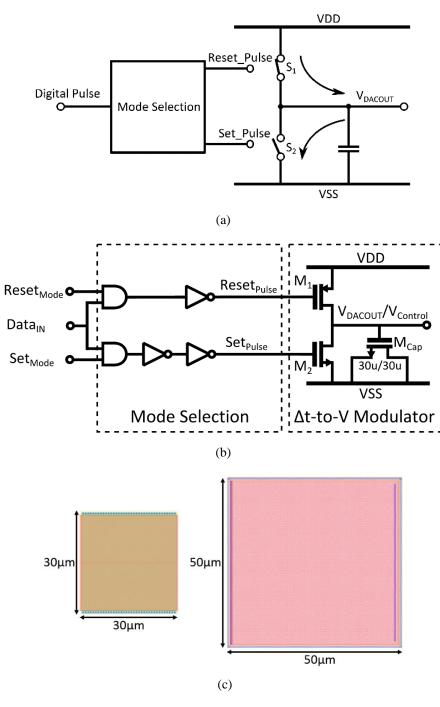

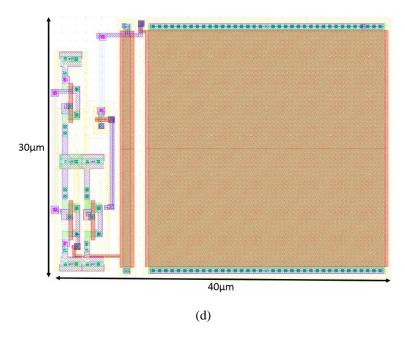

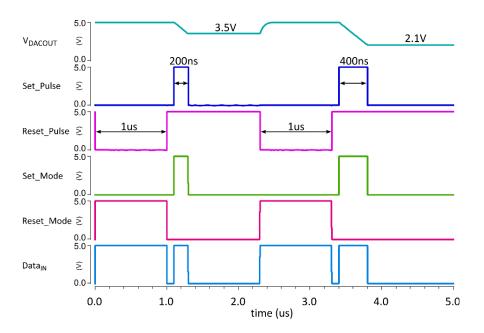

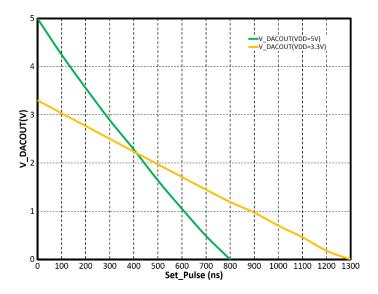

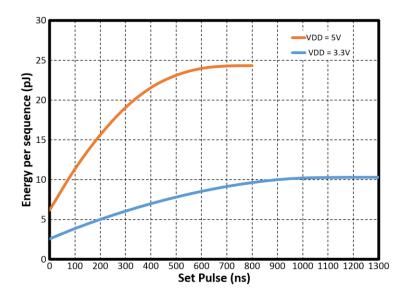

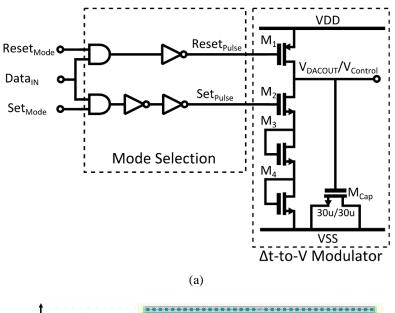

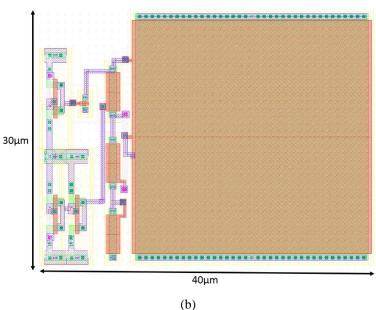

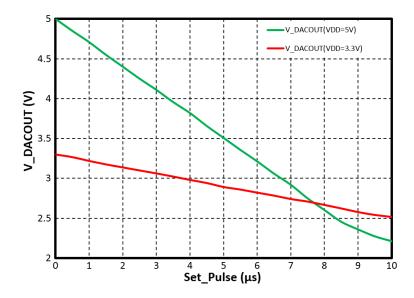

|   | 4.2.6.2    | Pulse Width Modulated DAC         | 129 |

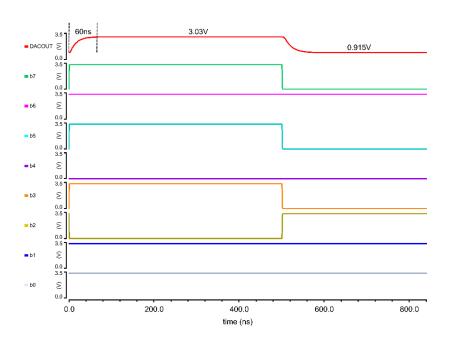

|   | 4.2.6.3    | Updated Pulse Width Modulated DAC | 135 |

|   | 4.2.6.4    | Summary                           | 138 |

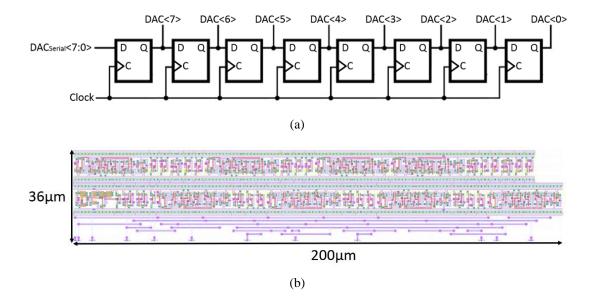

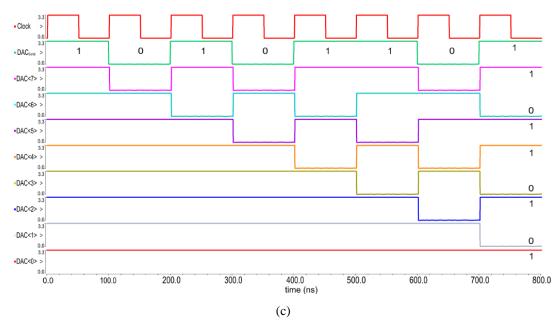

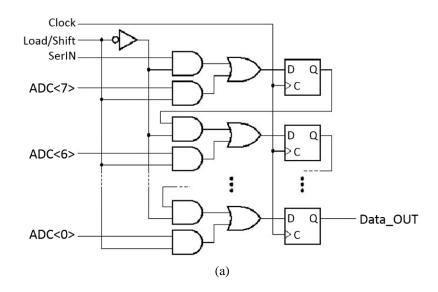

|   | 4.2.7 Se   | erial to Parallel Interface       | 139 |

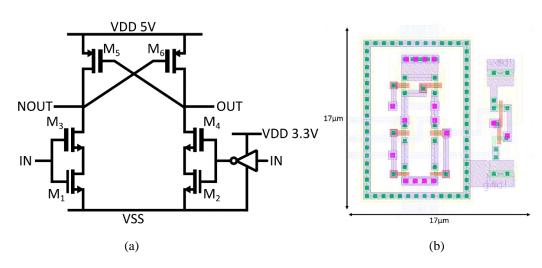

|   | 4.2.8 L    | evel Shifter                      | 140 |

|   | 4.2.9 S    | ummary                            | 141 |

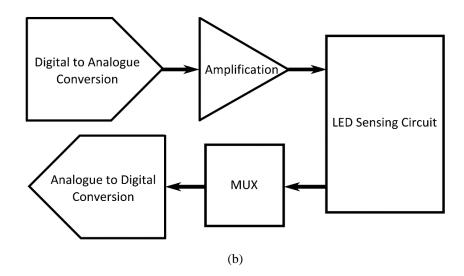

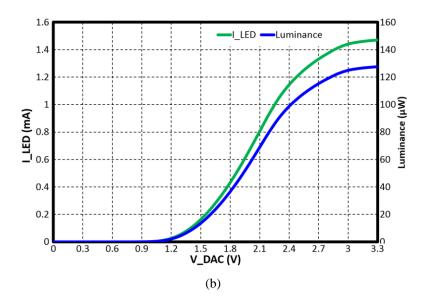

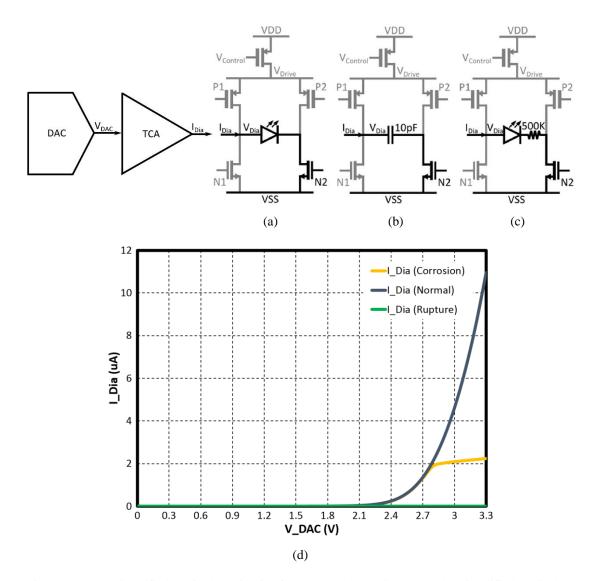

|   | 4.3 Diagno | ostic Sensing Circuitry           | 142 |

|   | 4.3.1 In   | ntroduction                       | 142 |

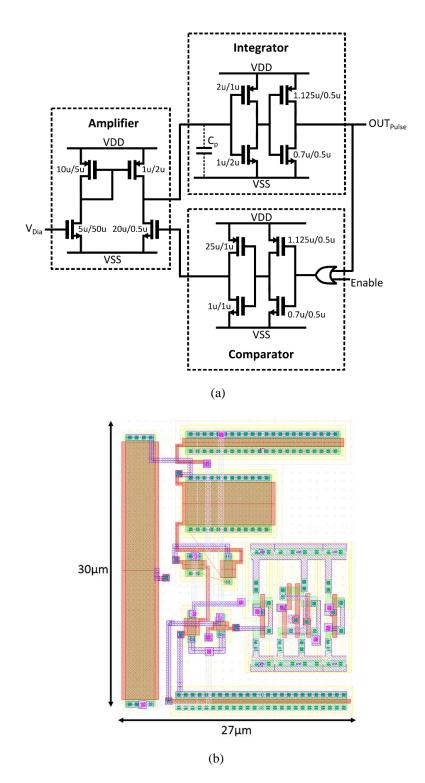

|   | 4.3.2 T    | rans-Conductance Amplifier        | 144 |

|   | 4.3.3 A    | nalogue to Digital Converter      | 147 |

|   | 4.3.3.1    | SAR ADC                           | 147 |

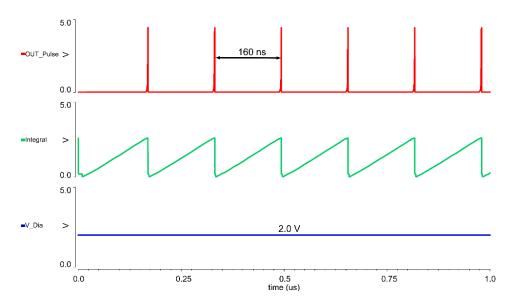

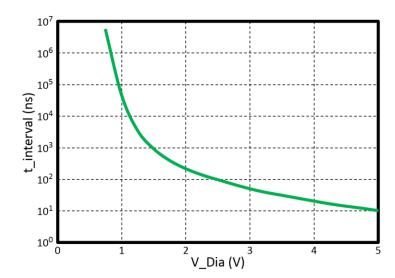

|   | 4.3.3.2    | Sigma-Delta ADC                   | 149 |

|   | 4.3.3.3    | Summary                           | 153 |

|   | 4.3.4 Pa   | arallel to Serial Interface       | 154 |

|   | 4.3.5 S    | ummary                            | 155 |

|   | 4.4 Concl  | usion                             | 156 |

| _ | G I        | 1 4. 4                            | 150 |

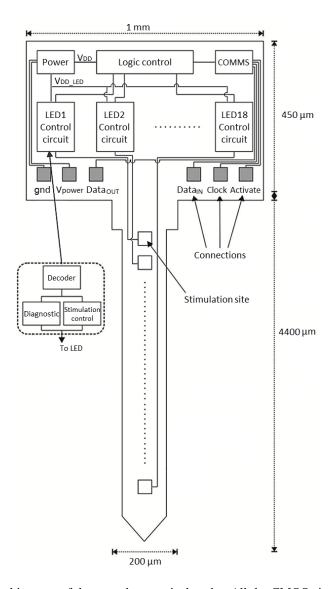

| 5 | System Imp | lementation                       | 159 |

|   | 5.1 Introd | uction                            | 159 |

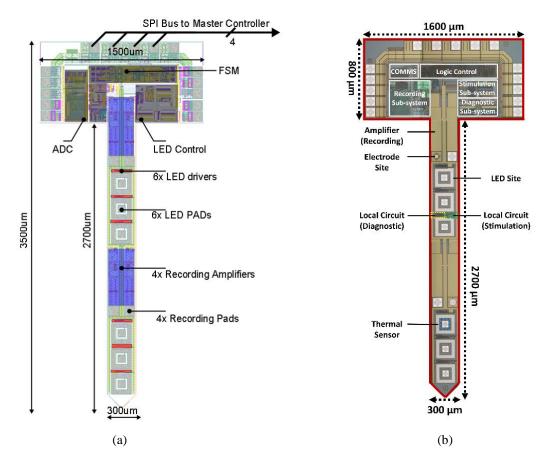

| 5. | .2 Ope  | en-Loop Optrode for Optical Neural Stimulation160              |

|----|---------|----------------------------------------------------------------|

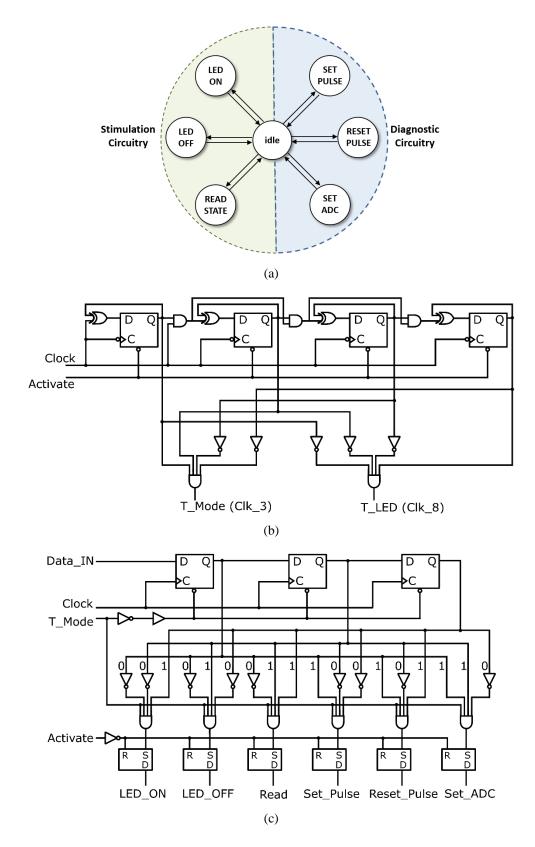

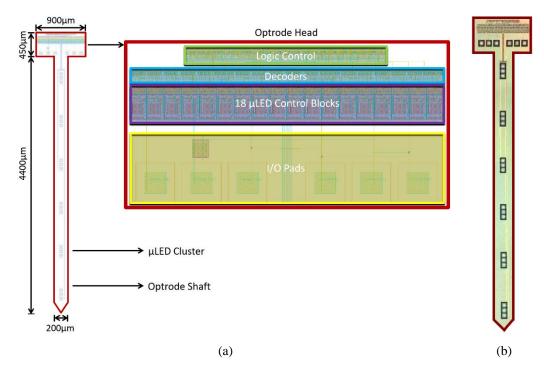

|    | 5.2.1   | System Architecture                                            |

|    | 5.2.2   | Logic Control                                                  |

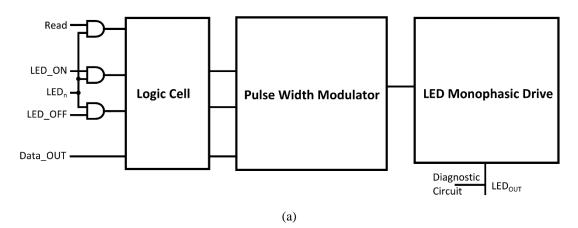

|    | 5.2.3   | Stimulation Control Subsystem                                  |

|    | 5.2.4   | Diagnostic Sensing Subsystem                                   |

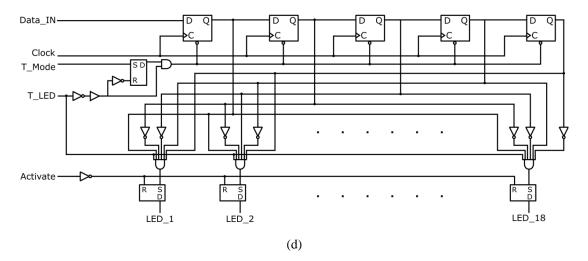

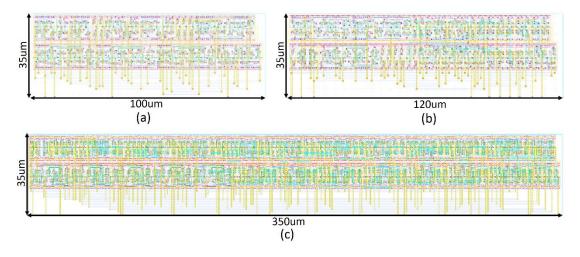

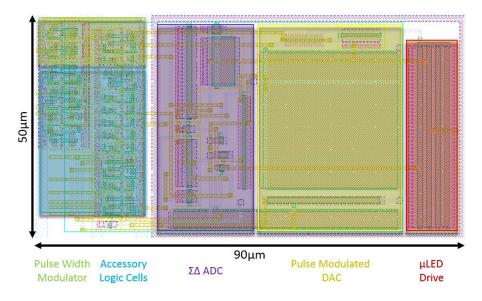

|    | 5.2.5   | Local Block Integration169                                     |

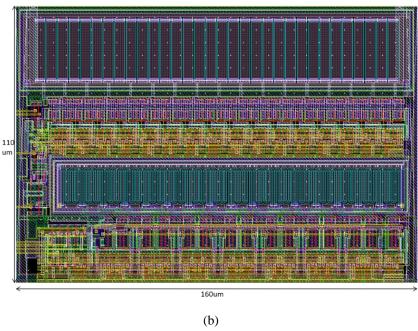

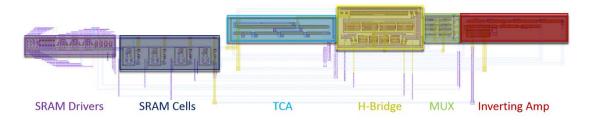

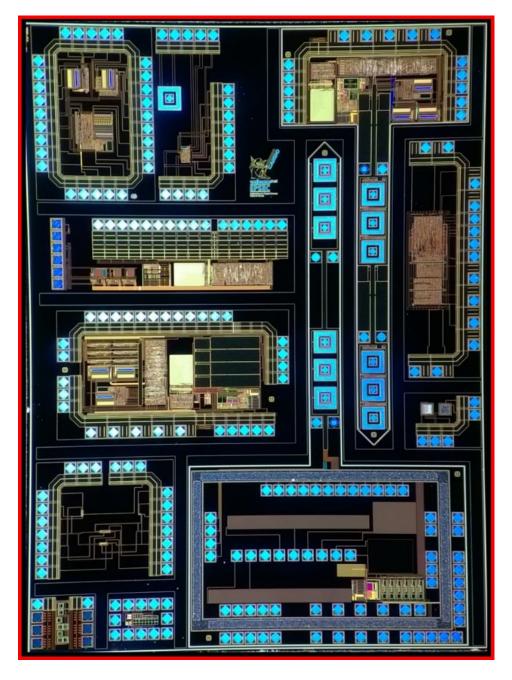

|    | 5.2.6   | Chip Layout and Fabrication                                    |

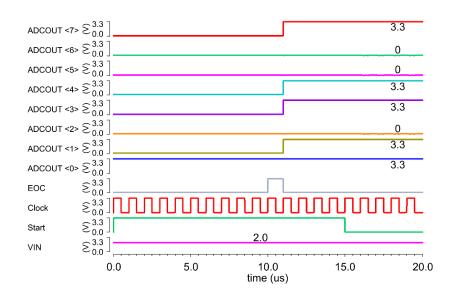

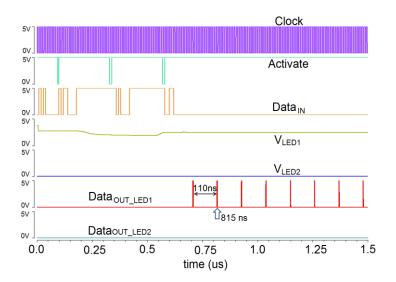

|    | 5.2.7   | Top-level Simulation Results                                   |

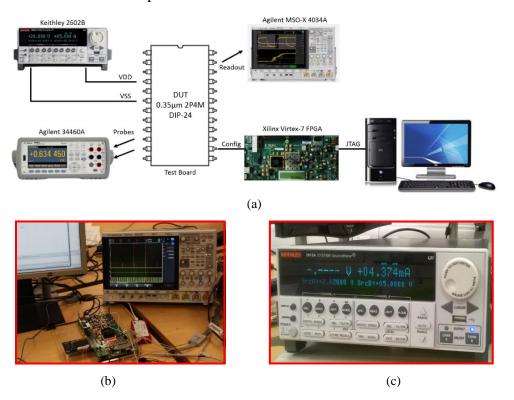

|    | 5.2.8   | Experiment Set-up                                              |

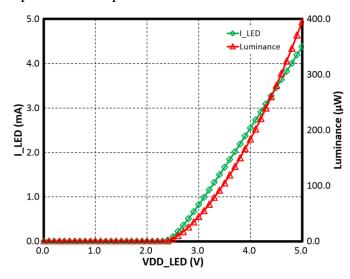

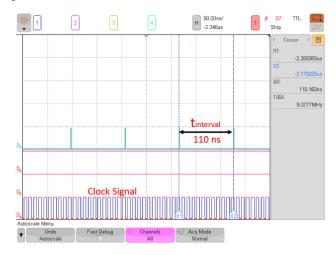

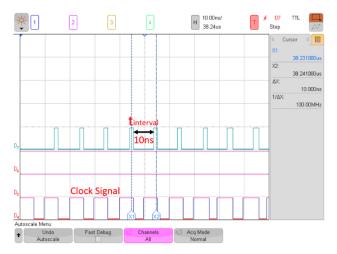

|    | 5.2.9   | Measurement Results                                            |

|    | 5.2.10  | Summary                                                        |

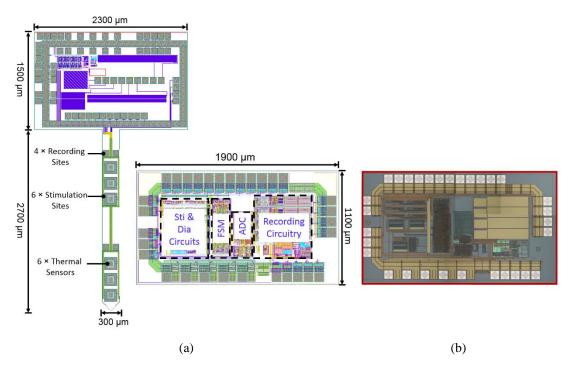

| 5. | .3 Clos | sed-Loop Optrode for Optical Neural Stimulation and Electrical |

|    | Neu     | ral Recording                                                  |

|    | 5.3.1   | System Architecture                                            |

|    | 5.3.2   | Logic Control                                                  |

|    | 5.3.3   | Stimulation Control Subsystem                                  |

|    | 5.3.4   | Diagnostic Sensing Subsystem                                   |

|    | 5.3.5   | Local Block Integration                                        |

|    | 5.3.6   | Temperature Sensor                                             |

|    | 5.3.7   | Neural Recording Subsystem (Dr Yan Liu's Work)                 |

|    | 5.3.8   | Configurations - Active Optrode and Passive Optrode 194        |

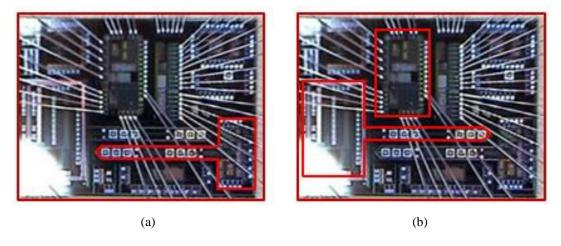

|    | 5.3.9   | Chip Layout and Fabrication                                    |

|    | 5.3.10  | Top-level Simulation Results                                   |

|    | 5.3.11  | Experiment Set-up                                              |

|    | 5.3.12  | Measurement Results                                            |

|    | 5.3.13  | Summary                                                        |

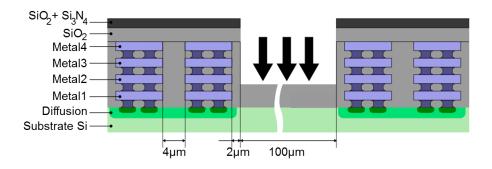

| 5. | 4 Pos   | t-processing219                                                |

|     | 5.5    | Conclusion                      | . 220 |

|-----|--------|---------------------------------|-------|

| 6   | Cone   | clusion                         | 222   |

|     | 6.1    | Original Contributions          | . 222 |

|     | 6.2    | Recommendations for Future Work | . 225 |

|     | 6.3    | Concluding Remarks              | . 226 |

| Ref | erence | S                               | . 228 |

| App | endix  | es                              | . 239 |

|     |        |                                 |       |

# **List of Figures**

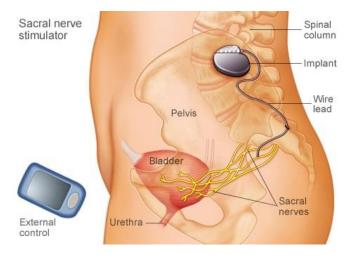

| Figure 2.1 A bladder prosthesis system which has been widely used for medical       |

|-------------------------------------------------------------------------------------|

| treatment [22]. The system mainly consists of a sacral nerve stimulate              |

| and an external controller. The stimulator is typically implanted throug            |

| a miniature cut above the tailbone via surgery, and it can stimulate th             |

| sacral nerves which dominant bladder functioning3                                   |

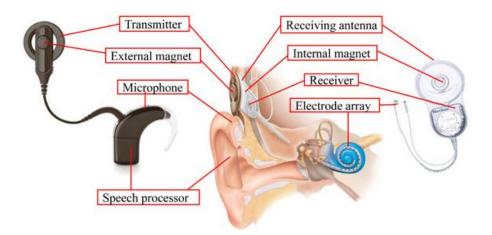

| Figure 2.2 Typical diagram of cochlear implant neural prosthesis system [8]. It use |

| external recording components to receive sound waves. Next, recorde                 |

| sound information is wirelessly transmitted into implanted electrodes               |

| These electrodes could then stimulate the targeted neurons, thus enablin            |

| patients to decode sound waves                                                      |

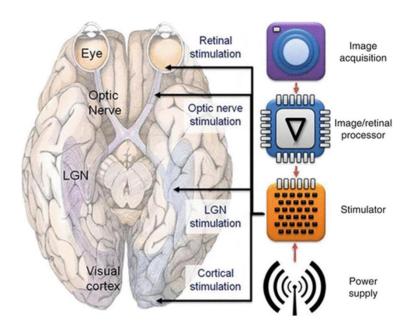

| Figure 2.3 General conceptual diagram of visual prosthesis [28]. Visual prostheti   |

| systems usually consist of four main modules: image acquisition stage               |

| image processing, neural stimulator, and power supply 4                             |

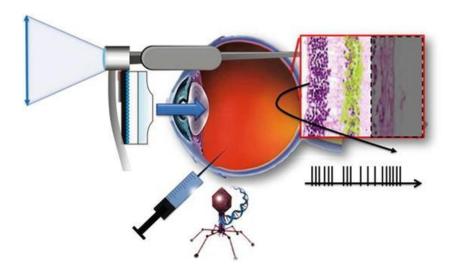

| Figure 2.4 Diagram of an optogenetics retinal prosthesis system [28]. A specifi     |

| virus is injected into the eye to photosensitize retinal cells. A high              |

| density optical array could be utilised to project light pattern into the ey        |

| 4                                                                                   |

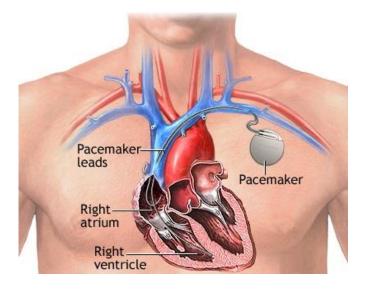

| Figure 2.5 A commonly-used heart pacemaker system [31]. The pulse generator is      |

| placed at the chest, and the pacemaker lead transfers the electrical pulse          |

| from the pacemaker to the heart4                                                    |

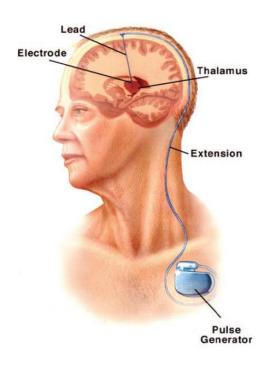

| Figure 2.6 A typical DBS system[3]. This system mainly consists of an electrode,    |

| bio-compatible lead with extension, and the pulse generator 4                       |

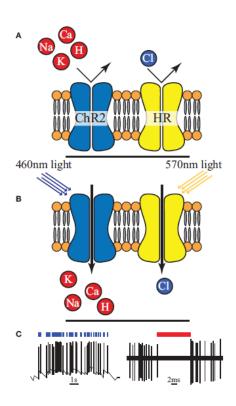

| Figure 2.7 A principle diagram of optogenetics stimulation using ChR2 and NpHl      |

| [11]. (a) The ChR2 ion channel and NpHR ion pump are both in inactiv                |

| states. (b) After receiving blue/yellow light (with predefine                       |

| wavelength), positive ions and chloride ions enter the cell via ChR2 an             |

| NpHR respectively. (c) ChR2 activation triggers action potentials, whil             |

| action potentials are inhibited by the activation of NpHR4                          |

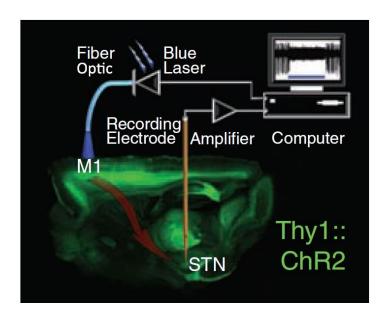

| Figure 2.8 Simplified diagram of the ChR2-NpHR optogenetics system[71]. A fibre     |

| coupled laser is used for light activation and inhibition. A recordin               |

| electrode observes the neural signals from the STN, and these signals ar            |

| then sent to a PC console after amplification                                       |

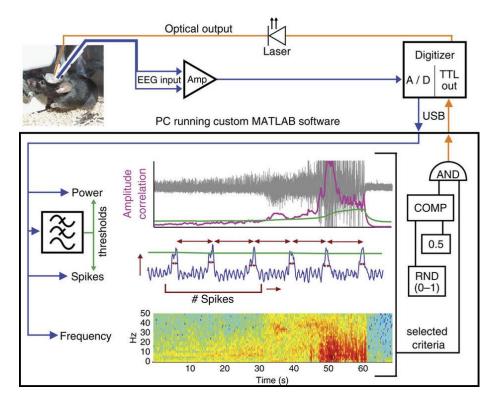

| Figure 2.9 Closed-loop optogenetics system for TLE [72]. EEG signals are recorde    |

| from the hippocampus area of the mouse. These are sent to a PC-base                 |

| seizure detection software via amplification and A-D conversion stages              |

| The PC console could then determine whether to trigger the optical                  |

| stimulator A                                                                        |

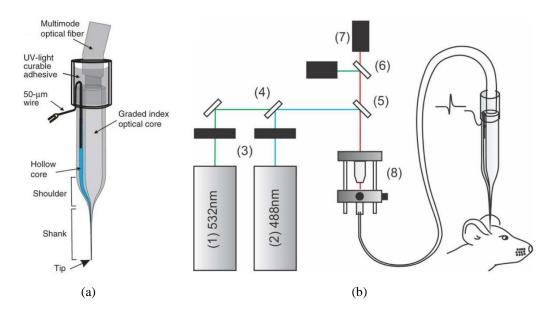

| Figure 2.10 | (a) Schematic diagram of the multimode optical fibre-coupled probe [95]                     |

|-------------|---------------------------------------------------------------------------------------------|

|             | A graded index optical core is coupled with the optical fibre to realise                    |

|             | light delivery. A hollow core is used for the in-situ observation of neural                 |

|             | activities. The shaft tip is shaped to 10 µm diameter for single-neuron                     |

|             | manipulation. (b) Experiment set-up of this optical-electrical microprobe                   |

|             | system [96]. (1) (2) are two different laser sources; (3) are two shutters;                 |

|             | (4) (5) (6) are dichroic mirrors; (7) are PMT detectors and bandpass                        |

|             | filters; (8) is a fibre optical launch system                                               |

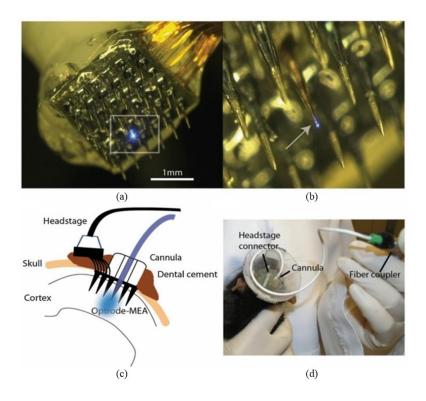

| Figure 2.11 | System diagram of this optrode-MEA system [97]. (a) Picture of the 6×6                      |

|             | Utah MEA with substituted fibre-coupled optical probe. (b) Zoom-in                          |

|             | view of the probe tip. (c) Cartoon image of the overall system. Cannula                     |

|             | and dental cement are used to encapsulate the optrode and MEA. (d) The                      |

|             | system is implanted into the subject via a headstage connector 50                           |

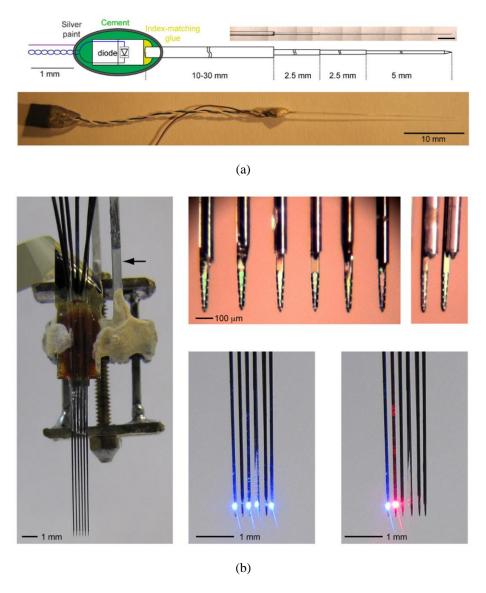

| Figure 2.12 | Fibre-coupled multi-diode optical array [99]. (a) A single four-step fibre                  |

|             | probe. The total length is 50 mm, and the last shank is 5 mm long with a                    |

|             | 12° tip. (b) Assembled fibre array, consisting of six individual probes                     |

|             | with ~200 µm spacing. Four of them are designed for blue light emission                     |

|             | and the other two are dedicated for red light stimulation51                                 |

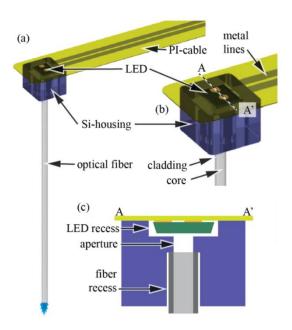

| Figure 2.13 | B Cartoon image of the fibre-coupled µLED optical probe [100]. This                         |

|             | system mainly consists of a $270\times220\times50~\mu\text{m}^3$ LED chip, a flexible Pl    |

|             | cable, a $550 \times 500 \times 380~\mu\text{m}^3$ Si housing, and a 5mm-long optical fibre |

|             | with 125 µm diameter                                                                        |

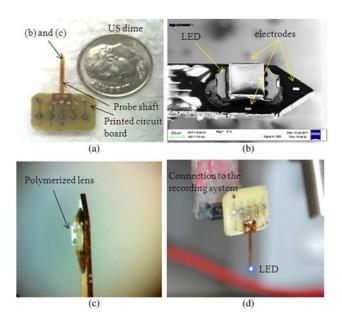

| Figure 2.14 | 4 Flexible polyimide-based μLED optrode [105]. (a) A printed circuit                        |

|             | board (PCB) is fabricated to assemble the optrode. (b) A scanning                           |

|             | electron microscope (SEM) image of the optrode tip. The $\mu LED$ site is                   |

|             | bonded along with three recording sites. (c) A polymerised lens is                          |

|             | covered on the $\mu LED$ . (d) The overall system. $\mu LED$ is turned on by a              |

|             | 2.9 V forward bias voltage                                                                  |

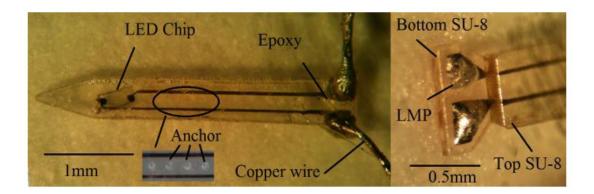

| Figure 2.15 | 5 Samsung µLED mounted at the tip of the fabricated optrode [107].                          |

|             | Several SU-8 anchors are created along the probe shaft, enhancing the                       |

|             | bonding strength of two SU-8 layers. Cooper wire is bonded on the                           |

|             | probe via the low melting point (LMP). Epoxy is adopted to further                          |

|             | strengthen the bonding robustness                                                           |

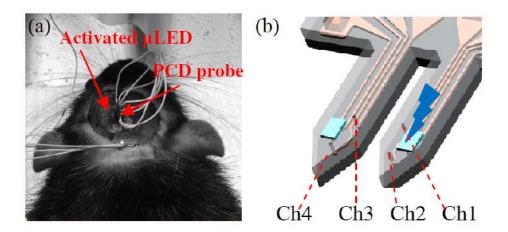

| Figure 2.16 | The PCD-based optical probe [108]. (a) This PCD probe is inserted into                      |

|             | an experimental rat for the <i>in-vivo</i> test. (b) A diagram of this two-shank            |

|             | probe. In each shank, the µLED is placed at the shaft tip, and two                          |

|             | recording channels are positioned in the vicinity of stimulation site 58                    |

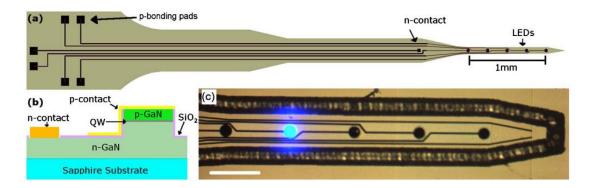

| Figure 2.17 | Sapphire-based GaN μLED optrode [109]. (a) System architecture of this                      |

|             | optrode. Six bonding pads are placed at the head part to control                            |

|             | corresponding µLEDs which are uniformly positioned along the optrode                        |

|             | shaft. (b) The cross-section view of the fabrication process. (c) The                       |

|              | light                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

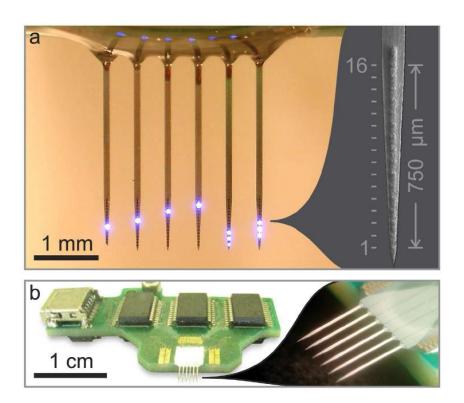

| Figure 2.18  | Silicon-based 6-shank GaN μLED optrode [110]. (a) 16 stimulation sites                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| υ            | are created on each shank, and they are uniformly distributed along the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|              | 750 µm shaft. Every µLED can be individually manipulated. (b) System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|              | diagram. The fabricated optrode is bonded on a dedicated control PCB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

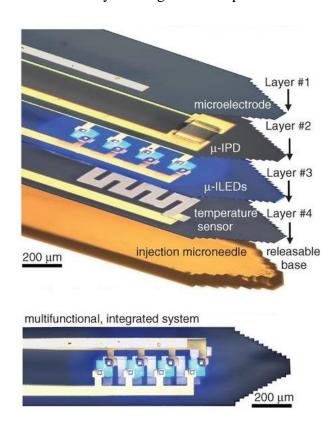

| Figure 2.19  | Flexible electronics-based multifunctional implantable probe [111]. Four                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 118410 2.17  | different functional layers are incorporated along with a releasable base.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|              | The recording microelectrode is constructed on Layer 1; and then a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|              | micro-inorganic photodetector ( $\mu$ -IPD) is utilised for photodetection at                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|              | Layer 2; Layer 3 contains four micro-inorganic LEDs (µ-ILEDs) for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|              | optogenetic stimulation; and Layer 4 is dedicated to temperature sensing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|              | optogenetic stimulation, and Layer 4 is dedicated to temperature sensing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

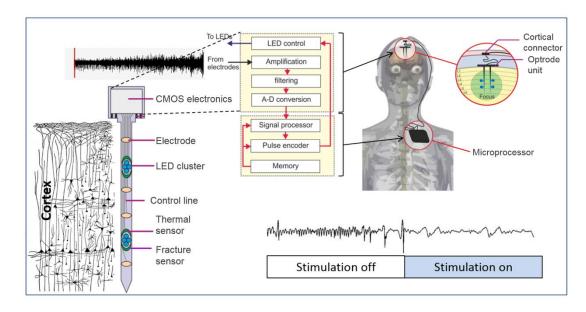

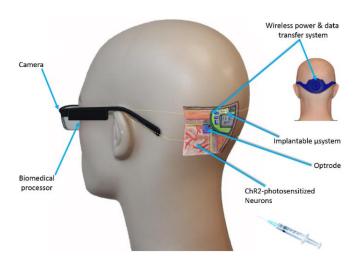

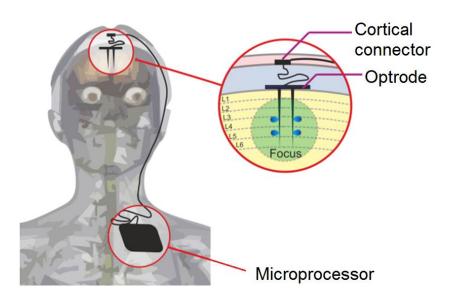

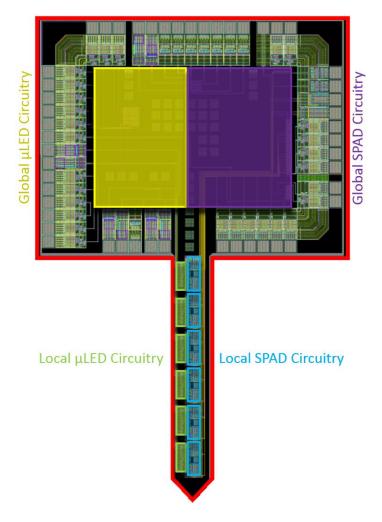

| Figure 3.1   | Conceptual diagram of the proposed optrode. This multifunctional                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 11guie 3.1   | optogenetic implant is fabricated in standard CMOS process. It mainly                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|              | consists of optical stimulation circuitry, electrical recording circuitry,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|              | diagnostic sensing circuitry, and temperature sensing circuitry. The                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|              | optrode will be utilised in practice with general neuroprosthetic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|              | pacemakers. Closed-loop algorithm will be embedded into the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| F: 0.0       | biomedical processor. This figure is modified from [115]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

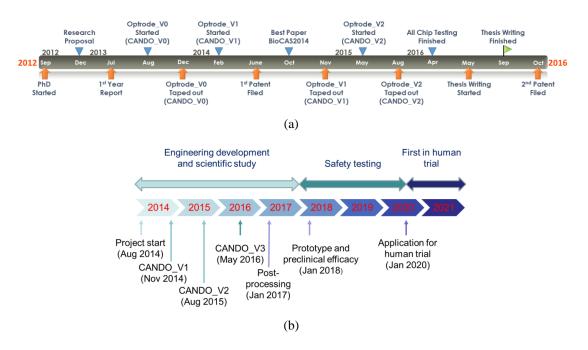

| Figure 3.2   | (a) My PhD timing line, from September, 2012 to September 2016. (b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|              | CANDO project timing line, launched August, 2014                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

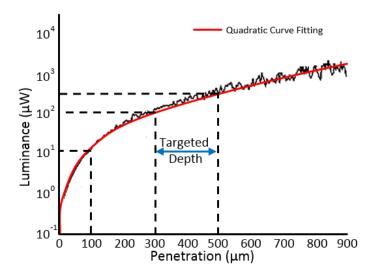

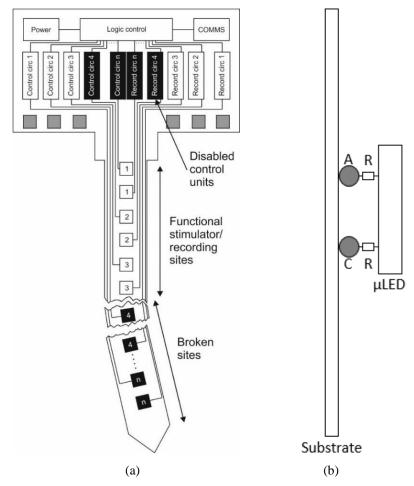

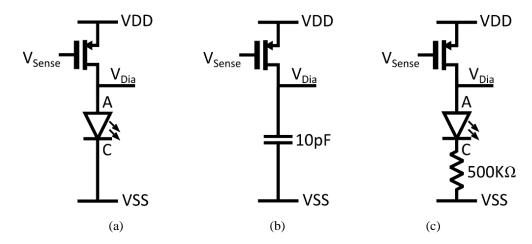

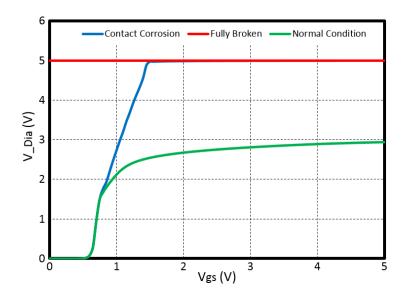

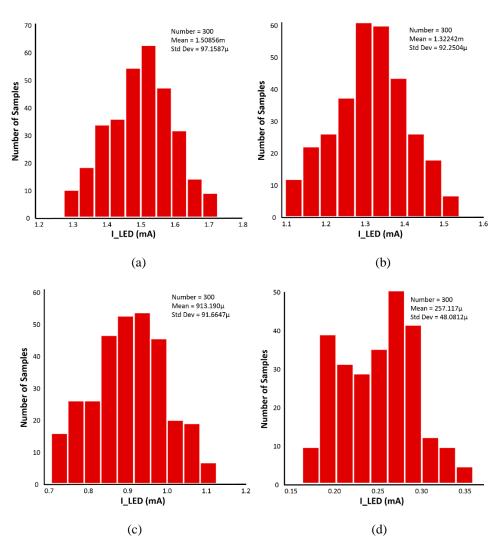

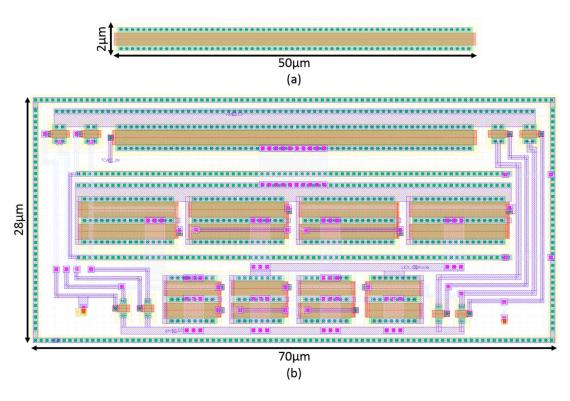

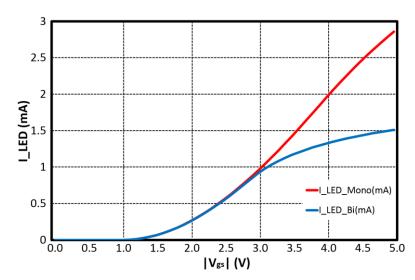

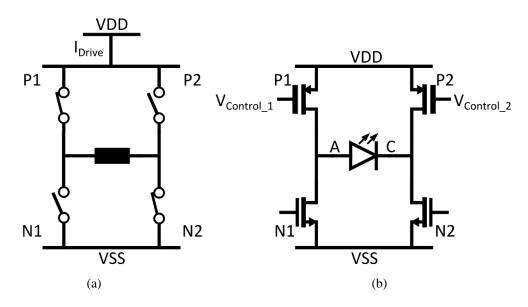

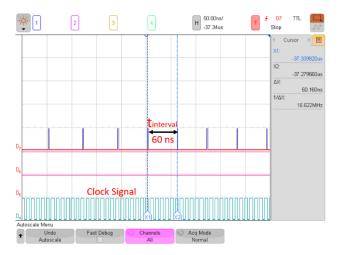

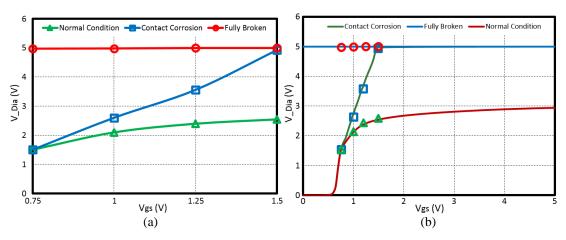

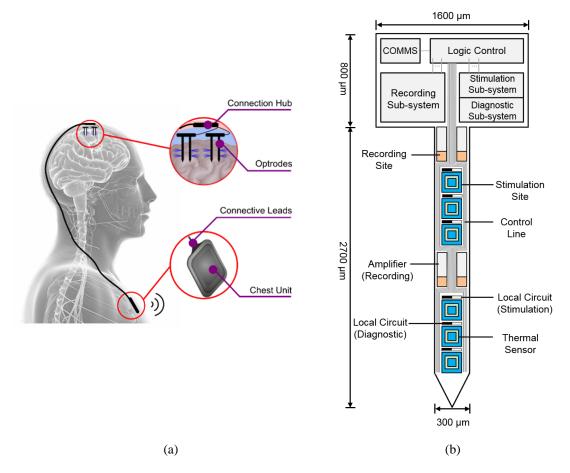

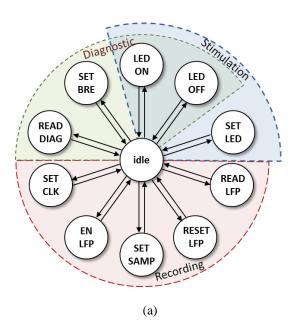

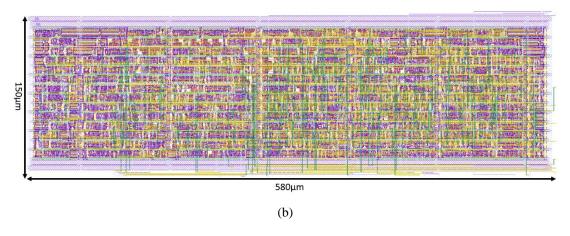

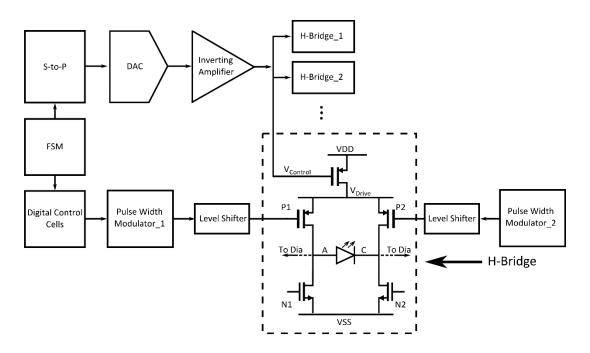

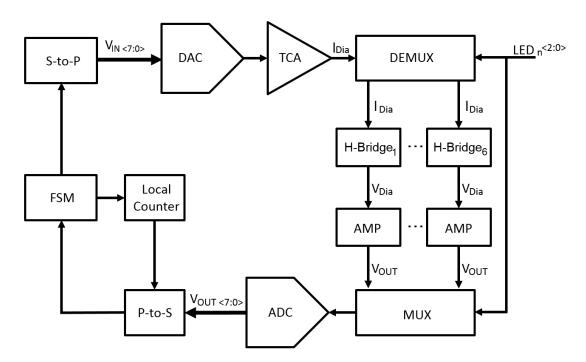

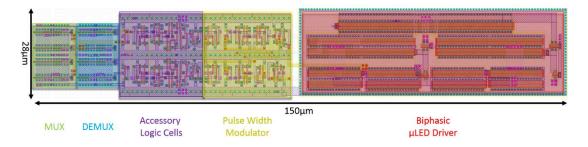

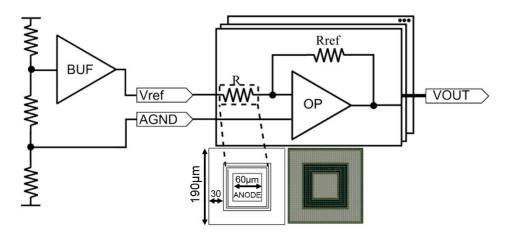

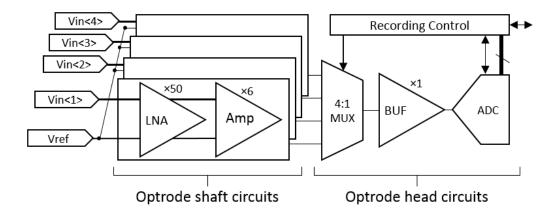

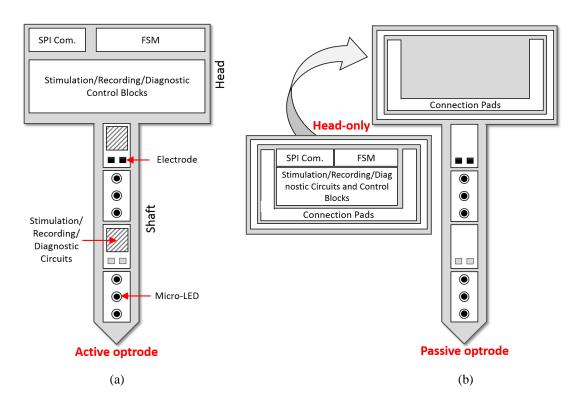

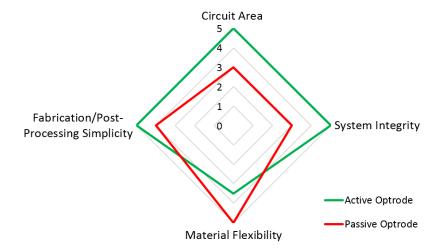

| Figure 3.3   | General diagram of an implantable µsystem for visual cortical prosthesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |