# Distributed static series compensator in 11kV networks

## **Afshin Pashaei**

A thesis submitted for the degree of Philosophy of Doctorate

May 2015

Newcastle University School of Electrical, Electronic & Computer Engineering

#### **Abstract**

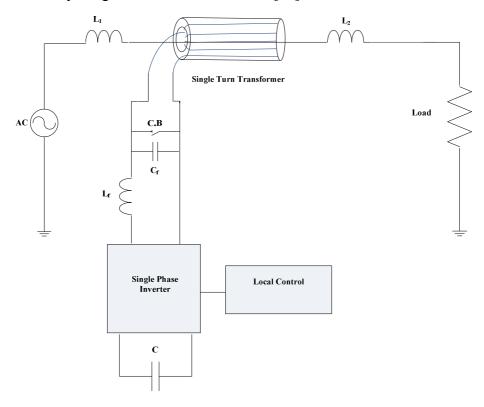

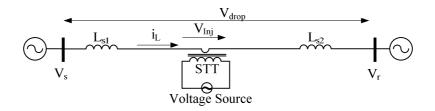

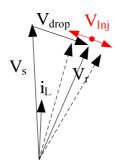

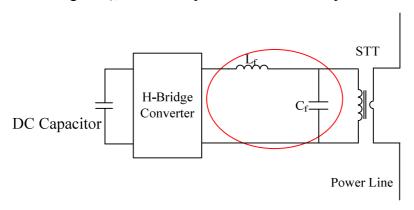

Series compensation techniques can be very effective when applied in an electrical network to increase the power transfer capacity of existing power lines. Distributed Static Series Compensation (DSSC) is a power electronics based series compensation scheme in which a DSSC device comprises of a single-phase H-bridge voltage source converter, a dc link capacitor and a low pass filter suspended from the power line via a single turn transformer. The application of DSSC in the 11kV distribution network is investigated in this thesis. This is followed by a study of existing control strategies employed in DSSC and Static Synchronies Series Compensation (SSSC) schemes.

Most of these controllers are based on dq transformation methods in which balanced conditions are assumed and zero sequence currents are assumed to be negligible. While this might be a reasonable assumption at transmission level voltages, but it can be argued that in the presence of unbalanced loads and currents (a common feature of lower voltage distribution networks) these strategies can be inaccurate, leading to the wrong amount of compensation being injected. In addition some of the studied controllers are based on the 90° phase shift of line current. Practically, the injection angle must be slightly different in order to compensate the internal losses of the DSSC. The need for the diversion from the 90° can change over the time and this can threaten the stability of the system.

A new single-phase control strategy based on the instantaneous power exchange between the DSSC devices and each of the three phase conductors is proposed in this thesis to address this issue. The new control method does not employ a dq transformation and is immune from the probable errors resulting from the presence of unbalanced network conditions. In the same time the injection angle is not fixed and it is adjusted by the controller.

The operation of DSSC can be categorized in two modes and transfer function of system is obtained based on these two modes. The transfer function is used in the design of controller. This is followed by analyzing immunity of the designed controller against change of system parameters. The proposed scheme is simulated (using PSCAD software) to examine the operation of the new control method and the resulting impact on the 11kV distribution feeder, including the ability to divert power from one line to another and the ability to improve network voltage profiles. Performance of DSSC using the proposed controller is compared with performance of DSSC when the traditional controllers are employed.

Effect of line resistance on the performance of the DSSC is studied and relation between the compensation and X/R ratio of compensated line is highlighted. A fault management study is conducted in order to find a fault recovery strategy in the occurrence of fault.

A 50V test rig has been designed and built to verify the operation of the DSSC devices employing the new control method. This includes the design and construction of a single turn transformer (STT), filter and all of required electronic boards to execute the control strategy. Different types of low pass filters are investigated and their capabilities are considered in selection of power topology of filter. Capacitive and inductive injection capability of the proposed controller is examined power flow control capability is demonstrated. Results obtained from the test rig are in good agreement with simulations validating the proposed controller. The experimental results of proposed controller are compared against those of traditional controller.

#### ACKNOWLEDGEMENT

First of all, I would like to thank all people who have encouraged me in pursuing this research topic and for having always supported me during the course. I am grateful to all my friends in the Power Electronics, Drives and Machines group (PEDM) at the School of Electrical and Electronic Engineering, Newcastle University. Their discussion was extremely helpful. I also take this opportunity to express my gratitude to the administrative, especially Ms. Gill Webber, and technical staffs at the school, whose have made my work as trouble-free as possible. I would like to express my appreciation to my supervisor Dr Bashar Zahawi and my examiners Dr Shady Gadoue and Dr Ahmed Khaled who provided productive comments.

I also would like to dedicate this work to my parents, who had always filled up my memory with their sweetest love. I am really missing them as well as their encouragement and support in my life. They have sacrificed whatever they could in order to get me educated and understood importance of lifetime study. Without bearing that in my mind I would not be as I am nowadays.

The list of thanks would not be complete without special thanks to my brother and sisters who have always been there when I need help. Bringing me up and guiding me with their endless love, they always mean a lot to me throughout my life.

At last but not least, I would like to express my deep gratitude to my beloved wife and my dearest son for their patience with the time spent away from them, their love and support throughout the work. Thank you, Sara, because I could not have finished the writing without your support and love. Thank you, Aryaz, for being my joy and motivation of my life.

Newcastle University, May of 2015 Afshin Pashaei

#### **List of Symbols**

w Angular frequency

B Flux density

H Magnetic field strength

μ Magnetic permeability

Hz Hertz

kN Kilo neton

lb Pound

$\Omega$  Ohm

P<sub>w</sub> Horizontal force of wind

X<sub>L</sub> Line reactance

V<sub>s</sub> rms value of sending end bus voltage

V<sub>r</sub> rms value of receiving end bus voltage

P<sub>sr</sub> Receiving end power

$\delta$  Load angle

X<sub>ini</sub> Injected reactance

K Boost Factor

X<sub>C</sub> Reactance of TCSC device capacitor

X<sub>TCSC</sub> Effective reactance of TCSC

$\lambda$  Root square  $X_C$  divided by  $X_L$

β Firing advance angle

i<sub>L</sub> Line current

DC Link Electrical node across the DC capacitor

$V_{inj}$  Phasor of injected voltage

$I_l$  Phasor of line current

$V_{injp}$  Direct component of  $V_{inj}$

$V_{injq}$  Quadrature component of Vinj

α Phase angle between injected voltage and line current

Q<sub>sr</sub> Receiving end reactive power

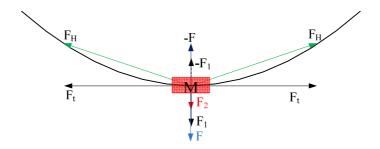

F<sub>2</sub> Generated force by mass of DSSC module

F<sub>1</sub> Generated force by mass of line

F Sum of two forces  $F_1$  and  $F_2$

F<sub>H</sub> Generates force by line

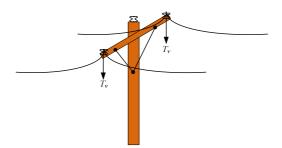

T<sub>v</sub> Vertical load on the cross-arm

$W_w$  Weight of wire

il Cross section of ice load

dw Cross section of wire

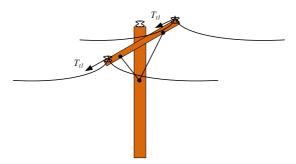

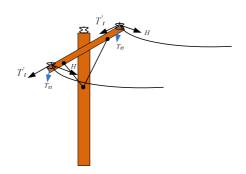

$T_{tl}$  Horizontal force of wind

$P_w$  Wind pressure

$S_w$  Effective length of the span

$T_{t2}$  Resultant horizontal force

H<sub>ten</sub> Horizontal tension

L<sub>min</sub> Minimum distance between line and pole

PC Minimum distance between two phases

F<sub>v</sub> Vertical force on to the pole

$S_1$  Length of span

F<sub>WH</sub> Horizontal force generated by the wind

W<sub>mf</sub> Maximum wind force through one meter of wire

ρ Parameter defined by environmental parameters

$V_d$  d component of the reference signal  $V_q$  q component of the reference signal

I<sub>dcref</sub> Reference dc current

I<sub>dc</sub> Measured DC current

K<sub>c</sub> Percentage of the compensation

$L_{XS}$  Inductances of the line at the sending end bus

L<sub>RS</sub> Inductances of the line at the receiving end bus

I<sub>abc</sub> Amplitude of current in three phases

I<sub>d</sub> Direct component of line current

I<sub>q</sub> Quadrature component of line current

V<sub>dc</sub> Voltage across the dc link

V<sub>Ave</sub> Average voltage

$\theta_{dc}$  Angle needed for adjustment of dc voltage

$\theta_{an}$  From the PLL

$V_{\text{Cinj}}$  Calculated capacitive compensation voltage

V<sub>Linj</sub> Calculated inductive compensation voltage

p(t) Instantaneous power

$V(t)_{Inj}$  Instantaneous injected voltage

I(t) Line Instantaneous line current

I<sub>CE</sub> Current flowing from collector to emitter

V<sub>CE</sub> Voltage across collector emitter

V<sub>GE</sub> Voltage across gate emitter

Wt Withstand time

$R_{G}$  Resistor between the gate drive and IGBT

Ipeak Maximum peak output current of gate drive

Re External resistor

V<sub>PN</sub> Input voltage of transducer

V<sub>PN</sub> Measured current at the primary of transducer

$\mathcal{R}$  Reluctance

r Thickness of the corel Length of the cylinder

N Number of turns of the winding around the core

A Net cross-sectional area of the core

f<sub>c</sub> Cut off frequency

vr Percentage of the ripple on dc voltage

$V_{drop}$  Voltage drop across a segment of line

#### **Abbreviations**

DSSC Distributed static series compensator

FACTS Flexible AC transmission system

UPFC Unified Power Flow Controller

STATCOM Static Synchronous Compensator

SVC Static VAR Compensator

ATC Available Transmission Capacity

SSR Sub-synchronous resonance

SSSC Static synchronous series compensators

STT Single turn transformer

MVAr Mega var

MOV Metal Oxide Varistor

SCL Short circuit level

TSSC Thyristor Switched Series Capacitors

TCSC Thyristor Controlled Series Compensation

GCSC GTO Thyristor-Controlled Series Capacitor

GTO Gate turn off Thyristor

IGBT Insulated Gate Bipolar Transistors

TSC Thyrsitor switched capacitor

SVC Static VAr Compensators

SVS Synchronous Voltage Source

VSC Voltage Source Converter

SSSC Static Synchronous Series Compensation

SSR Sub-Synchronous Resonance

DSPS Distributed static phase shifter

MTTR Mean time to repair

D-FACTS Distributed flexible AC transmission system

ACSR Aluminium-conductor steel-reinforced

MCP Maximum Conductor Pressure

MCW Maximum Conductor Weight

AAAC All Aluminium Alloy Conductors

CSI Current source inverter

PWM Pulse width modulation

PLL Phase locked loop

TOV Transient Over Voltage

VT Voltage transducer

PCB Printed circuit board

Op-amp Operational amplifier

CT Current Transducer

EMF Electromechanical force

DMA Direct Memory Access

ADC Analogue to Digital Converter

RAM Read access memory

CPU Central processing unit

I/O Input output

MW Mega watt

VA Volt amper

MVA Mega volt amper

UG lab Upper ground lab

## **Table of tables**

| TABLE 2.1: P OR Q AND THE CORRESPONDING CONVENTION                | 43  |

|-------------------------------------------------------------------|-----|

| TABLE 3.1: TYPICAL BARE CONDUCTORS IN AN 11KV DISTRIBUTION SYSTEM | 84  |

| TABLE 3.2: SUMMARY OF PARAMETERS AND CORRESPONDING VALUES         | 84  |

| TABLE 3.3: SYSTEM PARAMETERS FOR TWO PARALLEL LINES               | 84  |

| TABLE 4.1: SYSTEM PARAMETERS                                      | 103 |

| TABLE 4.2: CRITERIA IN ZERO/POLE PLACEMENT                        | 104 |

| TABLE 4.3: PARAMETERS FOR THE EMPLOYED LOW PASS FILTER            | 112 |

| TABLE 4.4: SYSTEM PARAMETERS                                      | 114 |

| TABLE 4.5: DSSC DEVICE PARAMETERS                                 | 115 |

| TABLE 4.6: SYSTEM PARAMETERS                                      | 124 |

| TABLE 4.7: SUMMERY OF POWER LOSS AND PHASE ANGLE STUDY            | 128 |

| TABLE 4.8: CONTROL PARAMETERS                                     | 140 |

| TABLE 4.10: REQUIREMENTS FOR THE DESIGNED CONTROLLER              | 154 |

| TABLE 4.11: PARAMETERS OF PI CONTROLLER                           | 156 |

| TABLE 4.12: SUMMARIZED RESULTS OF FURTHER TUNED CONVENTIONAL      | AND |

| PROPOSED CONTROLLER                                               | 169 |

| TABLE 5.1: TYPICAL LINE PARAMETERS IN AN 11KV DISTRIBUTION SYSTEM | 215 |

| TABLE 5.2: SUMMARY OF TRANSFORMER DESIGN                          | 218 |

| TABLE 5.3: SUMMERY OF DESIGN VALUE                                | 224 |

| TARLE 5.4: EXPERIMENTAL RESULTS FOR BOTH CONTROL METHODS          | 229 |

# Table of figures

| FIG.2.1: DIFFERENT TYPE OF COMPENSATION                                | 28       |

|------------------------------------------------------------------------|----------|

| FIG.2.2: SVS SHUNT COMPENSATION                                        | 30       |

| FIG.2.3: VOLTAGE SOURCE CONVERTER                                      | 30       |

| FIG.2.4: OUTPUT VOLTAGE                                                | 31       |

| FIG.2.5: TWO BUS POWER SYSTEM                                          | 32       |

| FIG.2.6: POWER TRANSMISSION VERSUS THE PHASE ANGLE WITH DIFFERENT      | AMOUNT   |

| OF COMPENSATION                                                        | 32       |

| FIG.2.7: LINE POWER-VOLTAGE CHARACTERISTICS                            | 33       |

| FIG.2.8: COMPENSATION OF LINE REACTANCE                                | 33       |

| FIG.2.9: TWO POSSIBLE SOLUTIONS FOR TRANSMITTING 2000 MW               | 34       |

| FIG.2.10: POWER TOPOLOGIES FOR SERIES CAPACITOR CONNECTION             | 35       |

| FIG.2.11: POWER TOPOLOGY OF TSSC                                       | 36       |

| FIG.2.12: NUMBER OF TSSC UNITS WHICH ARE CONNECTED IN SERIES           | 37       |

| FIG.2.13: THE EFFECTS OF TSSC ON POWER VERSUS ANGLE                    |          |

| FIG.2.14: POWER TOPOLOGY OF TCSC                                       | 37       |

| FIG.2.15: SERIES CONNECTION OF TCSC                                    | 38       |

| FIG.2.16: LINE CURRENT, CAPACITOR VOLTAGE AND REACTOR CURRENT          | 39       |

| FIG.2.17: BOOST FACTOR K VERSUS B; OPERATION OF TCSC IN CAPACIT        | IVE AND  |

| INDUCTIVE BOOST MODE                                                   | 40       |

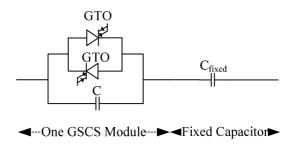

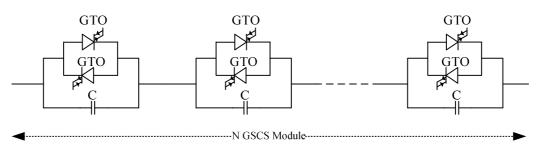

| FIG.2.18: GTO THYRISTOR-CONTROLLED SERIES CAPACITOR                    | 40       |

| FIG.2.19: GCSC SERIES WITH A FIXED CAPACITOR                           | 41       |

| FIG.2.20: NUMBERS OF GCSC CONNECTED IN SERIES                          | 41       |

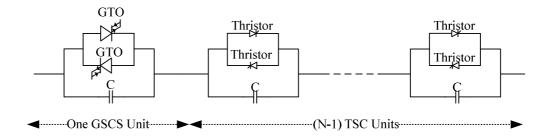

| FIG.2.21: COMBINATION OF NUMBER OF TSC AND A GCSC                      | 41       |

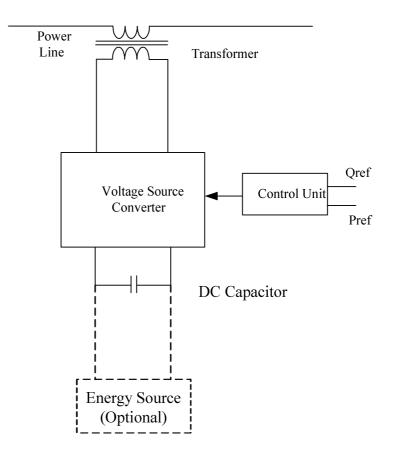

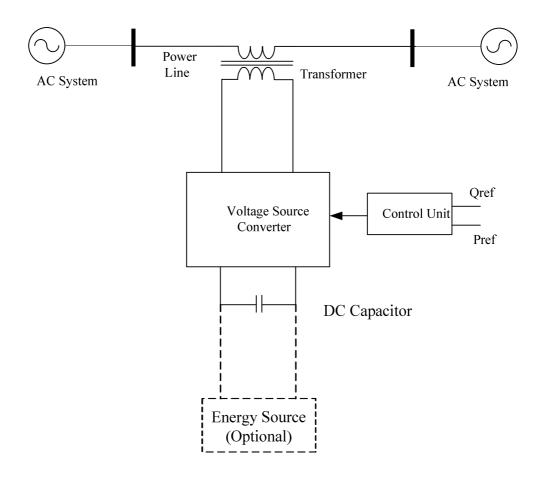

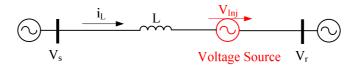

| FIG.2.22: VSC CONNECTED IN SERIES WITH THE POWER LINE (SERIES COMPENSA | TION).42 |

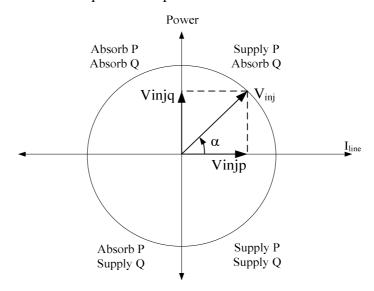

| FIG.2.23: THE OPERATION OF VSC IN SERIES COMPENSATION APPLICATIONS     | 43       |

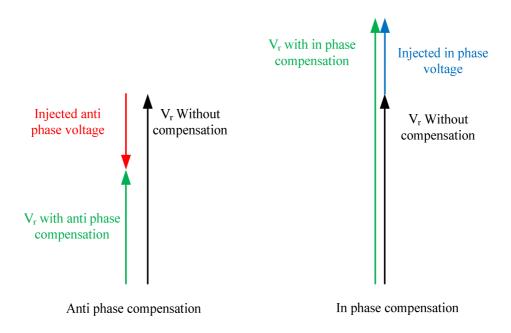

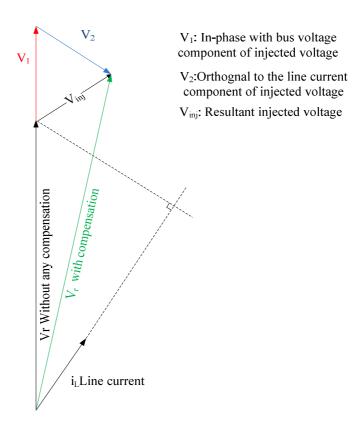

| FIG.2.24: REGULATING BUS VOLTAGE BY VSC BASED COMPENSATOR              | 44       |

| FIG.2.25: IN-PHASE AND ANTI-PHASE (WITH RESPECT TO THE BUS VOLTAGE)    | VOLTAGE  |

| INJECTION                                                              | 45       |

| FIG.2.26: CIRCUIT REPRESENTATION OF THE INJECTION                      | 45       |

| FIG.2.27: COMPENSATING LINE VOLTAGE DROPS                              | 46       |

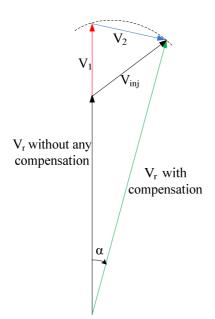

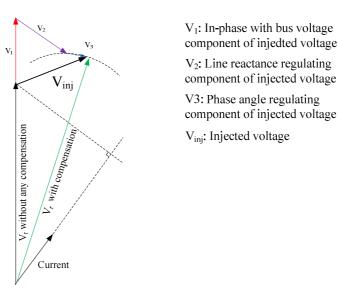

| FIG.2.28: COMPENSATION OF VOLTAGE DROP AND REGULATING THE PHASE AND    | GLE47    |

| FIG.2.29: REGULATING BUS VOLTAGE, LINE REACTANCE AND LOAD              | ANGLE    |

| REGULATION                                                             | 47       |

| FIG.2.30: SSSC BLOCK DIAGRAM                                           | 48       |

| FIG.2.31: A TWO BUS POWER SYSTEM WITH COMPENSATED LINE                 | 49       |

| FIG.2.32: PHASOR DIAGRAM OF THE SENDING END AND RECEIVING END VOLTA    | GES AND  |

| THE INJECTED VOLTAGE                                                   | 49       |

| FIG.2.33: SCHEME INTRODUCED BY HINGORANI                               | 50       |

| FIG.2.34: THE POSSIBLE INJECTION ANGLES TO GENERATE VIRTUAL CAPACIT    | ANCE OR  |

| INDUCTANCE                                                             | 52       |

| SYSTEM                                                                 |

|------------------------------------------------------------------------|

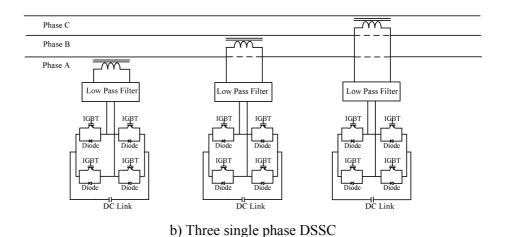

| FIG.2.36: DISTRIBUTED STATIC SERIES COMPENSATION (DSSC)                |

| FIG.2.37: EXAMPLE LINE REACTANCE PROFILE                               |

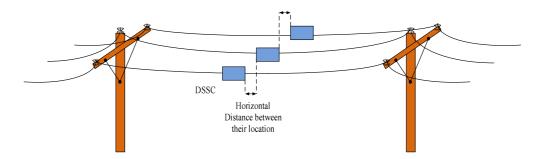

| FIG.2.38: A DISTRIBUTION LINE WITH SUSPENDED DSSC THROUGH THE LINE56   |

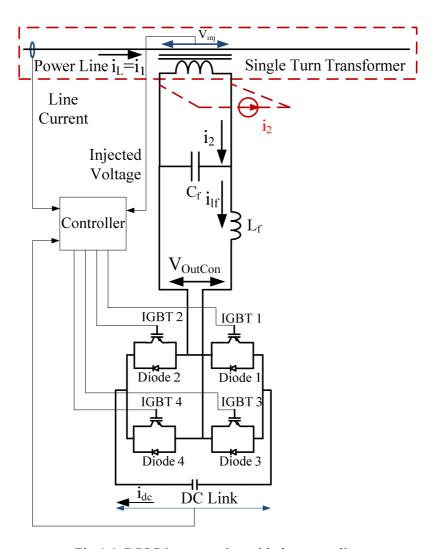

| FIG.2.39: CIRCUIT SCHEMATIC OF DSSC                                    |

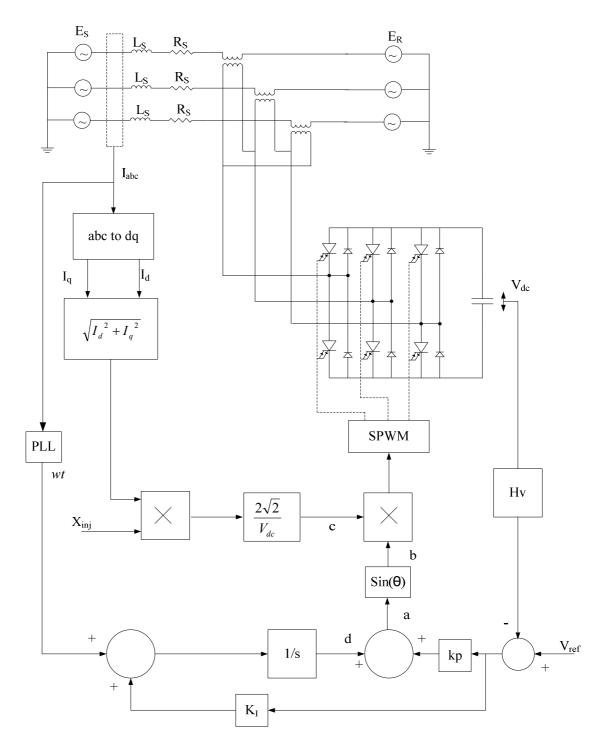

| FIG.2.40: CONTROL BLOCK DIAGRAM FOR GENERATING THE REFERENCE SIGNAL60  |

| FIG.2.41: BLOCK DIAGRAM OF DQ BASED CONTROLLER                         |

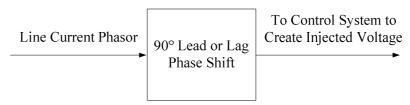

| FIG.2.42: SHIFTING LINE CURRENT                                        |

| FIG.2.43: LINE CURRENT SHIFTED ± 90 DEGREE                             |

| FIG.2.44: CONTROL BLOCK DIAGRAM OF SSSC USING 90 DEGREE PHASE SHIFT66  |

| FIG.2.45: DQ CONVERSION OF A BALANCED THREE-PHASE SYSTEM               |

| FIG.2.46: ABC TO DQ CONVERSION OF UNBALANCE THREE-PHASE SYSTEM68       |

| FIG.2.47: CONVERSION FROM ABC TO DQ AND FROM DQ TO ABC IN AN UNBALANCE |

| THREE-PHASE SYSTEM69                                                   |

| FIG.2.48: ABC TO DQ CONVERSION IN AN UNBALANCED SYSTEM69               |

| FIG.2.49: ABC TO DQ CONVERSION IN AN UNBALANCED SYSTEM SPANNED THROUGH |

| THE TIME AXIS70                                                        |

| FIG.2.50: THE ANGLE BETWEEN THE "D" AND "Q" COMPONENTS IN AN UNBALANCE |

| SYSTEM71                                                               |

| FIG.2.51: CONVERSION FROM ABC TO DQ AND FROM DQ TO A1B1C171            |

| FIG.2.52: BLOCK DIAGRAM OF DECOMPOSITION OF AN UNBALANCE SYSTEM AND    |

| APPLYING DQ CONVERSION72                                               |

| FIG.2.53: CONVERSION OF COMBINATION OF POSITIVE AND NEGATIVE SIGNAL73  |

| FIG.2.54: POSITIVE SEQUENCE AND FINAL CONVERTED WAVEFORM74             |

| FIG.2.55:PHASE ANGLE DIFFERENCE BETWEEN THE POSITIVE SEQUENCES AND THE |

| FINAL CONVERTED WAVEFORM74                                             |

| FIG.2.56: BLOCK DIAGRAM OF THE PHASE LOCKED LOOP (PLL)                 |

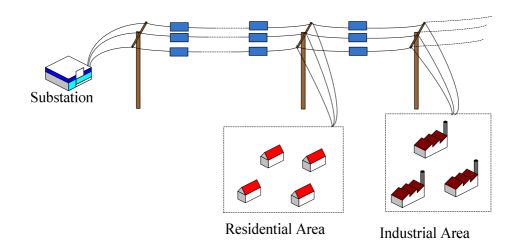

| FIG.3.1: APPLICATION OF DSSC IN ELECTRICAL DISTRIBUTION NETWORKS78     |

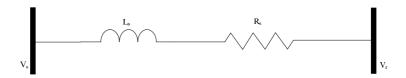

| FIG.3.2: TWO BUS AC POWER SYSTEM79                                     |

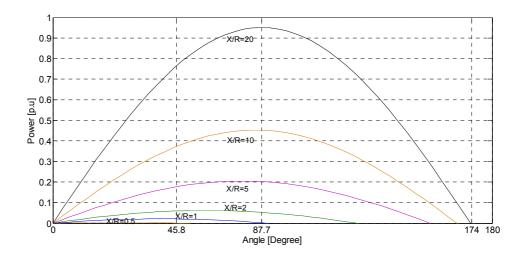

| FIG.3.3: EFFECT OF X/R RATIO ON THE TRANSMITTED POWER                  |

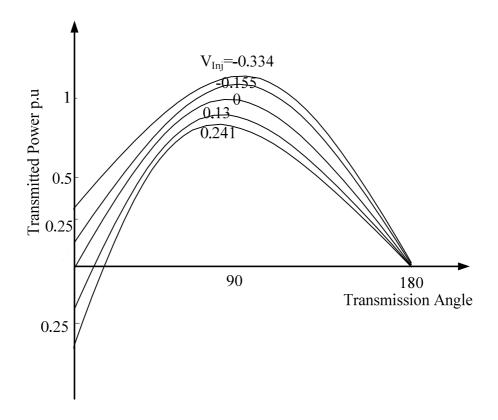

| FIG.3.4: COMPENSATED AC POWER SYSTEM81                                 |

| FIG.3.5: CHANGE OF TRANSMITTED POWER AGAINST TRANSMISSION ANGLE82      |

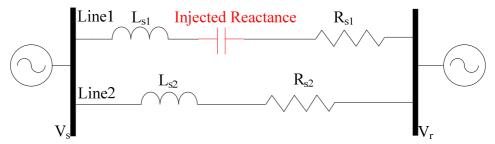

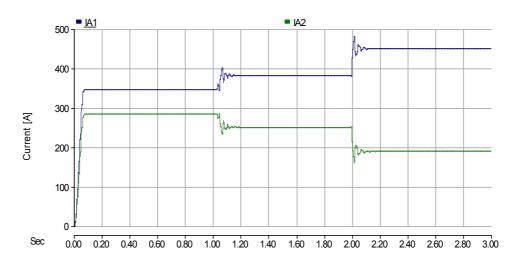

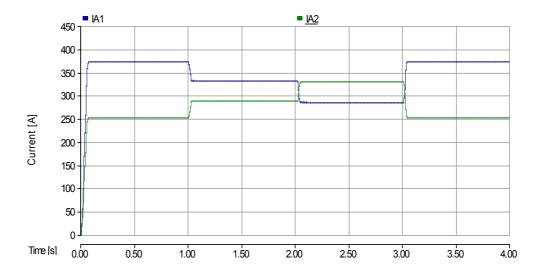

| FIG.3.6: COMPENSATION OF TWO PARALLEL LINES85                          |

| FIG.3.7: PHASE CURRENT WITH DIFFERENT LEVEL OF COMPENSATION85          |

| FIG.3.8: RMS VALUE OF LINES CURRENT IN PRESENCE OF INDUCTIVE INJECTION |

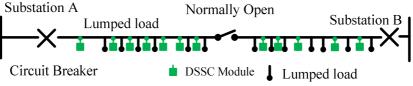

| FIG.3.9: 11KV LOOP DISTRIBUTION NETWORK INCLUDING DSSC DEVICES87       |

| FIG.3.10: THE MODEL OF FEEDER EQUIPPED WITH THE DSSC MODULE            |

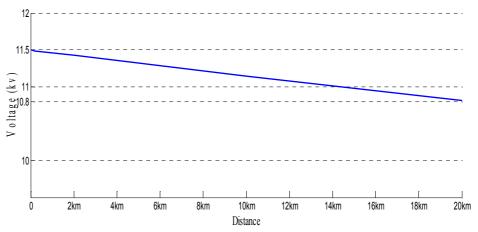

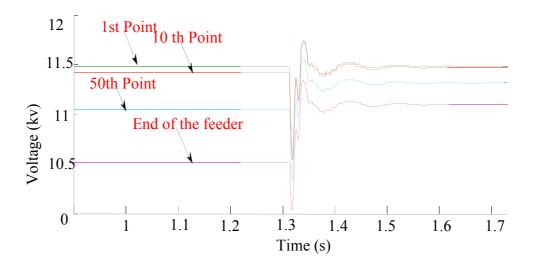

| FIG.3.11: FEEDER VOLTAGE PROFILE BEFORE COMPENSATION89                 |

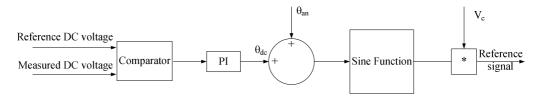

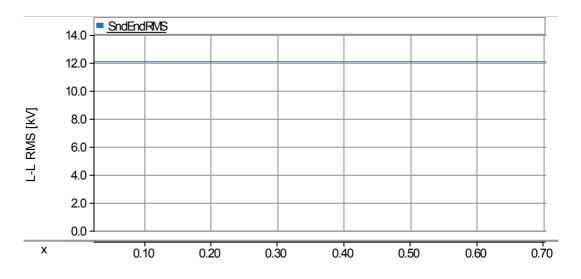

| FIG.3.12: VOLTAGES AT DIFFERENT DISTANCES ALONG THE FEEDER90           |

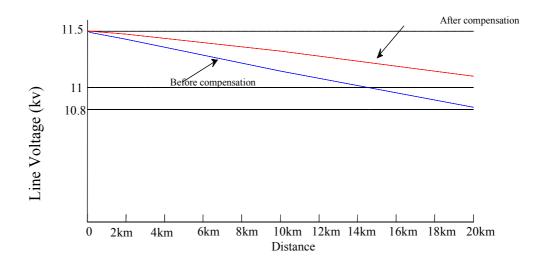

| FIG.3.13: FEEDER VOLTAGE PROFILE AFTER COMPENSATION90                  |

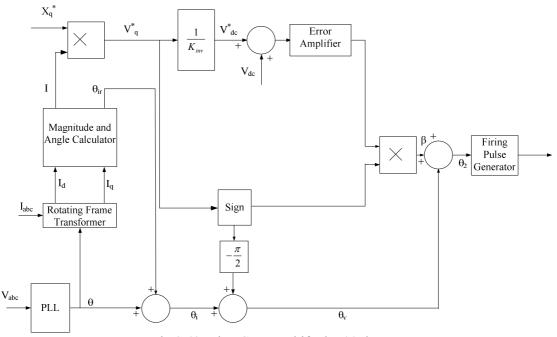

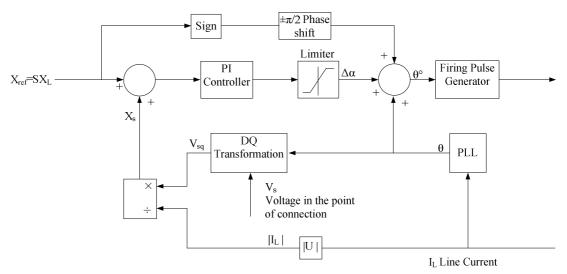

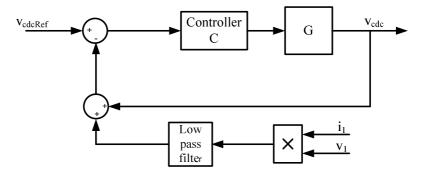

| FIG.4.1: CONTROL BLOCK DIAGRAM OF DC VOLTAGE REGULATING               | 92        |

|-----------------------------------------------------------------------|-----------|

| FIG.4.2: INJECTION PHASE ANGLE REGULATION CONTROL BLOCK DIAGRAM       | 95        |

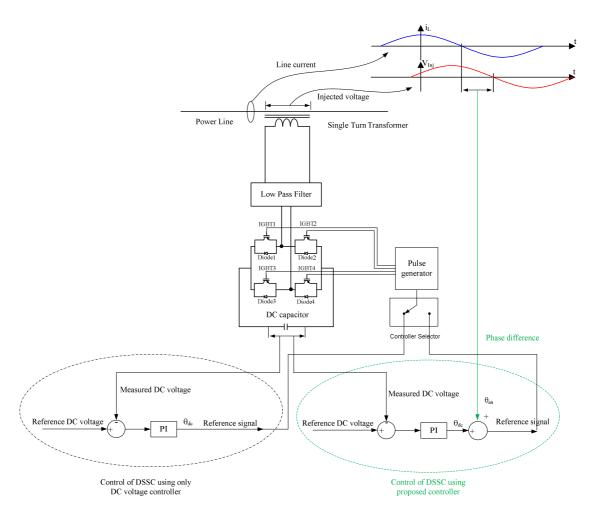

| FIG.4.3: BLOCK DIAGRAM OF THE PROPOSED CONTROLLER                     | 96        |

| FIG.4.4: MULTIPLICATION OF "LINE CURRENT SIGNAL" AND "INJECTED VOLTAG | E" 96     |

| FIG.4.5: DEPENDENCY OF ACTIVE POWER ABSORPTION ON THE PHASE A         | NGLE OF   |

| INJECTED VOLTAGE                                                      | 97        |

| FIG.4.6: DSSC IN CONNECTION WITH THE POWER LINE                       | 99        |

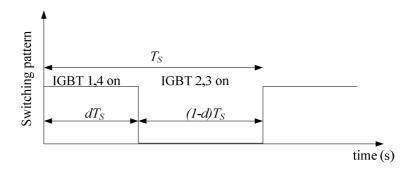

| FIG.4.7: TIMING DIAGRAM OF SWITCHING PULSES OF IGBT'S                 | 100       |

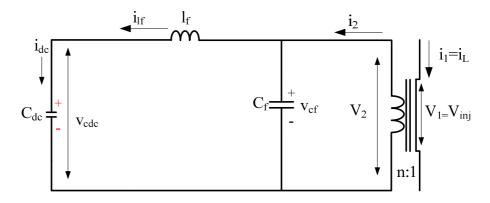

| FIG.4.8: EQUIVALENT CIRCUIT IN MODE 1                                 | 100       |

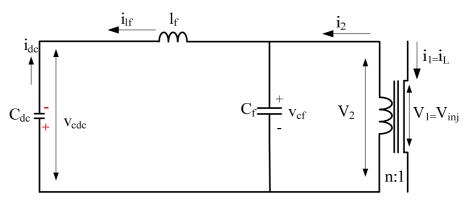

| FIG.4.9: EQUIVALENT CIRCUIT IN MODE 2                                 | 101       |

| FIG.4.10: BLOCK DIAGRAM OF CONTROL STRATEGY                           | 102       |

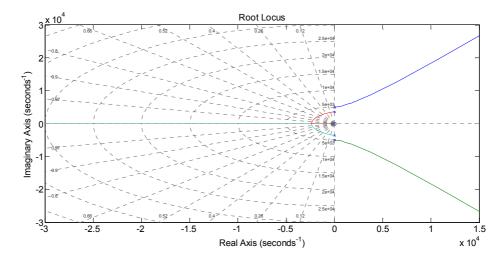

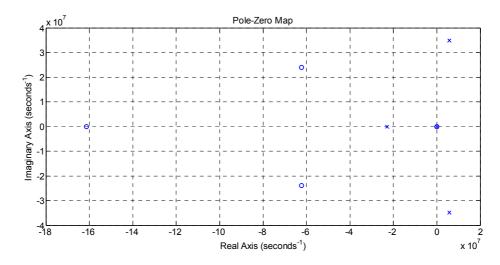

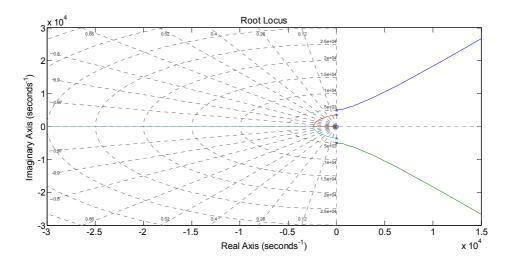

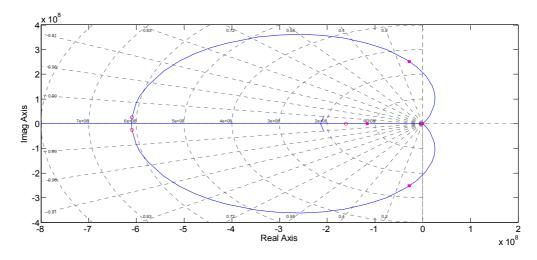

| FIG.4.11: ROOT LOCUS DIAGRAM OF THE TRANSFER FUNCTION G               | 103       |

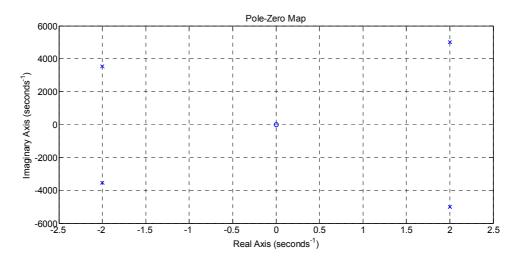

| FIG.4.12: POLES/ZEROES MAP FOR CLOSED LOOP SYSTEM                     | 104       |

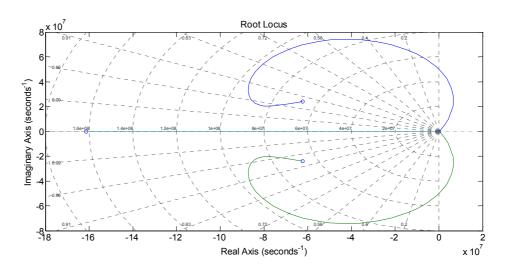

| FIG.4.13: ROOT LOCUS DIAGRAM OF THE OPEN LOOP SYSTEM INCLUDING CON    | TROLLER   |

| C                                                                     | 105       |

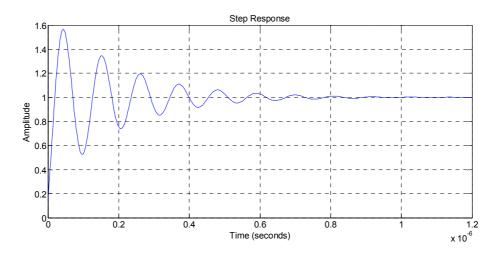

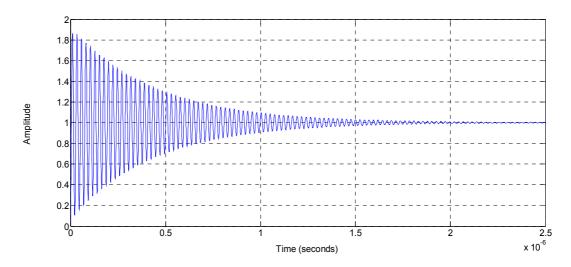

| FIG.4.14: STEP RESPONSE OF CLOSED LOOP SYSTEM WHEN GAIN OF CONTR      | OLLER IS  |

| 0.0163                                                                | 106       |

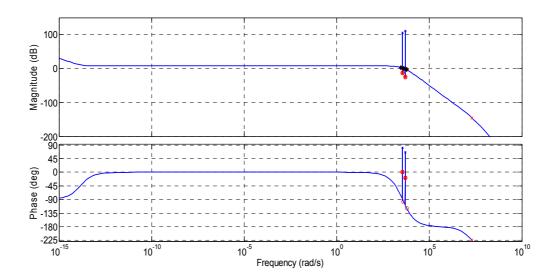

| FIG.4.15: BODE DIAGRAM OF SYSTEM                                      | 107       |

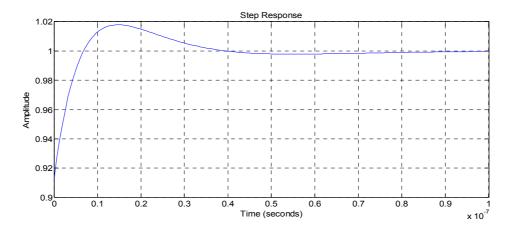

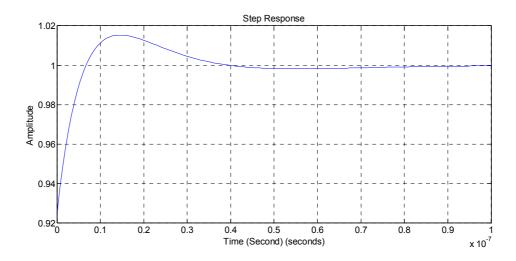

| FIG.4.16: STEP RESPONSE OF CLOSED LOOP SYSTEM MEETING OVERSHOOT       | OF 0.018% |

| AND DAMPING FACTOR OF 0.93                                            | 107       |

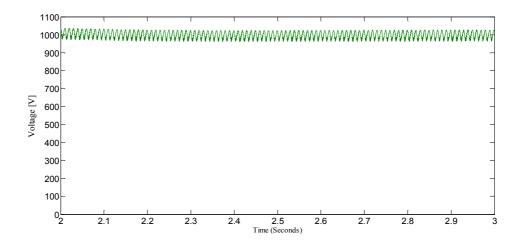

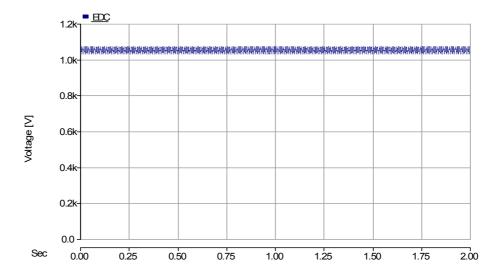

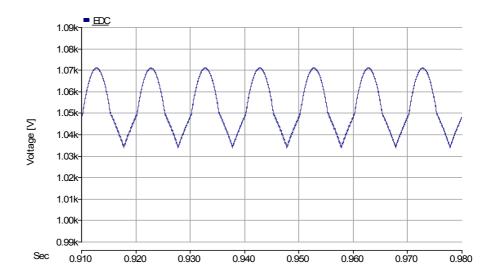

| FIG.4.17: VOLTAGE ACROSS THE DC CAPACITOR                             | 108       |

| FIG.4.18: STEP RESPONSE OF SYSTEM AFTER APPLYING 10% REDUCTION        | IN THE    |

| CAPACITANCE OF CDC                                                    | 109       |

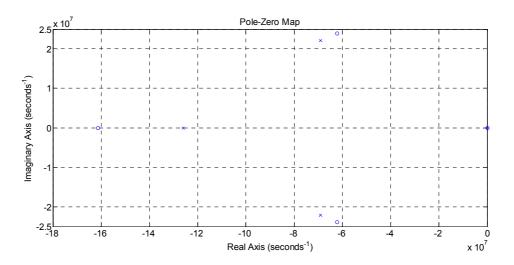

| FIG.4.19: POLE/ZERO MAP FOR A CLOSED LOOP SYSTEM AFTER APPLY          | TNG 10%   |

| REDUCTION IN THE CAPACITANCE OF CDC                                   | 109       |

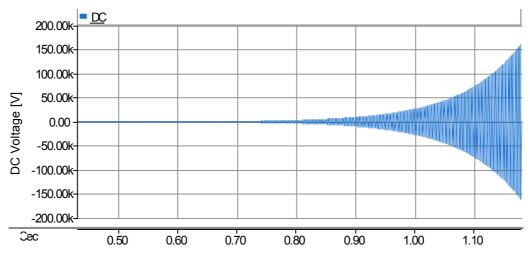

| FIG.4.20: EFFECT OF CHANGING CAPACITANCE OF CDC                       | 110       |

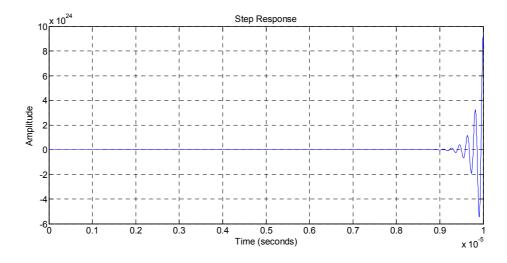

| FIG.4.21: STEP RESPONSE OF INSTABLE SYSTEM AFTER APPLYING 50% REDU    | CTION IN  |

| CAPACITANCE OF CDC                                                    | 110       |

| FIG.4.22: POLE/ZERO MAP OF CLOSED LOOP SYSTEM AFTER APPLYING 50% RE   | DUCTION   |

| IN CAPACITANCE OF CDC                                                 | 111       |

| FIG.4.23: INSTABILITY OF SYSTEM AFTER REDUCING CAPACITANCE OF CDC BY  | 50%111    |

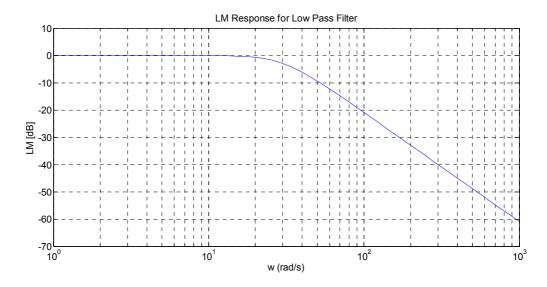

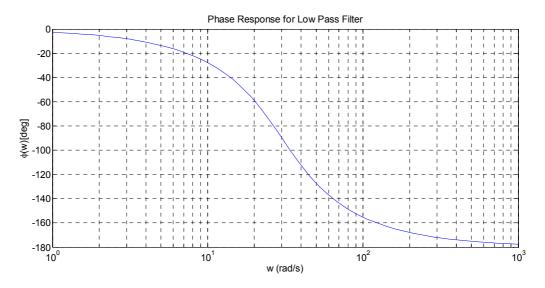

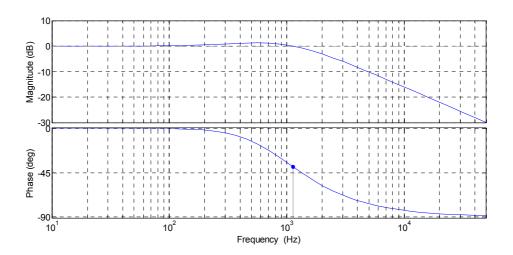

| FIG.4.24: LOGARITHMIC MAGNITUDE RESPONSE OF THE LOW PASS FILTER       | 112       |

| FIG.4.25: PHASE RESPONSE OF LOW PASS FILTER                           | 113       |

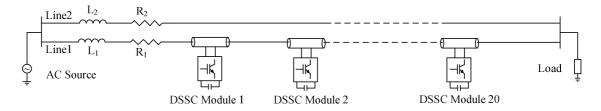

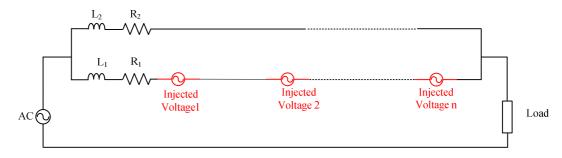

| FIG.4.26: ONE OF THE TWO FEEDERS IS EQUIPPED WITH 20 DSSC DEVICES     | 114       |

| FIG.4.27: DSSC IS SEEN AS A VSC THROUGH THE POWER LINE                | 115       |

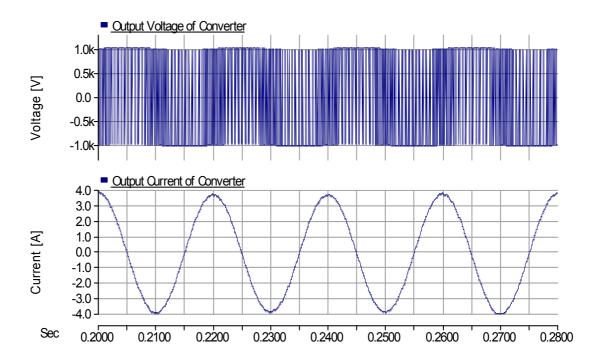

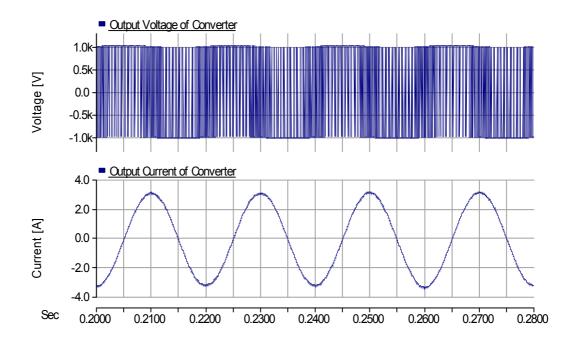

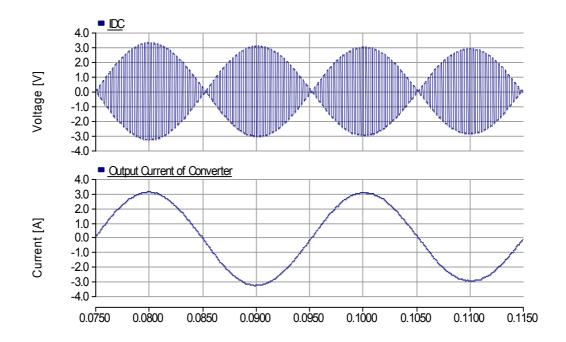

| FIG.4.28: THE OUTPUT VOLTAGE OF THE CONVERTER AND ITS INPUT CURRENT   | 116       |

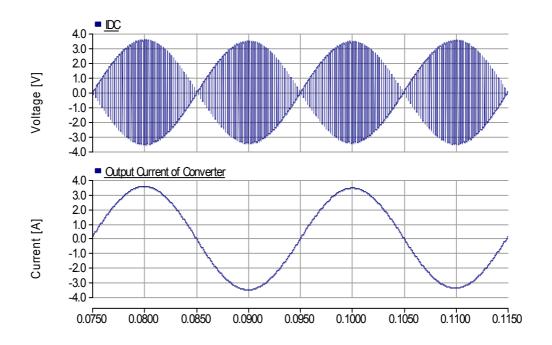

| FIG.4.29: DC LINK CURRENT AND OUTPUT CURRENT OF THE CONVERTER         | R IN THE  |

| CAPACITIVE INJECTION MODE                                             | 117       |

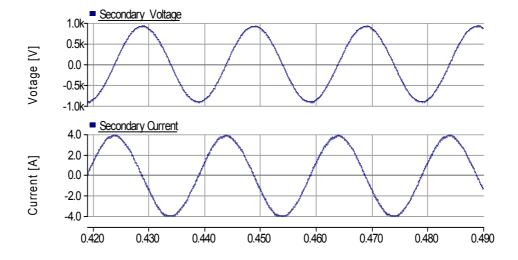

| FIG.4.30: VOLTAGE AND CURRENT IN THE POWER ELECTRONICS SIDE OF THE ST | ΓΤ IN THE |

| CAPACITIVE INJECTION MODE                                             | 117       |

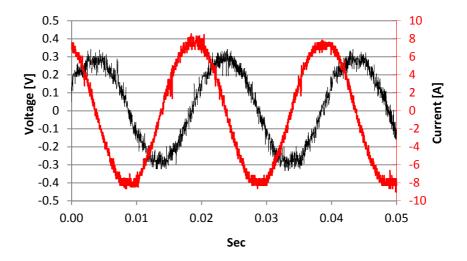

| FIG.4.31: CAPACITIVE INJECTION AND VOLTAGE IS LEADING THE CURRENT     | 118       |

| FIG.4.32: CAPACITIVE INJECTION IN THREE DIFFERENT LEVELS                | 118   |

|-------------------------------------------------------------------------|-------|

| FIG.4.33: OUTPUT VOLTAGE OF THE CONVERTER ALONG WITH THE INPUT CURRENT  | 119   |

| FIG.4.34: DC LINK CURRENT AND OUTPUT CURRENT OF THE CONVERTER IN        | THE   |

| INDUCTIVE INJECTION MODE                                                | 120   |

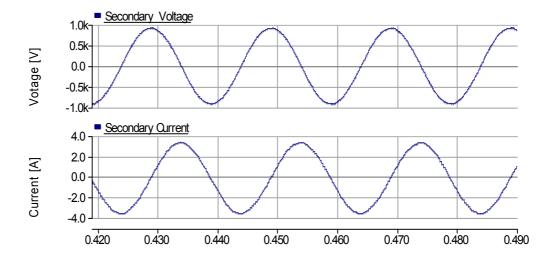

| FIG.4.35: VOLTAGE AND CURRENT IN THE SECONDARY SIDE OF THE STT IN       | THE   |

| INDUCTIVE INJECTION MODE                                                | 121   |

| FIG.4.36: INDUCTIVE INJECTION OF DSSC MODULES                           | 121   |

| FIG.4.37: DIFFERENT LEVEL OF INDUCTIVE INJECTION                        | 122   |

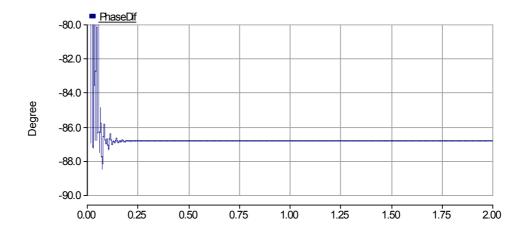

| FIG.4.38: PHASE DIFFERENCE IN CAPACITIVE INJECTION MODE USING THE 90° P | HASE  |

| SHIFT CONTROLLER                                                        | 123   |

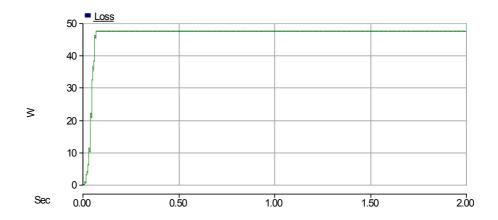

| FIG.4.39: POWER LOSS IN EACH DSSC MODULE USING THE CONVENTIONAL CON     | TROL  |

| SYSTEM                                                                  | 123   |

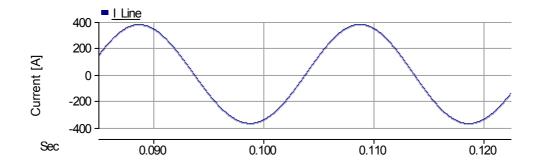

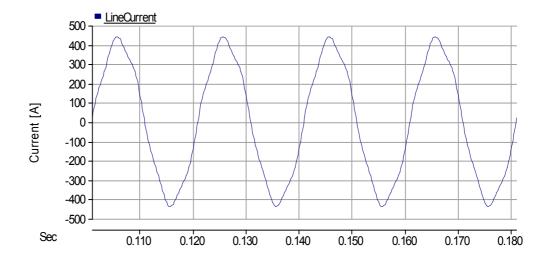

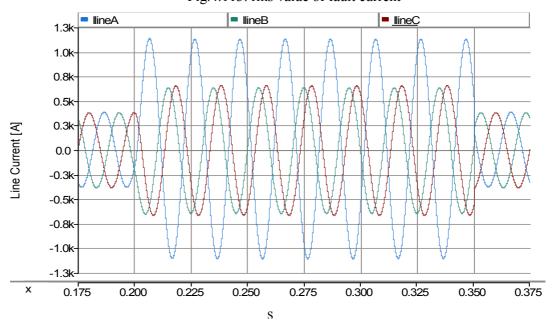

| FIG.4.40: LINE CURRENT                                                  | 124   |

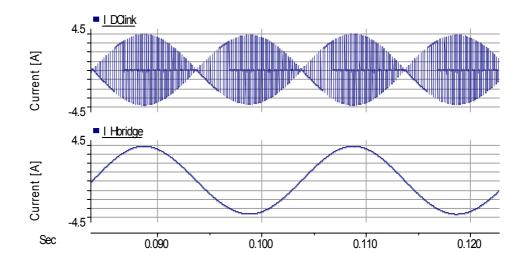

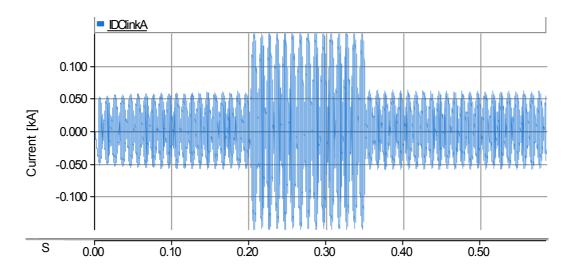

| FIG.4.41: CONVERTER CURRENT AND DC LINK CURRENT                         | 125   |

| FIG.4.42: RIPPLE OF DC VOLTAGE (WITH THE CONVENTIONAL METHOD)           | 125   |

| FIG.4.43: HARMONIC ANALYSIS OF INJECTED VOLTAGE USING THE CONVENTION    | ONAL  |

| CONTROL METHOD                                                          | 126   |

| FIG.4.44: PHASE DIFFERENCE IN CAPACITIVE INJECTION MODE USING THE PROP  | OSED  |

| CONTROLLER                                                              | 126   |

| FIG.4.45: POWER LOSS IN EACH DSSC MODULE USING THE PROPOSED CONTROL SY  | STEM  |

|                                                                         | 127   |

| FIG.4.46: RIPPLE OF DC VOLTAGE                                          |       |

| FIG.4.47: HARMONIC VOLTAGE INJECTION (USING THE PROPOSED CONTROL METHO  | D)129 |

| FIG.4.48: SYSTEM INCLUDING HARMONICS                                    | 130   |

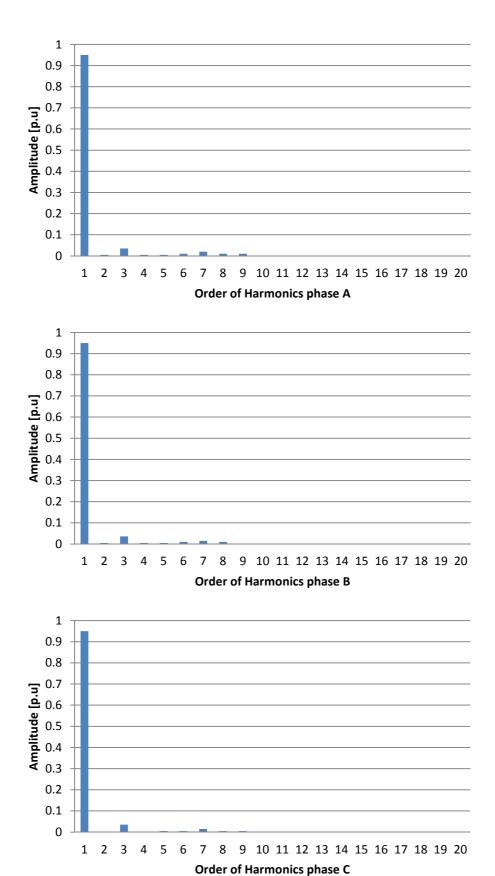

| FIG.4.49: LINE CURRENT INCLUDING 5% OF FIFTH HARMONICS                  | 130   |

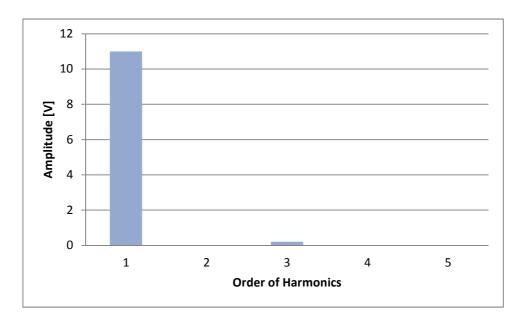

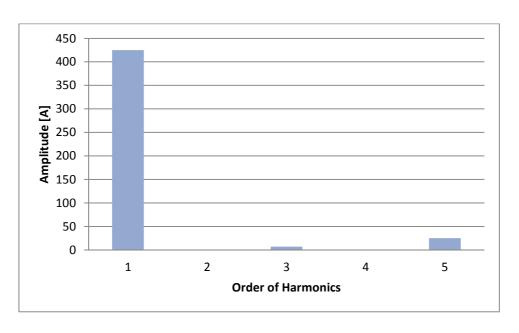

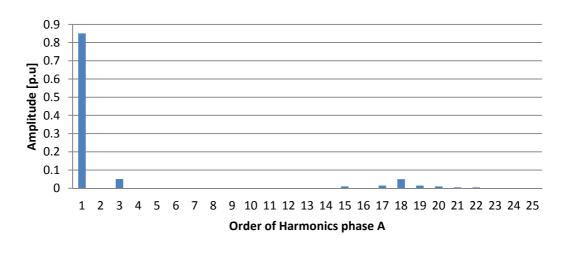

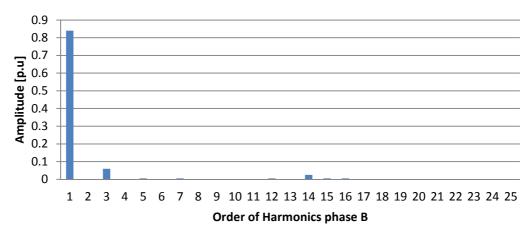

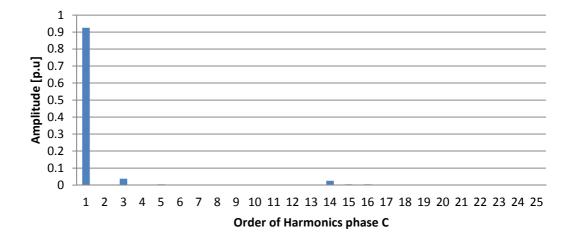

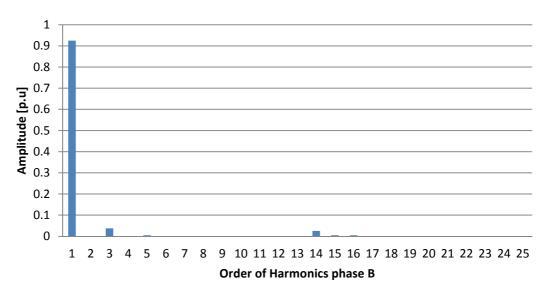

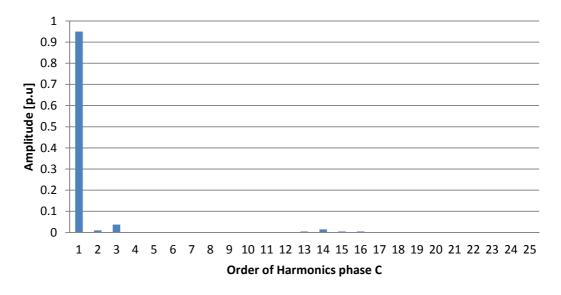

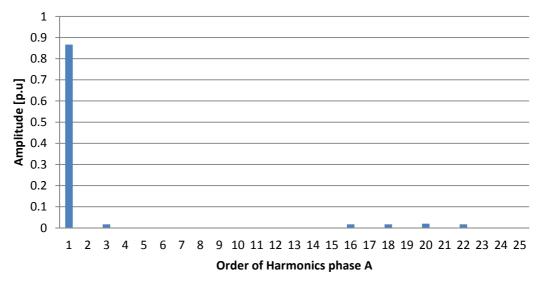

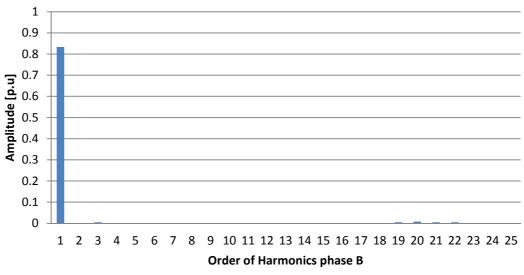

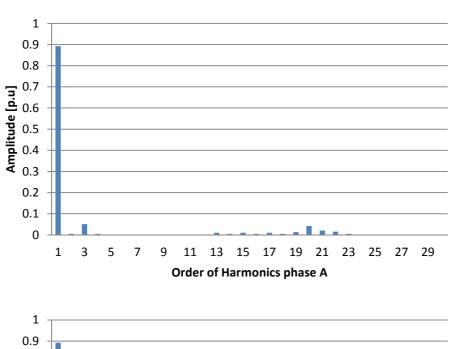

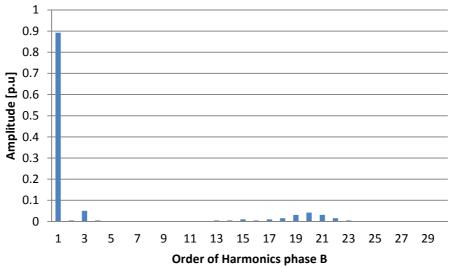

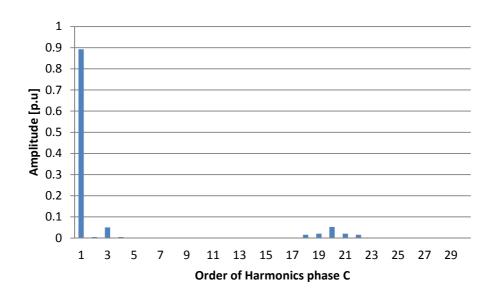

| FIG.4.50: HARMONIC ANALYSIS OF THE LINE CURRENT                         | 131   |

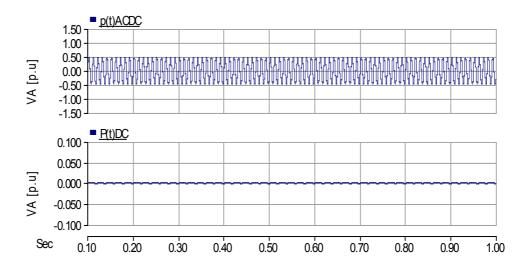

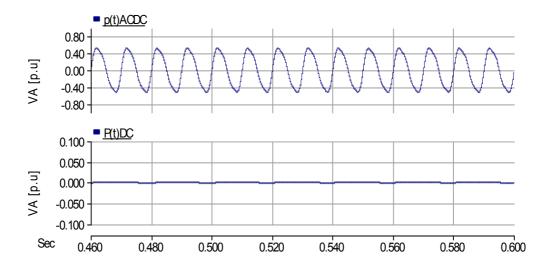

| FIG.4.51: P(T) ACDC AND P(T)DC IN PRESENCE OF 5% 5TH HARMONIC           | 131   |

| FIG.4.52: P(T)ACDC AND P(T)DC IN PRESENCE OF 5% 3RD HARMONIC AND 10%    | 5TH   |

| HARMONIC                                                                | 132   |

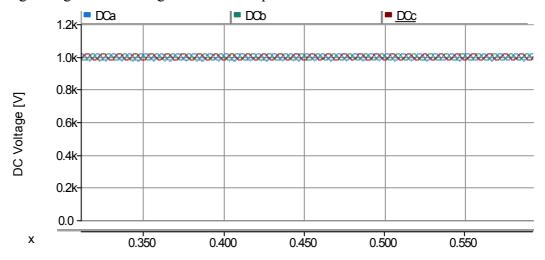

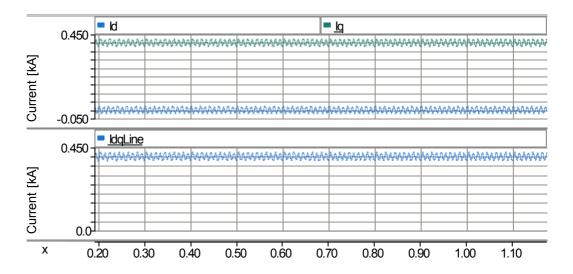

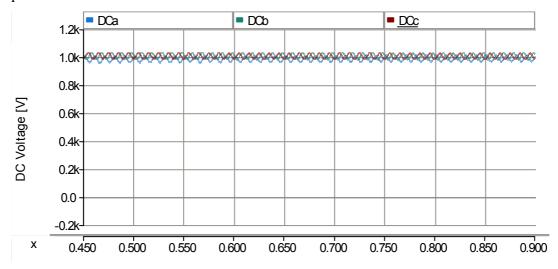

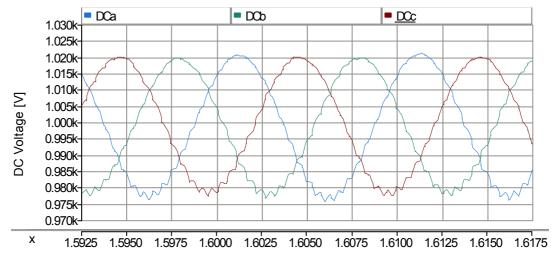

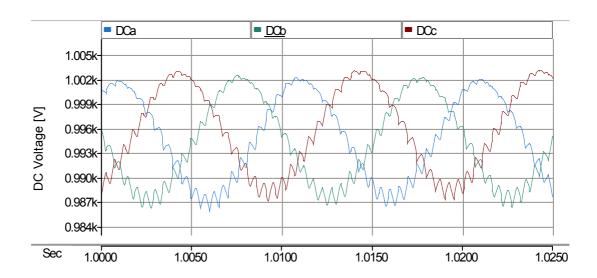

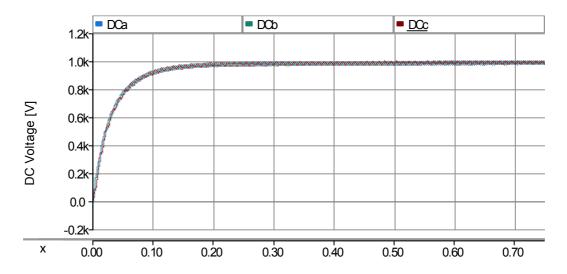

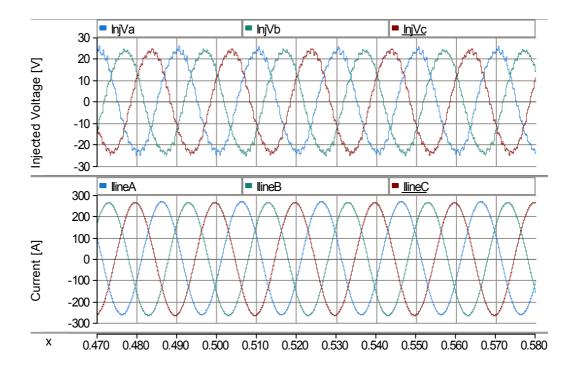

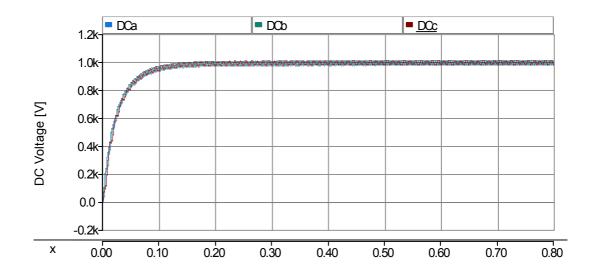

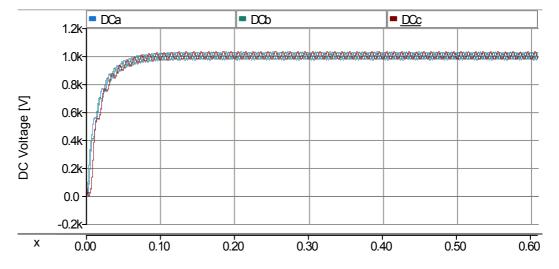

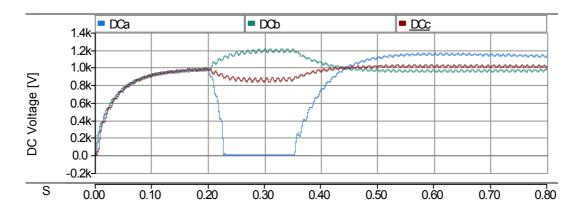

| FIG.4.53: VOLTAGE ACROSS THE DC LINK WITHIN DSSC MODULES EMPLOYED IN T  | HREE  |

| DIFFERENT PHASES                                                        | 133   |

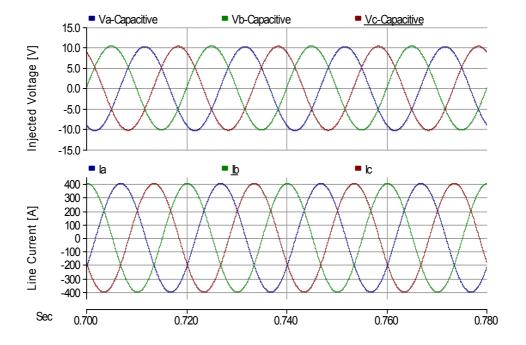

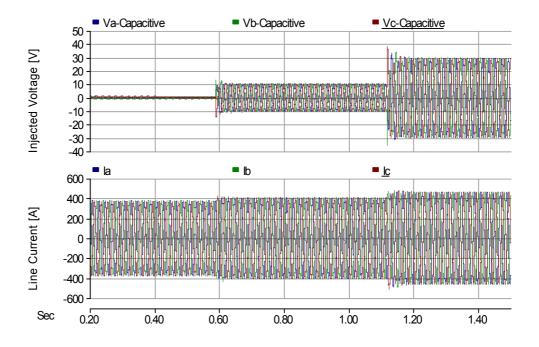

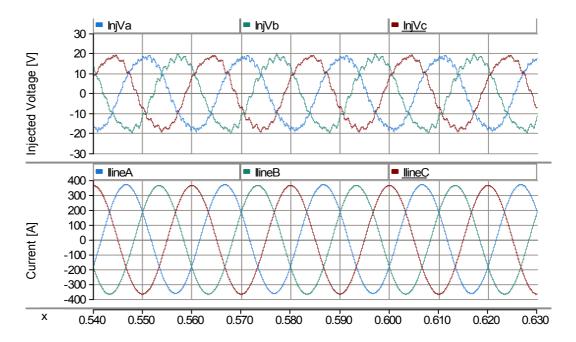

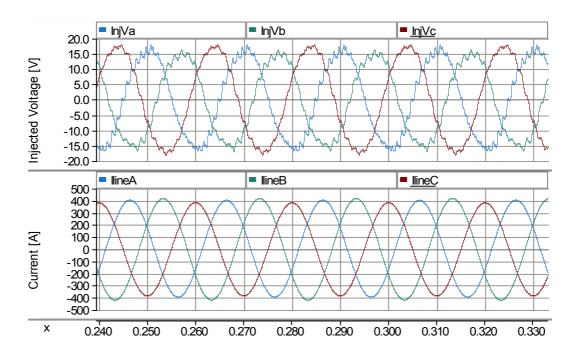

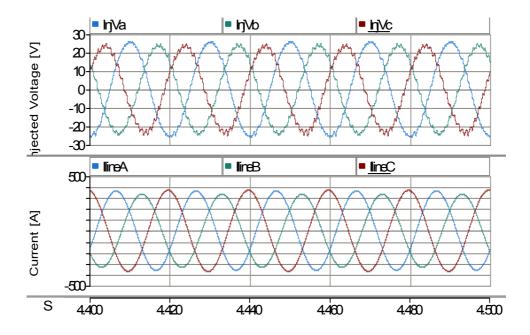

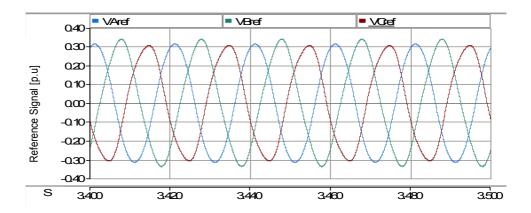

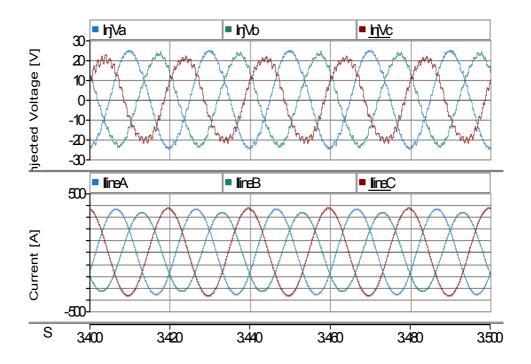

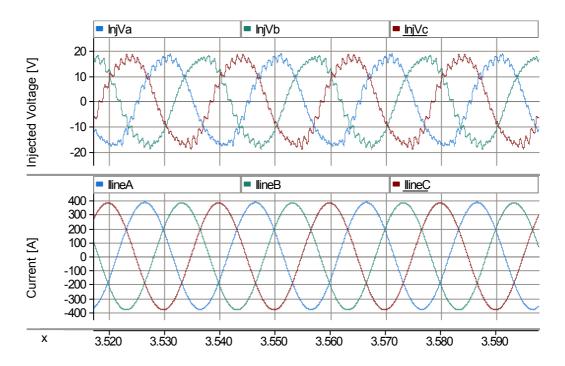

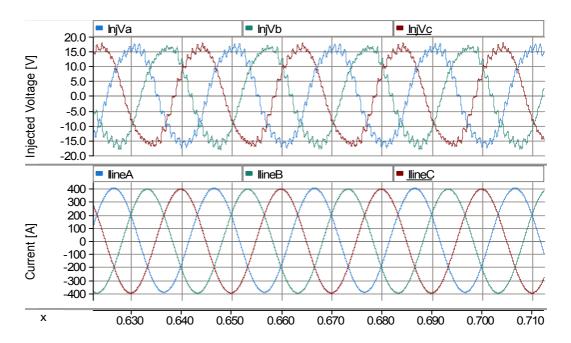

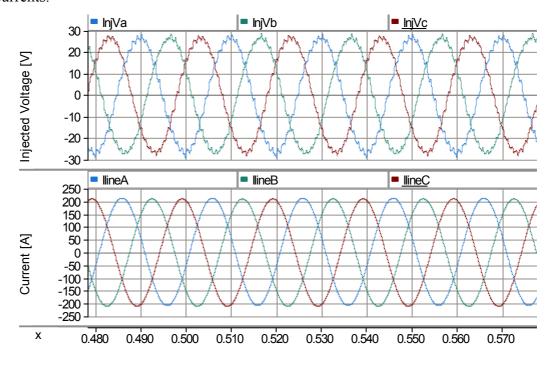

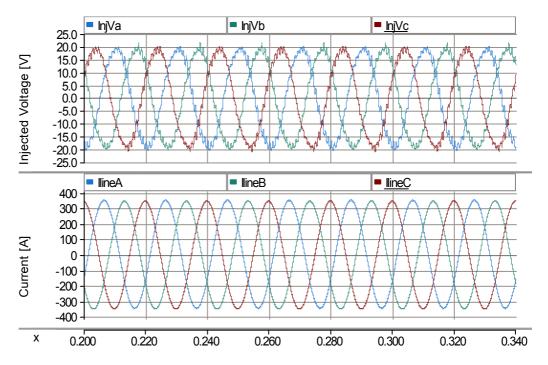

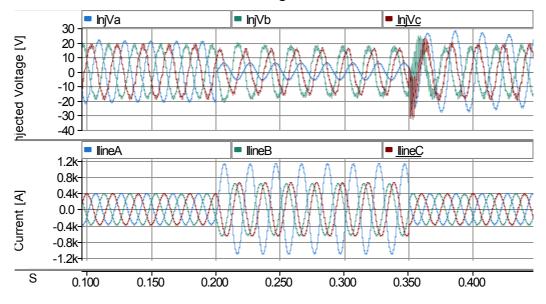

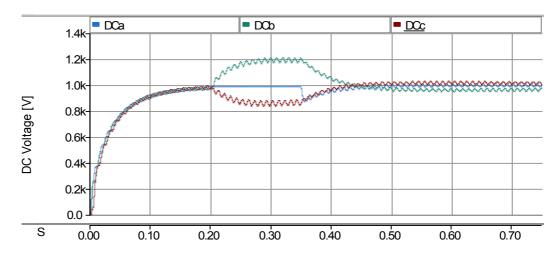

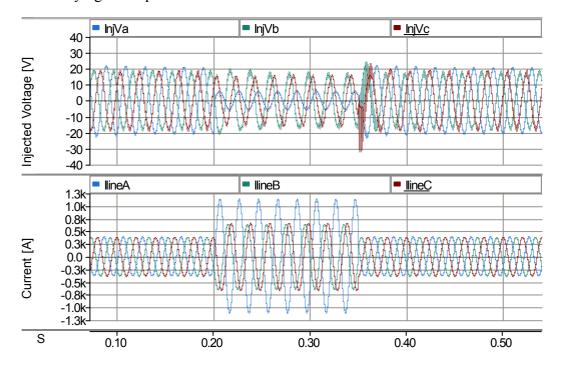

| FIG.4.54: INJECTED VOLTAGES BY DSSC DEVICES IN EACH PHASE AND THREE P   | HASE  |

| LINE CURRENTS                                                           | 134   |

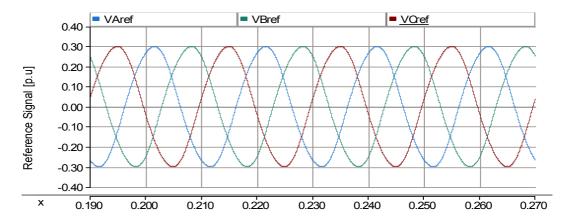

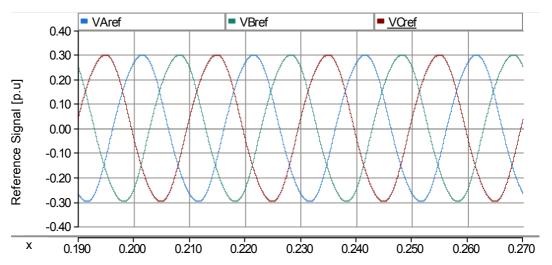

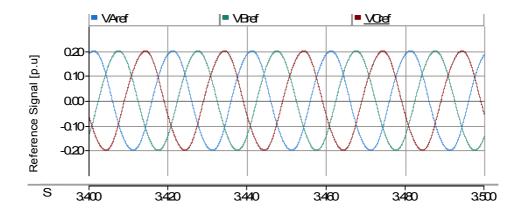

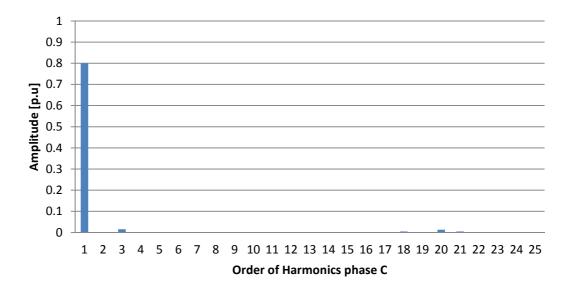

| FIG.4.55: REFERENCE SIGNALS OF INJECTED VOLTAGES PROVIDED BY EACH       | DSSC  |

| MODULES SEPARATELY                                                      | 134   |

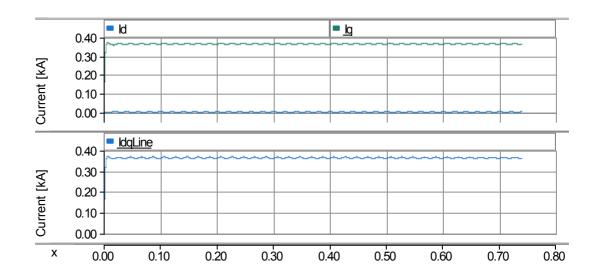

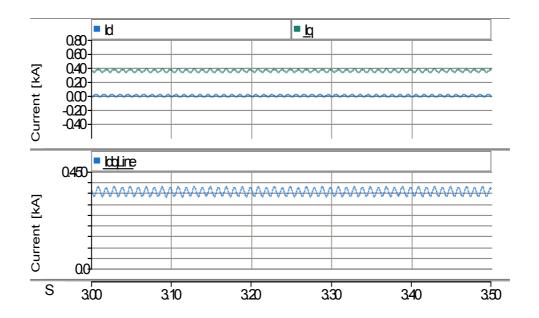

| FIG.4.56: ID, IQ AND AMPLITUDE OF THE LINE CURRENT                      | 135   |

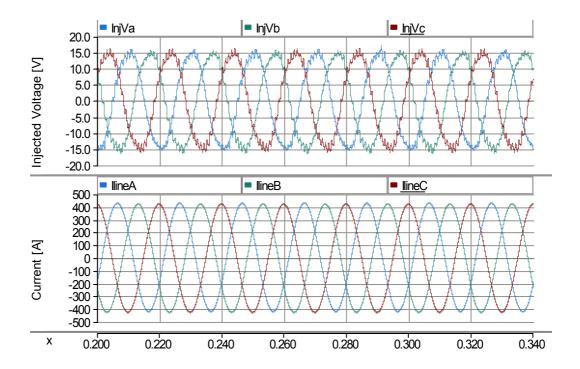

| FIG.4.57: INJECTED VOLTAGE AND LINE CURRENTS WHEN THE THREE PHASE SYST  | EM IS |

| UNBALANCED                                                              | 136   |

| FIG.4.58: THE ID AND IQ COMPONENTS ALONG WITH THE AMPLITUDE OF THE      | LINE  |

| CURRENT                                                                 | 136   |

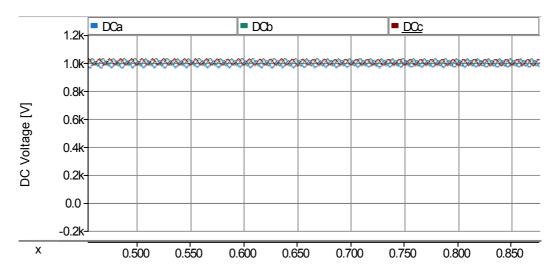

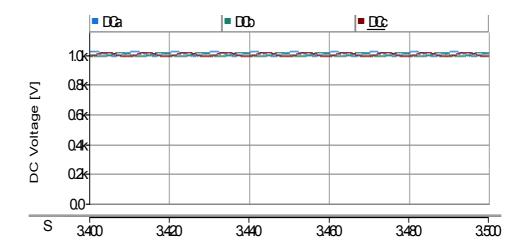

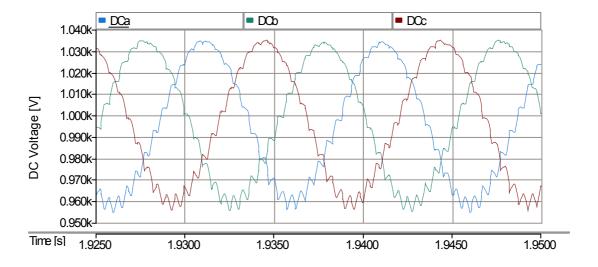

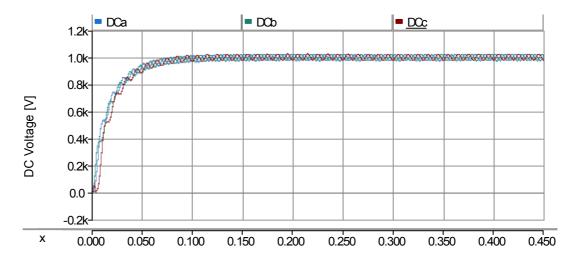

| FIG.4.59: DC VOLTAGES                                                   | 137   |

| FIG.4.60: REFERENCE VOLTAGES                                              | 137    |

|---------------------------------------------------------------------------|--------|

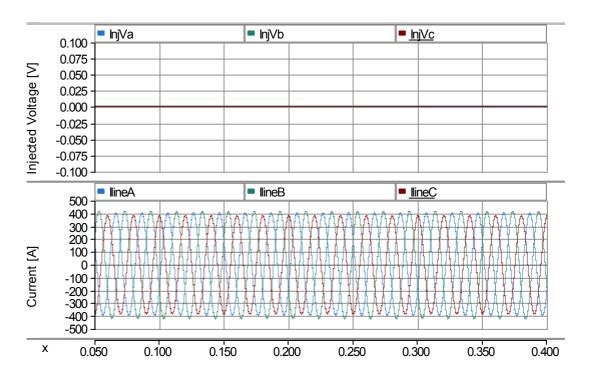

| FIG.4.61: THE INJECTED VOLTAGES BY DSSC DEVICES AND LINE CURRENTS         | 138    |

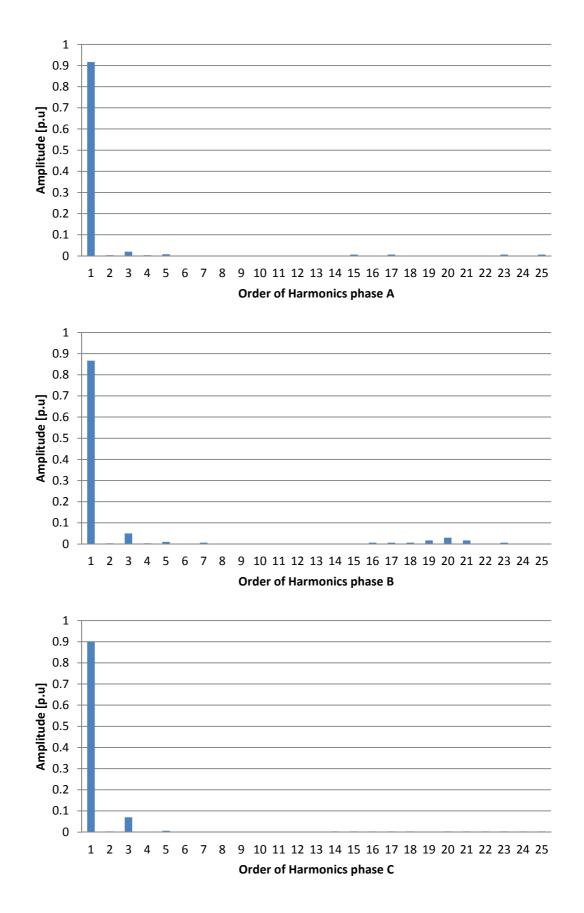

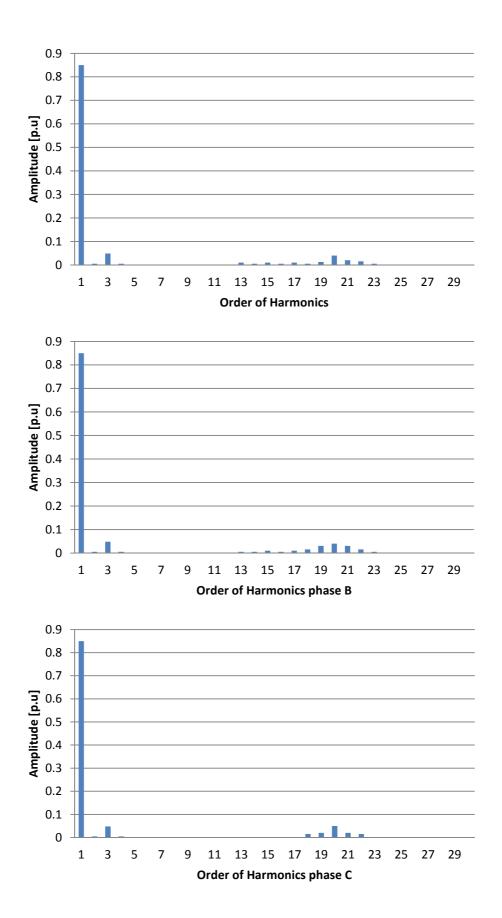

| FIG.4.62: INJECTED HARMONICS IN THREE PHASE                               | 139    |

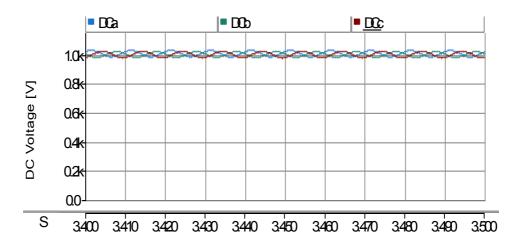

| FIG.4.63: DC VOLTAGES IN EACH PHASE                                       | 140    |

| FIG.4.64: DQ COMPONENTS AND AMPLITUDE OF THE LINE CURRENT                 | 141    |

| FIG.4.65: REFERENCE SIGNALS GENERATED BY THE DQ BASED CONTROLLER          | 141    |

| FIG.4.66: INJECTED VOLTAGE AND LINE CURRENTS                              | 142    |

| FIG.4.67: INJECTED HARMONICS IN THREE PHASE                               | 143    |

| FIG.4.68: AMPLITUDE OF EACH PHASE IN THE UNBALANCE SYSTEM                 | 144    |

| FIG. 4.69: DQ REPRESENTATION OF LOAD CURRENT                              | 144    |

| FIG.4.70: REFERENCE SIGNALS GENERATED BY SINGLE PHASE CONTROLLER          | 145    |

| FIG.4.71: INJECTED VOLTAGE BY DSSC AND LINE CURRENT WITHIN UNBAI          | LANCE  |

| SYSTEM.                                                                   | 145    |

| FIG.4.72: VOLTAGES ACROSS DC CAPACITORS                                   | 146    |

| FIG.4.73: SPECTRUMS OF INJECTED HARMONICS BY SINGLE PHASE CONTROLLER      | IN AN  |

| UNBALANCED SYSTEM                                                         | 147    |

| FIG.4.74: GENERATED REFERENCE SIGNAL BY THE DQ BASED CONTROLLER           | 148    |

| FIG.4.75: INJECTED VOLTAGE BY DSSC USING DQ BASED CONTROLLER              | 149    |

| FIG.4.76: VOLTAGE ACROSS THE DC CAPACITOR USING THE DQ BASED CONTROL      |        |

| AN UNBALANCED SYSTEM                                                      | 149    |

| FIG.4.77: SPECTRUMS OF INJECTED HARMONICS BY DQ BASED CONTROLLER          | IN AN  |

| UNBALANCED SYSTEM                                                         | 151    |

| FIG.4.78: COMPARISON BETWEEN THE PROPOSED CONTROLLER AND DC VO            | LTAGE  |

| (ONLY) CONTROLLER                                                         | 153    |

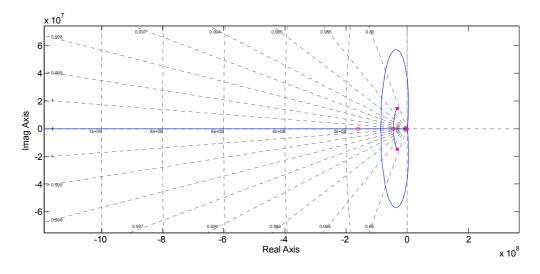

| FIG.4.79: ROOT LOCUS DIAGRAM OF G                                         | 154    |

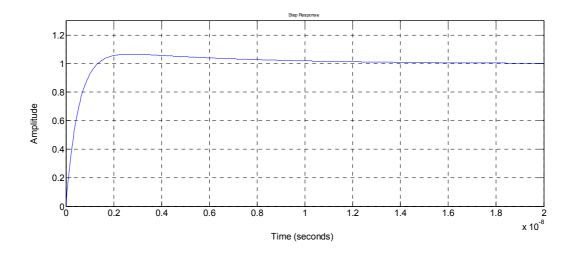

| FIG. 4.80: ROOT LOCUS WITH INSERTED ZERO AND POLE                         | 154    |

| FIG. 4.81: STEP RESPONSE WITH INSERTED ZERO AND POLE                      | 155    |

| FIG. 4.82: ROOT LOCUS WITH INSERTED ZERO IS MOVED FURTHER TO THE RIGHT    | 155    |

| FIG. 4.83: STEP RESPONSE OF THE SYSTEM WITH INSERTED ZERO IS MOVED FURTH  | IER TO |

| THE RIGHT                                                                 | 156    |

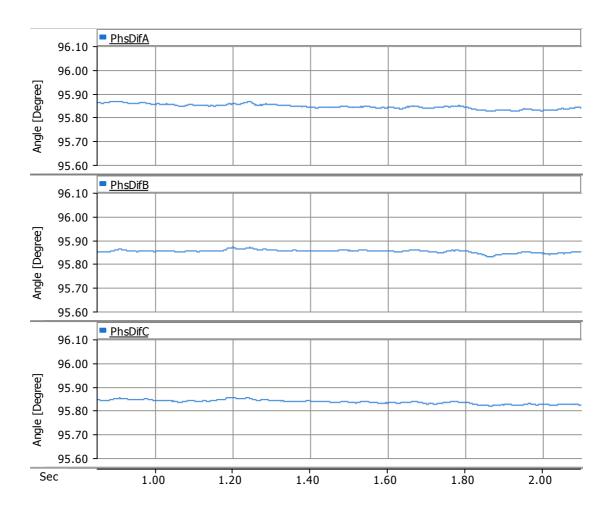

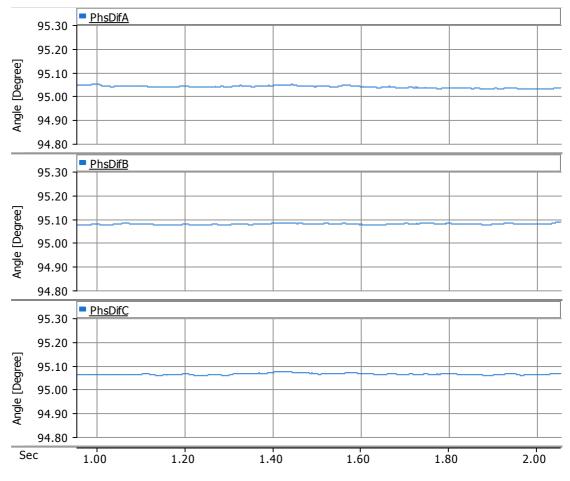

| FIG. 4.84: PHASE DIFFERENCE BETWEEN INJECTED VOLTAGE AND LINE CURRE       | ENT IN |

| EACH PHASE                                                                | 157    |

| FIG.4.85: DC VOLTAGES IN THREE DIFFERENT PHASES                           | 157    |

| FIG.4.86: INJECTED HARMONICS BY DSSC DEVICE                               | 159    |

| FIG. 4.87: VOLTAGES ACROSS THE DC CAPACITOR WHEN THE PI GAIN IS INCREASEI | D 160  |

| FIG. 4.88: INJECTION ANGLE WHEN GAIN IN THE PI CONTROLLER IS INCREASED    | 161    |

| FIG. 4.89: ORDER OF HARMONICS WHEN GAIN OF CONTROLLER IS REDUCED          | 162    |

| FIG. 4.90: VOLTAGES ACROSS THE DC CAPACITOR WHEN GAIN THE PI CONTROL      | LER IS |

| REDUCED                                                                   | 163    |

| FIG. 4.91: INJECTION ANGLE WHEN GAIN THE PI CONTROLLER IS REDUCED         | 164    |

| FIG. 4.92: ORDER OF HARMONICS WHEN GAIN OF CONTROLLER IS INCREASED        | 165    |

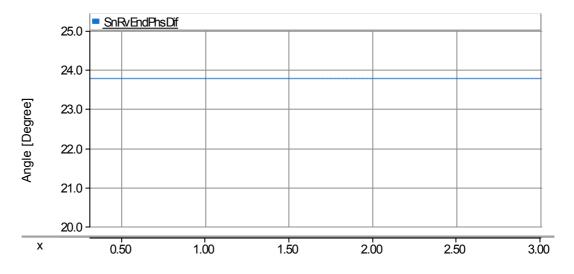

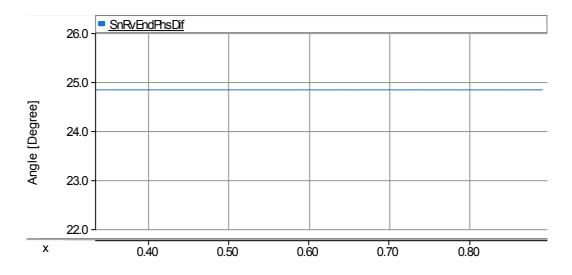

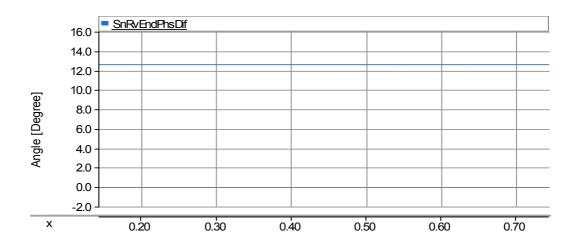

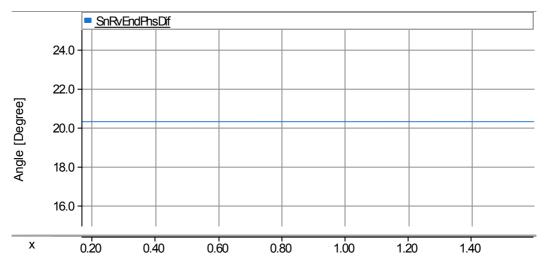

| FIG.4.93: INJECTION ANGLE                                              | 166      |

|------------------------------------------------------------------------|----------|

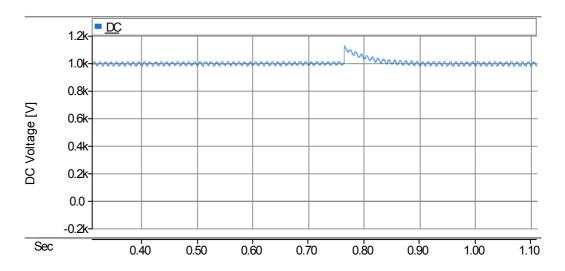

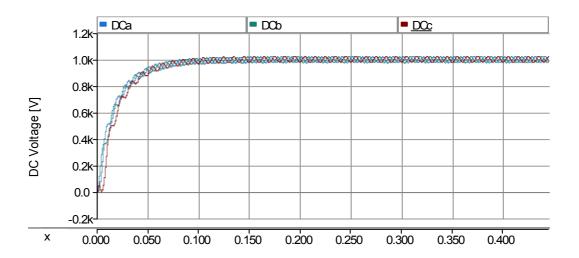

| FIG.4.94: DC VOLTAGE USING THE PROPOSED CONTROLLER                     | 167      |

| FIG.4.95: INJECTED HARMONICS USING THE PROPOSED CONTROLLER             | 168      |

| FIG. 4.96: DC VOLTAGE WHEN LINE IMPEDANCE INCLUDES 0.03 H REACTANCE    | AND 1Ω   |

| RESISTANCE                                                             | 170      |

| FIG.4.97: LINE CURRENT AND INJECTED VOLTAGE WHEN LINE IMPEDANCE IN     | CLUDES   |

| 0.03H REACTANCE AND 1Ω RESISTANCE                                      | 171      |

| FIG.4.98: LOAD ANGLE WHEN LINE IMPEDANCE INCLUDES 0.03 H REACTANCE     | AND 1Ω   |

| RESISTANCE                                                             | 171      |

| FIG.4.99: LINE CURRENT AND INJECTED VOLTAGE WHEN RESISTANCE OF THE     | LINE IS  |

| 0.1Ω                                                                   | 172      |

| FIG.4.100: LOAD ANGLE WHEN RESISTANCE OF THE LINE IS $0.1\Omega$       | 172      |

| FIG.4.101: DC VOLTAGE WHEN RESISTANCE OF THE LINE IS $0.1\Omega$       | 173      |

| FIG.4.102: VOLTAGE ACROSS THE DC LINK WHEN THE SUPPLIED LOAD IS HALVE  | D 174    |

| FIG.4.103: LINE CURRENT AND INJECTED VOLTAGE WHEN THE SUPPLIED         | LOAD IS  |

| HALVED                                                                 | 174      |

| FIG.4.104: LOAD ANGLE WHEN THE SUPPLIED LOAD IS HALVED                 | 175      |

| FIG.4.105: LOAD ANGLE WHEN ANOTHER LINE IS CONNECTED IN PARALLEL       | 175      |

| FIG.4.106: LINE CURRENT AND INJECTED VOLTAGE WHEN ANOTHER LINE IS CON  |          |

| IN PARALLEL                                                            |          |

| FIG.4.107: DC VOLTAGE WHEN ANOTHER LINE IS CONNECTED IN PARALLEL       |          |

| FIG.4.108: SENDING END LINE VOLTAGE WHEN THERE IS 10% OVER VOLTAGE     |          |

| FIG.4.109: INJECTED VOLTAGE AND LINE CURRENT IN PRESENCE OF 10% OVER V |          |

| FIG.4.110: DC VOLTAGE ACROSS THE CAPACITOR WHEN THERE IS 10% CHANG     |          |

| LINE VOLTAGE                                                           | 178      |

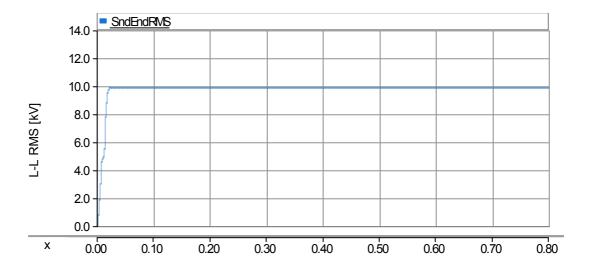

| FIG.4.111: RMS VALUE OF VOLTAGE AT THE SENDING END                     |          |

| FIG.4.112: INJECTED VOLTAGE AND LINE CURRENT WHEN THERE IS A 10% V     | OLTAGE   |

| DROP AT THE SENDING END BUS                                            |          |

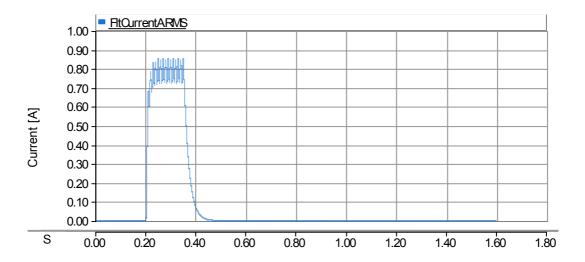

| FIG.4.113: RMS VALUE OF FAULT CURRENT                                  | 180      |

| FIG.4.114: THREE PHASE LINE CURRENT WITH SINGLE PHASE TO GROUND FAUI   | T IN "A" |

| PHASE                                                                  | 180      |

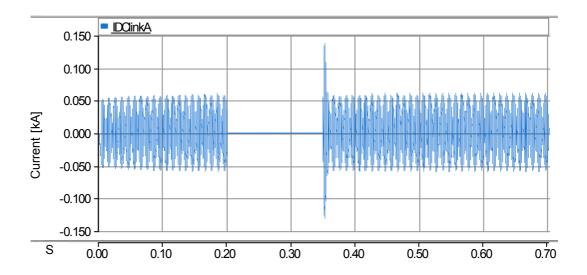

| FIG. 4.115: CURRENT FLOWING THROUGH THE DC CAPACITOR IN THE DSSC DEVI  | CE 181   |

| FIG.4.116: CURRENT THROUGH THE DC LINK WHEN STT IS BYPASSED            | 182      |

| FIG.4.117: INJECTED VOLTAGE AND LINE CURRENT WHEN THE STT IS BYPASSED  | 182      |

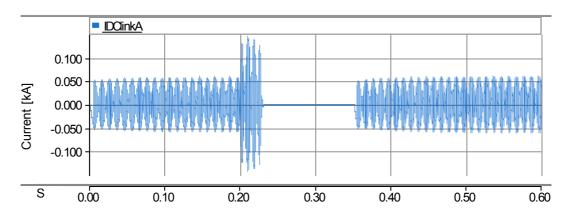

| FIG.4.118: DC VOLTAGE ACROSS THE CAPACITOR WHEN STT IS BYPASSED DUR    | ING THE  |

| FAULT                                                                  | 183      |

| FIG.4.119: VOLTAGE ACROSS THE DC CAPACITOR WHEN CONVERTER IS BLOCK     | CED AND  |

| STT IS BYPASSED                                                        | 183      |

| FIG.4.120: INJECTED VOLTAGE AND LINE CURRENT WHEN CONVERTER IS BLOCK   | KED AND  |

| STT IS BYPASSED                                                        | 184      |

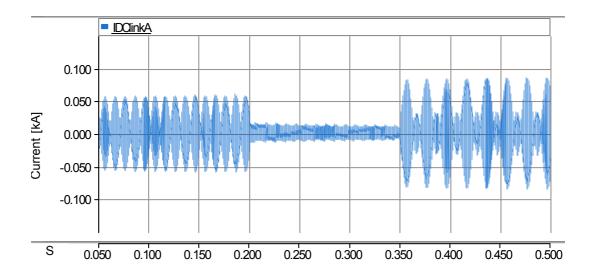

| FIG.4.121: DC LINK CURRENT WHEN CONVERTER IS BLOCKED AND STITIS BYPASSED.  |       |

|----------------------------------------------------------------------------|-------|

| FIG.4.122: DC LINK CURRENT WHEN STT IS OPEN CIRCUIT                        | . 185 |

| FIG.4.123: DC VOLTAGE INSIDE DSSC WHEN STT IS DISCONNECTED FROM            | THE   |

| CONVERTER                                                                  | . 185 |

| FIG.4.124: INJECTED VOLTAGE BY DSSC AND LINE CURRENT STT IS ISOLATED FI    | ROM   |

| CONVERTER                                                                  | . 186 |

| FIG.4.125: CURRENT THROUGH DC LINK WHEN ONLY CONVERTER IS BLOCKED          | . 187 |

| FIG.4.126: INJECTED VOLTAGE BY STT AND LINE CURRENT IN THREE DIFFERENT PHA |       |

| WHEN ONLY CONVERTER IS BLOCKED                                             | . 187 |

| FIG.4.127: VOLTAGE ACROSS THE DC LINK WHEN CONVERTER IS BLOCKED            | . 188 |

| FIG.4.128: HARMONICS AT THE INPUT AND OUTPUT OF THE RLC LOW PASS FILTER    | . 189 |

| FIG.4.129: OUTPUT VOLTAGE OF THE FILTER AND CONVERTER ALONG WITH           | THE   |

| SWITCHING PATTERN                                                          | . 190 |

| FIG. 4.130: OUTPUT VOLTAGE OF THE FILTER                                   | . 191 |

| FIG.4.131:OUTPUT VOLTAGE OF THE CONVERTER                                  | . 191 |

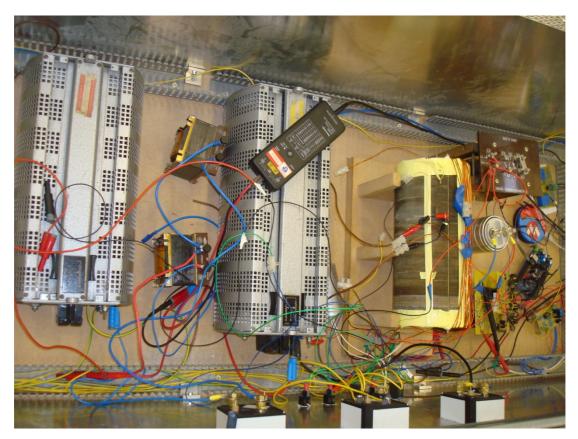

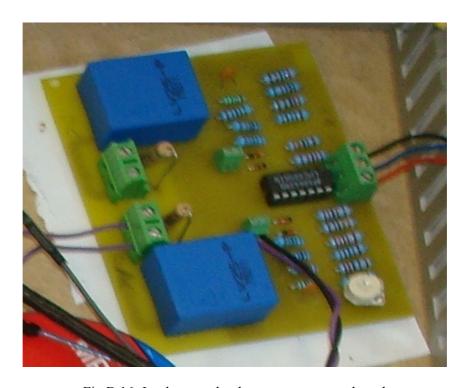

| FIG.5.1: THE OVERVIEW OF THE INSIDE OF THE TEST RIG                        | . 194 |

| FIG.5.2: H-BRIDGE VOLTAGE SOURCE CONVERTER                                 | . 196 |

| FIG.5.3: TYPICAL LAYOUT OF GATE DRIVE BOARD                                | . 198 |

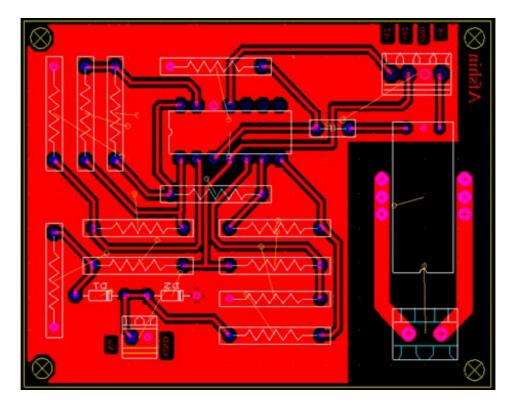

| FIG.5.4: DESIGN OF THE GATE DRIVE BOARD                                    | . 201 |

| FIG. 5.5: DESIGN OF VOLTAGE MEASUREMENT BOARD                              | . 205 |

| FIG.5.6: NON-INVERTING AMPLIFIER                                           | . 207 |

| FIG.5.7:FULL CIRCUIT OF THE CURRENT MEASUREMENT BOARD                      | . 208 |

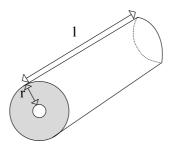

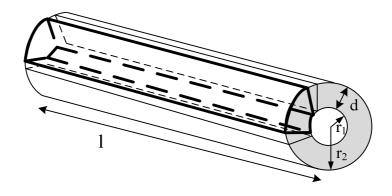

| FIG.5.8: SINGLE TURN TRANSFORMER                                           | . 209 |

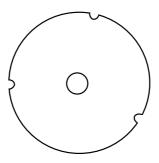

| FIG.5.9: CROSS SECTION OF THE STT CORE                                     | . 210 |

| FIG.5.10: THE CONNECTION OF DSSC DEVICE AND RELATIONS BETWEEN THE CURR     | ENT   |

| AND VOLTAGES                                                               | . 211 |

| FIG.5.11: CORE OF STT                                                      | . 212 |

| FIG.5.12: THE LOCATION OF BOLTS IN THE CROSS SECTION OF CORE               | . 214 |

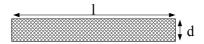

| FIG.5.13: RECTANGULAR CROSS SECTION                                        | . 216 |

| FIG.5.14: DESIGNED STT FOR AN 11KV DISTRIBUTION SYSTEM                     | . 216 |

| FIG.5.15: AIR GAP                                                          | . 216 |

| FIG.5.16: DIFFERENT TYPES (CONFIGURATIONS) OF FILTERS                      | . 220 |

| FIG.5.17: BODE DIAGRAMS OF THREE DIFFERENT TYPES OF FILTERS                | . 222 |

| FIG.5.18: DESIGNED AND EMPLOYED LOW PASS FILTER                            | . 223 |

| FIG.5.19: BODE DIAGRAM OF THE DESIGNED LOW PASS LC FILTER                  | . 224 |

| FIG.5.20: H-BRIDGE CONVERTER, RLC FILTER AND STT                           | . 225 |

| FIG.5.21: CAPACITIVE VOLTAGE INJECTION (SNAPSHOT OF THE SCREEN             |       |

| OSCILLOSCOPE)                                                              |       |

| FIG.5.22: CAPACITIVE INJECTION                                             |       |

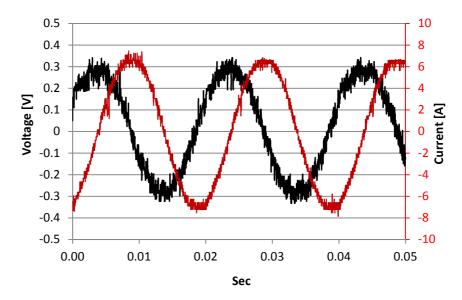

| FIG.5.23: INDUCTIVE INJECTION                                              | . 227 |

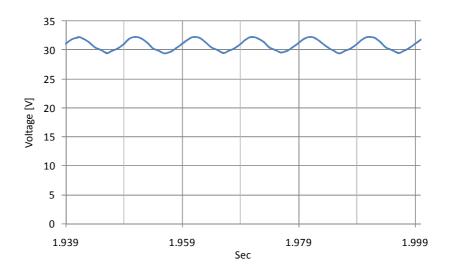

| FIG.5.24: DC LINK RIPPLES WITH PROPOSED CONTROL                            | . 228 |

| FIG.5.25: DC LINK RIPPLES WITH CONVENTIONAL CONTROL | 228 |

|-----------------------------------------------------|-----|

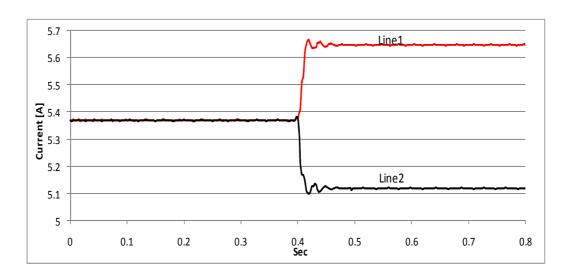

| FIG.5.26: PRACTICAL RMS VALUE OF LINE CURRENT       | 230 |

# **Table of Contents**

| 1    | Introduc            | ction                                                            | 23     |

|------|---------------------|------------------------------------------------------------------|--------|

| 1.1  | Background          |                                                                  | 23     |

| 1.2  | Research objectives |                                                                  | 24     |

| 1.3  | The                 | esis layout                                                      | 25     |

| 2    | Comper              | nsation in electrical networks                                   | 28     |

| 2.1  | Con                 | mpensation methods                                               | 28     |

| 2.2  | Shu                 | unt Compensation                                                 | 29     |

|      | 2.2.1               | Synchronous Voltage Source                                       | 29     |

| 2.3  | Ser                 | ies compensation                                                 | 31     |

|      | 2.3.1               | Improvement of power system stability                            | 32     |

|      | 2.3.2               | Improvement of voltage stability                                 | 33     |

| 2.4  | Fix                 | ed Series Capacitor Compensation (Series compensation)           | 33     |

|      | 2.4.1               | Power topologies of fixed series compensator                     | 34     |

|      | 2.4.2               | Point of connection of fixed series capacitors                   | 36     |

| 2.5  | Thy                 | yristor Switched Series Capacitors (TSSC)                        | 36     |

| 2.6  | Th                  | yristor Controlled Series Compensation (TCSC)                    | 37     |

|      | 2.6.1               | Bypass mode                                                      | 38     |

|      | 2.6.2               | Blocked mode                                                     | 38     |

|      | 2.6.3               | Capacitive boost mode                                            | 39     |

|      | 2.6.4               | Inductive boost mode                                             | 39     |

| 2.7  | GT                  | O Thyristor-Controlled Series Capacitor (GCSC)                   | 40     |

| 2.8  | Ap                  | plication of synchronous voltage source in series compensation   | 41     |

| 2.9  | Sta                 | tic Synchronous Series Compensator (SSSC)                        | 48     |

| 2.10 | O Co                | mparison between power electronics based series compensators and | series |

| fixe | ed capaci           | tors                                                             | 50     |

| 2.1  | l Dis               | tributed Static Synchronous Compensation (DSSC)                  | 51     |

| 2.12 | 2 Co                | ntrol of DSSC                                                    | 58     |

|      | 2.12.1              | Control strategy based on dq                                     | 59     |

|      | 2.12.2              | Control strategy based on 90 degree phase shift                  | 63     |

| 2.13 | 3 Dra               | wbacks with dq based controllers                                 | 66     |

|            | 2.13.1  | dq conversion in balanced three-phase system                        | 66     |

|------------|---------|---------------------------------------------------------------------|--------|

|            | 2.13.2  | dq conversion in unbalanced three wire three-phase system           | 68     |

|            | 2.13.3  | Decomposition of an unbalanced AC System                            | 71     |

| 2.14       | 4 Sur   | nmery                                                               | 76     |

| 3          | Applica | tions of DSSC in distribution networks                              | 78     |

| 3.1        | Ap      | plications of DSSC in the distribution networks                     | 79     |

|            | 3.1.1   | Effect of line resistance on the control of DSSC                    | 79     |

|            | 3.1.2   | Calculation of required numbers of DSSC                             | 83     |

| 3.2        | Loa     | nd flow control using DSSC                                          | 84     |

| 3.3        | Vo      | tage profile improvement using DSSC                                 | 86     |

| 3.4        | Sur     | nmary                                                               | 91     |

| 4          | New Co  | entrol Strategy                                                     | 92     |

| 4.1        | Nev     | w approach of controlling DSSC with single phase control            | 92     |

|            | 4.1.1   | Advantages of the proposed controller                               | 98     |

| 4.2        | Mo      | delling of DSSC                                                     | 99     |

|            | 4.2.1   | Operation mode 1                                                    | 100    |

|            | 4.2.2   | Operation mode 2                                                    | 101    |

|            | 4.2.3   | Average of current through DC capacitor                             | 101    |

| 4.3        | Cor     | ntroller design                                                     | 102    |

| 4.4        | Sen     | sitivity analysis of designed controller                            | 108    |

|            | 4.4.1   | Effects of change in the system parameters                          | 108    |

| 4.5        | Eff     | ect of adding a low pass filter to the proposed controller          | 111    |

| 4.6        | Sin     | nulation of performance of proposed controller                      | 114    |

|            | 4.6.1   | Capacitive injection.                                               | 115    |

|            | 4.6.2   | Inductive injection                                                 | 119    |

| 4.7<br>con |         | mparing performance of proposed controller with 90° phase shift     |        |

| 4.8        | Cor     | mparing performance of proposed controller and dq based controller. | 132    |

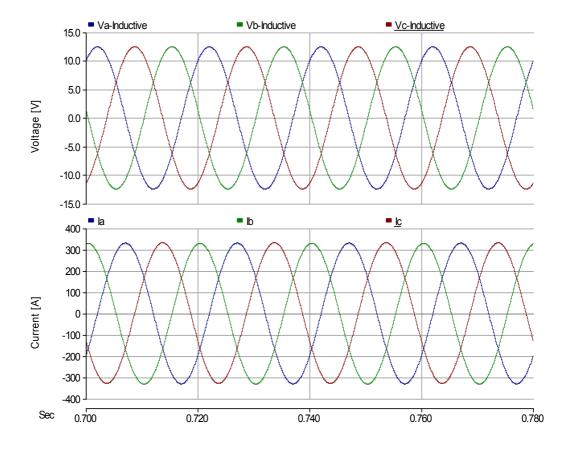

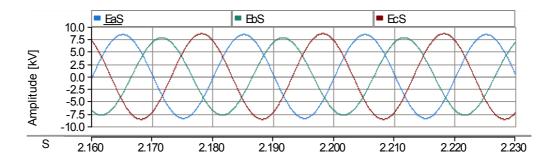

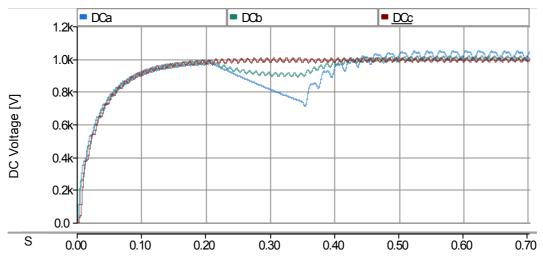

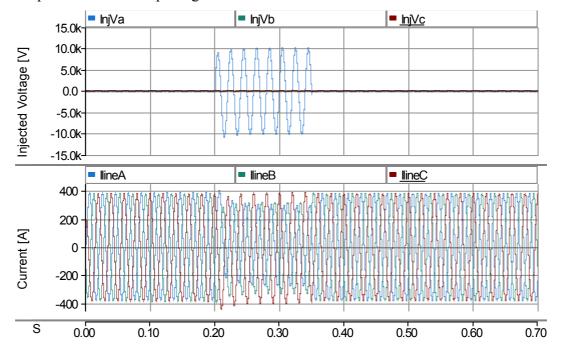

|            | 4.8.1   | Performance of proposed controller within three phase system        | 132    |

|            | 4.8.2   | An unbalanced three phase system with no series compensation        |        |

|            | 4.8.3   | Performance of propsed controller within unbalanced three phase lo  | ad 136 |

|     | 4.8.4            | Performance of dq based controller within unbalanced three phase 139 | se Ioac |

|-----|------------------|----------------------------------------------------------------------|---------|

|     | 4.8.5            | Performance of proposed controller in presence of unbalance three    | e phase |

|     | system           | 144                                                                  | 1       |

|     | 4.8.6            | Performance of dq based controller in presence of unbalance three    | phase   |

|     | system           | 148                                                                  | •       |

| 4.9 | Co               | mparing the performance of proposed controller with using only a D   | C link  |

|     |                  | roller                                                               |         |

|     | 4.9.1            | Performance of the device using voltage regulator only               | 153     |

|     | 4.9.2            | Performance of the device using proposed controller                  |         |

|     | 4.9.3            | Summarized results of conventional and proposed controller           |         |

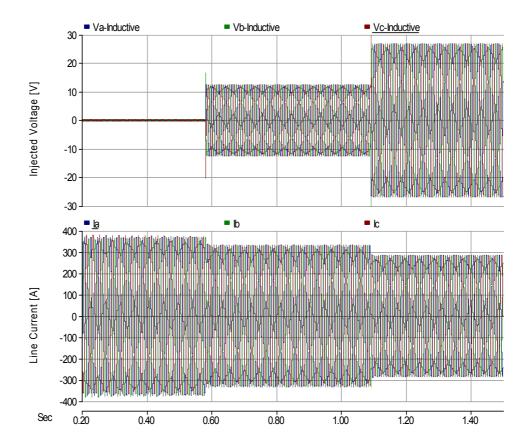

| 4.1 | () Inv           | estigation of the change of the system parameters on the performance |         |

|     |                  | ntroller                                                             |         |

| PTO | -                |                                                                      |         |

|     | 4.10.1           | Performance of the DSSS with no changes in system parameters         |         |

|     | 4.10.2           | Performance of the DSSS when resistance of the line is altered       |         |

|     | 4.10.3           | Performance of the DSSS when load is reduced in half                 |         |

|     | 4.10.4<br>4.10.5 | Performance of the DSSS in reconfigured network                      |         |

|     |                  | Performance of the DSSS in sag swell of the line voltage             |         |

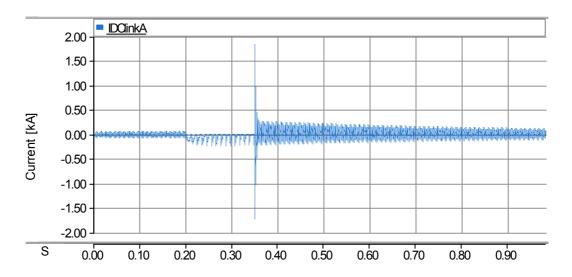

| 4.1 | 1 Fau            | ılt Management Study                                                 | 180     |

|     | 4.11.1           | STT is bypassed                                                      | 181     |

|     | 4.11.2           | STT is bypassed and converter is blocked                             | 183     |

|     | 4.11.3           | STT is opened                                                        | 185     |

|     | 4.11.4           | Converter is blocked                                                 | 186     |

|     | 4.11.5           | Concluded fault strategy                                             | 188     |

| 4.1 | 2 Sin            | nulation of LC filter                                                | 189     |

| 4.1 | 3 Sui            | nmary                                                                | 192     |

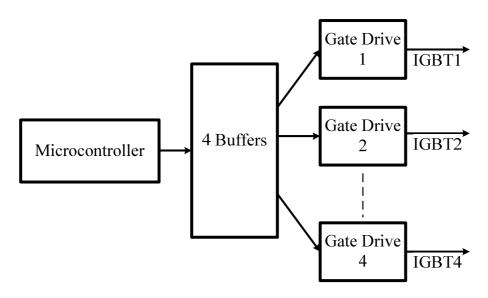

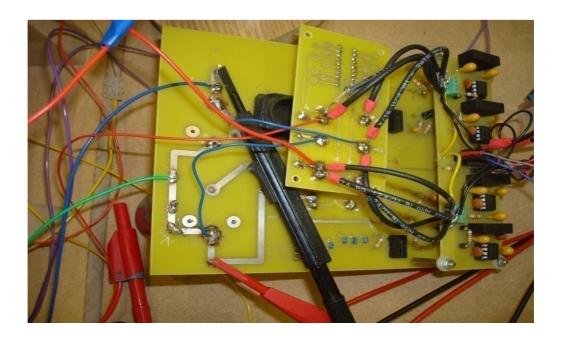

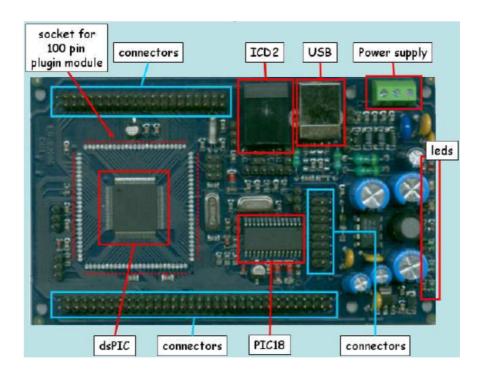

| 5   | Experin          | nental Results                                                       | 194     |

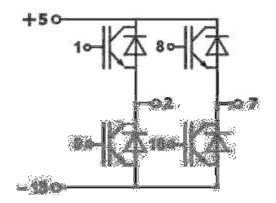

| 5.1 | H-1              | Bridge Voltage Source Converter                                      | 195     |

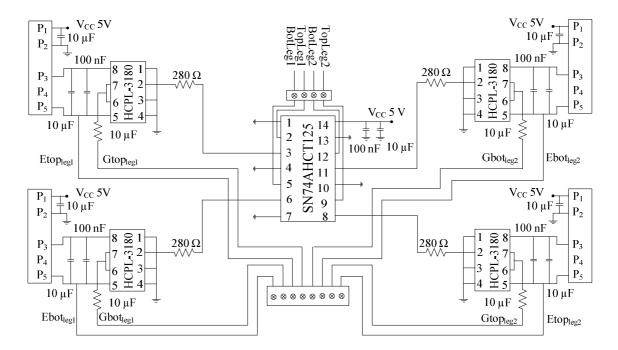

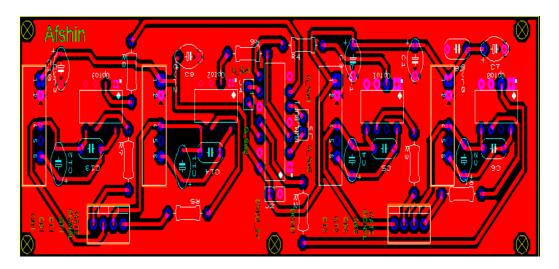

| 5.2 |                  | te Driver Board                                                      |         |

|     | 5.2.1            | Design of gate drive board                                           | 201     |

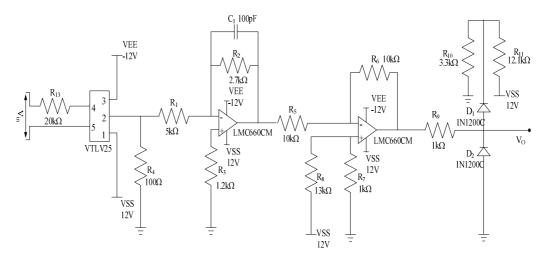

| 5.3 | Vo               | Itage Measurement Board                                              |         |

|     | 5.3.1            | Design of voltage measurement board                                  |         |

|     |                  | <u> </u>                                                             | 0 0     |

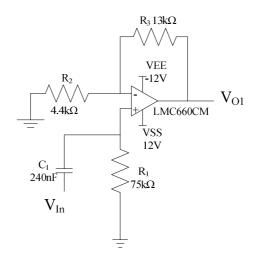

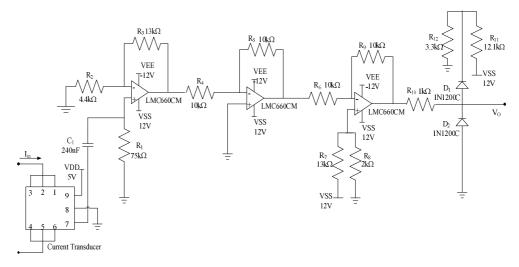

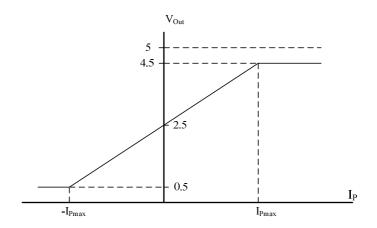

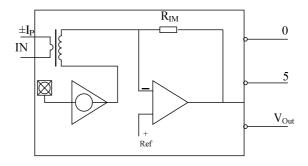

| 5.4         |          | Current Measurement                                                   | 205        |  |  |

|-------------|----------|-----------------------------------------------------------------------|------------|--|--|

|             | 5.4.     | 1 Design of electronic circuit of current measurement board           | 206        |  |  |

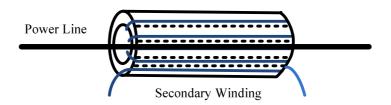

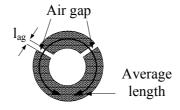

| 5.5         |          | Single Turn Transformer (STT)                                         | 209        |  |  |

| 5.6         |          | Design steps of single turn transformer to be employed in an 11kV dis | stribution |  |  |

| feed        | der      | 214                                                                   |            |  |  |

| 5.7         |          | Microcontroller                                                       | 218        |  |  |

| 5.8         |          | LC Filter                                                             | 219        |  |  |

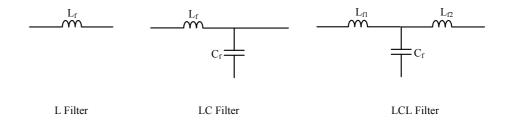

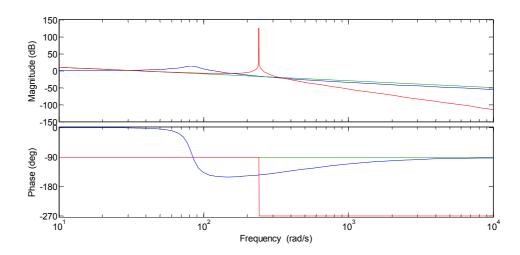

|             | 5.8.     | 1 Different types of low pass filters                                 | 219        |  |  |

|             | 5.8.     | 2 Performances of the filters                                         | 221        |  |  |

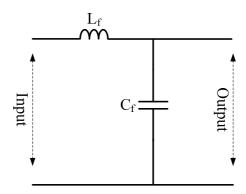

| 5.9         |          | Design of LC filter                                                   | 223        |  |  |

|             | 5.9.     | 1 Implemented RC filter                                               | 225        |  |  |

| 5.10        | 0        | Validation of proposed controller                                     | 226        |  |  |

| 5.1         | 1        | Summary                                                               | 230        |  |  |

| 6           | Cor      | nclusions and Future Work                                             | 233        |  |  |

| 6.1         |          | Conclusion                                                            | 233        |  |  |

| 6.2         |          | Contributions                                                         | 238        |  |  |

| 6.3         |          | Future work                                                           | 239        |  |  |

|             | 6.3.     | 1 Design consideration                                                | 239        |  |  |

|             | 6.3.     | 2 High level control and managing the modules in the network          | 239        |  |  |

| 7           | Ref      | erences:                                                              | 240        |  |  |

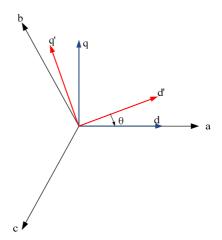

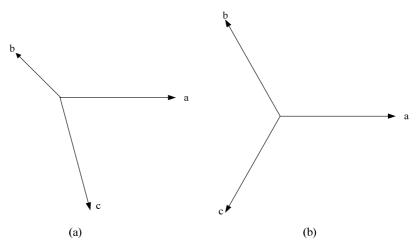

| App         | pend     | ix A: dq Conversion                                                   | 250        |  |  |

| <b>A</b> .1 |          | Introduction                                                          | 250        |  |  |

| A.2         |          | dq conversion                                                         | 250        |  |  |

| A.3         |          | Unbalanced Three Phase AC System                                      | 253        |  |  |

| Арр         | pend     | ix B: Technical Characteristics of Components                         | 254        |  |  |

| B.1         | Iı       | ntroduction                                                           | 254        |  |  |

| B.2         |          | H-Bridge Converter                                                    | 255        |  |  |

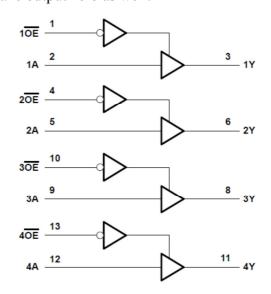

| B.3         | Buffer25 |                                                                       |            |  |  |

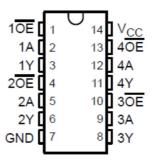

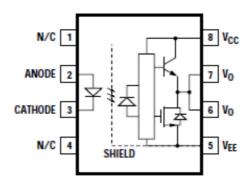

| B.4         |          | Gate Drive                                                            | 258        |  |  |

| B.5         |          | Isolated power supply                                                 | 260        |  |  |

| B.6         |          | Voltage Transducer (VT)                                               | 263        |  |  |

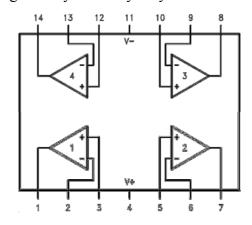

| B.7    | Op    | -Amp                                                              | 265 |

|--------|-------|-------------------------------------------------------------------|-----|

| B.8    | Cu    | rrent Transducer                                                  | 266 |

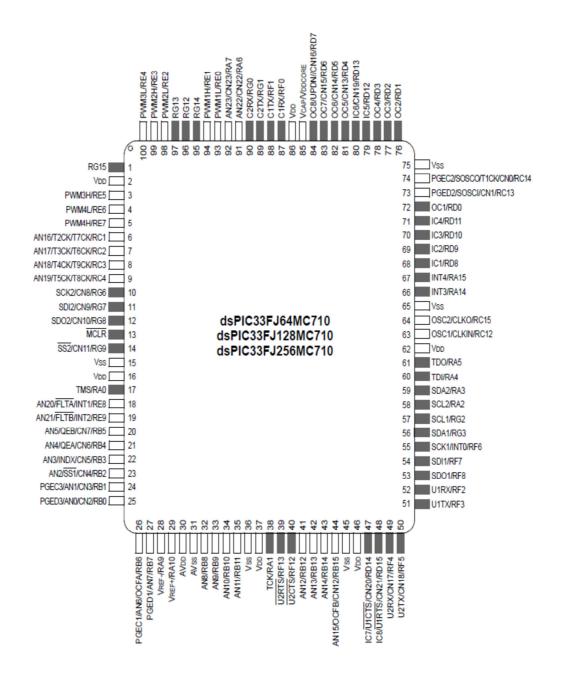

| Append | dix C | : Microcontroller                                                 | 270 |

| C.1    | Int   | roduction                                                         | 270 |

| C.2    | Mi    | crocontroller                                                     | 270 |

| C.3    | Diı   | rect Memory Access (DMA)                                          | 274 |

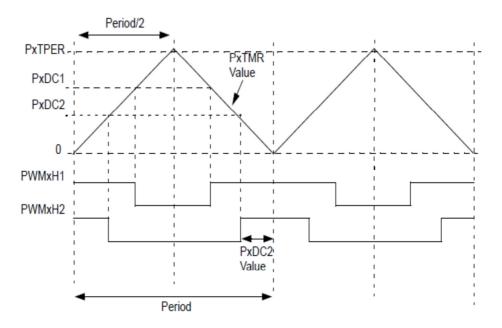

| C.4    | PW    | /M Generator                                                      | 275 |

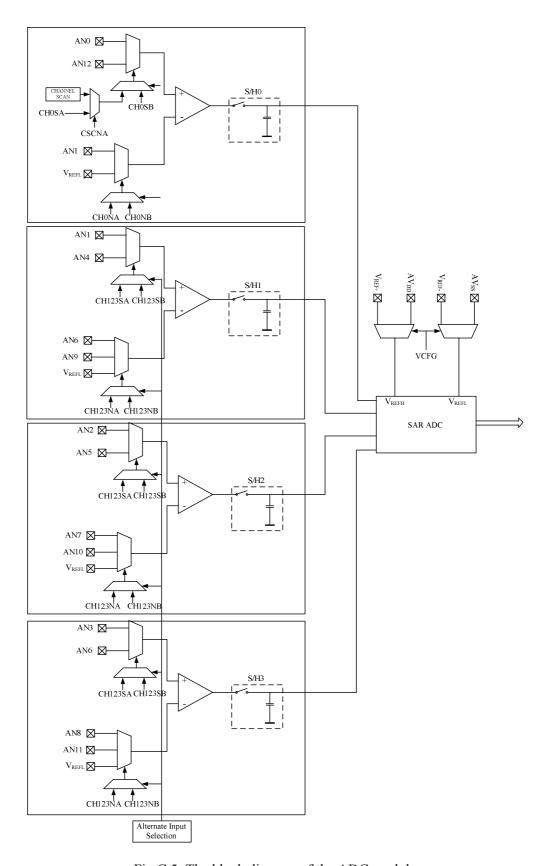

| C.5    | An    | alogue to Digital Converter (ADC)                                 | 279 |

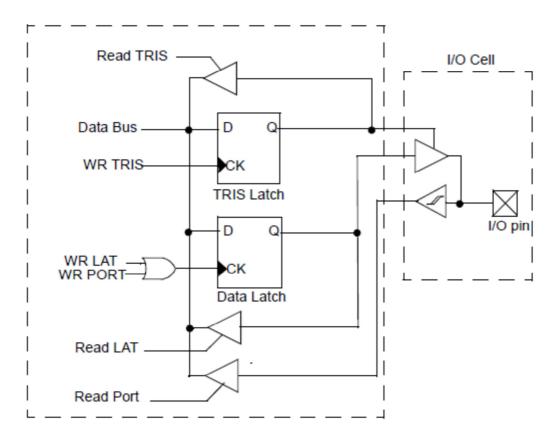

| C.6    | I/C   | Ports                                                             | 281 |

| Append | dix D | : Application of DSSC in Distribution Networks; Feasibility Study | 283 |

| D.1    | Int   | roduction                                                         | 283 |

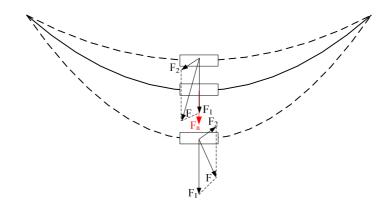

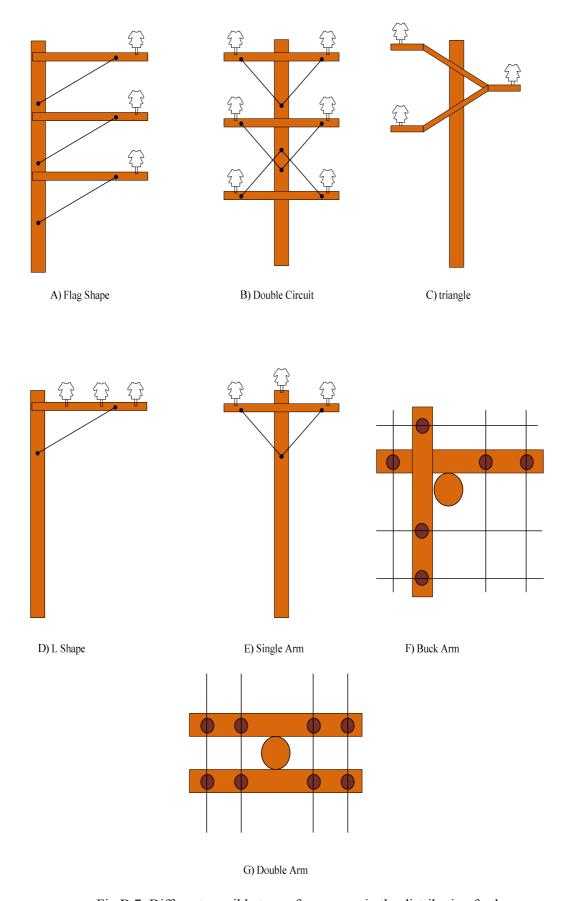

| D.2    | Ov    | erhead Line Design Consideration                                  | 283 |

| D.:    | 2.1   | Restricted vibration                                              | 283 |

| D.:    | 2.2   | Conductor tension                                                 | 285 |

| D.:    | 2.3   | Cross-arm                                                         | 287 |

| D.:    | 2.4   | Poles                                                             | 293 |

| D.3    | Su    | mmery                                                             | 297 |

#### 1 Introduction

#### 1.1 Background

Distributed static series compensator (DSSC) is a type of FACTS (Flexible AC Transmission System) devices that is utilized to compensate the line reactance in electrical networks. Through means of series compensation the line reactance can be reduced and the Available Transmission Capacity (ATC) can be increased. It can then maximize the utilization of the existing networks and postpone the construction of new electrical networks.

However, series compensation traditionally is achieved by implementation of fixed capacitors in series through the power lines. The combination of fixed capacitors and inductance of the line can initiate sub-synchronous resonance (SSR) phenomenon. This is a challenging issue with the application of fixed capacitors and it is established the idea of using power electronics based compensations.

DSSC is the most novel power electronic based series compensation in the transmission lines. Furthermore, by connection of solar generators and wind farms (in most of the cases) to the distribution networks the need of expansion in these networks become more important. Application of DSSC in the 11kV distribution networks along with a new control strategy to enhance the performance of the DSSC device has been introduced in this study. The proposed control system has been simulated and simulation results are presented to validate the proposed scheme. In addition a test bench has been designed and implemented to conduct experimental tests.

#### 1.2 Research objectives

This research focuses on series compensation and the aim, thus, is to primarily build up an inclusive understanding of the principle of series compensation. This includes investigation of existing series compensation solutions and highlighting their strengths and weaknesses. For example, the concept of fixed capacitors and power electronics based compensators are required to be studied in depth and their advantages and disadvantages identified. Sequentially, applied control strategies are required to be studied and drawbacks to be identified.

Control strategy of DSSC device has not received adequate attention in the literature and in most of the cases it is simply limited to stating that the injected voltage by DSSC must be orthogonal to the line current [1]. In the same time among series compensation devices, Static Synchrounes Series Compensator (SSSC) also operates with the same concept [2]. This is encouraging to consider investigating control strategies which have been employed within SSSC devices. However those strategies are mainly based on the abc to dq conversion [3] which they have own disadvantages in presence of unbalance AC system. Most of these controllers employ dq conversion in which balanced conditions and negligible zero sequence are necessary assumptions. The assumptions might be sensible at transmission level, however because of presence of unbalanced loads and currents it can be unreasonable assumption the distribution networks. As a result these strategies can be erroneous and provide wrong amount of compensation being injected.

Some of the control strategies are based on the 90° phase shift and practically in order to compensate the internal losses of the DSSC the voltage is slightly diverted from 90°. The diversion can vary over the time and this can put the stability of the system at risk.

A new control system needs to be developed to overcome drawbacks with the existing control systems. The controller must guaranty the 90° voltage injection and regulate the DC voltage at the desired value. It should be immune against the unbalance of the AC system and should provide reference signal for DSSC modules installed in three phase independently from each other. In order to address these requirements a new single-phase controller conceptually based on the instantaneous power exchange between power system and DSSC is proposed.

The developed control therefore is simulated and tested experimentally. In order to conduct experimental tests, a test rig is designed and implemented.

The objectives of the research are:

- To build up a broad understanding of series compensations

- To identify the drawbacks within the existing series compensation methods

- To investigate potential application of DSSC in 11kV distribution networks

- To develop an understanding of existing control methods and their drawbacks

- To develop a new control method for enhancing the performance of the system

- To design and implement a single turn transformer and a test rig for conducting of experimental tests

- To validate the proposed control strategy

#### 1.3 Thesis layout

This thesis introduces application of DSSC devices in 11kV distribution networks. At the same time it develops a new control method to enhance the performance of DSSC.

In chapter 2 a brief summary of compensations is stated and the principle of series compensation and available commercial solutions are explained and examined. Furthermore, their power topologies and the associated advantages and disadvantages are clarified. Fixed series capacitors, as a traditional and simple solution, are investigated in detail. This is then followed by explanation of power electronics based series compensators. In this category static synchronous series compensators (SSSC) are explained in detail and their drawbacks explained. DSSC is found to overcome some of the issues of application of SSSC in the electrical networks. It is followed by explanation of power topology and principle of operation of DSSC.

Subsequently, existing control algorithms of SSSC and DSSC are explained. The advantages and disadvantages of different control systems (existing control strategies in the literature review) have been studied. The drawback with dq conversion based controllers has been presented.

Chapter 3 presents potential applications of DSSC in 11kV distribution networks. Different applications of the DSSC device has been explained and simulated. The effect

of line resistance on the performance of DSSC has been investigated. Relationship between X/R ratio and power transfer capability of line with and without compensation is studied. In this chapter it has been shown that how this device can improve the voltage profile through an 11kV distribution feeder. It has been shown that the device can contribute toward power flow control by diverting current from one line to another one.

Chapter 4 is organized so that it primarily introduces the novel control algorithms and thereupon presents simulation results of its utilization. The modelling approach of DSSC to be employed in controller design using MATLAB is also explained in this chapter. The designed controller is implemented in the PSCAD model and the simulation results show the capability of controller in the injection of both capacitive and inductive voltages through the line. Sensitivity of the designed controller against change of system parameters has been investigated. An exhaustive list of simulation result comparing the performance of the developed controller with the performance of the traditional controllers is presented. Satisfactory performance of the developed controller in presence of unbalance system and voltage dip has been demonstrated. A fault management strategy has been developed in this chapter and the related simulation results are presented. An investigation regarding the effect of change of power system parameters on the performance of the DSSC has been conducted.

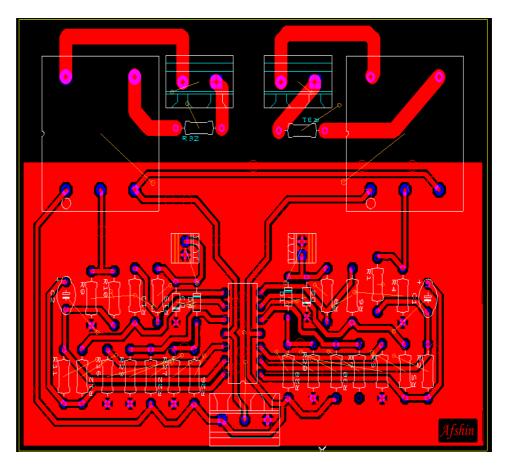

The design procedure of the test rig is presented in chapter 5. The explained procedure includes design of single turn transformer (STT), LC filter, all electronics and power electronics boards. This is followed by demonstrating full design steps of STT to be employed in an 11kV system. Different type of low pass filters has been studied and LC filter is selected to be employed in the DSSC device. Moreover, all hardware design calculations and implementation process are included. Finally, the chapter includes the procedure of conducting the experimental tests and the description of low voltage power system required for the tests. The experimental tests include demonstrating the capability of developed controller in injecting capacitive and inductive reactance through the line. Thereafter, performance of the proposed controller is compared with a traditional controller. Finally, load flow capability of DSSC has been demonstrated.

In chapter 6 represents the conclusions and author contributions. The publication from this research work is listed. This is followed by recommendations for the future works.

At the end of the thesis four appendixes A, B, C and D are presented. Appendix A provides expanded information about dq conversion and appendix B is about components specifications. Appendix C presents detailed information about microcontroller respectively. Feasibility study of application of DSSC devices in 11kV distribution networks in terms of mechanical withstand capability of the existing networks has been demonstrated in appendix D

#### 2 Compensation in electrical networks

This chapter describes different types of compensations including series, shunt and hybrid in the electrical networks. Shunt and hybrid compensators are explained briefly as they are not main subject of study. However series compensators are explained exhaustively with comprehensive literature review. This includes all available series compensation methods and related topologies.

This chapter presents the principle of control of SSSC and DSSC and it is followed by investigation on the existing employed control strategies in their applications. The advantages and disadvantages of the controllers are also discussed.

#### 2.1 Compensation methods

Compensation in electrical networks can be achieved in different ways and they can be employed to increase efficiency of the AC system and enhance its controllability. Efficiency of the system can be increased by optimal utilizing of ATC and avoiding unnecessary reactive power flow through the power lines [4], [5]. Different types of compensation, shunt, series and hybrid are categorized in Fig.2.1.

Fig.2.1: Different type of compensation

Shunt compensation can be accomplished by using Static Synchronous Compensator (STATCOM) or Static VAR Compensator (SVC) to regulate voltages in the connected buses of an electrical network. They can supply all or part of required reactive power locally and avoid occupying line capacity to deliver reactive power [6]. Shunt compensators act as current source and inject a current in parallel with the line.

However, series compensation is mainly used to alter reactance of line. This can be performed by inserting a capacitive reactance through the power line. Series compensation helps to release ATC and enhance power flow in the network. This compensator is of voltage source type and it injects a series voltage through the line. In addition, series and shunt compensation simultaneously can be achieved by hybrid compensation. Unified Power Flow Controller (UPFC) is a hybrid compensator which can control active and reactive power flow through the power lines independently [7, 8]. This device is comprised of a shunt compensator and series compensator. UPFC regulates bus voltage and compensates line reactance by injecting current in parallel and voltage in series respectively [9, 10].

#### 2.2 Shunt Compensation

Shunt compensation is usually used to regulate voltages in an electrical network. Shunt compensators generate leading current to compensate the lagging current of the load, i.e. they inject reactive power into the system and thus regulate the local voltage at the point of injection. Shunt compensator can also be inductive and in this case it can be used to reduce voltage levels if these are increased beyond the operating limits of a circuit. Shunt compensation is traditionally provided using fixed capacitors, reactors or rotating synchronous condensers. Compensation can also be provided using static switches and power electronics based devices such as STATCOM and SVC allowing a very fast response to system transients. Such devices have the capability of injecting both inductive and capacitive reactive power on demand [6].

#### 2.2.1 Synchronous Voltage Source

Rotating synchronous condensers (over excited synchronous generators running on no load) have been used as a shunt compensator in transmission and distribution networks for many years. Although the synchronous machine has an inductive nature and cannot therefore contribute toward any sub-synchronous resonance oscillations [11], [12], the scheme still has some disadvantages. For example, it has a slow response which disqualifies it from being used for system dynamic control enhancement. Furthermore, it has low short circuit impedance and high maintenance costs [13].

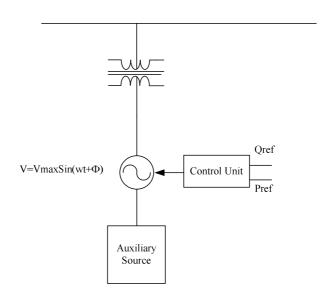

A SVS shunt compensation device using static switches is discussed in [13]. This has some advantages in comparison with the rotating synchronous condenser. For example,

it does not have inertia and its output can be controlled dynamically. Fig.2.2 shows a parallel connection of SVS into a power line.

Fig.2.2: SVS shunt compensation

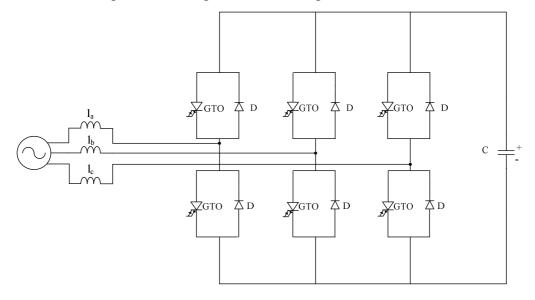

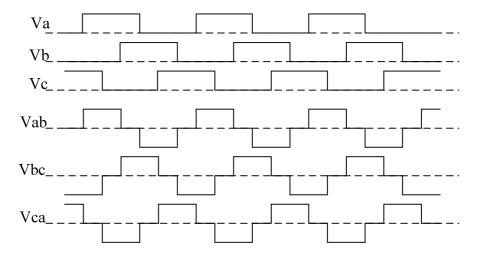

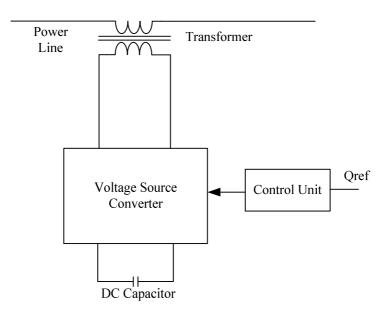

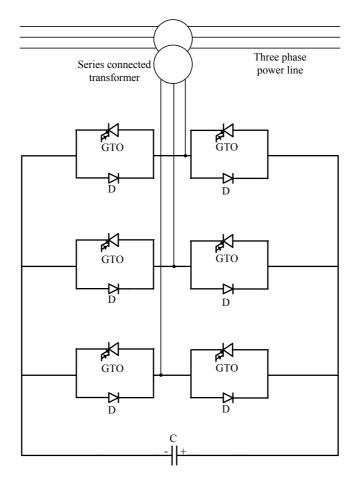

Converters with different power topologies can be employed as a SVS. In [13], a six pulse voltage source converter (VSC) is utilized as a static synchronous voltage Source. The converter, shown in Fig.2.3, comprises three legs connected in parallel with a DC capacitor, each leg consisting of two sets of GTOs with an anti-parallel diode. When the GTO in each leg is triggered, the voltage across the capacitor will appear at the corresponding ac output. With sequential switching of the GTOs, the converter output will be a three-phase ac voltage as shown in Fig.2.4.

Fig.2.3: Voltage Source Converter

Fig.2.4: Output voltage

The VSC converter shown in Fig.2.3 has the ability to exchange both active and reactive powers with the supply (if an auxiliary power supply is provided on the dc side). Power can flow in both directions across the converter (from the DC link into the AC system and vice versa) governed by the amplitude and phase angle of the converter output voltage. If the amplitude of the AC output voltage is higher than the voltage of the AC system, then the converter generates reactive power and behaves like a capacitor. However, if the amplitude of the ac output voltage is lower than the voltage of the AC system, the converter consumes reactive power and appears as an inductive load. Active power exchange can be achieved by controlling the phase angle of the ac output voltage (in the presence of an auxiliary dc power source). The converter can absorb active power from the AC system if the output voltage of the converter lags the AC system voltage and can inject active power into the AC system if the output voltage leads the AC system voltage [14].

#### 2.3 Series compensation

Applications incorporating series compensators within power lines are increasing nowadays, where they are becoming more important multi-purpose devices in power systems. The application of series compensation in transmission lines to increase the ATC by changing the line reactance has been proposed and implemented in high voltage transmission networks across the world [15, 16]. This provides a cost effective and fast solution which can have environmental benefits by reducing the need for the construction of new power lines. Additionally, series compensation can improve both power system stability and voltage stability as are explained in subsection 2.3.1 and 2.3.2.

#### 2.3.1 Improvement of power system stability

Because of the difficulties of building new transmission or distribution lines it is desirable to utilize existing power lines as much as possible. However there are some limitations and requirements which must be met for the proper operation of the system. Power system stability is one of these important issues that must be considered.

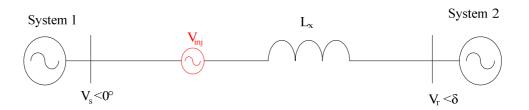

Power transfer between two buses in a power system (with ignored line resistance) is described by the equation (2.1)

$$P_{\rm sr} = \frac{V_{\rm s} V_{\rm r} \sin \delta}{X_{\rm L}} \tag{2.1}$$

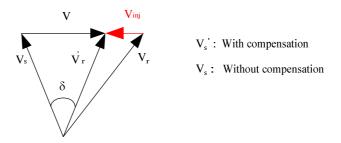

where  $V_s$  and  $V_r$  are the rms bus voltages (Fig.2.5) and  $\delta$  is the load angle (i.e. the phase angle between the sending end voltage  $V_s$  and receiving end voltage  $V_r$ .  $X_L$  is the reactance of the line and  $P_{sr}$  represents the received power at the destination bus.  $X_L$  could be altered by using fixed capacitor type of series compensation. With the insertion of the compensator,  $X_C$  is inserted into line and (2.1) can be rewritten as:

$$P_{sr} = \frac{V_s V_r \sin \delta}{X_L - X_C}$$

$$System 1 \qquad \qquad System 2$$

$$V_1 \qquad \qquad V_2$$

$$< 0^{\circ} \qquad < \delta$$

Fig.2.5: Two bus power system

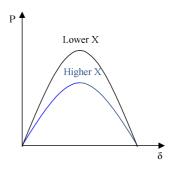

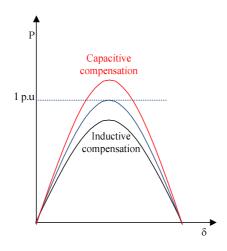

Fig.2.6 shows the amount of transmitted power versus the load angle ( $\delta$ ) for two different line reactances. Compensation of line reactance increases the capability of power transmission through the line. Therefore it can be concluded that if the transmission of a certain amount of power can cause instability in an uncompensated system, the compensated system would be more stable and more likely to be able to handle the extra power transmission.

Fig. 2.6: Power transmission versus the phase angle with different amount of compensation

#### 2.3.2 Improvement of voltage stability

The stability of system voltage in a power system can be affected by the amount of transmitted power. The improvement in system voltage stability as a result of reactance variation has been well argued in [8, 17].

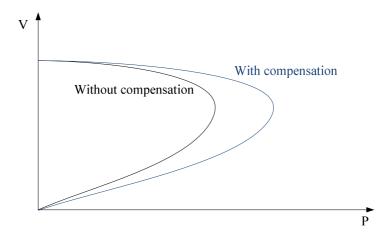

It has been shown that series compensation can even enhance the transient stability of the system [17]. Fig.2.7 shows the power-voltage characteristics of the line with and without compensation. This figure shows how the demanded active power (horizontal axis of the power-voltage characteristics) can be delivered to the load with a lower voltage drop at the receiving end bus in the compensated system.

Fig.2.7: Line power-voltage characteristics

#### 2.4 Fixed Series Capacitor Compensation (Series compensation)

Series compensators can be categorised into fixed series capacitor and power electronics based devices. In the fixed series capacitor simply a capacitor has been inserted in series through the line and alters the line reactance as shown in Fig.2.8.

Fig.2.8: Compensation of line reactance

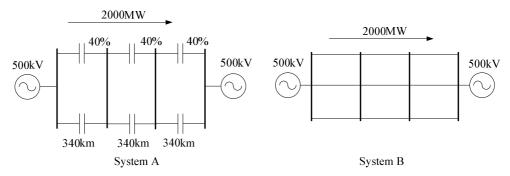

As a result of compensation, more transmission capacity will be available and more active power can potentially be delivered to the load. Without line compensation, a new line may be required to transmit the increased power demand. In a case study carried out

by ABB [18], two systems were considered for transmitting 2000 MW, as shown in Fig.2.9.

System A with two parallel 500 kV lines, each compensated by 40% and system B, with three parallel 500 kV lines without compensation.

Fig.2.9: Two possible solutions for transmitting 2000 MW

The total implementation cost of system A was found to be 35% less than system B. System A also enjoyed other environmental benefits in terms of generating fewer "right of way" issues than system B.

Although high percentage compensation of transmission lines seems to be economically efficient, the compensation level must not approach 100%. If this were to be the case, fault levels would be very high and line current and power flow would be highly vulnerable to any network voltage changes. Furthermore, it would make the protection system more complicated. In practice, the maximum recommended level of compensation is about 80% [19].

#### 2.4.1 Power topologies of fixed series compensator

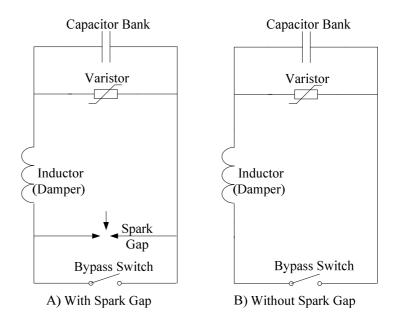

Series capacitors must be combined with other equipment in order to make them controllable while they are being used to compensate the power system [20, 21]. Another issue is the high voltages across the capacitors in case of a short circuit fault. For economic reasons, capacitors cannot be designed to withstand such high voltages and they must be protected against such conditions. Two topologies (Figs.2.10) have been employed in the past to achieve this [19], [21].

Fig.2.10: Power topologies for series capacitor connection

The circuits consist of the following components:

- Capacitor bank: this is the main component of the series compensator circuit and

is constructed using parallel and series connection of capacitors to meet the

required MVAr, voltage and current ratings.

- Damping circuit: made of a reactor (mainly air cored) to restrict the current which can be generated by the bypass switch or spark gap.

- Metal Oxide Varistor (MOV): protects the series capacitors from any possible over voltages before the bypass switch operates.

- Bypass switch: to bypass the capacitors (can be of SF6 type).

- Spark gap: to bypass the capacitor bank in case the energy absorption capability

of the varistor is exceeded.

The short circuit level (SCL) of the compensated system will increase as a result of the line reactance reduction. High SCLs will lead to high fault currents and this will put a high voltage stress across the series capacitors. For this reason some protection is needed for the capacitors. The Spark Gap bypasses the capacitor when an over voltage appears across the capacitor. The stored energy in the capacitor will then be absorbed by the damping reactor. By closing the bypass switch, the Spark Gap will be bypassed and the current will pass through the switch. Finally, when the current drops back to its' normal value the capacitor is reinstated and compensation is resumed. The minimum and maximum reinsertion times for the topology shown in Fig.2.10 (A) are 200ms and

400ms, respectively [19]. In Fig.2.10, the MOV has a nonlinear characteristic with a high resistance for the voltages below the protective level and a lower resistance for voltages above this level. For this reason, immediately after overvoltage across the capacitor the varistor quickly initiates conduction and bypasses the capacitor. After current returns to its normal value, varistor conduction will cease and this will reinsert the capacitor into the line [19]. The Spark Gap comes into operation to bypasses the varistor and capacitors current diverted in case the energy absorption capability of the varistor is exceeded.

## 2.4.2 Point of connection of fixed series capacitors

The point of connection for series capacitors is important in terms of cost, reliability, short circuit level and accessibility. In practice, the midpoint of the line as well as the sending and receiving end points are recommended for the installation of series capacitors. It would be cheaper to install all the compensation at the sending end or at the receiving end of the line but this would complicate the requirements of some protection systems such as distance protection schemes. To avoid any complications with the protection system, it is more convenient to install the capacitor bank in the middle of the line [19] despite the extra cost involved.

## 2.5 Thyristor Switched Series Capacitors (TSSC)

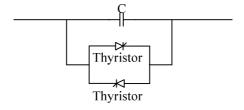

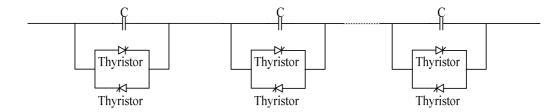

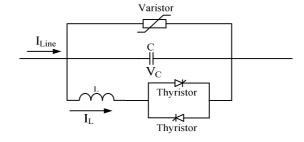

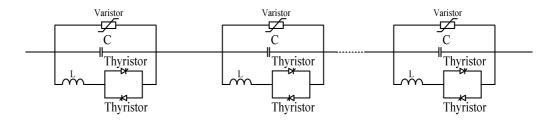

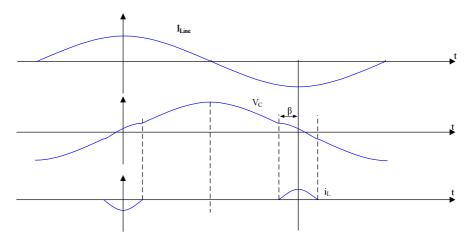

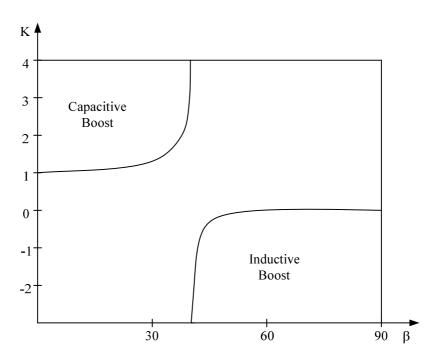

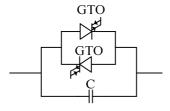

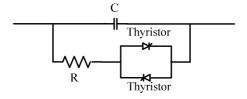

A thyristor switched series capacitor (TSSC) compensator [22] is comprised of a capacitor in parallel with two anti-parallel connected thyristors as shown in Fig.2.11.

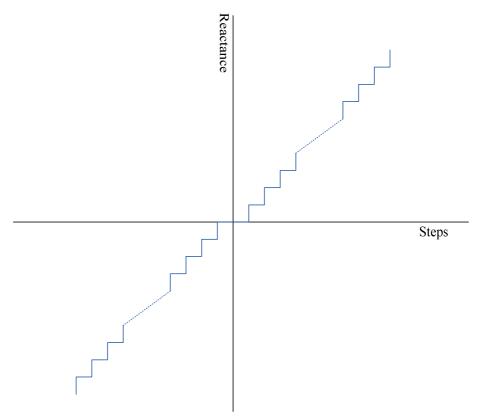

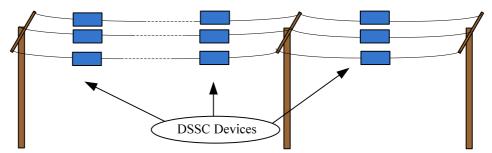

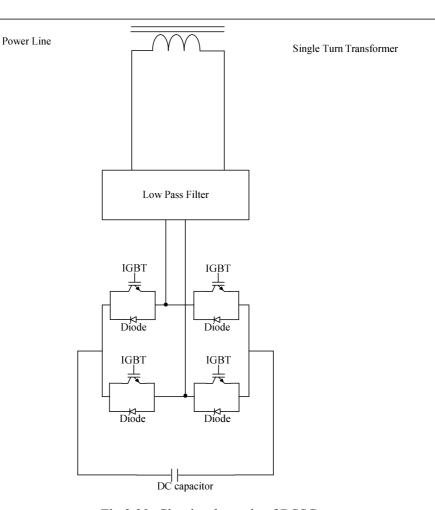

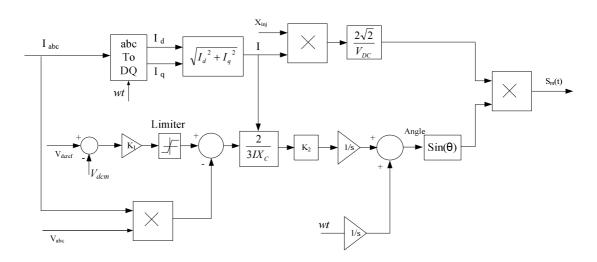

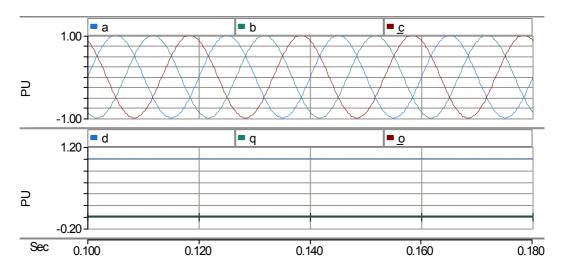

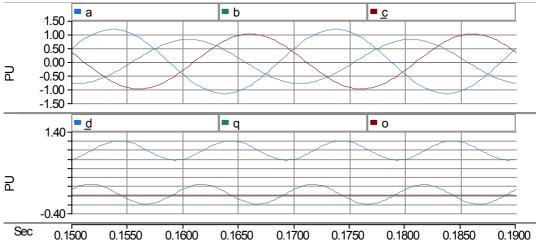

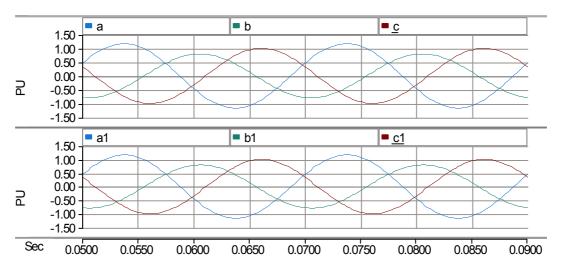

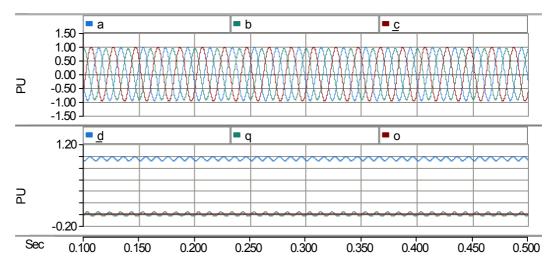

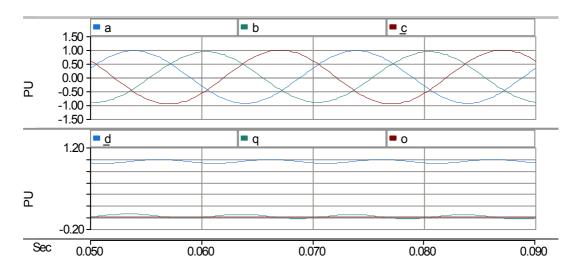

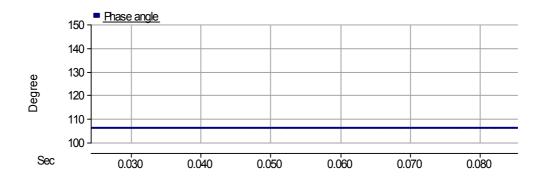

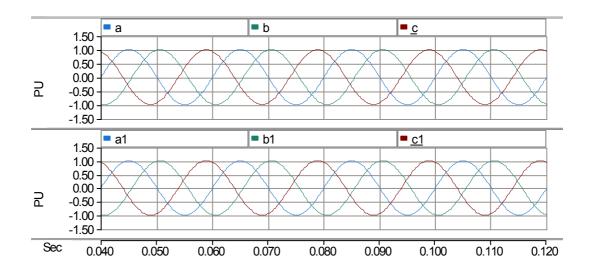

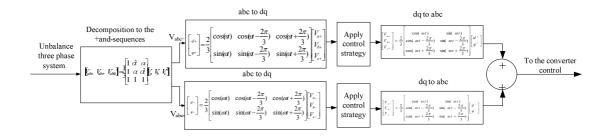

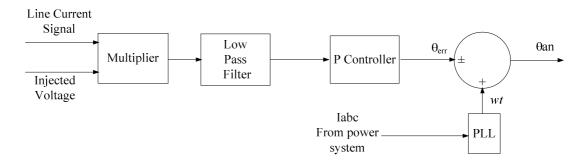

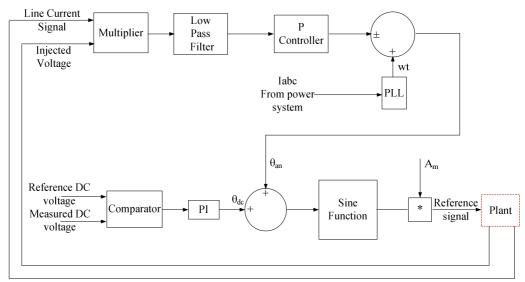

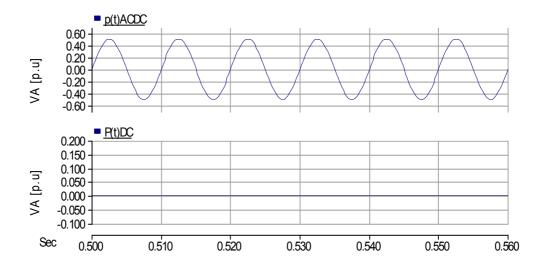

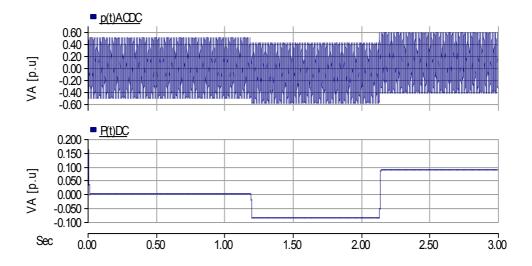

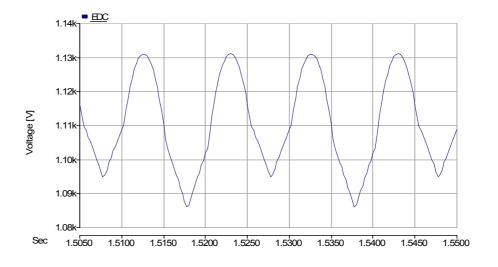

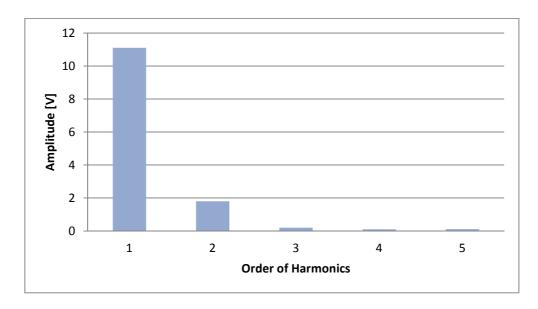

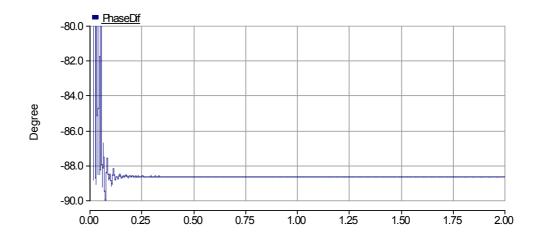

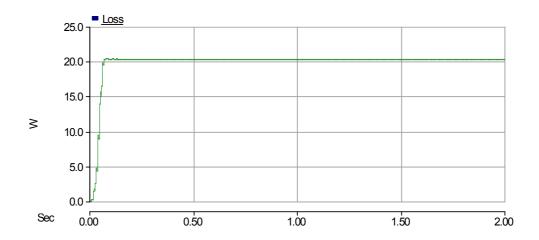

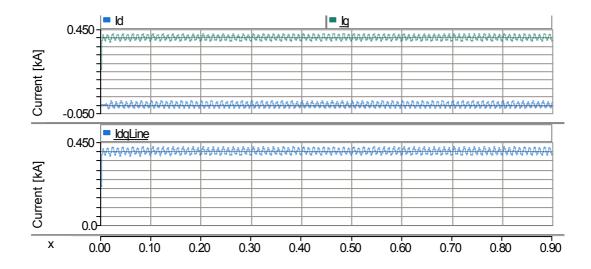

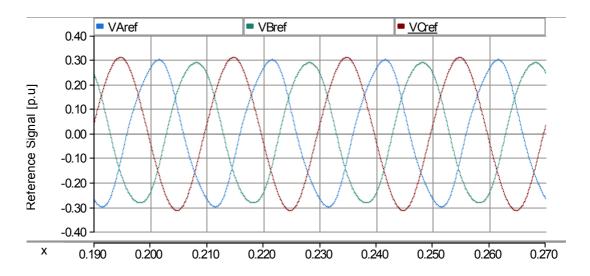

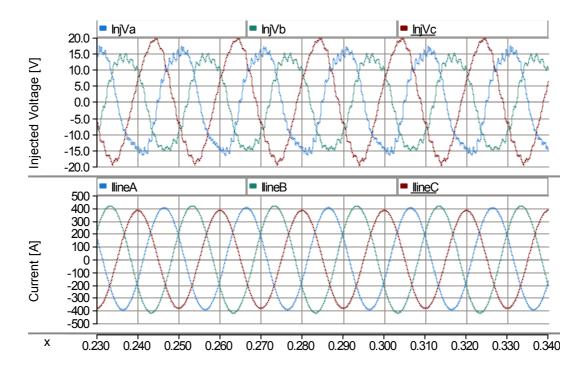

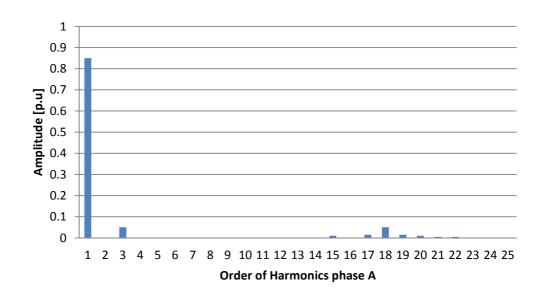

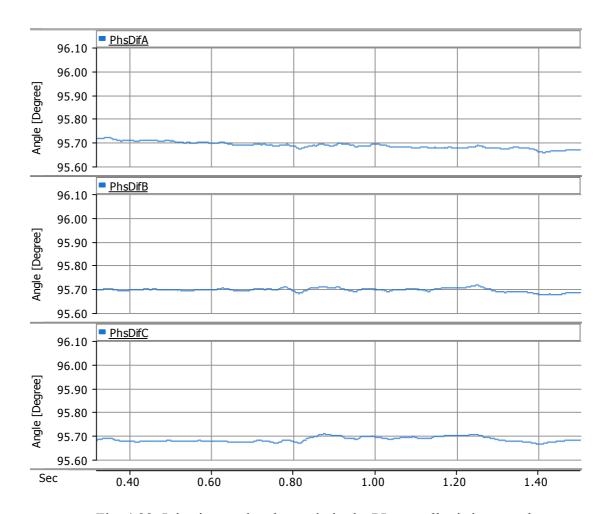

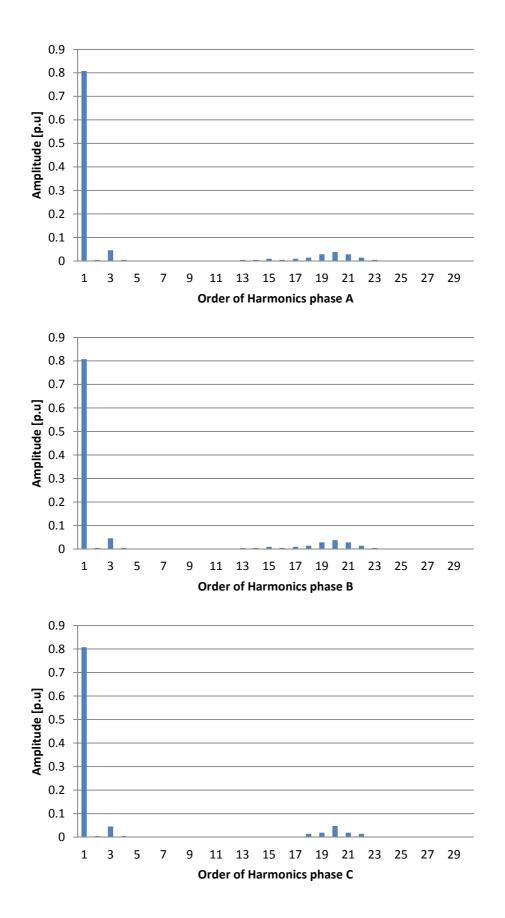

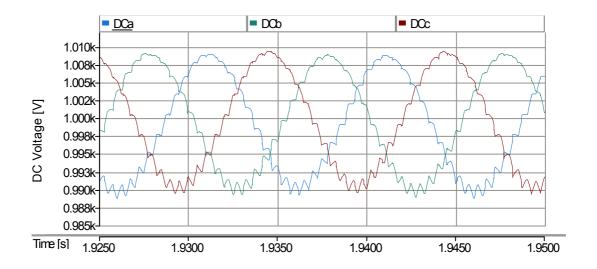

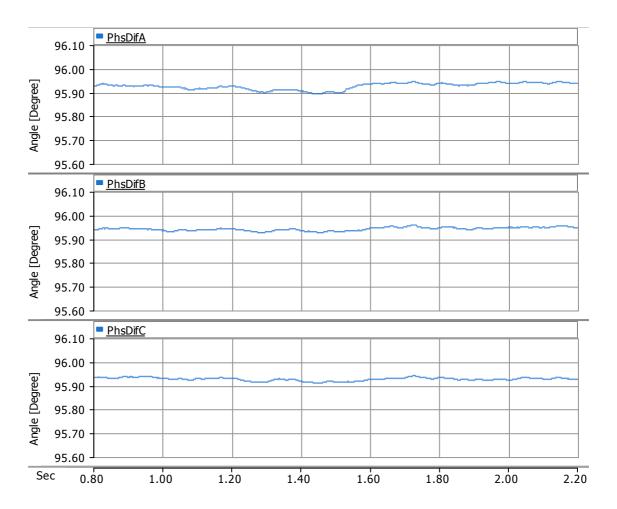

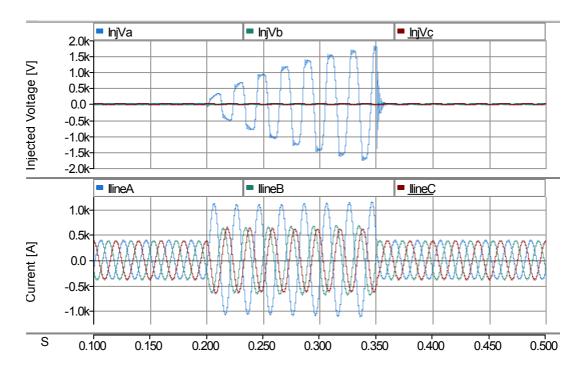

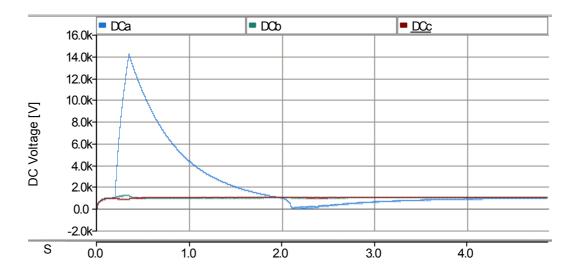

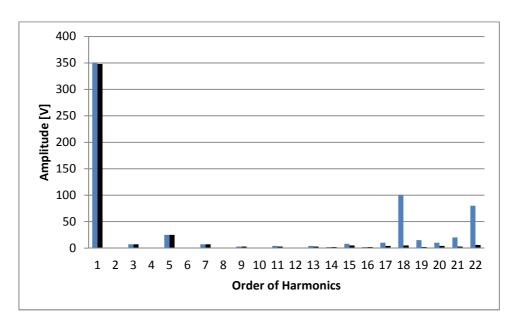

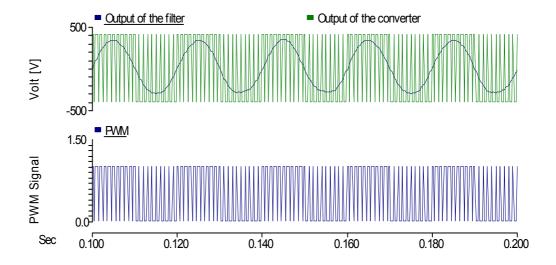

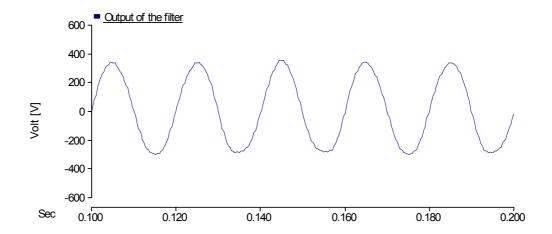

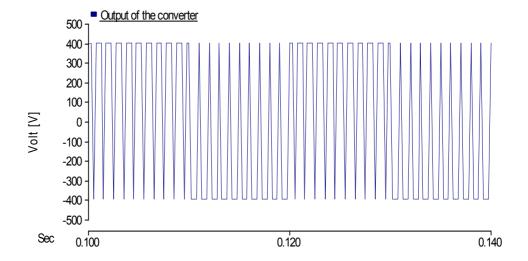

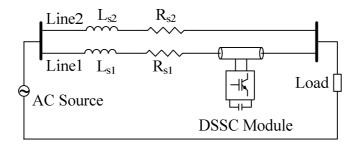

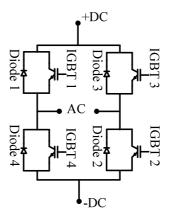

Fig.2.11: Power topology of TSSC