## Silicon Nanowire: Fabrication, Characterisation and Application

Sami Ramadan

Doctor of Philosophy

Submitted in fulfilment for the degree of Doctor of Philosophy in Electrical and Electronic Engineering

July 2015

## **Abstract**

This thesis focuses on the fabrication considerations and the characterisation of silicon nanowires and their integration into chemical sensors. One aim is to optimize a top-down fabrication process for silicon nanowires, in particular the methods that use optical lithography, wet etching and thermal oxidation. The main concerns here are to achieve a reproducible and high yield fabrication process and to obtain a controllable structure. Extensive work was carried out to study the parameters that affect the repeatability of the process. The properties of silicon nitride films, the oxidation method and the characteristics of the anisotropic etchant were found to be key parameters affecting the reproducibility of the process. Several silicon nitride films were deposited under various conditions and their optical properties were tested before and after thermal oxidation. It was found that the oxynitride thickness depends on the refractive index of the nitride film: the lower the refractive index, the thinner the oxynitride. Then an etching process was developed to selectively etch the oxidised silicon nitride over silicon dioxide. The etching process included two steps: firstly ion milling to remove the oxynitride film and secondly using boiling phosphoric acid to strip the silicon nitride film. Nitriderich silicon nitride films exhibited higher etching selectivity over silicon dioxide compared with silicon-rich silicon nitride. Based on the etch selectivity, oxynitride thickness, and silicon dioxide thickness the maximum thickness of silicon nitride film that can be used to act as a mask during the fabrication of silicon nanowires was determined. The impact of oxidation method on the reliability of the process was studied, and SOI and bulk silicon samples were oxidised at the same temperature and time using lamp-based RTP radiation and also a furnace with resistive heating. The results showed that the SOI sample is colder than the bare silicon sample when both were heated using the lamp-based RTP. This effect was considered during the fabrication of silicon nanowires to obtain a reliable process. Comprehensive experimental measurements were carried out to compare the characteristics of Tetra-Methyl Ammonium Hydroxide (TMAH) and Potassium Hydroxide (KOH) etching to optimise the fabrication process. The use of TMAH was found to lead to a more reliable process.

Another aim of the project was to characterise the fabricated devices, and for this the contact properties and the electrical properties of the silicon nanowires needed to be evaluated. Extensive electrical measurements were carried out to study the thermal stability and ohmic contact formation for the silicon nanowire. Three metallization schemes were studied: Al/Ti, Al/W/Ti and Al/Ti/AlO<sub>x</sub>. All these exhibited ohmic contact to the nanowires. However, Al/Ti/Si and Al/W/Ti/Si were found to be unstable after 425 °C RTP annealing. Al/Ti/AlO<sub>x</sub>/Si withstood this level of temperature but the contact resistance was about ten times higher than that of Al/W/Ti. The electrical resistivity of the silicon nanowires was then studied; it was found that the measured electrical resistivity decreases with the nanowire thickness. Several models were then developed to explain the apparent increase in resistivity. It was suggested it can be largely attributed to the reduction of the conductive area of the nanowire due to interface traps.

Finally, a silicon nanowire sensor was designed and fabricated, and this sensor was used to detect the changes in pH. The preliminary results showed that the sensor detected the change of pH in the buffer solution. However, reliability and yield were low, which was assumed to be due to the large parasitic current between the source/drain and the buffer solution.

## Acknowledgments

I would like to express my deep gratitude to my supervisor, Prof. Anthony O'Neill, for his guidance, support and constant advice throughout my research. I have been privileged to work under his supervision.

Warm gratitude to Konstantin Vasilevskiy, Gary Potts for their help in clean room; Kelvin Kwa and Jonathan Goss for their valuable advice. For interesting collaborative experience and work on the chemical sensor, I am very grateful to Christopher Adams and Jennifer Hannant from QuantuMDx. Thanks also to Benjamin Horrocks for his help during my work in the Chemistry school.

A bunch of wonderful people have been very helpful throughout my research and to whom I shall forever remain grateful. Shahin Mojarad, Nikhil Ponon and Niveen Kassem, thank you very much for sharing inspiring discussions, critical observations, help and for your true friendship.

I am equally grateful to all the nice PhD students and postdoc researchers whom I have met and had the pleasure to work with. The list is very long but I will particularly thank: Peter King, Carl Dale, Erhan Arac, Enrique Escobedo-Cousin, Ferran Urena, Amit Tiwari, Meaad Al-Hadidi, Raied AL-Hamadany, Bob Xu, Srinivas Ganti, Mohd Rashid and Sandip Roy for their interesting discussions and help.

For a scholarship to pursue my postgraduate studies, I am grateful to Damascus University in Syria.

I am most grateful to my late father of loving memories for challenging me as a child, and for thought provoking discussions; my beloved mother for her unconditional love, unwavering help and support; my most loving siblings, close friends and relatives for keeping me entertained, love and encouragement.

## Abbreviations

AFM Atomic Force Microscopy

ALD Atomic Layer Deposition

BHF Buffered Hydrofluoric Acid

BOX Buried Oxide

HF Hydrofluoric Acid

IPA Isopropyl Alcohol

IR Infrared Radiation

ISFET Ion Selective Field-Effect Transistor

KOH Potassium Hydroxide

LPCVD Low Pressure Chemical Vapour Deposition

MOSFET Metal Oxide Semiconductor Field-Effect Transistor

NMP N-Methylpyrrolidone

PECVD Plasma Enhanced Chemical Vapour Deposition

PVD Physical Vapour Deposition

RIE Reactive Ion Etching

RMS Root Mean Square

SEM Scanning Electron Microscope

SOI Silicon on Insulator

TEM Transmission Electron Microscope

TLM Transfer Length Method

TMAH Tetra-Methyl Ammonium Hydroxide

VLS Vapour Liquid Solid

## Contents

| Abstract i           |          |                                                    |    |

|----------------------|----------|----------------------------------------------------|----|

| Acknowledgements iii |          |                                                    |    |

| Abbr                 | eviation | ıs                                                 | V  |

|                      |          |                                                    |    |

|                      |          | troductiontroduction                               |    |

| 1.1                  |          | ound                                               |    |

| 1.2                  |          | overview                                           |    |

|                      |          | licon Nanowire Background                          |    |

| 2.1                  |          | tion methods                                       |    |

| 2.1                  | 2.1.1    | Bottom-up approaches.                              |    |

|                      | 2.1.2    | Top-down approaches.                               |    |

| 2.2                  |          | of semiconductor nanowires.                        |    |

| 2.2                  | 2.2.1    | Quantum confinement.                               |    |

|                      | 2.2.2    | Size effect.                                       |    |

|                      | 2.2.3    | Ionization energy.                                 |    |

|                      | 2.2.4    | Mobility                                           |    |

| 2.3                  |          | ations of silicon nanowire.                        |    |

|                      | 2.3.1    | Nanowire thermoelectrics.                          |    |

|                      | 2.3.2    | Piezoresistive silicon nanowire.                   |    |

|                      | 2.3.3    | Silicon nanowire-bio interface.                    |    |

|                      | 2.3.4    | Biosensing application.                            |    |

| 2.4                  | Summa    | ry                                                 |    |

| Refer                |          | ······································             |    |

| Chap                 | ter 3 Fa | abrication of Silicon Nanowire                     | 21 |

| 3.1                  | Introdu  | ction                                              | 20 |

| 3.2                  | Spin-or  | n-doping SOD                                       | 21 |

|                      | 3.2.1    | Doping background                                  | 21 |

|                      | 3.2.2    | SOD process                                        |    |

|                      | 3.2.3    | SOD removal                                        | 22 |

|                      | 3.2.4    | Doping Profile                                     | 23 |

| 3.3                  | Fabrica  | ation of silicon nanowires                         | 27 |

|                      | 3.3.1    | Fabrication process steps.                         | 27 |

|                      | 3.3.2    | Nanowires profiles                                 |    |

|                      |          | 3.3.2.1 AFM basics                                 | 29 |

|                      |          | 3.3.2.2 Modelling the tip effect on nanowire width | 30 |

|                      |          | $\epsilon$                                         | 32 |

|                      | 3.3.3    |                                                    | 33 |

|                      | 3.3.4    |                                                    | 34 |

|                      |          |                                                    | 34 |

|                      |          | 3.3.4.2 Size reduction by thermal oxidation        |    |

| 3.4                  | Fabrica  | tion considerations of silicon nanowires           | 39 |

|       | 3.4.1     | Characte   | risation of silicon nitride films                                   | . 39 |

|-------|-----------|------------|---------------------------------------------------------------------|------|

|       |           | 3.4.1.1    | Deposition rate and etch rate                                       | . 41 |

|       |           | 3.4.1.2    | Optical properties of silicon nitride                               | 41   |

|       |           | 3.4.1.3    | Film behaviour during thermal oxidation                             |      |

|       |           | 3.4.1.4    | Etching of thermally oxidised silicon nitride                       | 47   |

|       |           | 3.4.1.5    | Silicon Nitride Selection for nanowire process                      | . 50 |

|       | 3.4.2     | Characte   | ristics of thermal oxidation                                        | . 52 |

|       |           | 3.4.2.1    | RTP vs Furnace                                                      |      |

|       |           | 3.4.2.2    | The robustness of sidewall oxide                                    | . 56 |

|       | 3.4.3     | Characte   | ristics of TMAH and KOH for nanowire fabrication                    | . 57 |

|       |           | 3.4.3.1    | Etch rate and surface morphology                                    | 59   |

|       |           | 3.4.3.2    | Silicon dioxide and silicon nitride etch rates                      | . 61 |

|       |           | 3.4.3.3    | Undercut rate                                                       | 62   |

|       |           | 3.4.3.4    | Anisotropic etching on fabrication of nanowires                     | . 62 |

|       |           | 3.4.3.5    | First anisotropic etching step                                      | . 62 |

|       |           | 3.4.3.6    | 2nd anisotropic etching step                                        | . 64 |

| 3.5   | Null res  | sults      |                                                                     | . 67 |

| 3.6   | Summa     | ry         |                                                                     | 70   |

| 3.7   | Future v  | work       |                                                                     | . 71 |

| Refer | ences     |            |                                                                     | 73   |

| Chap  | oter 4 El | ectrical T | ransport in Silicon Nanowire                                        | . 77 |

| 4.1   | Introdu   | ction      |                                                                     | . 77 |

| 4.2   | Electric  | al contact | S                                                                   | 77   |

|       | 4.2.1     | Energy le  | evel alignment and band bending                                     | 78   |

|       | 4.2.2     |            | ransport mechanism for metal/semiconductor interface                |      |

|       | 4.2.3     | _          | ontact                                                              |      |

|       | 4.2.4     | Choice of  | f material for ohmic contacts                                       | 81   |

|       | 4.2.5     | Electrica  | l characterisation of contacts                                      | 81   |

|       |           |            | Experimental results: microwires                                    |      |

|       |           | 4.2.5.2    | <del>-</del>                                                        |      |

| 4.3   | Electric  | al charact | erisations of silicon nanowire                                      |      |

|       | 4.3.1     | Effective  | electrical resistivity of a nanowire                                | . 92 |

|       | 4.3.2     | Nonlinea   | rity behaviour of current-voltage curves in four probe              |      |

| 4.4   | Summa     |            |                                                                     |      |

| 4.5   |           | •          |                                                                     |      |

|       |           |            |                                                                     |      |

|       |           |            | Modelling of Resistivity in Triangular Silicon Nanowires            |      |

| 5.1   |           | •          | g                                                                   |      |

| 5.2   |           |            | listribution                                                        |      |

| 5.3   |           |            | due to interface traps                                              |      |

|       | 5.3.1     |            | on of the potential inside the neutral region $\psi_0$              |      |

|       | 5.3.2     |            | on of depletion region $r_{qdep}$                                   |      |

|       | 5.3.3     |            | on of the potential inside the depletion region $\psi_r$            |      |

|       | 5.3.4     |            | on of effective carrier density $n_{eff}$ and effective resistivity |      |

|       | 5.3.5     |            | resistivity in silicon nanowire: fitting the experimental           | 11)  |

|       |           |            | resistivity in sincon nanowire. Inting the experimental             |      |

|       | чиш       | 121        |                                                                     |      |

| 5.4   | Effect of                      | of surface scattering                                                  | 122 |

|-------|--------------------------------|------------------------------------------------------------------------|-----|

| 5.5   | Effect of surface roughness 12 |                                                                        |     |

| 5.6   | Summary 12                     |                                                                        |     |

| 5.7   | Future                         | work                                                                   | 129 |

| Refer | ences                          |                                                                        | 130 |

| Chap  | ter 6 Si                       | licon Nanowire Field-Effect Transistors in Aqueous Media               | 132 |

| 6.1   |                                | -sensitive field-effect transistor (ISFET)                             |     |

| 6.2   |                                | design and fabrication.                                                |     |

| 6.3   | pH measurements                |                                                                        |     |

|       | 6.3.1                          | Measurement set-up                                                     | 137 |

|       | 6.3.2                          | Dry test.                                                              | 138 |

|       | 6.3.3                          | pH response                                                            |     |

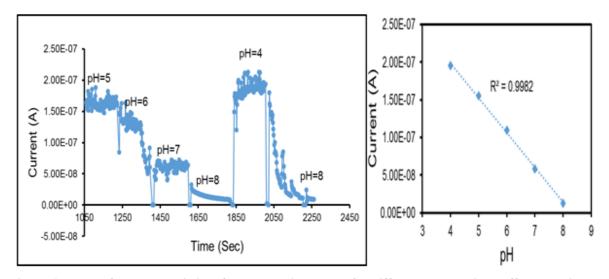

|       | 6.3.4                          | pH dynamic measurements                                                |     |

| 6.4   | Null res                       | sults                                                                  | 140 |

|       | 6.4.1                          | Parasitic leakage current between the source/drain and buffer solution | 140 |

|       | 6.4.2                          | Voids in the metal electrodes.                                         | 141 |

| 6.5   | Summa                          | ry                                                                     | 142 |

| 6.6   |                                | work                                                                   | 142 |

| Refer | ences                          |                                                                        | 143 |

|       |                                |                                                                        | 145 |

| 7.1   | Concer                         | ning the optimization of the fabrication process of silicon nanowire   | 145 |

|       | 7.1.1                          | Reproducibility and yield.                                             | 145 |

|       | 7.1.2                          | Controllability of the nanowire.                                       | 146 |

| 7.2   | Charact                        | terisation of devices                                                  | 147 |

| 7.3   |                                | of device properties                                                   | 148 |

| 7.4   |                                | ire integration for chemical sensing                                   | 148 |

| 7.5   |                                | mendations for future research                                         | 148 |

| Appe  |                                |                                                                        | 150 |

|       | ndix B                         |                                                                        | 151 |

## List of Tables

| Chapter 3   |                                                                                                              |

|-------------|--------------------------------------------------------------------------------------------------------------|

| Table 3.1:  | Oxide thickness ratios, regions A, B, C and D. Regions are defined in Figur                                  |

|             | 3.11(b)                                                                                                      |

| Table 3.2:  | Silicon nitride deposition conditions, deposition rates, thicknesses and etc.                                |

|             | rates in BHF and boiling phosphoric acid (H3PO4)                                                             |

| Table 3.3:  | The refractive indexes of silicon nitride films                                                              |

| Table 3.4:  | Films compassions and refractive indexes of oxidised silicon nitride as                                      |

| T 11 0 7    | function of depth4:                                                                                          |

| Table 3.5:  | The oxynitride and oxide ratios on oxidised silicon nitride to the silicon dioxide thickness on bere silicon |

| Table 3.6:  | dioxide thickness on bare silicon                                                                            |

| 1 able 5.6: | Etch rates of silicon nitride films in boiling H3PO4 after the removal of oxynitride layers                  |

| Table 3.7:  | Etch selectivity of oxidised silicon nitride over silicon dioxide in boiling                                 |

|             | H3PO4 and oxide thickness ratios consumed during the removal of oxid                                         |

|             | and oxynitride layers5                                                                                       |

| Table 3.8:  | Ellipsometry thicknesses results for SOI and Bulk Si samples                                                 |

| Table 3.9:  | AFM thicknesses results for SOI and Bulk Si samples (RTP 1000 °C, 1                                          |

|             | min)                                                                                                         |

| Table 3.10: | Average etch rates of <100> silicon, surface roughness of <100> and <1111                                    |

|             | after TMAH and KOH etching. 59                                                                               |

| Table 3.11: | Etch rates of thermal silicon dioxide and silicon nitride in TMAH and KOH                                    |

| Table 3.12: | Average undercut values 62                                                                                   |

| Table 3.13: | Average nanowire width as a function of 1st KOH etching time (2nd KOH                                        |

|             | adjusted for 4 min at 56 °C)63                                                                               |

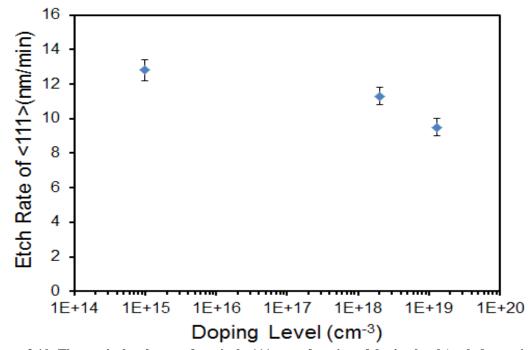

| Table 3.14: | Averages etch rates of <111>6                                                                                |

| Appendix A  |                                                                                                              |

| Table A.1:  | Deposition rate, etch rate and optical property15                                                            |

| Table A.2:  | Etching of thermally oxidised silicon nitride                                                                |

| Appendix B  |                                                                                                              |

| Table B.1:  | Nanowires with Al/Ti and Al/W/Ti contact structures                                                          |

| Table B.2:  | Nanowires with Al/AlOx/Ti contact structure                                                                  |

# List of Figures

| Chapter 2   | 4                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

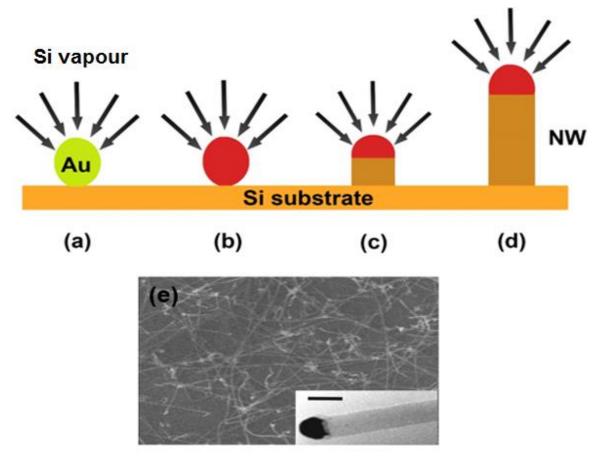

| Figure 2.1: | Vapour-liquid-solid growth mechanism of silicon nanowire: (a) gold nanodroplet on clean surface; (b) eutectic droplet; (c) nucleation; (d) nanowire growth; (e) FESEM image of silicon nanowire grown via a VLS mechanism [5]                                                                                                                                                                                                                  |

| Figure 2.2: | Schematic of nanoimprint lithography process steps                                                                                                                                                                                                                                                                                                                                                                                             |

| Figure 2.3: | Schematic diagram of key fabrication steps of sidewall lithography: (a) deposition of sacrificial layer; (b) conformal deposition of low temperature oxide; (c) selective anisotropic dry etching; (d) subsequent selective anisotropic dry etching                                                                                                                                                                                            |

| Figure 2.4: | Two examples of crystal orientation dependent etching techniques 10                                                                                                                                                                                                                                                                                                                                                                            |

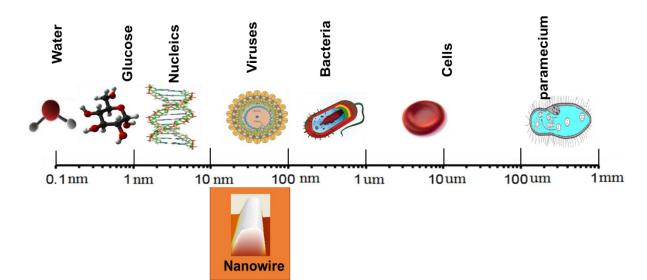

| Figure 2.5: | Scale bar of the size of nanowire compared to biological objects                                                                                                                                                                                                                                                                                                                                                                               |

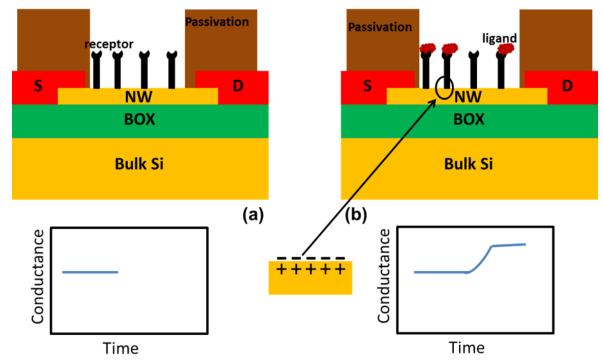

| Figure 2.6: | Basic structure of silicon nanowire biosensor: (a) schematic of a p-type silicon nanowire sensor with receptors and a plot of conductance as a function of time; (b) the nanowires response when negative ligands are attached to the receptors and the change in conductance as a function of time                                                                                                                                            |

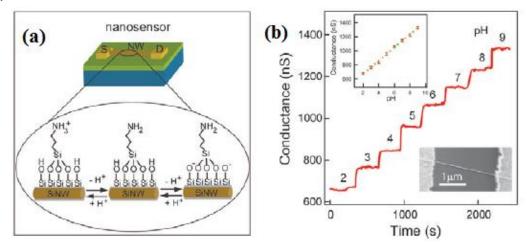

| Figure 2.7: | Silicon nanowire pH sensor: (a) schematic of silicon nanowire surface modified with a 3-aminopropyltriethoxysilane; (b) changes in nanowire conductance as a function of the pH in the solution [58, 59]                                                                                                                                                                                                                                       |

| Chapter 3   | 20                                                                                                                                                                                                                                                                                                                                                                                                                                             |

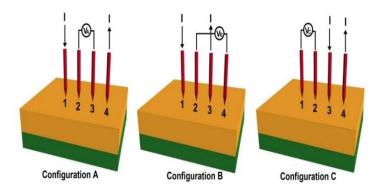

| Figure 3.1: | Schematic of four probe configuration technique                                                                                                                                                                                                                                                                                                                                                                                                |

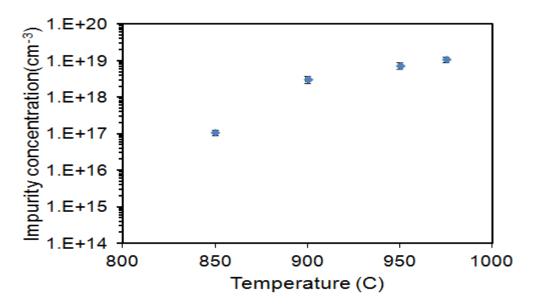

| Figure 3.2: | Average impurity concentrations as a function of RTP pyrometer set point temperature; diffusion time 5 min                                                                                                                                                                                                                                                                                                                                     |

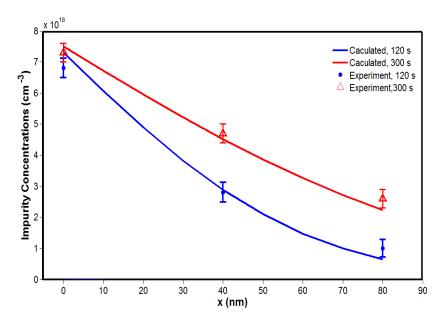

| Figure 3.3: | Impurity concentrations as a function of depth at pyrometer temperature of 975 °C for 120 sec (blue circle); 300 sec (red triangle); 120 sec calculated (blue line) and 300 sec (red line)                                                                                                                                                                                                                                                     |

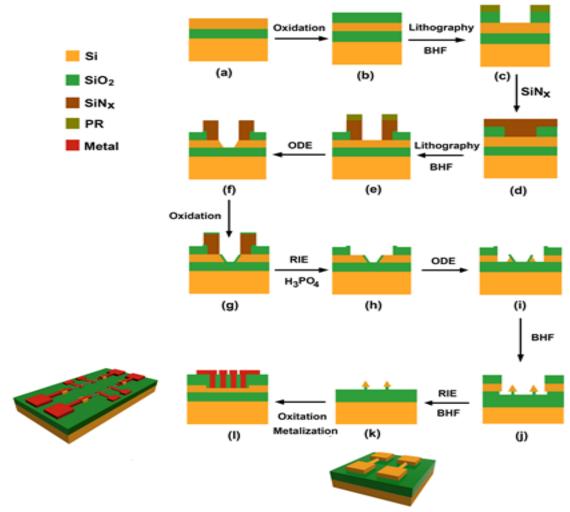

| Figure 3.4: | Process steps for the fabrication of silicon nanowire: (a) Doped SOI; (b) Oxidation; (c) Oxide opening; (d) Deposition of SiNx; (e) SiNx pattern; (f) 1st ODE etching; (g) Sidewall oxidation; (h) SiNx removal; (i) 2 <sup>nd</sup> ODE etching step; (j) Sidewall oxide removal; (k) Nanowire isolation; (l) Metal pattern for nanowire characterisation (with 3D schematic); (m) Metal pattern for nanowires FET characterisation (with 3D) |

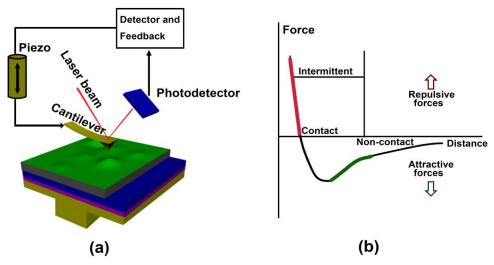

| Figure 3.5: | (a) A basic block diagram of an AFM; (b) the forces between the tip and the surface                                                                                                                                                                                                                                                                                                                                                            |

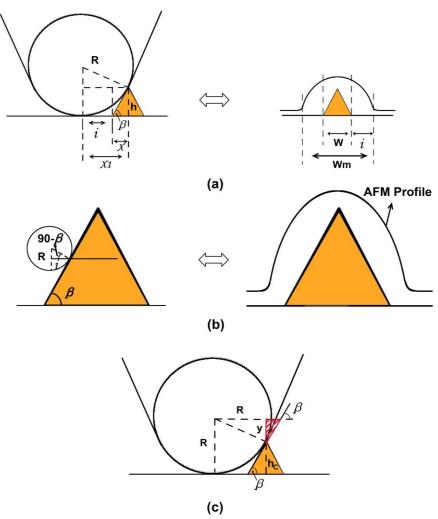

| Figure 3.6: | The convolution effect on the width of nanowire (a) an AFM tip with a radius larger than the thickness of nanowire (left), AFM trajectory (right);                                                                                                                                                                                                                                                                                             |

|               | (b) an AFM tip with a radius smaller than the thickness of nanowire (left), AFM trajectory (right); (c) the critical dimension of nanowire hc= R-Y31   |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

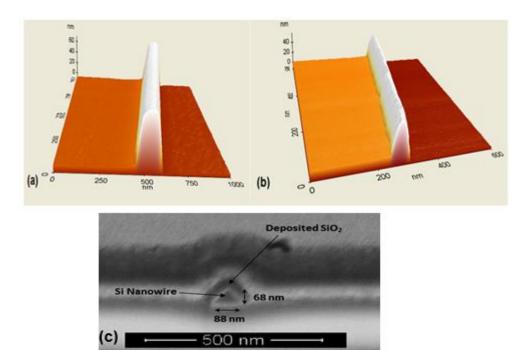

| Figure 3.7:   | (a) 3D images of silicon nanowires with a trapezoidal cross-section; (b) 3D images of silicon nanowires with a triangular cross-section; (c) SEM image |

|               | of a Si nanowire with a triangular cross-section [1]                                                                                                   |

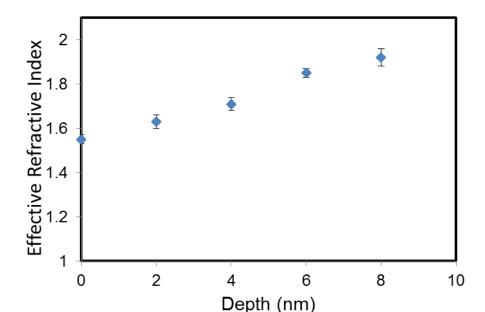

| Figure 3.8:   | The refractive index of oxidised RF sputtered silicon nitride as a function                                                                            |

|               | of depth (The process gas is nitrogen and the as-deposited refractive index                                                                            |

|               | is 1.9)                                                                                                                                                |

| Figure 3.9:   | Schematic of the process steps involved during in situ size reduction of                                                                               |

| <b>-</b> 10   | nanowires                                                                                                                                              |

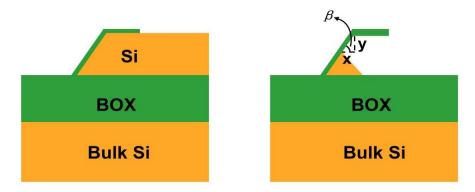

| Figure 3.10:  | The vertical etch rate of vertical <111> as a function of doping level 35                                                                              |

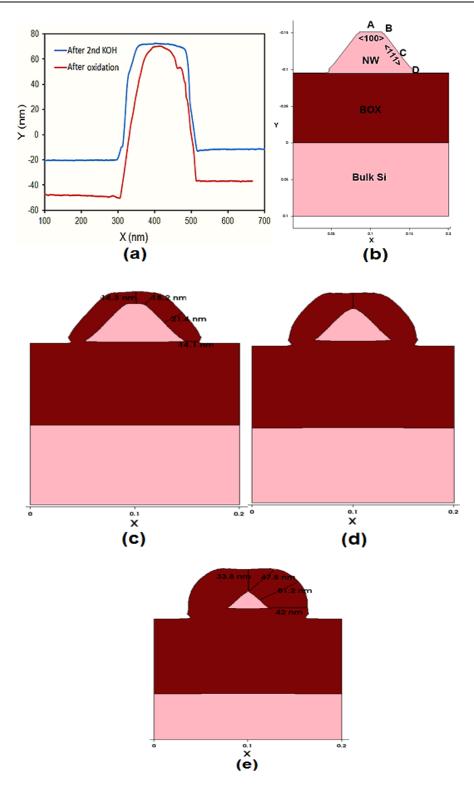

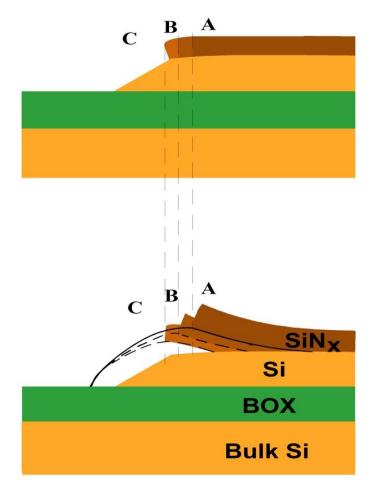

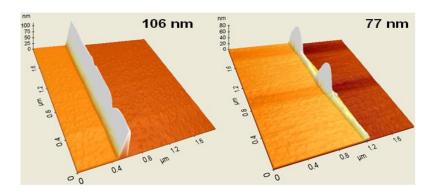

| Figure 3.11:  | Size reduction of silicon nanowire by using thermal oxidation (a)                                                                                      |

|               | experimental results before and after 930 °C in RTP and 20 sec in BHF; (b)                                                                             |

|               | simulated structure: (c) after 30 min oxidation; (d) af.ter 60 min; (e) after 120 min. 38                                                              |

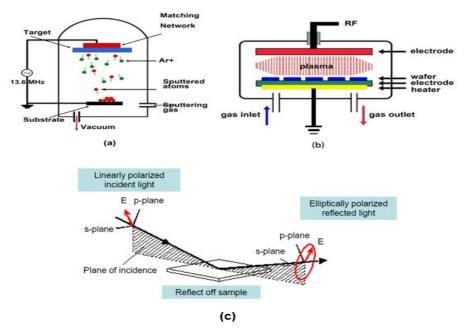

| Figure 3.12:  | Schematic diagram of: (a) RF sputter; (b) PECVD; (c) ellipsometry                                                                                      |

| 1 iguic 5.12. | experiment                                                                                                                                             |

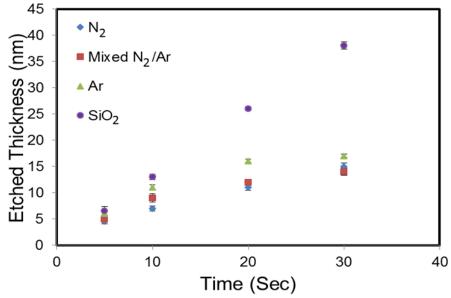

| Figure 3.13:  | The etch behaviour of oxidised silicon nitride and silicon dioxide in BHF                                                                              |

| 8             | (N <sub>2</sub> , mixed N <sub>2</sub> /Ar and Ar are the process gases)                                                                               |

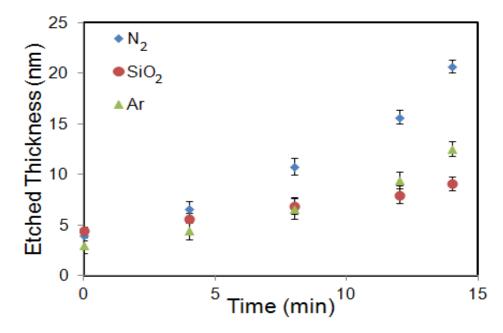

| Figure 3.14:  | The etch behaviour of oxidised silicon nitride and silicon dioxide after                                                                               |

|               | etching in boiling H3PO4 followed 4 sec BHF (N2 and Ar are the process                                                                                 |

|               | gases)                                                                                                                                                 |

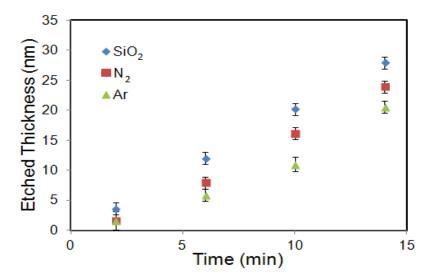

| Figure 3.15:  | The etch behaviour of oxidised silicon nitride and silicon dioxide in ion                                                                              |

|               | milling with argon at DC=530 V, P=12 mtorr                                                                                                             |

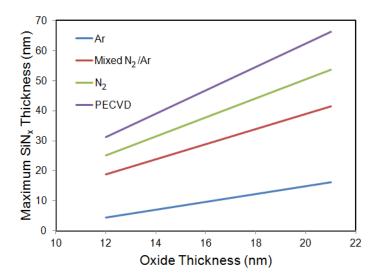

| Figure 3.16:  | The maximum thickness of silicon nitride mask for different types of silicon                                                                           |

| F' 0.15       | nitride films as a function of sidewall oxide                                                                                                          |

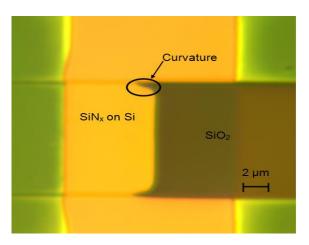

| Figure 3.17:  | Optical microscopy image shows that an insufficient nitride mask causes a                                                                              |

|               | change of etch direction during ODE etching which is seen as curvature and                                                                             |

| Figure 3.18:  | discontinues at the corners                                                                                                                            |

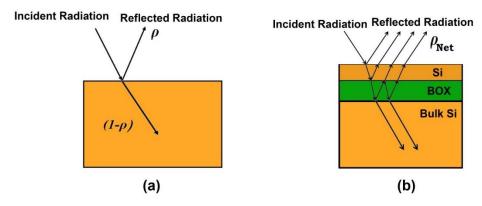

| Figure 3.19:  | Schematic of (a) KTT configuration, (b) thermal oxidation furnace                                                                                      |

| 11guic 5.17.  | SOI wafer                                                                                                                                              |

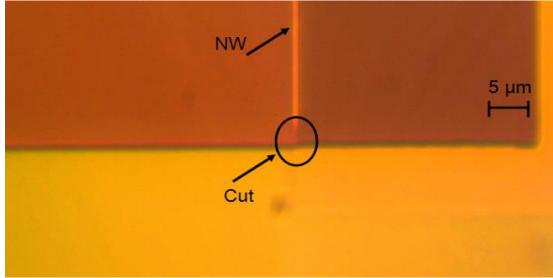

| Figure 3.20:  | Optical microscopic image shows a cut at the corner of nanowire56                                                                                      |

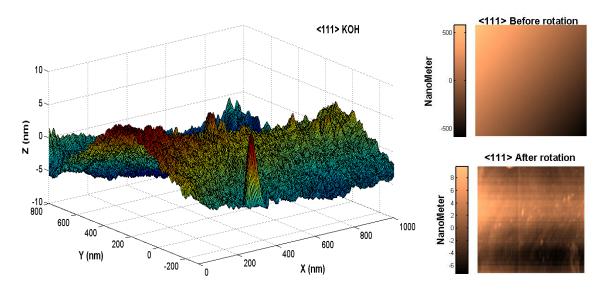

| Figure 3.21:  | 3D image of <111> silicon surface after KOH etching (left) and 2D image                                                                                |

| C             | of the same surface before and after rotation (Rq=3.2 nm)                                                                                              |

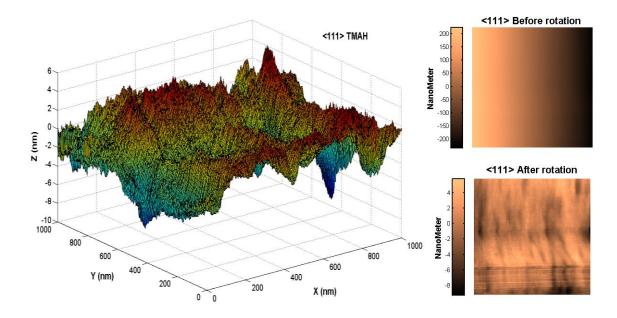

| Figure 3.22:  | 3D image of <111> silicon surface after TMAH etching (left) and 2D image                                                                               |

|               | of the same surface before and after rotation (Rq= 2.4                                                                                                 |

|               | nm)61                                                                                                                                                  |

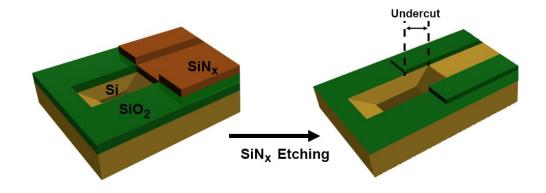

| Figure 3.23:  | The fabrication steps that involved in the undercut measurements 62                                                                                    |

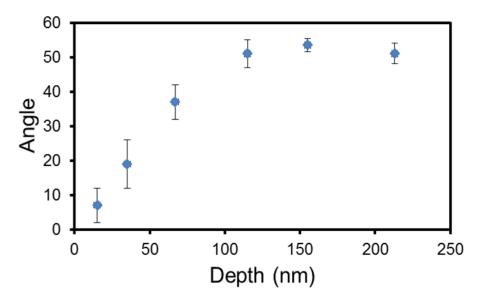

| Figure 3.24:  | The effect of short etching time on the angle between <100> and <111>                                                                                  |

|               | planes 63                                                                                                                                              |

| Figure 3.25:  | Schematic shows the impact of the position of nitride film on lateral                                                                                  |

| Eigung 2 26   | oxidation [51]                                                                                                                                         |

| Figure 3.26:  | Silicon nanowires after 5 min (left) and 8 min (right) in 2nd KOH 65                                                                                   |

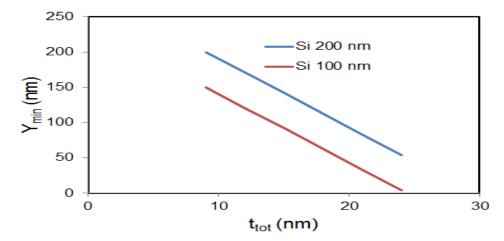

| Figure 3.27:  | The minimum thickness of nanowires (Ymin) that can be obtained with                                                                                    |

|               | KOH; Kt_tot=0.7t_tot, t_c=5 nm calculated for 27 nm nitride thickness66                                                                                |

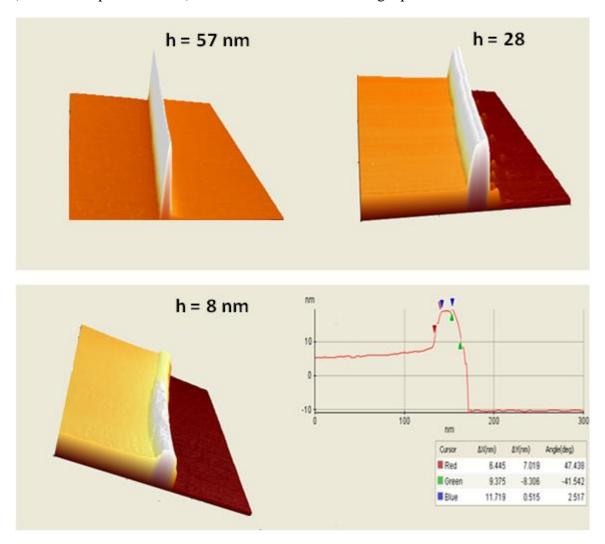

| Figure 3.28: | Different sizes nanowires formation by using in situ size reduction. (Sub 10 nm is obtained)                                                                                                                                                                                                                                                                                                                      |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.29: | Schematic of nanowire profile after 2nd ODE etching; (a) and (b) should have the same height after AFM scan                                                                                                                                                                                                                                                                                                       |

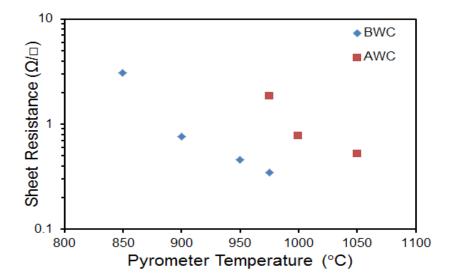

| Figure 3.30: | Sheet resistance measurements before (BWC) and after (AWC) pyrometer window cleaning.                                                                                                                                                                                                                                                                                                                             |

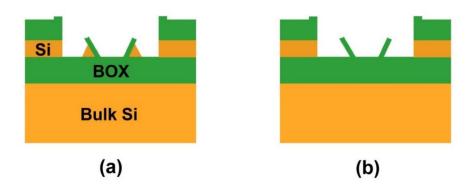

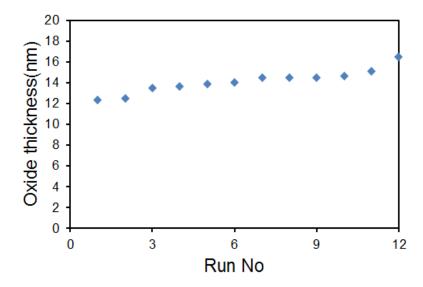

| Figure 3.31: | Run to run variation of oxide thickness using RTP (the trend does not represent the real order). Figure 3.32: 3D schematic of the nanowires after 2nd ODE; oxide remains on the bulk source and drain (useful for selective doping of nanowires).                                                                                                                                                                 |

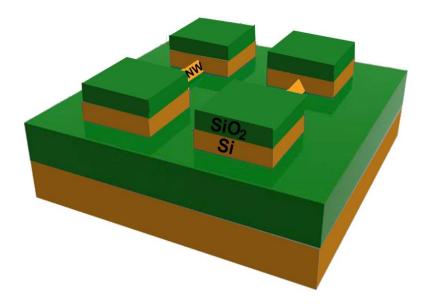

| Figure 3.32: | 3D schematic of the nanowires after 2nd ODE; oxide remains on the bulk source and drain (useful for selective doping of nanowires)                                                                                                                                                                                                                                                                                |

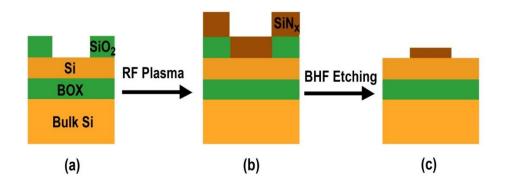

| Figure 3.33: | Deposition-Etching technique                                                                                                                                                                                                                                                                                                                                                                                      |

| Chapter 4    | 77                                                                                                                                                                                                                                                                                                                                                                                                                |

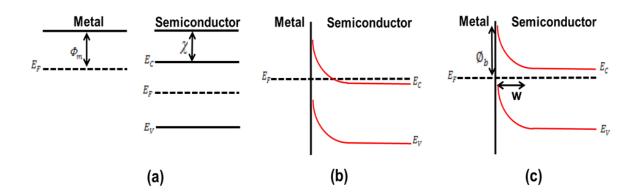

| Figure 4.1:  | (a) Energy band diagram of a metal and semiconductor before contact; (b) energy band diagram for ohmic contact of metal/n-type semiconductor; (c) energy band diagram for Schottky contact of metal/n-type semiconductor, (we is the deplation region width)                                                                                                                                                      |

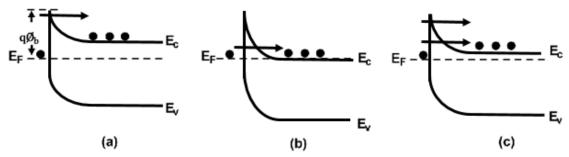

| Figure 4.2:  | (w is the depletion region width)                                                                                                                                                                                                                                                                                                                                                                                 |

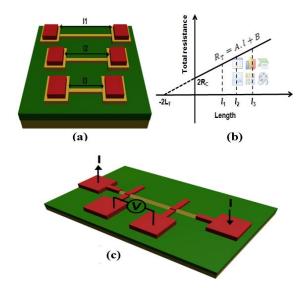

| Figure 4.3:  | (a) Schematic of multiwire test method; (b) plot of total resistance as a function of wire length for multiwire structure; (c) schematic of four probe method                                                                                                                                                                                                                                                     |

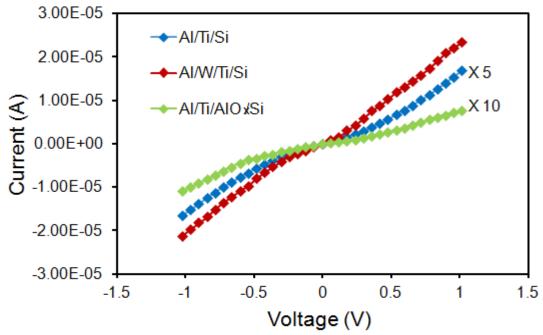

| Figure 4.4:  | Current-voltage characteristics of as-deposited silicon microwires with contacts of different metallization structures (l=30 $\mu$ m, w=2 $\mu$ m, h=90 nm)85                                                                                                                                                                                                                                                     |

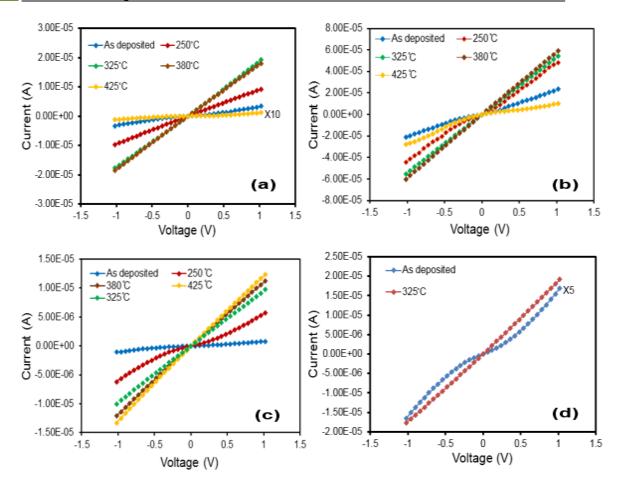

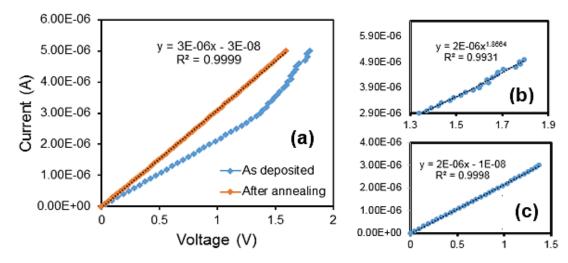

| Figure 4.5:  | The effect of various annealing temperatures on the current-voltage characteristics of different contact systems: (a) Al/Ti/Si (Note that the current-voltage after 425°C is after current is multiplied by 10(orange colour)); (b) Al/W/Ti/Si; (c) Al/Ti/AlOx; (d) the effect of annealing temperature on linearity and performance of Al/Ti /Si (the as-deposited graph is after multiplying the current by 10) |

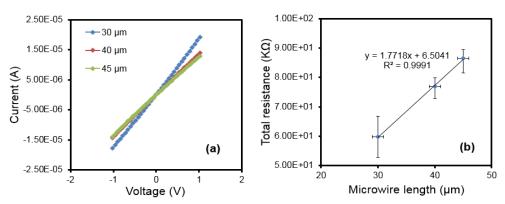

| Figure 4.6:  | (a) Current-voltage characteristics of microwire devices with different lengths; (b) total contact resistance as a function of microwire length (Al/Ti/Si contact system, w=2 µm, doping >3.5 X 10 <sup>18</sup> cm-3)                                                                                                                                                                                            |

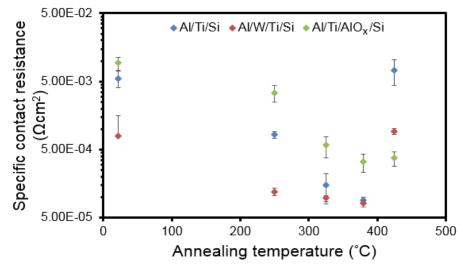

| Figure 4.7:  | Specific contact resistivity as a function of annealing after various annealing temperatures                                                                                                                                                                                                                                                                                                                      |

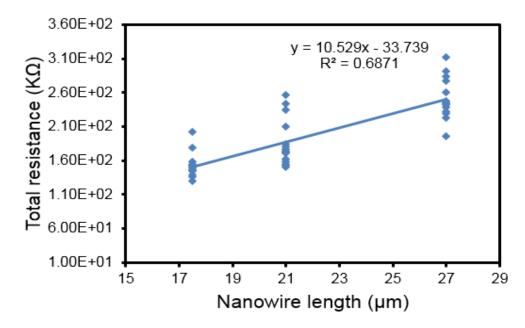

| Figure 4.8:  | The total resistance as a function of nanowire length                                                                                                                                                                                                                                                                                                                                                             |

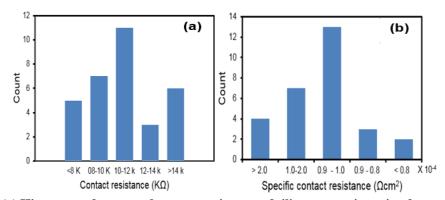

| Figure 4.9:  | (a) Histogram of measured contact resistance of silicon nanowire using four probe method (b) histogram of measured specific contact resistivity of silicon nanowire using four probe method (Al/Ti/SiNWs, Ac= 360 nm, doping >3.5 X 10 <sup>18</sup> cm-3)                                                                                                                                                        |

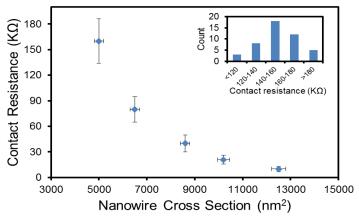

| Figure 4.10: | Measured contact resistance as a function of nanowire cross section, inset: histogram of measured contact resistance at A=5200 nm <sup>2</sup> 91                                                                                                                                                                                                                                                                 |

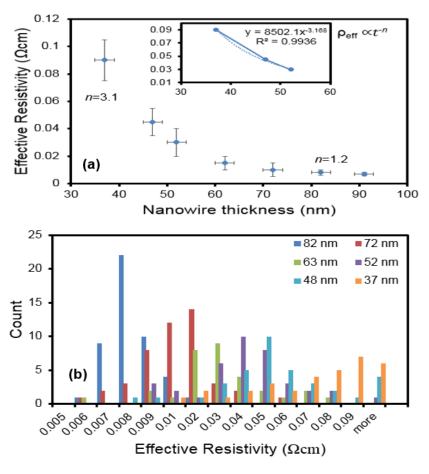

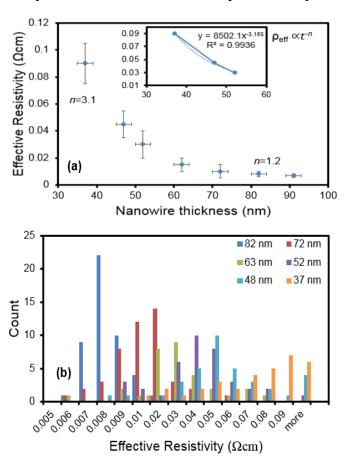

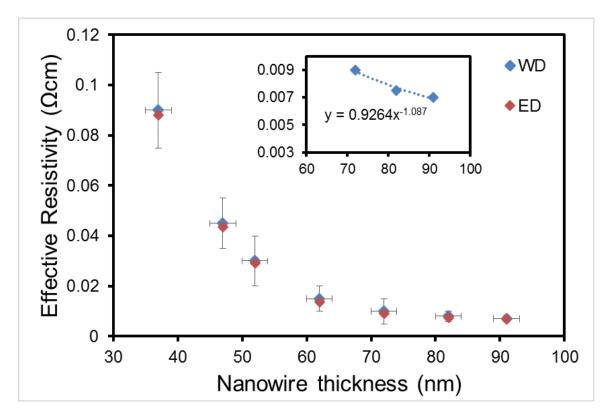

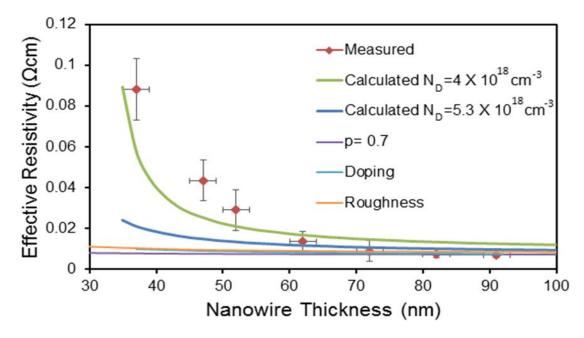

| Figure 4.11: | (a) The measured resistivity of silicon nanowires as a function of its thickness (the inset: the function that fits the measured resistivity when the thickness of nanowire is less than 60 nm) (b) Histogram of measured resistivity of silicon nanowire with different thicknesses92                                                                                                                            |

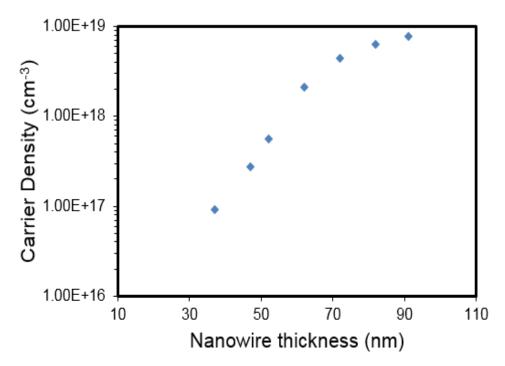

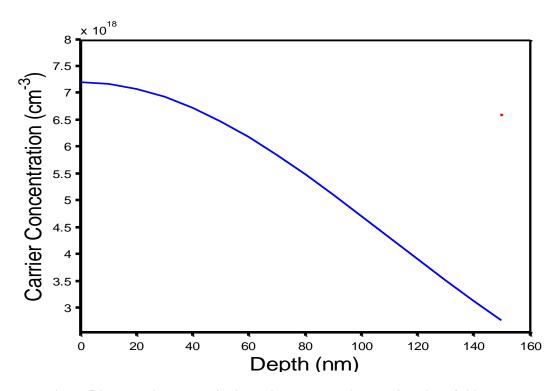

| Figure 4.12: | The effective carrier concentration in silicon nanowire as a function of<br>nanowire thickness (this average calculated data is based on the measured |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | resistivity in Figure 4.11)93                                                                                                                         |

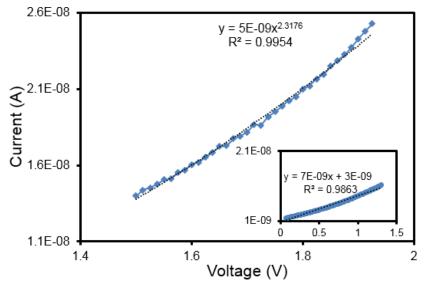

| Figure 4.13: | Nonlinearity examples of four probe current-voltage characteristics in four                                                                           |

| rigule 4.13. | probe measurements (a) heavily doped nanowire $n > 3.5 \times 10^{18}$ cm-3, t=                                                                       |

|              |                                                                                                                                                       |

|              | 65 nm (b) moderately doped nanowire 1x $10^{17}$ cm-3 < n < 1X $10^{18}$ cm-3, t=                                                                     |

| E' 4.1.4     | 45 nm                                                                                                                                                 |

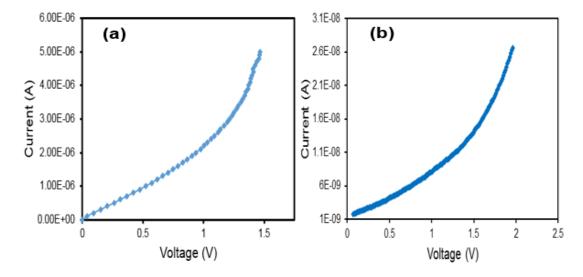

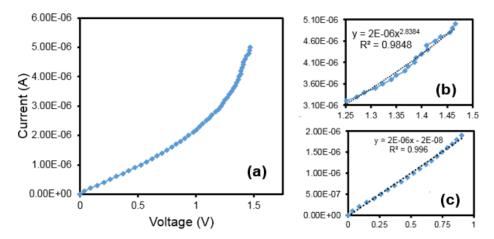

| Figure 4.14: | (a) Four contact current-voltage characteristics of a heavily doped silicon                                                                           |

|              | nanowire: (b) power fits to the nonlinear regime in (a), (c) linear fits to the                                                                       |

|              | ohmic regime in (a)95                                                                                                                                 |

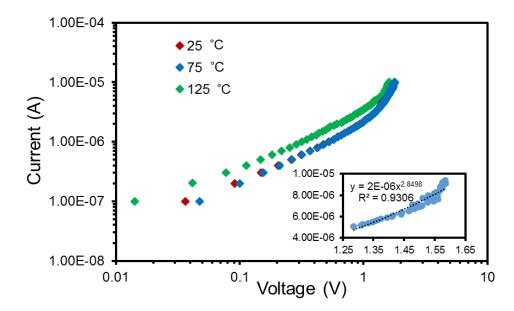

| Figure 4.15: | Temperature dependent four probe current-voltage characteristics of a                                                                                 |

|              | heavily doped nanowire (the inset: power fits to the nonlinear regime at                                                                              |

|              | 125 ℃)96                                                                                                                                              |

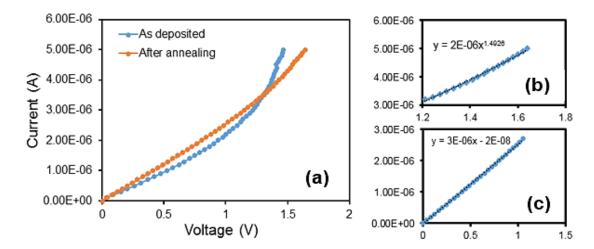

| Figure 4.16: | The four probe current-voltage characteristics of a heavily doped nanowire                                                                            |

|              | before and after annealing (b) the power fits to the nonlinear regime of the                                                                          |

|              | nanowire after post-metallization annealing (c) the linear fits to the linear                                                                         |

|              | regime of the device after post-metallization annealing97                                                                                             |

| Figure 4.17: | (a) A linear four probe current-voltage characteristics of silicon nanowire                                                                           |

| C            | after annealing (b) and (c) are the nonlinear and linear regimes of the curve                                                                         |

|              | before annealing respectively                                                                                                                         |

| Figure 4.18: | The power law fits to the nonlinear regime of the device in Figure 4.13(b)                                                                            |

| 118010101    | (the inset: the linear fits to the ohmic regime for the same device)98                                                                                |

| Figure 4.19: | Temperature dependent four probe current-voltage characteristics of a                                                                                 |

| 118010 11171 | moderately doped nanowire (Vc is the crossover voltage)99                                                                                             |

| Chapter 5    |                                                                                                                                                       |

| Figure 5.1:  | (a) The measured resistivity of silicon nanowire as a function of its thickness                                                                       |

| 118010 3.11  | (inset: the function that fits the measured resistivity when the thickness of                                                                         |

|              | nanowire is less than 60 nm); (b) Histogram of measured resistivity of                                                                                |

|              | silicon nanowire with different thicknesses                                                                                                           |

| Figure 5.2:  | Modelling results for impurity concentration as a function of silicon                                                                                 |

| riguie 3.2.  |                                                                                                                                                       |

| Figure 5.2.  | depth                                                                                                                                                 |

| Figure 5.3:  |                                                                                                                                                       |

|              | and after (ED) eliminating the effect of non-uniformity in impurity                                                                                   |

|              | concentration (inset: the function that fits the measured resistivity after                                                                           |

|              | eliminating the doping effect for thicknesses of nanowire larger than 65                                                                              |

| T: # 4       | nm)                                                                                                                                                   |

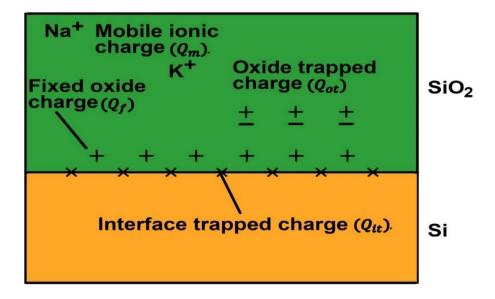

| Figure 5.4:  | Charges associated with the silicon-silicon dioxide interface                                                                                         |

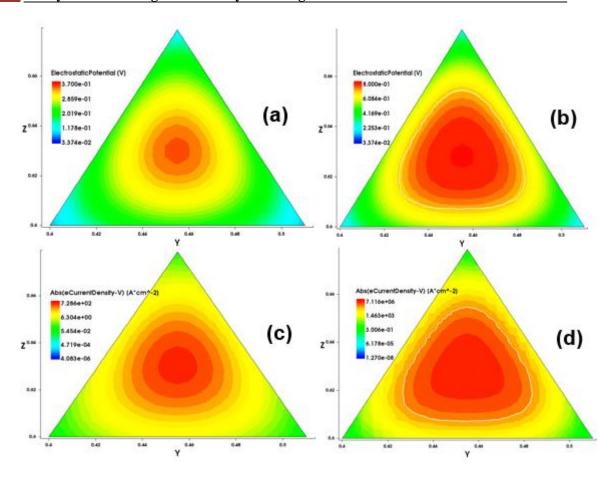

| Figure 5.5:  | TCAD simulation of the electrostatic potential and current density                                                                                    |

|              | distributions inside triangular silicon nanowire: (a) electrostatic potential for                                                                     |

|              | fully depleted nanowire with doping 1 X 10 <sup>17</sup> cm-3; (b) electrostatic                                                                      |

|              | potential for partially depleted with doping 1 X 10 <sup>18</sup> cm-3; (c) current                                                                   |

|              | density for fully depleted nanowire with 1 X 10 <sup>17</sup> cm <sup>-3</sup> ; (d) current density                                                  |

|              | for partially depleted nanowire with 1 X 10 <sup>18</sup> cm-3112                                                                                     |

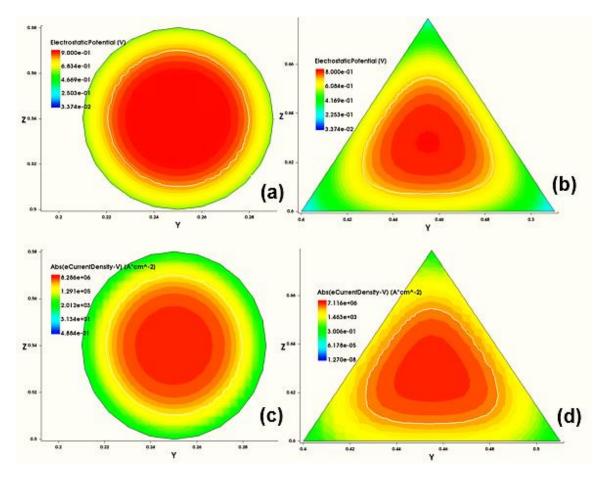

| Figure 5.6:  | TCAD simulation of the electrostatic potential and current density                                                                                    |

|              | distribution inside circular and triangular cross sections: (a) electrostatic                                                                         |

|              | potential inside circular cross section; (b) electrostatic potential inside                                                                           |

|              | triangular cross section; (c) current density inside circular cross section; (d)                                                                      |

|              |                                                                                                                                                       |

|              | current density inside triangular cross section (doping 1 X 1018 cm-3 for all                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

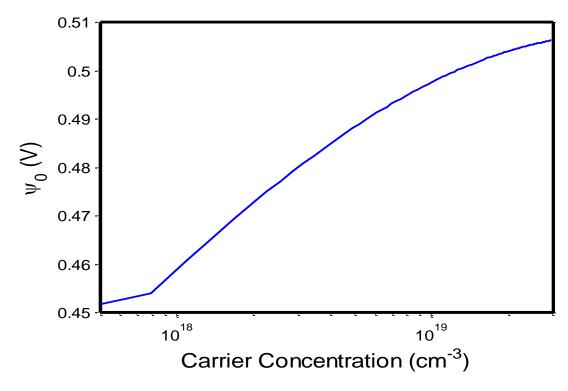

| Figure 5.7:  | simulated devices)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

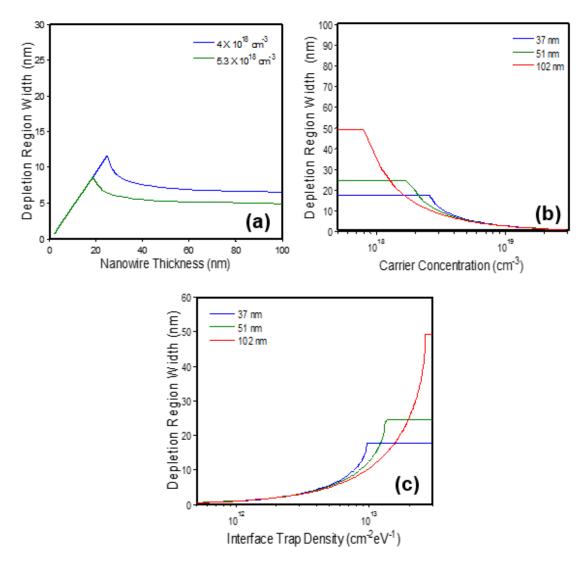

| Figure 5.8:  | concentration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

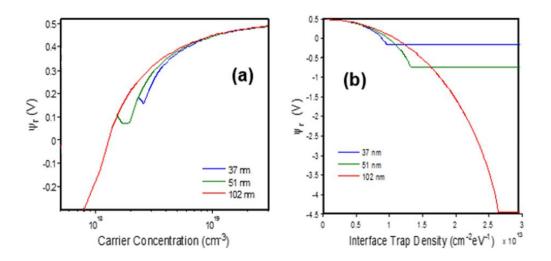

| Figure 5.9:  | (a) The effect of carrier concentration on electrostatic potential inside depletion region, Dit= $5 \times 10^{12} \text{ cm}^{-2}\text{eV}-1$ , t= 37 nm, 51 nm and 102 nm, (b) the effect of interface trap density on electrostatic potential inside depletion region, ND= $5.3 \times 10^{18} \text{ cm}-3$ , t= 37 nm, 51 nm and 102 nm.                                                                                                                                                                                                                                                    |

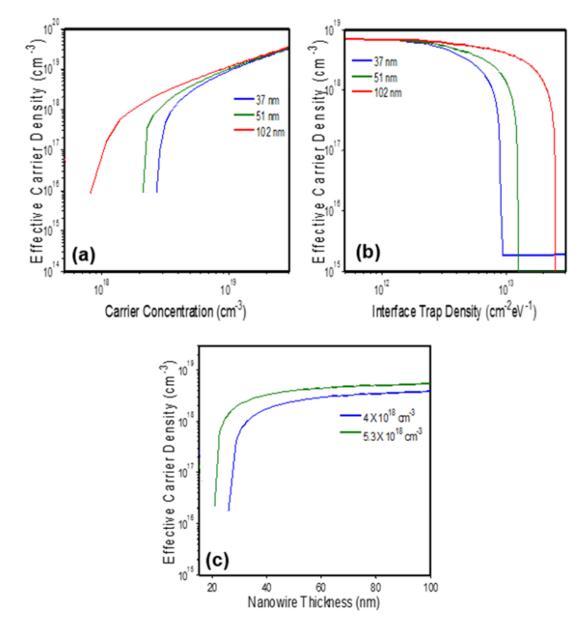

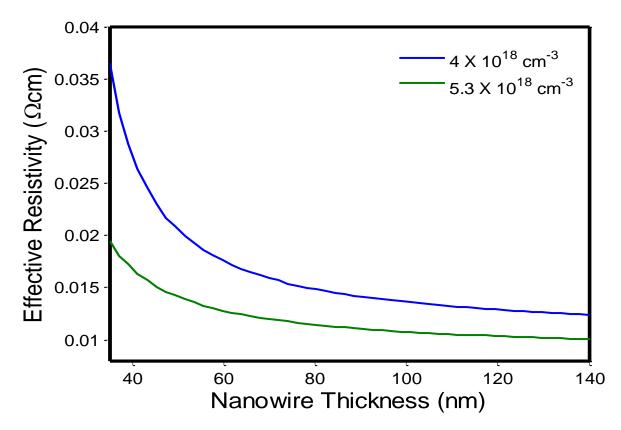

| Figure 5.10: | (a) Effective carrier density as a function of carrier concentration, Dit= $5 \times 10^{12} \text{ cm}^{-2}\text{eV}-1$ , t= $37 \text{ nm}$ , $51 \text{ nm}$ and $102 \text{ nm}$ ; (b) effective carrier density as a function of interface trap density on the depletion region width, ND= $5.3 \times 10^{18} \text{ cm}-3$ , t= $37 \text{ nm}$ , $51 \text{ nm}$ and $102 \text{ nm}$ ; (c) effective carrier density as a function of nanowire thickness, Dit= $5 \times 10^{12} \text{ cm}-2\text{eV}-1$ , ND= $4 \times 10^{18} \text{ cm}-3$ and $5.3 \times 10^{18} \text{ cm}-3$ . |

| Figure 5.11: | The effective resistivity as a function of nanowire thickness (Dit= $5 \times 1012$ cm- $2eV-1$ , ND= $4 \times 10^{18}$ cm- $3$ and $5.3 \times 10^{18}$ cm- $3$ )                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Figure 5.12: | Fitting the surface depletion effect to the measured electrical resistivity of silicon nanowire for $D_{it} = 5.9 \times 10^{12} \text{ cm}^{-2} \text{ eV}^{-1}$ .                                                                                                                                                                                                                                                                                                                                                                                                                              |

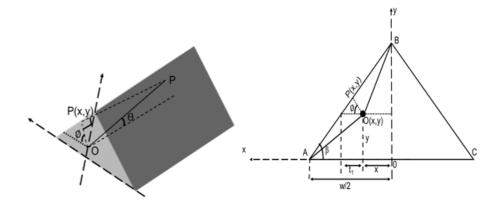

| Figure 5.13: | Schematic used to calculate the effect of surface scattering on the electrical resistivity in triangular nanowire                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

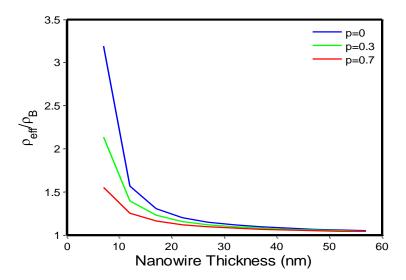

| Figure 5.14: | Calculated relative resistivity of nanowire to bulk resistivity as a function of nanowire thickness with different values of the specularity parameter (mean free path of 15 nm)                                                                                                                                                                                                                                                                                                                                                                                                                 |

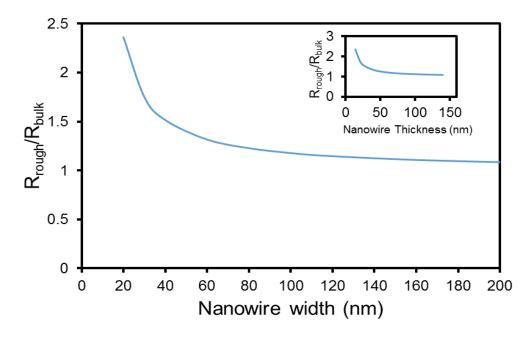

| Figure 5.15: | The effect of surface roughness on the electrical resistance of nanowire as a function of nanowire width (inset: relative resistance as a function of nanowire thickness)                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Figure 5.16: | All possible modelled affects the increase of resistivity in the nanowire compared with measured one (measured (red dots); the effect of doping distribution (cyan); the effect of surface depletion for $D_{it} = 5.9 \times 10^{12} cm^{-2} eV^{-1}$ , $N_D = 4 \times 10^{18} cm^{-3}$ (green); the effect of surface depletion effect for $D_{it} = 5.9 \times 10^{12} cm^{-2} eV^{-1}$ , $N_D = 5.3 \times 10^{18} cm^{-3}$ (blue); the effect of surface roughness (orange); scattering effect (purple).                                                                                   |

| Chapter 6    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

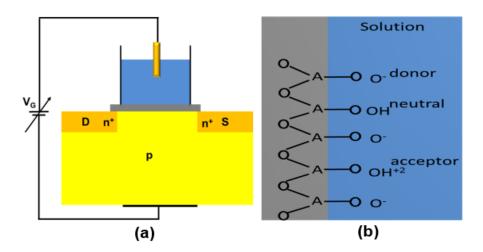

| Figure 6.1:  | (a) Schematic diagram of basic structure of ISFET; (b) dielectric/electrolyte interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

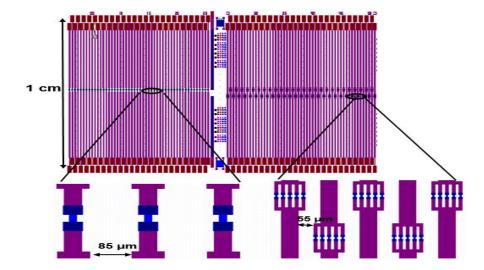

| Figure 6.2:  | Mask layout of the nanowires where the expanded views show the distance between the electrodes in the case of a single nanowire (bottom left) and bundles of five nanowires (bottom right)                                                                                                                                                                                                                                                                                                                                                                                                       |

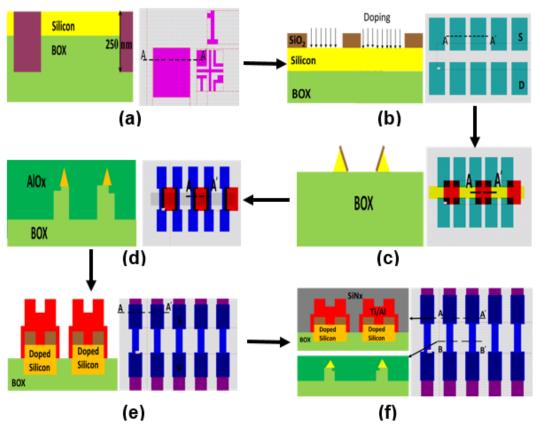

| Figure 6.3:  | Main process steps for the fabrication of silicon nanowire field effect sensor: (a) Printing the alignment marks; (b) doping the source and drain; (c) fabrication of the silicon nanowire (see Figure 3.4 for full fabrication process of the nanowire); (d) deposition of the aluminium oxide to act as an                                                                                                                                                                                                                                                                                     |

|             | active sensing layer; (e) deposition of the source/drain contacts; (f)            |

|-------------|-----------------------------------------------------------------------------------|

|             | deposition of the silicon nitride layer to act as a passivation layer. The cross- |

|             | sections A-A' and B-B' are views of the layout                                    |

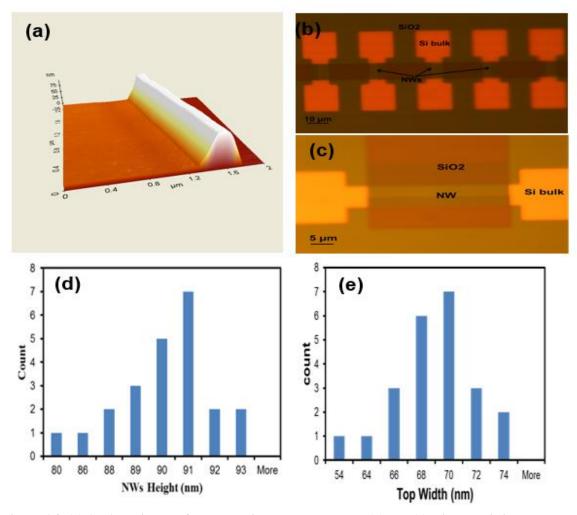

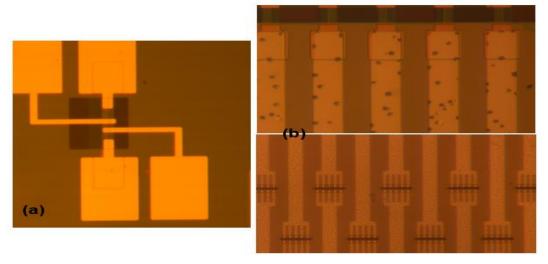

| Figure 6.4: | (a) An AFM image of the nanowire used as a sensor; (b) and (c) microscopic        |

|             | images showing the two types of structures of a bundle of five and a single       |

|             | nanowire; (d) and (e) histograms showing uniformity in thickness and width        |

|             | for 23 nanowires                                                                  |

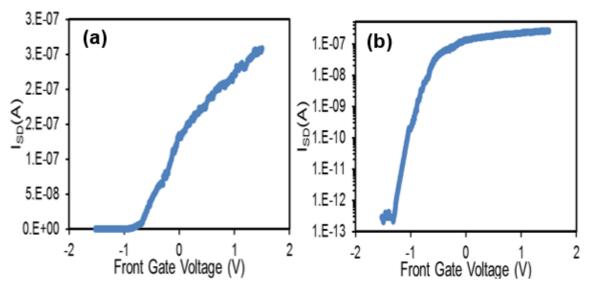

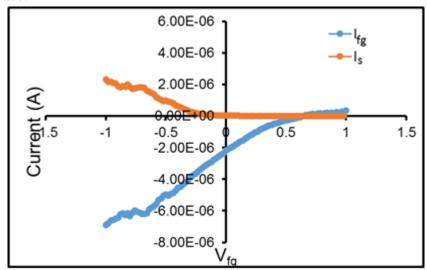

| Figure 6.5: | Back-gate measurements of silicon nanowire field effect transistor: (a)           |

|             | linear scale; (b) logarithmic scale                                               |

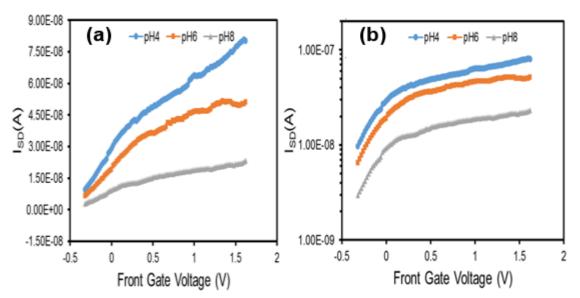

| Figure 6.6: | Transfer characteristics of source-drain current for different pH solution        |

|             | buffers, Vsd=0.4 V: (a) linear scale; (b) logarithmic scale                       |

| Figure 6.7: | Transfer characteristics of source-drain current for different pH solution        |

|             | buffers, Vsd=0.7 V and Vfg = 0.3 V                                                |

| Figure 6.8: | Transfer characteristics of a nanosensor in the buffer solution and the           |

|             | leakage current between the front gate (Vfg) and the source/drain141              |

| Figure 6.9: | (a) Microscopic image of an as-deposited Al/Ti metal; (b) microscopic             |

|             | image of metal electrode after a long period of exposure to air142                |

## Chapter 1

## Introduction

## 1.1 Background

In his 1959 lecture, "There is plenty of room at the bottom", physicist Richard Feynman discussed the possibility of obtaining devices which would be very small in size, and he claimed that "the wires should be 10 or 100 atoms in diameter, and the circuits should be a few thousand angstroms across". More than fifty years after Feynman's prediction, nanotechnology has become one of the most attractive subjects in science, medicine and engineering. Tens of thousands of research papers are published every year investigating novel techniques to make objects a few nanometres in diameter, studying their characteristics, understanding their fundamental properties and pushing them into exciting areas of application.

In this field of research, silicon nanowires are one of the most suitable objects for investigation, for many reasons. Silicon is an abundant element and practical material, and it forms an oxide which is chemically stable at the interface with silicon. Moreover, it is at the heart of CMOS technology. A nanowire can be defined as a nanostructure that has a high length to thickness ratio with a typical diameter of less than one hundred nanometres.

Silicon nanowires can be realized using bottom-up and top-down methods. The bottom-up methods are inspired by the beauty of nature's method in constructing charming objects from the bottom-up. Silicon nanowires formed from the bottom-up have high quality with controlled diameter. These methods are both simple and cheap. However, there is still a major challenge in controlling the doping level and growth positions of these nanowires, and these main drawbacks considerably limit the use of bottom-up methods. For decades top-down methods have dominated the area of IC manufacturing. Their application is still superior for achieving nanometre scale array structures with high control of doping, position and feature sizes. However, further scaling using top-down methods requires complex and often expensive equipment. Over the last decade, new fabrication techniques have been introduced to fabricate nanostructures using top-down methods without the need

CHAPTER 1 Introduction 2

for high lithography techniques. However, it has become clear that achieving reliability and reproducibility with many of these new methods is problematic.

Accessing the nanoscale regime is associated with the appearance of new fundamental properties. Electrical, optical, electronic and mechanical properties become size-dependent. The nature of the surface plays an important role in a material's properties. Surface states, the nanowire's surroundings and scattering all have a large influence on the properties of nanowires. Understanding these effects is essential in order to integrate nanowires into device applications.

Silicon nanowires can have a significant impact in various fields of application, including electronics, biology, energy devices and sensing. Among the above-mentioned applications, silicon nanowire-based sensors offer low-cost, label free and real time sensing applications.

### 1.2 Thesis overview

This thesis investigates the fabrication of silicon nanowire-based devices for electronics and sensing applications. This thesis addresses the challenges in fabricating silicon nanowires using indirect top-down methods, and in particular the methods that use optical lithography, wet etching and thermal oxidation. The issues involved in each fabrication step that affects the reproducibility of the process are addressed, and attempts are made to find solutions so as to obtain a reliable fabrication process. The thesis also addresses the issues related to the contacts for nanowires and characterises several important properties of nanowires such as resistance, resistivity and doping. This study attempts to offer insights into the effect of scaling on the electrical properties of nanowires, and also attempts to integrate silicon nanowires into functional devices for a chemical sensor.

There are four main objectives of this thesis:

- Optimization of the fabrication process of silicon nanowires using an indirect topdown method based on optical lithography, anisotropic wet etching and thermal oxidation, along with investigations of the key factors to obtain a reproducible process with high yields and a controllable structure.

- Characterisation of the fabricated devices and an investigation of the key issues that affect their performance.

- Development of models and simulation to understand the properties of fabricated nanowires in mesoscopic systems.

- Design, fabrication, and characterisation of a silicon nanowire-based chemical sensor.

This thesis is organised as follows:

CHAPTER 1 Introduction 3

Chapter two provides the background and a review of silicon nanowire fabrication by topdown and bottom-up methods. The effect of size and surface to volume ratio on the electrical and electronic properties of a silicon nanowire is discussed. Some applications of silicon nanowires in thermoelectrics, mechanical and biological applications are presented, with a special focus on the principles and applications of silicon nanowire biosensor.

Chapter three considers the fabrication of silicon nanowire field effect transistors, and reports on the optimization of the fabrication process of silicon nanowires using optical lithography, anisotropic wet etching and thermal oxidation, and investigates the key factors that affect the reproducibility and reliability of the process, such as properties of the silicon nitride film during thermal oxidation, the behaviour of Si and SOI substrates during oxidation using radiant and resistive heating sources, the robustness of a sidewall mask, and the etching characteristics of Trimethyl Ammonium Hydroxide (TMAH) and Potasium Hydroxide (KOH).

Chapter four concerns electrical transport in silicon nanowires, and discusses the issues related to contacts for nanowires in addition to the electrical properties of the nanowire itself. The electrical properties of three metallisation schemes are investigated, which are Al/Ti/Si, Al/W/Ti/Si and Al/Ti/AlO<sub>x</sub>/Si, and their stability at different elevated temperatures is determined. The key properties of electrical transport in silicon nanowires such as electrical resistivity, electrical resistance and impurity concentration, are also investigated.

Chapter five presents the analytical modelling of resistivity in triangular silicon nanowires. Several models are developed to explain the apparent increase in measured electrical resistivity with decreasing thickness of the silicon nanowire. The features described in this chapter include doping distribution, surface depletion, surface scattering due to boundary conditions, and sidewall surface roughness. The 3D Sentaurus Device simulator is used to support the analytical modelling of the effects of surface depletion effects on the electrical characteristics of a triangular silicon nanowire.

Chapter six considers silicon nanowires in aqueous media, and the theoretical background of the ionic-sensitive field-effect transistor (ISFET) and its pH sensitivity is discussed in this chapter. Experimental data for silicon nanowires in aqueous media are presented concerning the sensitivity of the nanowire to changes in pH value.

Chapter seven provides the general conclusions for the major work presented in this thesis. It also recommends further directions for research into the fabrication of nanowires, especially in the fields of selective ionic sensing, drug delivery, biosensing and thermoelectrics.

# Chapter 2

## Silicon Nanowire Background

In this chapter, the most successful techniques developed to fabricate silicon nanowires are reviewed. Some of the fundamental electrical and electronic properties of silicon nanowires are also introduced. Finally, a review of the major applications of silicon nanowires is presented, including thermoelectrics, mechanical and biological applications.

### 2.1 Fabrication methods

Two main approaches have been developed to fabricate nanostructures. These are the top-down, and the bottom-up methods. Bottom-up approaches involve assembly processes where small functional units are joined to form more complex structures. The top-down approaches start with a complex structure and reduce its size to a very fine structure and mostly use the same techniques as used in CMOS processing.

## 2.1.1 Bottom-up approach

#### Vapour-liquid-solid (VLS)

The vapour-liquid-solid process can be used to grow silicon nanowires [1-4]. In this method, a catalyst of nanoparticles of a transition metal, usually gold, is deposited on a clean and defect free substrate which can be silicon or glass (Figure 2.1(a)). Then the nanoparticle catalyst is heated to a temperature higher than the eutectic temperature for the chosen metal-semiconductor, which is Au-Si in this case, in the presence of a vapour phase source of semiconductor. The vapour can be generated through chemical vapour deposition (CVD) [3, 5], the laser ablation technique [6] or by molecular-beam-epitaxy (MBE) [7, 8]. This results in the formation of a droplet of metal-semiconductor, Au-Si, on the substrate surface (Figure 2.1(b)). The mixture will have a melting point much lower than that of the components, 360 °C in the case of Au-Si. Through the continuous introduction of gas precursor, the eutectic droplet absorbs more silicon until the eutectic supersaturates, and

the semiconductor starts to nucleate due to the precipitation of Si out of the supersaturated droplet (Figure 2.1(c)). Continually, the nanowire is formed (Figure 2.1(d)). For SINWs, Silane SiH<sub>4</sub> is used as a reactant source, and diborane ( $B_2H_6$ ) and phosphine ( $PH_3$ ) respectively are the p-type and n-type dopants.

Nanowires grown using the vapour-liquid-solid (VLS) technique can have a diameter of 15 nm with tens of micrometres in length. Vapour-liquid-solid (VLS) method is cheap and can be used to fabricate a wide range of materials with a diameter of 10 nm and tens of micrometres in length [2, 5]. However, it is still incompatible with conventional CMOS devices due to the lack of control of growth positions and the numbers of the nanowires, in addition to the incorporation of metal impurities into the nanowire during the growth [9].

### 2.1.2 Top-down approaches

The main methods that can be used to release SiNWs using top-down approaches are electron beam or nanoimprint lithography, and indirect methods.

Figure 2.1: Vapour-liquid-solid growth mechanism of silicon nanowire: (a) gold nanodroplet on a clean surface; (b) eutectic droplet; (c) nucleation; (d) nanowire growth; (e) FESEM image of silicon nanowire grown via a VLS mechanism (scale bar 20 nm) [5].

Electron beam lithography

In this method, a focused beam of electrons is used to define the fundamental device structure on a layer of photoresist; etching is then performed to transfer the pattern onto the substrate. This method has much higher resolution compared with optical lithography because of the short electron wavelength that can be obtained [10], which is given by:

$$\lambda = \frac{h}{\sqrt{2qVm_e}} \tag{2.1}$$

where  $\lambda$  is the electron wavelength, h is Planck's constant, V is the accelerated voltage, q is the elementary charge, and  $m_e$  is the mass of the electron. This technique does not require a mask and features with less than 10 nm have been reported using this technique [10-12]. However, it is a slow and expensive technique.

#### Nanoimprint lithography

The concept and the main development in nanoprimrint lithography (NIL) were proposed by Chou's group in mid-1990s [13, 14]. Since that time this method has attracted considerable research effort and wide application due to its ability to fabricate small features for mass production with low cost [15-17].