## University of Newcastle upon Tyne School of Computing Science

# Formal Modelling and Analysis of an Asynchronous Communication Mechanism

by Neil Henderson

PhD Thesis

February 1, 2005

NEWCASTLE UNIVERSITY LIBRARY

204 06180 9

Thesis L7857

#### Abstract

This thesis makes a contribution towards cutting the cost of development of real-time systems. The development of real-time systems is difficult: often errors in the specification are not identified until late in the development process, and there is a requirement to reduce the amount of rework to correct flaws introduced in the early stages of development. A Real-time Network-Specification Language (RTN-SL) is being developed to allow the rigorous specification of functionality and timing properties of computations. The correct specification of end to end timing constraints, however, requires an understanding of the timing properties of the communications between components. A theory of communication is therefore required, to be used with the RTN-SL, to analyse timing properties of systems early in the development process.

The work demonstrates how a tool set can be used to gain an understanding of the behaviour of the system, to help to identify and correct ambiguities that arise in the early stages of development. An incremental development approach is recommended. Starting with an abstract model and exploring properties of increasingly realistic models of the implementation, to gain confidence about the correctness of the implementation, and an understanding its behaviour. The strengths and weaknesses of a number of tools are discussed and it is shown that it is possible to use a compositional rely-guarantee method to verify properties of systems where the individual components give few or no guarantees about their behaviour. This rely guarantee method makes it possible to record assumptions in the specification, to help ensure they are not overlooked and thereby introduce errors in the design and implementation. This approach can form the basis of a theory of communication, which can be used with the RTN-SL to reason about end to end timing properties of systems in the early stages of development.

#### Acknowledgements

This thesis would never have been completed without the generous and invaluable help received from many people and organisations during the course of study.

I would like to express my gratitude to my Supervisors at the University of Newcastle: Professor Cliff Jones for his invaluable insight, which helped to guide the work, and Dr John Fitzgerald for encouragement and assistance during the early work and his patience and moral support while I was completing this thesis.

I am deeply indebted to Dr Stephen Paynter of MBDA UK Limited and Dr Jim Armstrong of the University of Newcastle, for their guidance and assistance in helping me to understand the technicalities of automated theory proving, and in particular PVS. In addition Stephen provided help, encouragement and moral support while the work was progressing.

Thanks are also due to Professor Hugo Simpson of MBDA UK Limited, and many colleagues at the University of Newcastle, including Professors Alex Yakovlev and Majiec Koutny and Drs Ian Clark and Fei Xia who have commented on various aspects of the work as it has progressed.

Thanks must go to the BAE SYSTEMS Dependable Computing Systems Centre for funding, and providing time, to complete the work.

I am deeply grateful to my family, in particular my wife Alison, for their support and encouragement during yet another period of study.

# Contents

| 1 | Intr        | roduction                                                    | 1  |

|---|-------------|--------------------------------------------------------------|----|

|   | 1.1         | Verifying the Correctness of Real-time Systems               | 2  |

|   |             | 1.1.1 The Role of Hierarchical Development Methods           | 3  |

|   |             | 1.1.2 The Role of Communication Mechanisms                   | 4  |

|   |             | 1.1.3 The Role of Formal Methods                             | 9  |

|   | 1.2         | Contribution                                                 | 11 |

|   | 1.3         | Thesis Structure                                             | 12 |

| 2 | ΑΊ          | axonomy of Asynchronous Communication Mechanisms             | 13 |

|   | 2.1         | Real-time Logic                                              | 14 |

|   | <b>2</b> .2 | Lamport's Taxonomy of Asynchronous Registers                 | 15 |

|   |             | 2.2.1 Base Type and Valid Type                               | 16 |

|   |             | 2.2.2 Lamport's Taxonomy                                     | 16 |

|   | 2.3         | A Critique of Lamport's Taxonomy of Asynchronous Registers   | 19 |

|   | 2.4         | An Extended Taxonomy of ACMs                                 | 20 |

|   | 2.5         | Desirable Properties of ACM implementations                  | 30 |

|   | 2.6         | Using the taxonomy to Verify Properties of an Implementation | 31 |

|   | 2.7         | Summary                                                      | 33 |

| 3 | L-at        | comic ACMs                                                   | 34 |

|   | 3.1         | Communication Mechanism Implementations                      | 35 |

|   |             | 3.1.1 1-slot ACMs                                            | 36 |

|   |             | <b>3.1.2</b> 2-slot ACMs                                     | 36 |

|   |             | 3.1.3 3-slot ACMs                                            | 39 |

|   | 3.2         | An Implementation Classification Scheme                      | 42 |

|   |             | 3.2.1 Impossibility Results for ACM Implementations          | 43 |

|   | 3.3         | Simpson's 4-slot ACM                                         | 43 |

|   |             | 3.3.1 Description of Simpson's 4-slot                        | 43 |

|   |             | 3.3.2 The 4-slot Algorithm                                   | 46 |

|   |             | 3.3.3 A Formal Model of Simpson's 4-slot                     | 46 |

|   | 3.4         | Summary                                                      | 53 |

| CONTENTS  | •  |

|-----------|----|

| CONTLINIS | 1V |

| 4 | A N              | Iodel of L-atomicity                                      | 54         |

|---|------------------|-----------------------------------------------------------|------------|

|   | 4.1              | The (Abstract) Model                                      | 55         |

|   | 4.2              | Verification of the Model of L-atomicity                  | 60         |

|   |                  | 4.2.1 A Rigorous Proof for the end_read Operation         | 62         |

|   | 4.3              | Summary                                                   | 68         |

| 5 |                  | ng Refinement to Verify Properties of Simpson's 4-slot    | 70         |

|   | 5.1              | Refinement                                                | 71         |

|   | 5.2              | A Retrieve Function?                                      | 72         |

|   | 5.3              | Formal Definitions of the Proof Obligations               | 74         |

|   | 5.4              | A Retrieve Relation Between the Formal Models             | 75         |

|   | $5.\overline{5}$ | Discharging the Proof Obligations                         | 80         |

|   | 5.6              | Summary                                                   | 86         |

| 6 | App              | olying a Compositional Proof Method                       | 89         |

|   | 6.1              | Rely-Guarantee                                            | 90         |

|   | 6.2              | A Proof Method for Shared Variable Concurrency            | 91         |

|   | 6.3              | Verifying L-Atomicity of the 4-slot Implementation        | 94         |

|   |                  | 6.3.1 Assertion Networks for the Component Processes      | 94         |

|   |                  | 6.3.2 Formal Descriptions of the Proof Obligations        | 95         |

|   |                  | 6.3.3 The Coherence Proof                                 | 97         |

|   |                  | 6.3.4 The Freshness Proof                                 | 104        |

|   | 6.4              | Identifying and Correcting Defects in a 3-slot ACM Imple- |            |

|   |                  | mentation                                                 | 111        |

|   | 6.5              | Summary                                                   | 113        |

| 7 |                  | del Checking Simpson's 4-slot ACM                         | 116        |

|   | 7.1              | Metastability                                             | 117        |

|   | 7.2              | CSP and the FDR Model Checker                             | 118        |

|   | 7.3              | Modelling Bit Control Variables                           | 119        |

|   |                  | 7.3.1 Models of the BIT variables                         | 121        |

|   |                  | 7.3.2 LB1 and LB2 - Local Copies of the Control Variables | 123        |

|   | 7.4              | A CSP Model of the 4-slot                                 | 125        |

|   | 7.5              | Model Checking the 4-slot ACM using CSP and FDR           | <b>127</b> |

|   |                  | 7.5.1 Relationship Between the Specifications             | 128        |

|   |                  | 7.5.2 Results and Analysis                                | 128        |

|   | 7.6              | Further Work                                              | 130        |

|   | 7.7              | Summary                                                   | 132        |

| 8 | Con              | clusions                                                  | 133        |

|   | 8.1              | A Taxonomy of ACMs                                        | 133        |

|   | 8.2              | Verifying Properties of an ACM Implementation             | 134        |

|   |                  | 8.2.1 Applying Refinement to Verify Properties of Systems | 135        |

CONTENTS v

|              |                        | 8.2.2<br>8.2.3 | Applying a Rely-Guarantee Proof Method Model Checking Using CSP | 136<br>136 |

|--------------|------------------------|----------------|-----------------------------------------------------------------|------------|

|              | 8.3                    |                | ne Assisted Formal Proofs                                       | 137        |

|              | 8.4                    |                | d Work                                                          | 138        |

|              | 8.5                    |                | Work                                                            | 139        |

|              |                        | 8.5.1          | An Incremental Development Method                               | 139        |

|              |                        | 8.5.2          | Developing a Theory of Communication Mechanisms                 | 140        |

|              |                        | 8.5.3          | Tool support                                                    | 140        |

|              |                        | 8.5.4          | Atomicity Refinement                                            | 141        |

|              |                        | 8.5.5          | Identifying and Verifying New Impossibility Results             |            |

|              |                        |                | for ACM Implementations                                         | 141        |

|              |                        | 8.5.6          | Verifying Properties of Fully Asynchronous Systems              |            |

|              |                        |                | Using Rely-Guarantee                                            | 141        |

|              | 8.6                    | Conclu         | iding Remarks                                                   | 141        |

| A            | Tra                    | nslatin        | g from VDM-SL to the PVS Logic                                  | 153        |

| В            | An                     | embed          | ding of RTL in the PVS Logic                                    | 159        |

| $\mathbf{C}$ | АТ                     | 'axomo         | ny of ACMs                                                      | 165        |

| D            | Sim                    | pson's         | 4-slot                                                          | 178        |

| $\mathbf{E}$ | $\mathbf{A}\mathbf{n}$ | Abstra         | act Model of L-Atomicity                                        | 184        |

| F            | The                    | Retri          | eve Relation                                                    | 189        |

| $\mathbf{G}$ | Pro                    | of of C        | Coherence                                                       | 193        |

| Н            | The                    | Fresh          | ness Proof                                                      | 209        |

| I            | 3-sle                  | ot ACI         | M Implementations                                               | 234        |

| _            | I.1                    |                | nplementation from [Sim90a]                                     | 234        |

|              | I.2                    |                | ucing a Timing Constraint                                       |            |

|              | I.3                    |                | ised 3-slot ACM Implementation                                  |            |

| J            | Mod                    | delling        | Metastability Using CSP                                         | 260        |

# List of Figures

| 1.1                             | A Generic ACM                                                                                                                                                                                | 8                                 |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| 2.1<br>2.2<br>2.3               | Reading From and Writing To an ACM                                                                                                                                                           | 17<br>28<br>30                    |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5 | Accidental Synchronisation of a Reader and Writer Incorrect Operation of a 2-slot ACM - 1 Incorrect Operation of a 2-slot ACM - 2 Incorrect Operation of the 3-slot ACM Simpson's 4-slot ACM | 36<br>38<br>39<br>41<br>44        |

| 4.1<br>4.2                      | Sequence of items                                                                                                                                                                            | 55<br>61                          |

| 5.1<br>5.2<br>5.3<br>5.4        | A one to many retrieve relation                                                                                                                                                              | 73<br>73<br>74<br>3 77            |

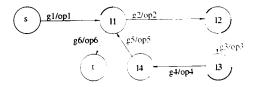

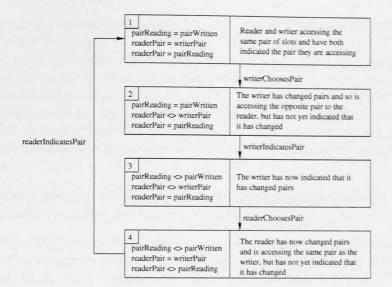

| 6.1<br>6.2<br>6.3<br>6.4        | •                                                                                                                                                                                            | 91<br>94<br>94<br>106             |

| 6.5 $6.6$                       | Assertion Network for the Reader to the 3-slot                                                                                                                                               | <ul><li>111</li><li>112</li></ul> |

# List of Tables

| 1.1 | The Blocking or Non-Blocking Behaviour of the Basic Protocols | 1   |

|-----|---------------------------------------------------------------|-----|

| 3.1 | A 2-slot ACM Implementation                                   | 37  |

| 3.2 | An Implementation of a 3-slot ACM                             | 40  |

| 3.3 | Assignments to the Control Variables                          | 41  |

| 3.4 | The 4-slot mechanism                                          | 47  |

| 6.1 | Incorrect Operation of the 3-slot ACM                         | 113 |

| 7.1 | The Descriptions of the Different Bit Models                  | 129 |

| 7.2 | 4-Slot Coherence, Sequencing and Freshness Results            | 130 |

## Chapter 1

## Introduction

This thesis makes a contribution towards cutting the cost of development of asynchronous real real-time systems, by demonstrating how it is possible to gain an understanding, and verify properties, of such systems in an incremental manner. It recommends starting with an abstract, easy to understand, model of the required behaviour of the system, and building and verifying more realistic models as understanding increases. It also shows how it is possible to verify properties of systems using a compositional rely-guarantee method, when the individual components of the system give few or no guarantees about their individual behaviour. The work has been sponsored by the BAE SYSTEMS Dependable Computing Systems Centre (DCSC) and in particular MBDA UK Limited.

The specification and development of asynchronous real-time systems is difficult, and often errors that arise from a lack of understanding of the specifications of these systems are not identified until late in the development process. The development of relatively small fully asynchronous systems. which have apparently simple specifications, may also be difficult because their components can interact in unexpected ways. Correcting errors may require a large amount of rework, because, depending on the stage in the development process at which the error was introduced, this may require the specification, design and implementation to be modified and verification and testing work may need to be repeated for the modified system. There is therefore a requirement to identify and correct flaws and ambiguities earlier in the development process to reduce the amount of rework that is required, in order to cut the cost of, and time for, developing those systems. A classical method of dealing with complexity is to specify the system as a number of simpler components [Kop98]. There is then an obligation to verify that the complete system meets its specification, when it is composed of those components. Formal models of systems can aid the analysis of requirements and the use of formal methods makes it possible to verify the behaviour of

the system in a rigorous manner. This analysis can help to expose errors and ambiguities in the requirements and specification of the system, and identify ways of correcting those errors.

A (formal) Real-time Network-Specification Language (RTN-SL) [PAH00. Pay02] is being developed jointly by the DCSC and MBDA UK Limited. based on VDM-SL [ISO96] and Real-time Logic (RTL) [JM86, JMS88], to allow the rigorous specification of functionality and timing properties of computations in systems. The correct specification of end to end timing constraints, however, also requires an understanding of the timing properties of the communications between components in a system. Communication is often assumed to occur instantaneously, however the time taken for an item to be transmitted from one component to another can influence the overall timing of, or affect the precise item of data that is used in, a computation, depending on the type of the communication mechanism that is used between the reader and writer. A theory of communication is therefore required, to be used with the RTN-SL, to analyse the timing properties of systems early in the development process. This has motivated two requirements: first the use of a model based approach where functions can be expressed implicitly for compatibility with the RTN-SL, and; second, a method that facilitates the verification of properties of systems, where the communication mechanisms are used as components, would be advantageous.

The remainder of this chapter is structured as follows. Section 1.1 discusses the difficulty in specifying and designing complex real-time systems, how hierarchical development methods can help to manage the complexity of specifications and designs, the role of communications in complex systems and how the use of formal models can help to identify errors and ambiguities in specifications. Section 1.2 then discusses the contribution of the work described in this thesis in more detail.

### 1.1 Verifying the Correctness of Real-time Systems

[RLKL95] defines a real-time system as:

"A real-time system is a system that is required to react to stimuli from the environment (including the passage of physical time) within time intervals dictated by the environment."

The critical aspects of this definition are that a real-time system should be: reactive, that is react to its environment; and timely, that is react and respond to stimuli within defined time limits. This may not simply mean that the system needs to acknowledge receipt of the stimulus, but it may

be required to carry out an action, for example to complete a computation, within a specified time of receiving the stimulus.

These critical requirements make the specification and design of real-time systems complex, because the environmental stimuli can occur at any time and the system must therefore be ready to react to them at any time. There are two categories of deadline that a real-time system may be required to meet: soft deadlines and hard deadlines [Kop90]. In the case of soft deadlines. while it may be that a system is required to perform an action within the deadline, it may be acceptable for this deadline to be missed: the system may continue to operate with reduced functionality for a short period of time, for example. In the case of hard deadlines, however, it may be more critical if a deadline is missed. For example a critical system such as a flight control system on an aircraft, where missing a deadline could cause catastrophic failure (e.g. loss of life). Even then it may be acceptable to miss a hard deadline occasionally, provided it is possible to extrapolate from previous data to enable the system to continue to operate in a stable state. It is unlikely that all of the components in any system will have hard deadlines. but it is necessary to ensure that components that do not have hard deadlines are unable to interfere with components that do in such a way that those hard deadlines cannot be met. Systems which contain components with hard deadlines are referred to as hard real-time systems. The specification, design and implementation of hard real-time systems is more difficult than for soft real-time systems, because of the need to meet these critical deadlines.

The techniques described in this thesis can be used for the development of all types of complex system, however the development of hard real time systems is of particular interest. Their development is especially complex, because such systems have all of the properties of soft real-time systems and additional ones, such as the above requirement to meet safety critical deadlines.

#### 1.1.1 The Role of Hierarchical Development Methods

A classical method of dealing with complexity in systems is to partition the system into a number of simpler components. These components can then, themselves, be split into sub-components in a hierarchical manner until the individual sub-components are simple enough to be understood and implemented. A hierarchical development process will assist in recording the relationship between the components and sub-components in the system.

The use of a hierarchical method introduces an obligation to show that the specifications of the components combine to meet the specification of the complete system. Care must be taken with the specification of the components, because they may interfere with each other, or interact in unexpected ways[Per99]. For example, in the case of fully asynchronous systems, if two components communicate with each other using a shared area of memory, one component may overwrite the area of memory while another component is attempting to read an item of data from it. In the case of synchronous systems it is possible that the failure of one of the components may lead to deadlock. In reactive systems, where the system is required to react to stimuli from its environment, it is possible that the environment can interfere with the operation of the system at any time. For example the user of the system may cancel a partially completed operation.

MASCOT [JIM87, Sim86], which was the UK MOD preferred method [MoD91, MoD85] for the development of software systems and is still used in parts of the defence industry, is such a hierarchical development process. When using MASCOT a system is structured in terms of a number of interacting components (sub-systems, servers etc.), which, at the lowest level are decomposed into a number of activities in a Real-time Network (RTN), [Sim90c, Sim90b]. These activities are used to specify single sequential computations: parallelism can then arise because multiple activities may execute concurrently, depending on available resources. The sub-systems and activities in a RTN only communicate with each other via explicitly defined routes using a range of different types of communication mechanisms.

#### 1.1.2 The Role of Communication Mechanisms

There is a need for the individual components in a system to communicate with each other, and the type of communication mechanism used can influence the timing properties of a system and also the outcome of a computation. A range of mechanisms is required to facilitate communication between the components of a system: from those that enable synchronous communication to those that allow fully asynchronous communication.

Synchronous communication, as the name implies, requires the components to synchronise in order to communicate with each other. This may be achieved by using a global clock to enable the processes to synchronise and communicate at particular times, or by forcing one process to wait until the other is also ready to communicate. Synchronous communication may be used, for example, where it is necessary for a component to respond to all of the outputs from another component. Its use may, however, lead to a reader of a communication mechanism being held up, while it waits for another component to write the result of a computation to the communication mechanism. The close coupling of components required by synchronous communication may also lead to deadlock, if one of the communicating components fails.

At the other extreme are fully asynchronous communication mechanisms

(or pure ACMs) which do not require any synchronisation between communicating components. This type of mechanism must have some means of ensuring that the reader does not attempt to read an item of data at the same time as it is being written. Pure ACMs are of particular interest because:

- 1. They allow components that do not share a clock to communicate with each other. This is true even when there is apparent support for synchronous communication, as such synchronous mechanisms need to be built from ACMs, although this may be at the hardware level and hidden from the software (or user).

- 2. They support the integration of components that run at different speeds, or which are sporadic.

- 3. They provide a means for decoupling the temporal interactions of components that use them: this may make it easier to analyse the timing behaviour of individual components, because one component cannot interfere with timing behaviour of another component. For example an end to end deadline for a computation can be partitioned among the components that contribute to the computation. It may then be possible to verify that the computation will be completed within an end to end deadline provided the individual components meet their deadlines.

- 4. They make systems more robust to deadlock of one of their components. For example if the writer is held up the reader can re-read the previous item of data.

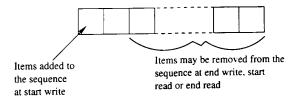

Pure ACMs are essentially shared variables that allow communication between processes without placing any constraints on the behaviour of their reader(s) and writer(s). The reader of an ACM may end one read and start the next one while a write is in progress and so multiple reads can overlap a write. Similarly multiple writes can overlap a read. It is possible for an item to be read by the reader a number of times and it is also possible that items will be overwritten before the reader attempts to read them. The asynchronous communication that ACMs support is therefore to be distinguished from the model of "asynchronous communication" supported by (conceptually infinite) buffers, where all items written are read by the reader (normally in the order that they written), for example [JHJ89].

In between the two extremes there are implementations of communication mechanisms that allow different levels of asynchrony between the communicating processes. For example, if it is known that the reader and writer of a mechanism execute on average at the same rate, it may be acceptable to implement the communication mechanism using a first in first out buffer. This may ensure that the reader is not held up, because there will always be data available to be read, and the writer may never be held up, because there is always space in the buffer to write a new item to. This type of mechanism may be used where it is important that the reader uses every item of data that is communicated. In such circumstances it may even be acceptable for the reader or writer to be held up for a short time, waiting for data or space to become available.

In large distributed systems it is possible for communication between two remote processes to be facilitated via a route which is composed of a number of components. In this case hierarchical methods may be used to develop the specifications of the communication mechanisms themselves.

#### Communication in MASCOT

MASCOT uses a range of communication protocols, which describe the manner in which the reader(s) and writer(s) communicate with each other on a particular communication route between the components. These protocols facilitate a range of different types of communication between a reader and writer, including fully asynchronous mechanisms and buffer types, where the reader may be held up waiting for data to become available and the writer may be held up waiting for space. In general MASCOT communication mechanisms support multiple readers and/or writers, however, in order to define a theory of communication, it is first necessary to gain an understanding of the behaviour of basic communication mechanisms which have single readers and writers. A range of single reader, single writer protocols is introduced in the next section.

#### A Range of Communication Protocols

There is a need to provide a means for developers to reason about the behaviour of different communication mechanisms, and this section describes a way of classifying this different behaviour. A set of *basic* communication protocols([PAH00, Sim94, Sim96, Sim03]), that can be used in the design of systems is introduced. These protocols, which are illustrated in Table 1.1, describe a range of levels of synchronisation that may be required between the reader and writer of a communication mechanism as follows:

Channel: similar to a single space buffer. The writer is held up if there is no space available for the item to be written, and the reader can only read each item of data once. The data is conceptually *destroyed* by a read and the reader is held up when the channel is empty.

|                                                     | Non destructive read<br>(Never held up) | Destructive read<br>(Held up when no<br>data) |

|-----------------------------------------------------|-----------------------------------------|-----------------------------------------------|

| Destructive write<br>(Never held up)                | Pool                                    | Signal                                        |

| Non destructive write<br>(Held up when no<br>space) | Constant                                | ——————————————————————————————————————        |

Table 1.1: The Blocking or Non-Blocking Behaviour of the Basic Protocols

**Signal:** similar to a single space overwriting buffer. The writer can overwrite older data and is never held up waiting for space to become available. The reader, however, removes data from the protocol and is held up when it is empty.

Constant: as its name implies the data, once written, cannot be overwritten. The reader can always re-read the item that the protocol was initialised with, and the protocol is typically used to store configuration data.

**Pool:** similar to a shared variable. The reader and writer are never held up. The reader can re-read items of data many times, and the writer can overwrite older items of data.

They are called basic protocols, because, conceptually, they have a single place to store data that is available for communication between the reader and writer, although they may be implemented using a multiple place area of shared memory. Each place is called slot, or buffer, and the provision of multiple slots facilitates concurrent accesses by the reader and writer by directing them to different slots. For example the channel may be implemented with three slots, one to hold the latest item of data, another to hold the item of data that is being read, and a third slot where the writer can write an additional item, before it is held up. This implementation allows a greater level of asynchrony between the communicating processes than would

otherwise be possible. The use of multiple slots ensures that the reader can obtain complete items that have been previously written as the result of a read, even if the writer is concurrently accessing the communication mechanism i.e. the protocol ensures mutual exclusion of the reader and writer on the slots rather than on the communication mechanism itself as would be the case with a Hoare monitor [Hoa74].

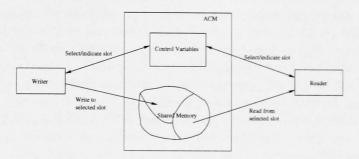

Figure 1.1: A Generic ACM

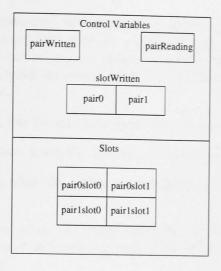

Of the mechanisms described above the only pure ACM is the pool. The remaining mechanisms require a certain amount of synchronisation between the reader and writer. Pure (true) ACMs typically use a number of areas of shared memory, with separate control variables to direct the reader and writer to different slots if they both access the mechanism at the same time. These control variables are implemented in shared memory themselves, and in fully asynchronous implementations the writer of a control variable can interfere with the reader by writing to the variable while it is being read. This may result in the reader obtaining an incorrect value as the result of reading a control variable. The implementation must still ensure that the reader: accesses a different slot to the writer when this occurs, so that it returns valid data as the result of a read and; second, that it reads a recently written item of data. A generic ACM is illustrated in Figure 1.1. The implementation of a pool that is described in this thesis, Simpson's 4slot [Sim90a], uses four slots and four control variables to allow the reader and writer to access the mechanism in a fully asynchronous manner.

The techniques described in this thesis have been used to analyse basic ACMS, such as those described in this section, although it may be possible to extend them to enable analysis of the more complex ones: for example multiple reader and writer mechanisms, and mechanisms which are implemented on routes which are comprised of a number of components. This is to be the subject of further work and this point will be revisited in Chapter 8.

#### 1.1.3 The Role of Formal Methods

Section 1.1.1 describes how the use of hierarchical methods can assist in the development of complex systems and Section 1.1.2 describes the role of communication in those systems. This section discusses the role of formal methods in the development of such complex systems.

Errors can arise in the specifications of asynchronous systems for a number of reasons, for example as a result of unexpected interactions between the components (it is also possible for errors to arise in the design and implementation of asynchronous systems with apparently simple specifications for the same reason). There is also an obligation to verify that the specifications of the components combine to meet the specification of the complete system. The use of formal specifications can assist in both of these areas [Hal90, BH95a, BH95b, LFB96, Bic98, HB99, Jon90]. Formal models of the system can be used to explore its possible behaviours and this can help to expose, and correct, errors and ambiguities in the specifications of the system and its components. In addition by starting with an abstract specification and progressively building, and exploring properties of, more realistic models it is possible to gain a better understanding of the behaviour of the system and the interactions of its components. Established techniques can then be used to verify that the composition of a set of components meets the specification of the complete system. For small systems it may be possible to verify the correctness of the complete system by showing that the required properties hold of the complete system in an exhaustive manner i.e. that those properties hold for all possible states of the system. For larger systems, however, the state space of the complete system may be too big, or too complex, for this type of method to be practical. Even if it is possible to construct a finite state model of the system, it is extremely difficult to ensure that the the model is constructed correctly. In addition it may not be tractable to discharge the required proof obligations for all possible states of the system. Model checking methods may be used to verify properties of some systems, but this may require abstraction to be used, or a model checking technique to reduce the state space. There is a danger that any abstraction hides a crucial property that may invalidate the results obtained. In any case, even with modern fast machines, model checking large systems with very large state spaces may not be tractable. It may be possible to use a compositional proof method to overcome these disadvantages: if it is possible to establish invariants (or assertions) that hold in the different states of the individual components that are sufficient in themselves to ensure the required properties of the system hold. There is then a requirement to prove that the individual components do not interfere with each other. In other words it is necessary to show that, if an assertion holds for a component, any actions executed by the other components do not invalidate that assertion.

A formal specification language, called RTN-SL, is being developed to allow the rigorous specification of functionality and timing properties of activities in RTNs, so that it is possible to analyse and verify properties of the specification of those activities in a rigorous manner. A state machine is used to specify the ordering and timing of operations within the computation with a VDM-SL like language to specify the functionality of those operations. However, there is currently no means of analysing the timing behaviour of the communication between activities and there is a need to develop a theory of communication, which is compatible with the RTN-SL, for this purpose. This theory may then be used with the RTN-SL to verify properties of complete systems in a compositional manner. Discharging the proof obligations to verify properties of the complete system may be difficult and some form of machine assistance will be invaluable in making the proofs more tractable.

#### Machine Assisted Proofs

There is a need to discharge proof obligations in order to verify properties of formal models: the proofs are often long and tedious, and the probability of errors completing such proofs by hand is high. While it is acknowledged that proofs may also be long and involved even with machine assistance, the use of a proof tool will help to make the proofs less error prone. Using such a tool to assist with completion of the proofs is therefore felt to be essential. PVS[OSRSC99a, OSRSC99b] has been used to assist with the completion of the proofs described in this thesis.

PVS is an interactive environment for writing formal specifications that facilitates machine assistance for discharging formal proofs. It provides an expressive specification language, which augments classical higher order logic, with a sophisticated type system containing, for example, predicate sub-types, combined with a mechanism for defining abstract data types, such as lists and trees.

PVS has a powerful interactive theorem prover with built in proof tactics that can make the individual proof steps much larger than is possible with comparable systems. It has been used to verify properties of complex fault-tolerant algorithms [LR93a, LR93b, LR94]. The use of PVS to verify properties of the models has helped in making some of the complex proof obligations, that need to be discharged to show that the 4-slot is Lamport-atomic, more tractable, and also helped in ensuring correctness of the models<sup>1</sup>.

<sup>&</sup>lt;sup>1</sup>The prover automatically checked the models for type correctness, for example.

1.2. Contribution

#### 1.2 Contribution

This thesis shows how it is possible to use a range of tools to explore the properties of asynchronous real-time systems, to gain a better understanding of those systems and increase confidence that they meet their requirements. A number of methods are available to help cope with the complexity. These include the use of a hierarchical development method to partition the system into a number of simpler components. There is then a proof obligation to show that the system meets its specification when it is composed of those components. In addition formal models can be used to explore properties of the system, to gain a better understanding of its behaviour.

The contribution of this work is that it identifies a means for analysing the behaviour of asynchronous real-time systems, which can form the basis of a method to develop a theory of communication, and assist to reduce the amount of rework that is required as a result of flaws in the earlier stages of development. Specifically it:

- 1. demonstrates how a tool set can be used to gain an understanding of the behaviour of the system, to help to identify and correct ambiguities that arise in the earlier stages of development;

- 2. shows how an incremental development approach can be used: first to verify properties of increasingly realistic models of the system, building confidence about the correctness of a model of the implementation at each stage; and second to gain an increased understanding of the behaviour of the system as properties of those increasingly sophisticated models are explored. The better understanding gained in the earlier stages can to help to identify properties that need to be observed by the models in the later stages;

- 3. identifies a means of recording assumptions in the specification, to help ensure they are not overlooked, thereby introducing errors in the design and implementation; and

- 4. shows that it is possible to use a compositional rely-guarantee method to verify properties of systems where the individual components give few or no guarantees about their individual behaviour. It may then be possible to use the rely-guarantee conditions that have been verified to hold, to explore and verify properties of larger systems, where the system is itself used as a component.

#### 1.3 Thesis Structure

The remainder of this thesis is structured as follows: First Chapter 2 introduces a taxonomy of asynchronous communication mechanisms. [Lam86b] gives a taxonomy of ACMs that give increasing guarantees about their behaviour: the ACM that gives the strongest guarantees is called atomic. The taxonomy described in this thesis builds on that from [Lam86b] and includes additional types of ACM that can be used to build more complex ACMs. The taxonomy uses Real-time Logic (RTL), [JM94,JMS88], to reason about the timing of actions of the reader and writer to the ACMs. Chapter 3 introduces a number of communication mechanisms: first a series of mechanisms are described that require varying degrees of synchronous atomic ACM implementation is introduced. While the taxonomy in the previous chapter is not used directly to verify the correctness of any implementations. Chapter 3 also shows how Simpson's 4-slot can be constructed from components, some of which are described by the taxonomy.

12

Chapter 4 describes an abstract model of atomicity and verifies the correctness of the model. This model forms the basis for the proofs in the remainder of the thesis, when Simpson's 4-slot (an implementation of a fully asynchronous ACM) is used as a case study to demonstrate the use of a tool set in developing a system in an incremental manner. Chapter 5 shows how the 4-slot implementation can be shown to be a refinement of the model in Chapter 4 (subject to an assumption about the atomicity of the actions of the component processes). Chapter 6 then describes a compositional relyguarantee method that can be used to verify properties of implementations where the individual actions of the components are (Hoare) atomic (for example implementations on single processors). This method is used to verify that the 4-slot implementation is (Lamport) atomic when the actions of the reader and writer can interleave in an unconstrained manner. The models described in Chapters 2 to 6 are given using a VDM-like syntax, and have all been encoded in the PVS logic using the encoding of VDM-SL operations from [ABM98]. Chapter 7 describes how it is possible to verify properties of fully asynchronous implementations of the 4-slot, using CSP. [Hoa85, Ros98], and the FDR tool [Ros98]. The conclusions from the work are given in Chapter 8. Complete details of the formal models that have been used to verify properties of the implementation are contained in Appendices D to I, in the PVS logic (a brief explanation of the translation from VDM-SL to the PVS logic is given in Appendix A), and the complete CSP model from Chapter 7 is given in a further appendix.

# Chapter 2

# A Taxonomy of Asynchronous Communication Mechanisms

A range of asynchronous communication mechanisms that is available to developers was briefly introduced in Section 1.1.2, and a range of single reader, single writer ACMs will be further described in Chapter 3. This chapter presents Lamport's taxonomy of registers [Lam86b] and extends it to encompass the ACMs that are of interest in the design methods under consideration in this thesis. Lamport's taxonomy describes three different types of register, called safe, regular and atomic, which give increasingly strong guarantees about their behaviour when readers and writers access them, in terms of the items that are communicated between those readers and writers. Safe registers give the weakest guarantees about their behaviour and atomic registers give the strongest guarantees: an atomic register guarantees that the behaviour of the register will be equivalent to some Hoare-atomic interleaving of the read and write accesses. A second paper published at the same time, [Lam86a], introduces a formal definition of the meaning of implementing a system with (instances of) a lower level one, and for reasoning about concurrent systems. [Lam86b] gives examples of registers with stronger guarantees being implemented with registers that give weaker guarantees, including an atomic register that uses regular ones, and the formalism is used to prove the correctness of these implementations. The taxonomy is not used directly to explore properties of communication mechanisms in this thesis, however it includes formal definitions of the desirable properties of ACMs, as will be described later in this chapter. In addition Section 3.3 describes how instances of one the types of ACM from the extended taxonomy can be used as components to construct Simpson's 4-slot ACM and

<sup>&</sup>lt;sup>1</sup>These registers are used for asynchronous communication between processes or components in a system and they will be referred to as ACMs in the sequel, except where direct reference is made to Lamport's work.

a model of (Lamport) atomicity is used to verify properties of the 4-slot in Chapters 5 and 6.

The rest of this Chapter is organised as follows. The formal definitions of the ACMs in the taxonomy use RTL to reason about the ordering of actions of the readers and writer of ACMs, and RTL is introduced in Section 2.1. Lamport's taxonomy of asynchronous registers is described in Section 2.2, and Section 2.3 critiques Lamport's taxonomy. An extended taxonomy, which includes additional types of ACM that are used in practice, both for communication between processes in distributed systems and for constructing other ACMs, is given in Section 2.4 and a formal model of the extended taxonomy is given. Section 2.5 describes some desirable properties of ACMs and relates these properties to the taxonomy, and finally Section 2.6 discusses why the taxonomy has not been used directly to verify properties of ACM implementations.

#### 2.1 Real-time Logic

The taxonomy in this chapter requires a means of reasoning about the timing properties of the ACMs it defines. One of the first methods proposed for specifying timing properties of real-time systems was Real-Time Logic (RTL), [JM86, JMS88]. RTL is based around the concept of timed events. which can be the start and end events of a particular action, for example. In RTL events occur at specific times, have no duration and can recur many times during the operation of a system. Each occurrence of a particular RTL event must occur at a different time, and later occurrences must occur at a later time to earlier occurrences<sup>2</sup>. RTL can, therefore, be used to reason about the ordering of events during the execution of a computation, for example. RTL has been used in the definition of the semantics of several graphical notations for specifying and designing real-time systems, for example Modecharts, [JLM88, JM94, MSJ96]; in defining the semantics of a hierarchy of communication protocols [Sim03] and for for defining the semantics of Real-Time Kernels, [FW96, FW97]. [Pay01] proposes an extension to RTL to allow the use of *continuous* time, rather than discrete time. Time can then be specified using  $\mathbb{R}_{>0}$ , the positive real numbers including zero. That extension is not considered in this thesis.

RTL associates events with the number of occurrences of those events up to a particular time. The original RTL syntax used an uninterpreted function, @, which returned the time of a particular occurrence of an event:

$$@: Event * Occ \to Time$$

(2.1)

<sup>&</sup>lt;sup>2</sup>RTL does not support the super dense micro model described in [MP93].

where Event, Occ and Time represent types of events, occurrence numbers and times, respectively. A type of event can be, for example, the start or end of a computation, Occ is often represented using  $\mathbb{N}$ , the set of all natural numbers, where 0 is used as the occurrence number for the first, or *initial* occurrence of an event. Time is taken to be discrete, or more precisely as  $\mathbb{N}^-$ , the set of positive natural numbers. There is no concept in RTL of different types of events that occur at the same *instant* of time being ordered, nor of any causal relationship between events<sup>3</sup>. This original syntax has the drawback that the function,  $\mathbb{Q}$ , is partial: for example, the time returned is undefined if the event does not have an ith occurrence.

@ has been used in later papers (for example [JM94]), however [JMS88] advocated the used of an occurrence relation.  $\Theta$  to replace @. The relation.  $\Theta$ , has the following signature:

$$\Theta: Event * Occ * Time \rightarrow \mathbb{B}$$

(2.2)

and asserts that a particular occurrence of an event occurs at a particular time. This relation is used in the definitions of the different types of ACM in the taxonomy given in this chapter, because it has the advantage of being total, which considerably simplifies the logic, and allows classical theorem provers, such as PVS [OSRSC99b], to be used to reason in RTL.

It should be noted that it is not essential to include occurrence numbers in the definition of the occurrence relation, since occurrence numbers can be derived from the event types and times. Indeed the embedding of RTL in the PVS logic given in Appendix B uses such a relation, called  $\psi$ . The inclusion of occurrence numbers in the  $\theta$  relation does, however, help to simplify the some of the definitions of the extended taxonomy given in Section 2.4, and also simplifies the proofs of some of the theorems that verify properties of RTL and the taxonomy, for example where the proof of a theorem is discharged by induction.

# 2.2 Lamport's Taxonomy of Asynchronous Registers

This section describes Lamport's taxonomy of asynchronous registers, but first the distinction between the *base type* that an ACM can communicate and the *valid type* that it is specified to communicate is introduced. This distinction is important in the definitions and discussion that follow.

<sup>&</sup>lt;sup>3</sup>It is not possible to specify that one event caused another, simply that they are ordered in time.

#### 2.2.1 Base Type and Valid Type

[Lam86b] distinguishes between the different values that a register is capable of communicating, its base type, and the values that it is specified to communicate, its valid type. A register implementation consists an area of memory that is used to communicate data. The register is capable of containing any value that can be represented by the different combinations of values of the individual bits from which that area of memory is composed. its base type. For example, a register that uses an 8 bit area of memory for communication between its reader and writer can communicate 256 different values. If the ACM is designed to communicate natural numbers these 256 values may correspond to the numbers 0 to 255. It may be, however, that the specification of the ACM states that it should communicate the numbers 0 - 199 between its reader(s) and writer(s). This smaller set of values constitutes the valid type for that particular ACM implementation. In some implementations the base type and the valid type are the same, as would be the case in the above implementation if the ACM was specified to communicate the values 0 to 255.

#### 2.2.2 Lamport's Taxonomy

[Lam86b] describes three types of asynchronous register, for which following descriptions are given:

...The weakest possibility is a *safe* register, in which it is assumed only that a read not concurrent with any write actions obtains the correct value - that is the most recently written one. No assumption is made about the value obtained by a read that overlaps a write, except that it must obtain one of the possible values of the register...

...The next stronger possibility is a regular register, which is safe, (a read not concurrent with a write gets the correct value) and in which a read that overlaps with a write obtains either the old or new value. ... More generally a read that overlaps any series of writes obtains either the value before the first of the writes or one of the values being written...

...The final possibility is an *atomic* register, which is safe and in which reads and writes behave as if they occur in a definite order. In other words, for any execution of the system, there is some way of totally ordering the reads and writes so that the values returned by the reads are the same as if the operations had been performed in that order, with no overlapping...

These concepts are now described in more detail in order to clarify the definitions. A distinction is made in this thesis between items and values communicated: this distinction is important when it is necessary to reason about the ordering of reads and writes to the mechanisms. It is possible for the writer of an ACM to coincidently write the same value on a number of (possibly consecutive) occasions. In order to distinguish between several attempts to communicate the same value, in the descriptions and models, each value written to the ACMs is encapsulated in an item, and each item is given a unique serial number<sup>4</sup>, which increases by one for each item written. Implementations of the ACMs may only be required to communicate values, if no distinction is necessary between different instances of the same value being communicated.

#### Safe Registers

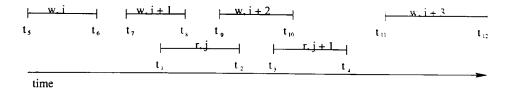

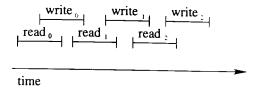

Figure 2.1: Reading From and Writing To an ACM

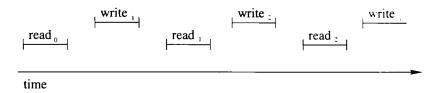

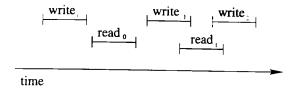

The behaviour of a safe register is described using the example behaviour illustrated in Figure 2.1, which shows a possible set of interactions of a writer and reader to the register. There are four write accesses and three read accesses, where the durations of the reads and writes are indicated by the length of the line segments. In this example, because  $read_1$  does not overlap any of the writes to the register, it will read the latest item that is available; the item written by  $write_1$ . In the cases of  $read_2$  and  $read_3$ , however, which do overlap with writes to the register, no guarantee is given about the items returned, other than that their values will be of its valid type. These reads can return any of the possible values that are specified to be communicated by the register, including ones that have never been written. This is because the reader and writer are both accessing the same area of memory at the same time, and there is no guarantee about how their actions will interleave.

<sup>&</sup>lt;sup>4</sup>Chapter 3 introduces a model which uses a sequence to represent the items of data that are available to a reader. The model conforms to the VDM convention that the index numbers of sequences start at 1, and the indices of the data items the model, and all of the models in subsequent chapters, also start at 1. The models in the Appendices, that were used to verify properties of ACMs, are given using the PVS logic and the index numbers there commence at zero, since the indices of PVS finite sequences commence at zero.

In the case of read2 the reader may return part(s) of the items written by write<sub>1</sub>, write<sub>2</sub>, write<sub>3</sub> and write<sub>4</sub>, and read<sub>3</sub> may return part(s of the items written by write3 and write4, although it is possible that one or both of the reads may return complete items written by the respective writes. It should be noted that this behaviour is even possible where some guarantees are given about atomic accesses to data by the underlying hardware. For example, the hardware may guarantee that accesses to individual words are atomic, where the length of the word will be implementation specific. However, if a large data structure is being communicated, for example a database with many different fields, this guarantee is unlikely to be sufficient to ensure valid data is communicated if the reader attempts to read an item of data at the same time as it is being updated by the writer. The simplest implementation of a safe ACM is where the number of values in the data-set that is to be communicated is the same as the number of possible values that the register can represent. For example, if the ACM was implemented using 8 bits and there were 256 different values in the data-set, it would only be possible for the reader to return one of these (valid) values.

#### Regular Registers

A regular register is safe, in that a read that does not overlap with a write will get the latest item previously written, so in the example shown in Figure 2.1 read<sub>1</sub> will again get the item written by write<sub>1</sub>. A read that overlaps with a write, or more generally a number of writes, will return either the item previously written (by the latest write to finish before the read starts) or the item written by (one of) the overlapping write(s). So in Figure 2.1 read<sub>3</sub> could return the item written by write<sub>3</sub> or write<sub>4</sub>, and read<sub>2</sub> could return any one of the items written by write<sub>1</sub>, write<sub>2</sub>, write<sub>3</sub> or write<sub>4</sub>. Each of the reads must return a valid item, but it is possible for read<sub>2</sub> to return the item written by write<sub>4</sub> and subsequently for read<sub>3</sub> to return the item written by write<sub>3</sub>. This behaviour seems strange and may be undesirable in an implementation: it is likely that one of the assumptions of an implementation would be that the items would be read in the order they are written.

#### Atomic Registers

An atomic register has all of the properties of a regular one, but in addition the reads and writes behave as if they had occurred in a particular total order. In other words the implementation is equivalent to a Hoare-atomic sequence of reads and writes; although it is possible for the reader to read the same item a number of times, and for the writer to overwrite items before they have been read. A read that does not overlap with a write will return the item previously written, so read<sub>1</sub> in Figure 2.1 will return the

item written by  $write_1$ . A read that does overlap with a write, or more generally a number of writes, will return either the item written by the latest write that finished before the start of the read, or (one of) the item(s) overlapping write(s), as with a regular register. A read to an atomic register, however, cannot return an item that was written before the item returned by the previous read; i.e. the items must be read in the order that they were written. So in the example in Figure 2.1 an atomic register would behave in the same manner as a regular register, except that if  $read_2$  returned the item written by  $write_4$ ,  $read_3$  would also return the same item (the item written by the earlier write is not then available to the later read).

# 2.3 A Critique of Lamport's Taxonomy of Asynchronous Registers

Safe is a slightly strange name for Lamport's first class of register, where it is possible for a reader, that accesses the register at the same time as the writer, to read any valid value of the type being communicated. A more appropriate term is type-safe or type-compatible, and the term type-safe is used in the rest of this thesis to describe such a mechanism. Atomic is also a slightly unexpected description of any ACM, because this term usually refers to devices that achieve total ordering of reads and writes (not merely the appearance of it) via synchronisation of the reader and writer, for example Hoare's monitors[Hoa74]. This type of ACM will be referred to as L-atomic in the remainder of this thesis to distinguish this type of atomicity from Hoare-atomicity

[Lam86b] states that any single bit register is type safe. This is because, since the register can only hold two values, the reader must return one of the possible valid values that the register is specified to communicate as the result of a read. It is claimed that this is true even when the value is being overwritten by a new value, since the reader must return either the old or the new value. However a single bit control variable may not even be type safe in some implementations, if read and write accesses to the variable are fully asynchronous. For example, in a hardware implementation it is possible that the reader of the variable will access it when the value is changing, and the result returned by the read may not be a zero or a one. This possibility is fully described and addressed in Chapter 7.

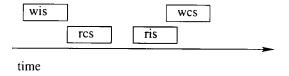

An important point to note is that Lamport's definitions are all couched in terms of complete reads and writes to the registers. However there is a subclass of ACM where there is a critical point during a read when the reader *chooses* to read a particular item, and also a critical point where an item written becomes available to the reader. Simpson's 4-slot is an example of

this type of ACM, as are the L-atomic ACMs in [Tro89.HS94.AG92]. These algorithms use buffers to communicate data between the reader and writer, and control variables; that the writer uses to indicate the buffer that the latest item of data has been written to, and that the reader uses to choose the buffer to read from. These control variables are used to ensure that the reader and writer access different buffers, if a read and write occur at the same time. Effectively the end of the write is when the writer has indicated the buffer that the new item has been written to, which is the time when the new item is available to the reader.

[Lam86b] gives an implementation of a regular register using single bit registers, and of a L-atomic register implemented using regular registers, and states that the weakest (presumably useful) possibility for an ACM is a type-safe one, because situations where anything weaker is used in implementations cannot be envisaged. Many later implementations of L-atomic ACMs (including Simpson's 4-slot) use a type of ACM, to implement buffers which are used to communicate the data items between the reader and writer, that has weaker guarantees than type-safeness. A definition of this weaker type, called persistent, is given in the next section, which describes some useful extensions to Lamport's taxonomy.

#### 2.4 An Extended Taxonomy of ACMs

This section describes an extended taxonomy that includes some useful types of ACM, in addition to those in Lamport's taxonomy, and describes a formal model of the extended taxonomy (The model given here is presented using an adaptation of VDM-SL, which uses the RTL  $\Theta$  relation to reason about the relative timing of actions. The model uses a shallow embedding of RTL in the PVS logic (due to Paynter), which is described in Appendix B, and the full formal model of the taxonomy, also in the PVS logic, is given in Appendix C). The taxonomy starts with a definition of a noisy ACM and builds successive ACMs that give progressively stronger guarantees about their behaviour, with the final definition being that of L-atomicity.

First the model defines a basic ACM, which has a base type of values it can communicate (all of the possible values its registers can represent); a valid type, which consists of all of the user-defined values that are to be communicated by it and is a (possibly complete) subset of the base type (the definition of a valid type is not given here, because it is implementation dependent, although all members of the valid type must also be members of the base type); and a mapping from time to the particular value of the base type that the ACM contains at that time. The valid type is not used in the definition of the basic ACM, but is used in the remaining definitions

to reason about values that can be written or read.

```

\begin{split} Value &= \mathsf{token}; \\ Time &= \mathbb{N}; \\ ACM :: baseType : Value\text{-set} \\ validType : Value\text{-set} \\ content : Time &\stackrel{m}{\longrightarrow} Value \\ \\ \mathsf{inv} \ \mathsf{mk-}ACM \ (bT, vT, c) \ \triangle \ (vT \subseteq bT) \land (\mathsf{rng} \ c \subseteq bT); \end{split}

```

The above definition is given in a VDM-SL like style, and the final line, starting with the VDM-SL keyword inv, is the invariant of the type. The VDM-SL keyword mk indicates the start of the type constructor, and mk-ACM(bT, vT, c) constructs an ACM with a base Type called bT, a valid Type called vT and a content called c. These names can then be used in the definition of the invariant that follows to refer to the relevant fields of the type.

The formal definitions below make use of the following auxiliary boolean functions (all of the auxiliary functions in the taxonomy are boolean functions, because they are used in the definitions of invariants, axioms and theorems):

val: This auxiliary function takes a reader or writer, an occurrence number and an ACM as parameters, and relates the values written to the particular occurrence of the read or write. The signature of the function is either val(r, i, v) or val(w, i, v) to reason about values read and written respectively. This function does not need to refer to the time of the occurrence, since the time can be derived from the occurrence number.

access: This auxiliary function relates a reader, or writer, to an access of an ACM, and the signature of the function is access(r, acm) or access(w, acm) respectively. This function does not refer to the time or occurrence number of the event, since it is only used in the definitions of a basic ACM and communicates (which relates the accesses to occurrence numbers and times as described below), to relate the read and write events to a particular ACM.

communicates: This auxiliary function takes a reader (when it has the signature  $communicates(r, i, t_1, t_2, v, acm)$ ) or writer (when its signature is  $communicates(w, i, t_1, t_2, v, acm)$ ), an occurrence number, two

times, a value and an ACM as parameters, and defines what it means for the reader, or writer, to communicate with an ACM, in terms of the start and stop times, occurrence number and the value written or read.

The basic type of ACM, from which the others are constructed, in the extended taxonomy, could be called noisy. It has at least one reader and a single writer, and gives no guarantees about the value a reader will return as the result of a read, other than it will be a member of the base type of the ACM. The writer writes valid values to it, but they may be corrupted as they are written or while they are contained in the ACM, so it is possible that the reader will never read values that have been written. A valid value is, however, communicated to the ACM by the writer when the system is initialised. This type of ACM would not ideally be used in any implementation, but there might be occasions when noisy would be the best description of the particular communication mechanism that is being used, and it is necessary to reason about the behaviour of a particular protocol built on such mechanisms. For example an implementation that uses the TCP/IP protocol for communication over a network would need to allow for the possibility of part(s) of the message being lost, or corrupted, in transmission. In order to ensure correct communication of complete data items the writer would be required to check that all parts of the items had been received and retransmit missing part(s) as necessary. The formal definition of a basic ACM is:

The first useful type of ACM in the taxonomy also has properties weaker than those of a type-safe ACM. Many implementations of L-atomic ACMs. such as those given in [Sim90a, Sim97, HS94], use this type of ACM, which will be referred to as *persistent*, for communicating the data items between the writer and reader. It is called persistent because, at the end of a write the ACM contains the item written to it, and the item will remain constant (persist) until it is overwritten by the next write. A persistent ACM has the following properties:

- 1. When a read access to the ACM does not coincide with a write the reader will return the item that was last written to the ACM.

- 2. A read access that coincides with a write to the ACM may not return a complete item that has been written: the value of the item returned can be any value of the base type.

The set of values that can be returned by a read that clashes with a write is determined to an extent by the type of the data that is being communicated, and also by the implementation of the ACM. Two examples of implementations of a persistent ACM are:

- An important implementation is dual port memory, which is memory that the reader and writer can access concurrently (effectively it resides on two different data buses). If the data consists of a single word (whatever size that happens to be), the reader can return any value that the ACM can contain. For example if the word size is 8 bits, the reader can return any of the 256 combinations that the word can take. Some, or all, of these values may be valid values of the type that is being communicated, depending on the size of the data type. If the valid type contains 256 different values the ACM will behave in the same way as a type safe register - whatever value is returned it will be one of the valid values of the type. If there are less than 256 values in the type it is possible that invalid values may be returned by a read in these circumstances. Even then the ACM can be made to behave in the same way as a type safe one, by mapping more than one value that the register can take to some, or all, of the valid values of the type being communicated. A read to dual port memory can return part(s) of the old value and part(s) of the new one.

- Another implementation is where a large data structure is being communicated. In this case the writer may be given control of a large part of memory so that it can assemble the new data value to be communicated, which may consist of a number of values of smaller sub-types. The underlying hardware may make it impossible for the reader to

access anything smaller than a word, but clearly if the reader accesses this area of memory while the new value is being assembled, it may return part of the old value and part of the new one.

This type of ACM requires some mechanism to ensure that it is not accessed by the reader and writer at the same time. Implementations of the class of ACMs described in this thesis all use buffers of this persistent type to communicate the items of data between the reader and writer. Separate control variables are used to indicate which of the slots the reader and writer are accessing. The reader and writer each check which data slot the other is accessing, before starting their own access, and then chose a different data slot to read or write respectively. The definition of a persistent ACM makes use of the auxiliary boolean function conflicting\_read, which returns true if an occurrence of a read occurs concurrently with one or more writes to the ACM. This function takes a reader and an occurrence number as parameters and has the following signature:  $conflicting\_read(r, i)$ . The definition also needs to distinguish between the start and end of writes to the ACM, and a the start of a write is referred to by the start(w) event in the auxiliary functions. Similarly the end of a write could be referred to as end(w) and the start and end of a read as start(r) and end(r), respectively. The formal definition of a persistent ACM is:

```

Persistent\_ACM :: b\_acm : Basic\_ACM inv \ mk-Persistent\_ACM \ (acm) \ \triangle \\ write\_val\_prop2(acm) \land persistent\_acm1(acm) \land \\ persistent\_acm2(acm) \land persistent\_acm3(acm) : write\_val\_prop2 : Basic\_ACM \rightarrow \mathbb{B} write\_val\_prop2 \ (a) \ \triangle \\ let \ w = a.writer, \\ acm = a.acm \ in \\ \forall \ i : Occ; \ v : Value; \ t_1, t_2 : Time \cdot \\ communicates(w, i, t_1, t_2, v, acm) \ \Rightarrow \\ acm.content(t_2) = v;

```

```

persistent\_acm1: Basic\_ACM \rightarrow \mathbb{B}

persistent\_acm1(a) \triangle

let w = a.writer.

acm = a.acm in

\forall i: Occ; t_1, t_2: Time; v: Value \cdot

communicates(w, i, t_1, t_2, v, acm) \Rightarrow

(\exists t_3 : Time \cdot \Theta(start(w), i + 1, t_3) \land

(\forall t: Time \cdot t_2 \leq t < t_3 \implies

acm.content(t) = v) \lor

\neg (\exists t_3 : Time \cdot \Theta(start(w), i + 1. t_3) \land

(\forall t : Time \cdot t_2 \leq t \Rightarrow acm.content(t) = v);

persistent\_acm2: Basic\_ACM \rightarrow \mathbb{B}

persistent\_acm2(a) \triangle

let acm = a.acm in

\forall r \in a.readers, i: Occ; t_1, t_2: Time; v: Value \cdot

communicates(r, i, t_1, t_2, v, acm) \land

\neg conflicting\_read(r, i) \Rightarrow acm.content(t_2) = v;

persistent\_acm3: Basic\_ACM \rightarrow \mathbb{B}

persistent\_acm3(a) \triangle

let w = a.writer,

acm = a.acm in

\forall v : Value, t : Time \cdot acm.content(t) = v \land

\neg acm\_being\_written(acm, t) \Rightarrow

(\exists t_1, t_2 : Time; i : Occ \cdot t_2 < t \land)

communicates(w, i, t_1, t_2, v, acm) \land

\neg (\exists t_3 : Time \cdot t_2 \leq t_3 < t \land \Theta(start(w), i + 1, t_3)));

```

(The auxiliary function acm\_being\_written is not given here, but defines what it means for a writer to be accessing the ACM in terms of the start and end times of the write access).

Lamport's type-safe ACM is the next in the taxonomy, where the reader is guaranteed to return a valid value as a result of a read as described in Section 2.2.2. It was originally thought that type-safeness was a sufficiently strong property so that a L-atomic ACM could be implemented using 4 type-safe single bit control variables. However, [HV01] gives an informal proof that 5 control variables are required in order to implement a L-atomic ACM from type-safe bits. This is an unpublished paper, but some preliminary results are published in [HS94] and [HV96]. Indeed [Rus02] shows that Simpson's 4-slot ACM is not L-atomic, but only regular, if its 4 control

variables are implemented using type-safe bits. The formal definition of a type-safe ACM is:

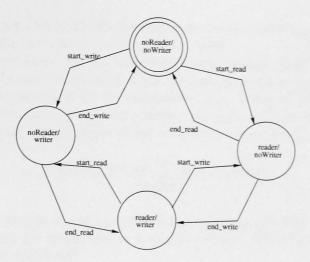

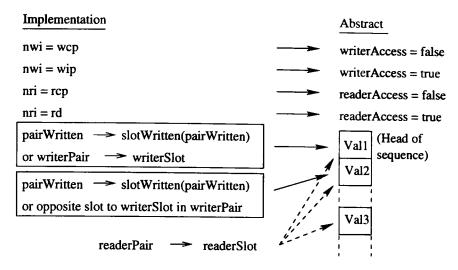

```