|                                                    | NEWCASTLE UPON TYNE<br>University Herary |

|----------------------------------------------------|------------------------------------------|

|                                                    | ACCESSION No.                            |

|                                                    | 83-10990                                 |

| GENERAL FURPOSE DECENTRALISED COMFUTER ARCEITECTUR | LOCATION<br>Thesis                       |

|                                                    | L2772                                    |

Richard F. Hopkins

Computing Laboratory, University of Newcastle upon lyne

# Fh.D. Thesis

1983

### ABSTRACT

This thesis is concerned with decentralised highly concurrent computer architectures which may eventually provide alternatives to the centralised sequential architectures of conventional generalpurpose computers. There is currently considerable research into such alternatives, for which the principal motivations are the use of concurrency to improve performance, the support of various novel, very high level programming languages, and the exploitation of very large scale circuit integration (VLS1). The different proposed alternative architectures are surveyed and analysed, and architectures synthesising their underlying concepts are proposed.

The thesis consists of three main parts. The first part is an analysis and survey of proposed general-purpose decentralised architectures. Three classes of architectures are identified, namely control flow, data flow and reduction. The analysis shows that each class has particular, complementary, strengths and weaknesses.

The second and third parts cover the development of two architectures which combine the different concepts underlying control flow, data flow and reduction in order to overcome the individual weaknesses in each. Thus the second part presents a "data/control flow" architecture which is a synthesis of data flow and control flow. There is an experimental implementation of this architecture in which a number of standard microcomputers cooperate in the execution of a program.

In contrast the third part presents a "recursive control flow" (RCF) architecture which is a synthesis of control flow, data flow and reduction. This architecture is based on a set of general principles of recursive structuring which are intended to provide a common basis for decentralised system organisation at various architectural levels, ranging from VLSI design to geographically distributed networks. The RCF work is thus not only an investigation into the possibility of incorporating control flow, data flow and reduction concepts in a single parallel computer but also an initial investigation of the application of the recursive structuring principles. These two aspects of the work are closely related in that recursive structuring facilitates the modularity which is required for the synthesis of control flow, data flow and reduction into a cohcrent overall system.

An implementation of the RCF architecture, using a number of identical microcomputers, is proposed. The detailed design of a special-purpose LSI microcomputer chip for this implementation is currently being produced.

### ACKNOWLEDGEMENTS

I gratefully acknowledge the diligence and interest taken in this research by my colleagues in the Computer Architecture Research Group, principally Philip Treleaven and Paul Rautenbach, and my thesis supervisor Brian Randell. Particularly I thank Fhilip Treleaven and Brian Kandell for having patiently read various drafts of this thesis and having made some improvement in my ability to write.

This research would have been impossible but for financial support from the Science and Engineering Research Council of Great Eritain both for myself as a research student and research associate, and for the computing facilities that I have used.

## CONTENTS

| 1   | INTRODUCTION.                              |

|-----|--------------------------------------------|

|     | .1Background1.2Thesis Gutline1             |

| 2   | ANALYSIS AND SURVEY                        |

| 2.1 | Operational Models 9                       |

|     | .1 Control Flow                            |

|     | .2 Data Flow                               |

|     | .3 Reduction                               |

|     | .4 Discussion                              |

| 2.2 | Program Organisation                       |

|     | .1 Data Structures                         |

|     | .2 Conditionals                            |

|     | .3 Procedures and Iteration                |

|     | .4 Non-Determinacy                         |

| 2.3 | Machine Organisation and Implementations43 |

| ~~~ | .1 Classification                          |

|     | .2 Control Flow                            |

|     | .3 Data Flow                               |

|     | .4 Reduction                               |

| 2.4 |                                            |

|     | .1 Expressive Power                        |

|     | .2 Concurrency and Ferformance 54          |

|     | .3 Exploiting VLSI                         |

|     | .4 Generality                              |

| 3   | COMEINING DATA FLOW AND CONTROL FLOW       |

| 3.1 | Operational Model 60                       |

| 3.2 | Program Organisation                       |

|     | .1 Data Structures 65                      |

|     | .2 Conditionals                            |

|     | .3 Iteration and Procedures                |

|     | .4 Non-Determinacy                         |

| 3.3 | Machine Organisation and Implementation 73 |

| 3.4 | Summary and Discussion                     |

(iii)

| 4   | GENERALISING CONTROL FLOW                 |

|-----|-------------------------------------------|

| 4.1 | Operational Model 80                      |

|     | .1 Storage Organisation                   |

|     | .2 Addressing                             |

|     | .3 Program Representation                 |

|     | .4 Program Execution                      |

|     | .5 Further Examples                       |

|     | .6 Discussion                             |

| 4.2 | Program Organisation                      |

|     | .1 Notation                               |

|     | .2 Including Control Flow, Data Flow      |

|     | and Reduction                             |

|     | .3 Data Structures                        |

|     | .4 Conditionals                           |

|     | .5 Iteration                              |

|     | .6 Procedures                             |

|     | .7 Higher Order Procedures                |

|     | .E Non-Determinacy                        |

|     | 9 Discussion                              |

|     |                                           |

| 4.3 | Machine Organisation                      |

|     | .] General Structure                      |

|     | .2 Special-Purpose Computing Elements 142 |

|     | .3 Extensibility                          |

|     | .4 Locality                               |

| 4.4 | Summary and Discussion                    |

|     | .] Combining Models 149                   |

|     | .2 Recursive Structuring                  |

|     | •2 Accurative bendetating••••••••••••••   |

| 5   | RECURSIVE SYSTEMS IMPLEMENTATIONS         |

| 5.1 | The LECO Design                           |

|     | .1 Memory                                 |

|     | .2 Processing                             |

|     | .3 Activity Migration and                 |

|     | Resource Allocation 163                   |

|     | .4 Communications                         |

|     | .5 Control Elements                       |

|     | .6 Multi-level Organisation 173           |

|     | .7 Discussion                             |

| 5.2 | UNIX United                               |

| 5.3 | BASIX                                     |

| 5.4 | RIRMS                                     |

| 5.5 | R.M                                       |

| 5.6 | Discussion                                |

(iv)

ر **6** CONCLUSIONS. . -207 -. -• 2 APPENDIX A - A ECF Machine Code .... 219 A.1 Machine Model. . . . . • • . .219 . -A.2 . . 222 A.3 . . . 222 A.4 A.5 A.6 A.7 A.9 REFERENCES .... -233

### INDEX TO FIGURES

| CI    | APTER | 2 |

|-------|-------|---|

| - UII |       |   |

| Conventional Control Flow                                       |

|-----------------------------------------------------------------|

| Multi-thread Control Flow                                       |

| Parallel Control Flow                                           |

|                                                                 |

| Data Flow                                                       |

| String Reduction                                                |

| Graph Reduction                                                 |

| Control and Data Mechanisms                                     |

| Unbounded Lata Structures                                       |

| Two Forms of Conditional in Data Flow                           |

| Procedures and Iteration in Lata Flow                           |

| Procedures and iteration in tala riow                           |

| Procedures in String Reduction                                  |

| Higher Order Procedures in Reduction                            |

| Non-determinacy in Data Flow                                    |

| Machine Organisations                                           |

| Some Novel Architectures                                        |

| Packet Circulation for Multi-thread Control Flow                |

| Packet Circulation for Data Flow                                |

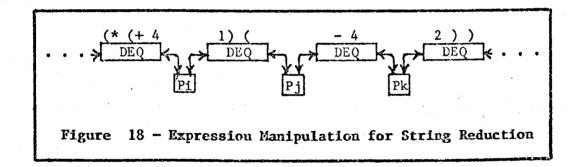

| Furnession Marinulation for States Poduction                    |

| Expression Manipulation for String Reduction                    |

| Pointer Reversal for Implementing Graph Reduction               |

|                                                                 |

| CRAPTER 3                                                       |

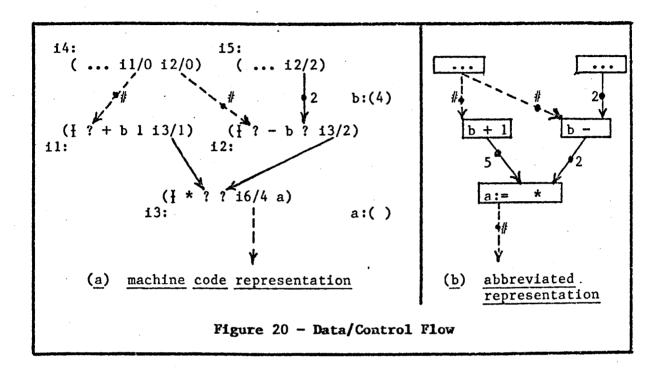

| Data/Control Flow                                               |

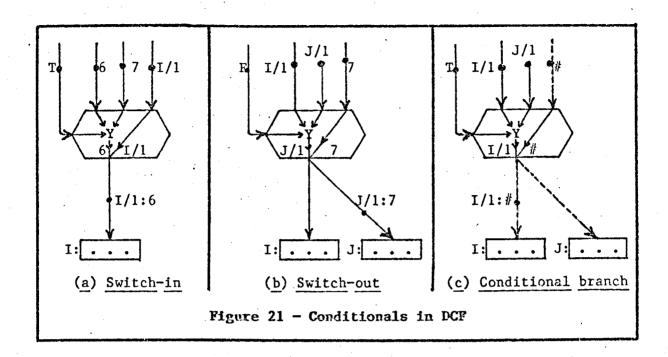

| Conditionals in DCF                                             |

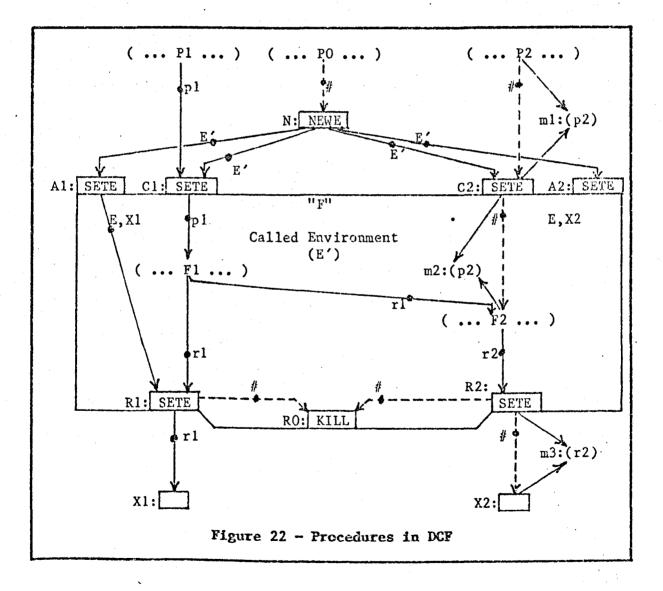

| Procedures in DCF                                               |

| Non-Determinacy in DCF                                          |

| Non-Determinacy in Dor                                          |

| DCF Machine Organisation and Implementation                     |

|                                                                 |

| CHAPTER 4                                                       |

| Addressing Selectors in RCF                                     |

| Addressing Selectors in RCF                                     |

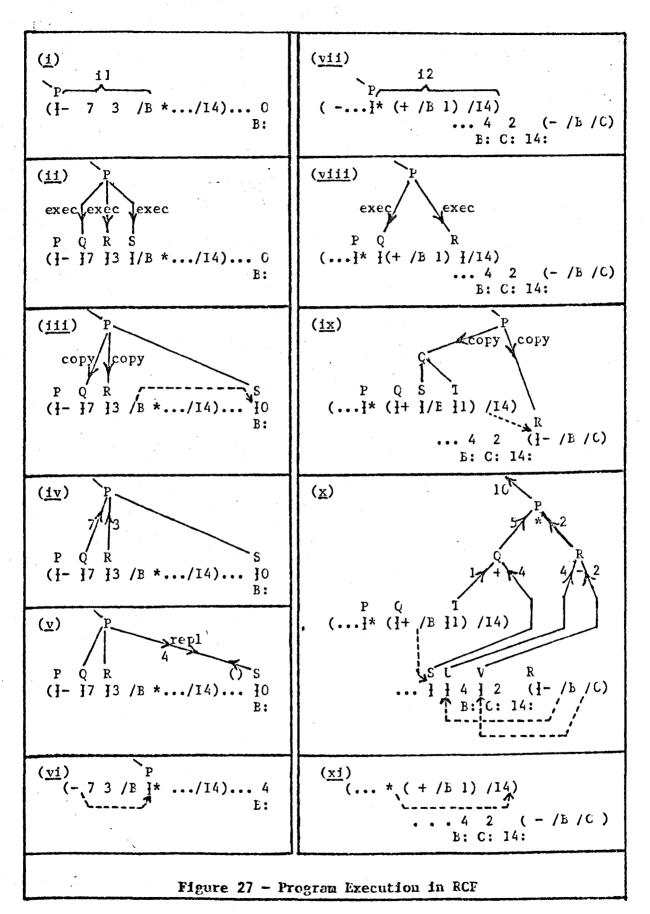

| Program Execution in RCF                                        |

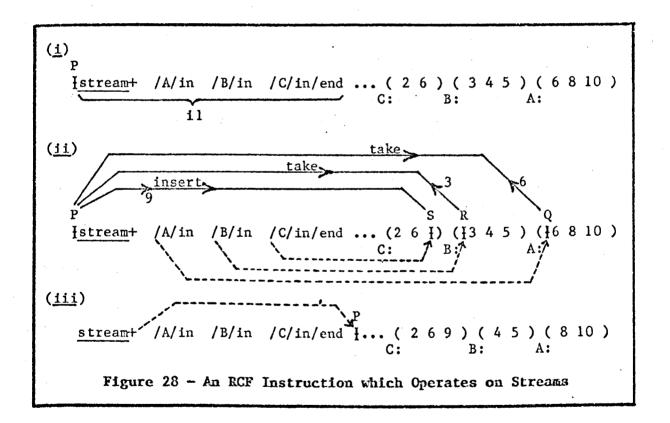

| An RCF Instruction which Cperates on Streams                    |

| An DCE Instruction which December of Constants and Arguments (7 |

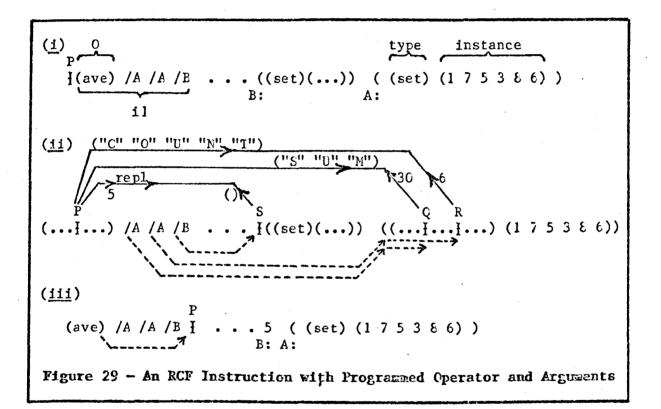

| An RCF Instruction with Programmed Operator and Arguments 97    |

| Different Organisations for Expression Evaluation in RCF 110    |

| Unbounded Data Structures in RCF                                |

| Three Forms of Conditional in RCF                               |

| Iteration Using FIFO Queues in RCF                              |

| Procedures in RCF                                               |

| Higher Order Procedures in RCF                                  |

| Non-determinacy in RCF.                                         |

|                                                                 |

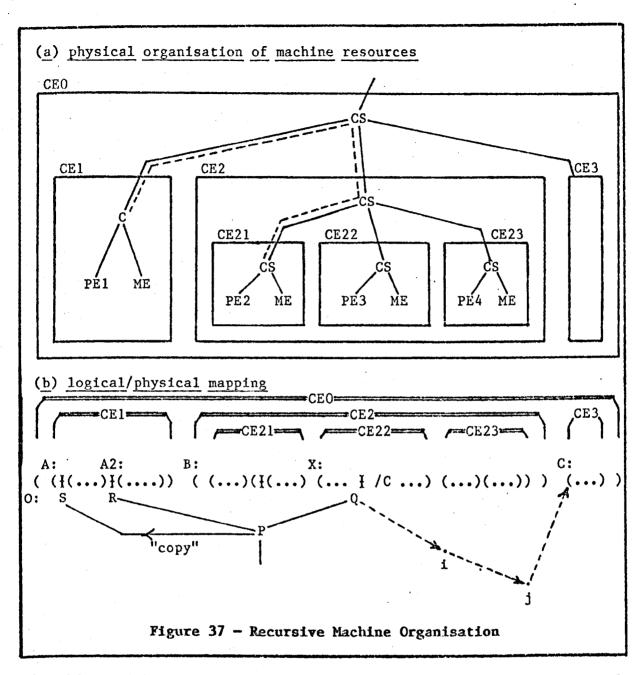

| Recursive Machine Organisation                                  |

|                                                                 |

| CHAPTER 5                                                       |

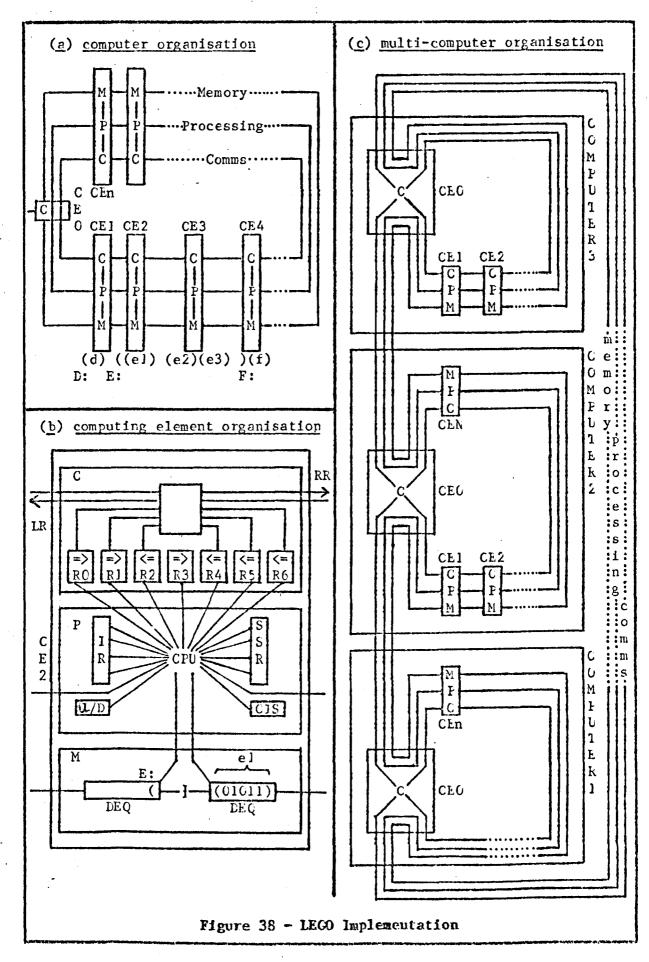

| LEGO Implementation                                             |

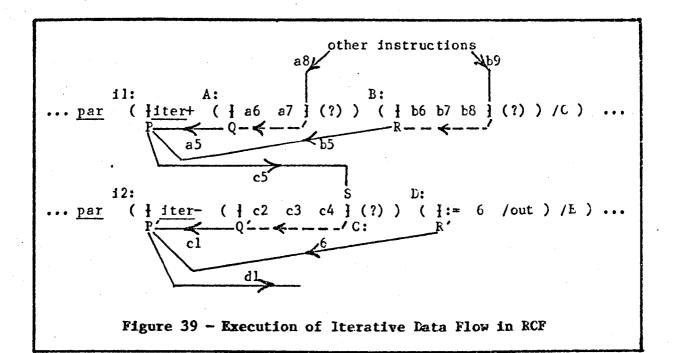

| Execution of Iterative Data Flow in RCF                         |

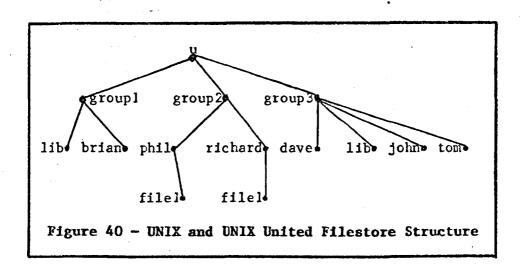

| UNIX and UNIX United Filestore Structure                        |

|                                                                 |

| APPENDIX A                                                      |

|                                                                 |

### 1. INTRODUCTION

#### 1.1. Eackground

Conventional von Neumann architectures can be characterised by a number of "von Neumann principles":

1. linear organisation of fixed size memory cells

2. one level address space, where each address is globally unique

- low level machine code in which instructions are elementary operations performed on elementary operands

- 4. sequential, centralised control of execution

- centralised machine organisation of a single computer incorporating processor, communications and memory

Although these principles have for over 30 years provided an adequate basis for general-purpose computers, there has recently been much interest in possible alternative general-purpose architectures. There are currently at least 20 research groups working on experimental, nonvon Neumann architectures in which one or more of the above principles are modified.

There are three main, related, motivations for this interest in novel architectures. Firstly there is the continuing demand for increased computing power, particularly in applications such as weather forecasting and wind tunnel simulation. The technologies available (and ultimately the natural laws of physics) limit the possible performance attainable for a single processor, and thus the ability of conventionally organised high-speed computers to meet these demands[1]. The utilisation of a large number of processors cooperating on a single task offers the potential of overcoming the technological performance limitations.

Secondly there is the interest in new classes of very high level applicative languages, particularly functional programming or languages [2,3], and logic languages [4], which are claimed to have greater expressive power than conventional languages and are intended to provide easier means of producing reliable programs. Whereas existing sequential assignment-based languages are well matched to the von Neumann architecture, these new classes of language are based on radically different principles, and implementations on conventional architectures tend to be relatively inefficient. An essential characteristic of these languages is that a program does not specify a sequence in which statements are to be executed and this naturally leads to highly concurrent implementations.

Thirdly there is the need to exploit very large scale integration (VLSI) in the design of general-purpose computers. There are a number of considerations in VLSI design which make it desirable to find an alternative to conventional architectures[5,6]. In particular there is the need to implement storage and processing functions close together on the same chip in order to minimise communications. These considerations lead to architectures such as [7] in which a large powerful computer is constructed from a multiplicity of simple single-chip microcomputers each incorporating a general-purpose processor and local memory. Research projects motivated by one or more of the above considerations have resulted in a number of experimental special-purpose and general-purpose architectures which are able to utilise many processors operating concurrently on a single task under decentralised control. In the special-purpose decentralised architectures the hardware organisation is closely matched to the concurrency structure of a particular class of tasks, as for example in Systolic Arrays[8]. The concern of this thesis however is with general-purpose decentralised architectures which can be programmed to perform effectively, and exploit implicit concurrency in, a large range of tasks.

Three classes of general-purpose computer architectures can be identified as control flow, data flow and reduction. These classes differ fundamentally in their operational models, that is in the way instruction execution is initiated and the way data is communicated between instructions. In control flow the execution of an instruction is triggered by the flow of control through the program, and data is communicated between instructions by being stored in shared memory cells. (Conventional von Neumann architectures have a single flow of control whereas control flow architectures providing concurrency have multiple flows of control.) In data flow the execution of an instruction is triggered by the availability of the input data that it uses and when executed an instruction stores its result directly into those instructions which use that result. In reduction the execution of an instruction is triggered by the requirement for the output data which it generates and when executed an instruction is replaced by (is reduced to) its result. The single most important characteristic of the novel data flow and reduction models is that they are implicitly concurrent. If

- 3 -

several data flow instructions have all their inputs available then they can all be executed concurrently. If one reduction instruction requires the outputs from several other instructions then those instructions can be executed concurrently. In contrast, the concurrency provided by multiple flows of control is explicitly controlled by the programmer.

Parallel computers form one of two major fields of decentralised computing systems research, the other being that of geographically dis-There is some degree of relationship tributed computer networks. between these two fields. The design of individual computers may be affected by the likelihood of their being connected into computer networks. Similar functions may be found in both types of decentralised system, for example to organise the cooperation between concurrently executing program units, and the decentralised allocation of system resources. There is the possibility of the same microcomputer being used as one of the processors for a general-purpose parallel computer, as the main processor of a node in a local area network, or as a component of an embedded system such as an on-board flight control system. This latter class of system could be considered as either a specialpurpose parallel computer or a small-scale computer network. Thus the distinction between parallel computer architecture and computer network architecture is becoming more a matter of degree than fundamental difference. These considerations have contributed towards developments such as the "building sized computer" of [9], the Intel 432[10] and transputers[11]. In terms of the three classes of architectures identified above, these developments are all based on the conventional control flow model (rather than one of the novel, implicitly concurrent models) and carry forward most of the von Neuman principles.

- 4 -

### 1.2. Thesis Outline

The principal work reported here consists of an analysis of control flow, data flow and reduction computers and the synthesis of their underlying concepts, together with the application of principles of recursive structuring, in the design of general-purpose decentralised computer architectures. The application of recursive structuring principles in the context of geographically distributed computer networks is also considered. This research constitutes a major part of the work of the Computer Architecture Research Group at the University of Newcastle upon Tyne. Much of the work covered by this thesis, together with related work of other members of the group, has been previously reported elsewhere[12-18].

5

The first part of the thesis, Chapter Two, is an analysis and survey of existing control flow, data flow and reduction architectures. The basis for this analysis is the classification first developed by Treleaven and myself in [14] and subsequently expanded by ourselves and Brownbridge in a broad survey of data flow and reduction computers[16]. This Chapter repeats and further develops those parts of [16] to which I made a major contribution. It covers for each class of architecture the operational concepts on which it is based, the ways in which machine code programs are organised, and the ways in which machine resources are organised. The analysis shows that a fundamental characteristic of an architecture, largely determining its particular and strengths weaknesses, is the choice of mechanisms provided for propagating control and data through a program. The strengths and weaknesses of control flow, data flow and reduction are largely complementary which suggests experimenting with combinations of the concepts and mechanisms found separately in each.

All the novel computer architectures discussed in this Thesis, data flow and reduction covered in Chapter 1 and the experimental architectures developed subsequently, provide for computing machines that are Universal, in the Turing Machine sense. Thus the only ultimate criteria for their evaluation is their "efficiency" in terms of hardware cost, program execution performance, and production costs of software to provide an effective user interface and to organise the effective exploitation of machine resources. Quantitative evaluation of an architecture in those terms requires extensive experimentation on "realistic" imple-However at the time of writing, development of novel data mentations. flow and reduction architectures has only progressed to the point of "demonstration" rather than realistic implementations. Thus they can as yet only be evaluated in qualitative terms of particular conceptual strengths and weaknesses which may be expected to affect their quantitative characteristics. These comments apply even more to the highly experimental architectures covered in the subsequent Chapters which build on the concepts of data flow and reduction and are in an even earlier stage of development.

The second part of the thesis, Chapter Three, presents an experimental architecture which is a synthesis of data flow and (concurrent) control flow[13,15]. The original idea of such a synthesis was first suggested by Treleaven and developed into this architecture principally by Rautenbach and myself. This Chapter is a summary of the full report on the architecture[12] covering its operational model, program organisation and machine organisation. Implementations of the architecture, based on several cooperating microcomputers, were subsequently developed by other members of the Computer Architecture Group and are reported on in detail elsewhere[19,20].

The third part, Chapters Four and Five and Appendix A, presents a second experimental architecture, the recursive control flow architecture, which is a synthesis of control flow, data flow and reduction obtained by generalising the conventional von Neuman architecture. This generalisation is based on the use of recursive decentralised structures, and involves the replacement of all the von Neuman principles by corresponding "recursive principles":

1. hierarchy of variable length memory cells

- 2. contextual address space, where an address is a variable length sequence of selectors like a telephone number

- recursive machine language in which instructions may contain elementary or complex operations or operands

- 4. parallel, decentralised control of execution

- 5. network of computing elements with each element incorporating processor-communications-memory and a group of computing elements being functionally equivalent to a single computer

Chapter Four covers the architecture's operational model, its program organisation and machine organisation. Also, towards the end of Chapter Four there is a discussion of the applicability of the recursive control flow operation model and machine organisation in the context of geographically distributed networks. Chapter Five covers a proposed hardware implementation of the recursive control flow architecture using large numbers of a special-purpose LSI chip. Appendix A defines a machine code instruction set for this implementation. Chapter Five also covers a number of other computing system implementations which incorporate similar recursive structuring concepts, including both a general-purpose parallel computer and a computer network system.

The material contained in these two Chapters and the Appendix is original to this thesis and has not been published elsewhere, although it is based on outline ideas proposed by Treleaven and myself in [17]. The proposed implementation is now being developed by another member of the Computer Architecture Group in order to produce a detailed chip design.

Chapter 6 presents the main conclusions of the thesis. It is claimed that the recursive control flow architecture enables the different styles of control flow, data flow and reduction programs to be easily combined, so that each can be used where appropriate. Also that the architecture in general provides a promising basis for future general-purpose decentralised VLSI computing systems, and warrants further development. Further work to be done and possible lines of future development are then identified.

- 8 -

### 2. ANALYSIS AND SURVEY

This Chapter covers recent research into general-purpose decentralised architectures, particularly in the areas of data flow and reduction. Currently there are many research groups working in these areas, a number of whom have produced experimental machine designs[16]. The purpose of this Chapter is to identify the concepts and relationships within these areas of research and to discuss the advantages and disadvantages of different approaches. The Chapter starts by introducing the operational models underlying control flow, data flow and reduction architectures, then discusses ways in which the architectures are programmed and implemented, and finally evaluates their main advantages and disadvantages.

### 2.1. Operational Models

Control flow, data flow and reduction architectures are each based on different concepts of the way programs are represented and executed and the way control and data are passed from one part of a program to another. In order to illustrate and compare these basic concepts I will discuss the representation and execution of an example program fragment, the statement a:= (b+1) \* (b-c), in terms of simple operational models for each class of architecture. For the operational models an abstract machine code representation will be used in which an instruction is a sequence of arguments delimited by brackets. For example the (b+1)might be represented as the machine code instruction (+ b l tl) with four arguments, the last of which, tl, identifies the destination of the result. At a particular point in the execution of a machine code

- 9 -

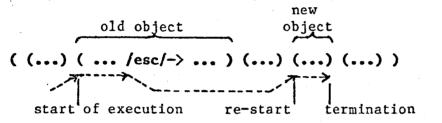

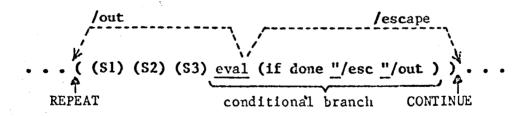

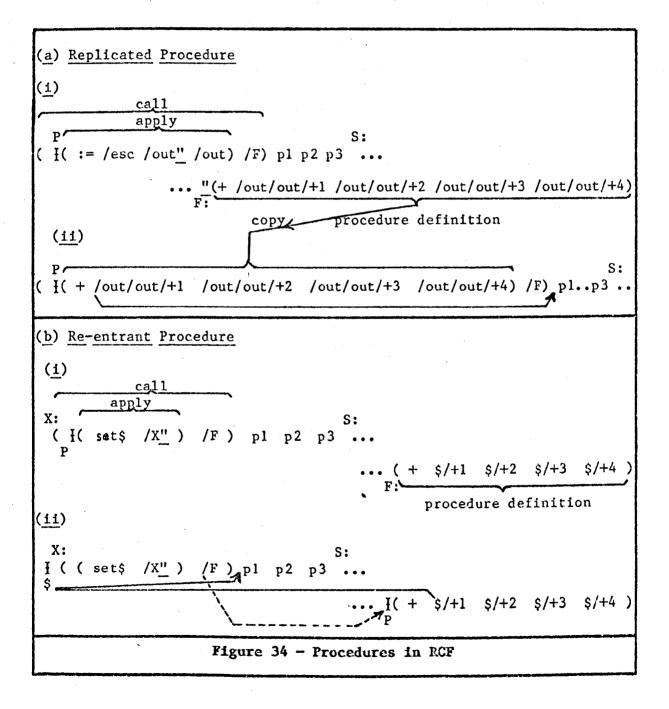

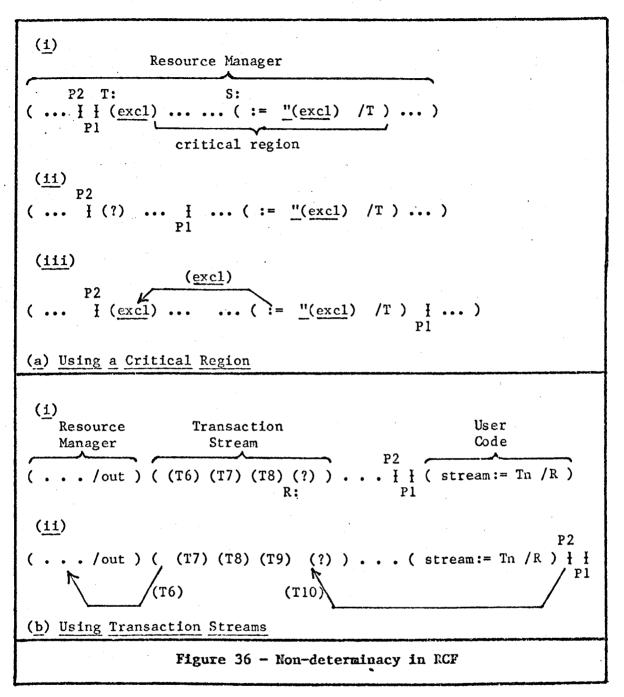

program there will be (one or more) active instructions to be executed. For example in a conventional architecture the instruction pointed to by the program counter is the single active instruction. In discussing the operational models, the progress of execution through a program will be indicated by marking a currently active instruction with a ], referred to as an "activity". For example (]+ b l tl) means that the + operator is about to be executed and the activity, ], can be thought of as representing an actual processor to execute that operator.

### 2.1.1. Control Flow

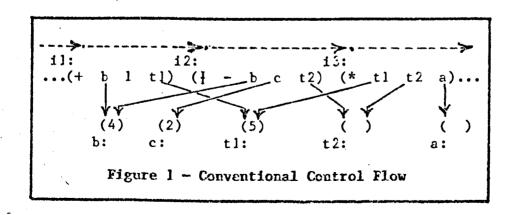

Figure 1 shows a conventional control flow representation for the example a:= (b+1) \* (b-c). There is a sequence of instructions, i1, i2 and i3, and some shared memory cells, b, c, t1 etc., for passing data between instructions. Each instruction (e.g. i1) consists of an operator (+), input arguments each of which may be a literal (1) or a reference (b) to a memory cell, and a reference (t1) to the memory cell for the result. The references to memory cells are also shown as solid arcs.

There is a single activity, I, shown at 12, which passes from one

- 10 -

instruction to the next along the thread of control shown by dotted arcs. To execute an instruction, addressed operands are loaded from memory, the result is computed as defined by the operator, the result is stored back in memory, and the activity then implicitly passes on to the next instruction in sequence.

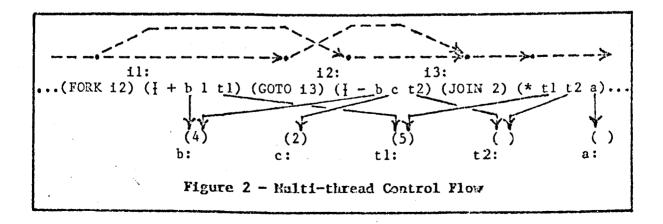

There are also forms of control flow which provide concurrent pro-In the "multi-thread" form of control flow, convengram execution. tional control flow is augmented by special control operators for creating and synchronising multiple threads of control, such as the FORK and JOIN shown in Figure 2. After the execution of the FORK there are two activities, one at its implicit successor, il, and one at the addressed instruction, 12. Instructions il and i2 thus execute concurrently. Both activities will then reach the JOIN instruction, either via the explicit GOTO following il, or as the implicit successor of i2. The JOIN synchronises the two activities and then execution continues with its implicit successor, the multiply instruction. Apart from the inclusion of such special control operators multi-thread control flow is similar to conventional control flow.

- 11 -

Another form of concurrent control flow, shown in Figure 3, is "parallel" control flow in which instruction execution is controlled by explicit control signals or control tokens, rather than there being implicitly sequential threads of control. All instructions can potentially execute in parallel, but each instruction requires some number of control tokens from other instructions before it can actually execute. In Figure 3 each ? in an instruction is a control argument representing the requirement for a control token. When an instruction has executed it transmits control tokens to successor instructions identified by its final reference arguments (the flow of control tokens is represented by dotted arcs). A reference for a control token, such as 13/2 in 12, specifies a particular argument position, 2, in a particular instruction, i3. This form of control flow is logically equivalent to multithread control flow, with multiple successors (as in 14) corresponding to a FORK, and multiple control arguments (as in i3) corresponding to a JOIN.

#### 2.1.2. Data Flow

Data flow architectures provide highly concurrent program execution without the programmer needing to organise the concurrency explicitly. This is achieved by basing execution on the availability of data so that concurrency is implicit - any instruction can execute if all its operands have been produced.

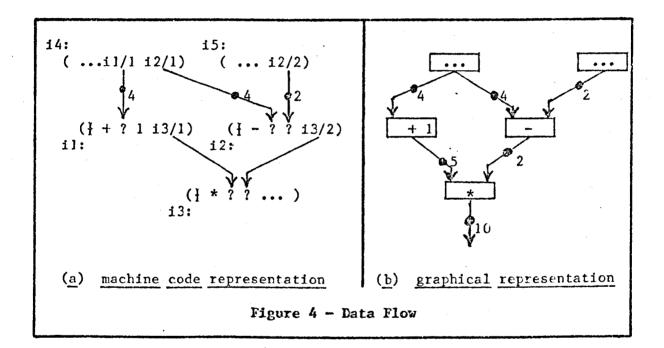

Figure 4 shows a data flow program for the same example, using in (a) a machine code representation and in (b) a more usual graphical representation (data flow programs are often referred to as data flow graphs, with the instructions being referred to as nodes). An instruction (e.g. 11) consists of an operator (+), input arguments each of which may be a literal (1) or an unknown (?), and output arguments each of which is a reference (13/1). An output reference identifies a destination instruction (13) and a particular unknown argument position (1). (These references specify the flow of data through the program which is also shown by solid arcs.)

All instructions are notionally active and can potentially execute in parallel, execution being constrained by the availability of data. When an instruction (e.g. 14) has executed it transmits its result (the value of b, i.e. 4) as data tokens to the other instructions using that result. (Data tokens are shown as black dots flowing down the arcs.) A data token overwrites an unknown in the destination instruction, thereby making its value available to that instruction. When all of an instruction's operands are available, i.e when all unknowns have been replaced by results, it can execute, computing its result which is then transmitted to further instructions. (In terms of the graphical representation, an instruction executes when a data token is present on each of its input arcs and places its result on all its output arcs.)

### 2.1.3. Reduction

In data flow and concurrent forms of control flow, the major divergence from conventional control flow is in providing for concurrent program execution. These architectures retain the conventional form of program representation in which a program is a collection of fixed size instructions whose arguments are primitive operators and operands. In contrast, the principal concern in reduction architectures is the direct support of very high level applicative programming, which motivates a different form of program representation. In reduction an "instruction" is an expression comprising a function or primitive operator and its arguments. Each argument may be a simple operand or a nested expression. A program is a set of named expressions each defining a value. For example the program fragment -

# $a \equiv (b+1) * (b-c)$ where $b \equiv 7-3$ , $c \equiv 2$

gives a definition for a using subsidiary definitions for **b** and **c**. Unlike a named variable of control flow, a named definition has a fixed value (possibly determined by parameters). Thus a reference such as **b**, its defining expression, 7-3, and its value, 4, are all mathematically equivalent and can be freely interchanged without affecting the result of the program. The interchangeability of a reference and the referenced expression is an important property known as "referential transparency". This property is claimed to facilitate both informal understanding of a program and its formal manipulation in for example program verification.

In executing a reduction program instructions are progressively evaluated and replaced by their results until the program has been reduced to its simplest form. Reduction architectures differ both in the order in which instructions are selected for evaluation and in the way in which instructions are represented and manipulated. The order of evaluation is not explicitly controlled by the programmer but is determined by an implicit "computation rule". There are a number of possible computation rules[21], the main differences being between "innermost" and "outermost" rules. An innermost computation rule only selects instructions with literal (fully evaluated) operands (initially the instructions will result in other instructions being selected. An outermost computation rule starts with the instruction for the required result (the multiplication in this example) and is recursively applied

- 15 -

to evaluate the required operands. Every computation rule produces the same result for a program, if the program terminates with that rule. However there are programs which terminate with an outermost computation rule but not with an innermost rule, and subsequently I will concentrate on reduction architectures using outermost computation.

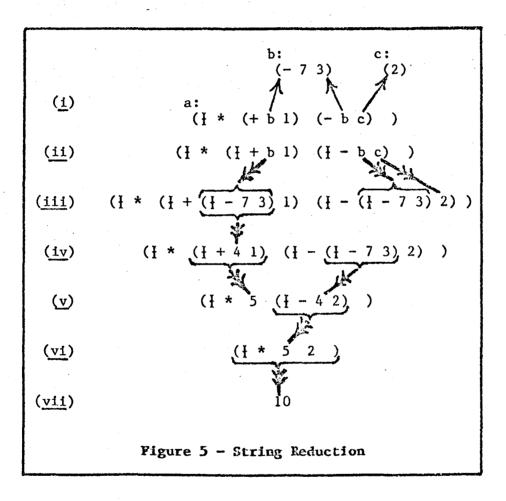

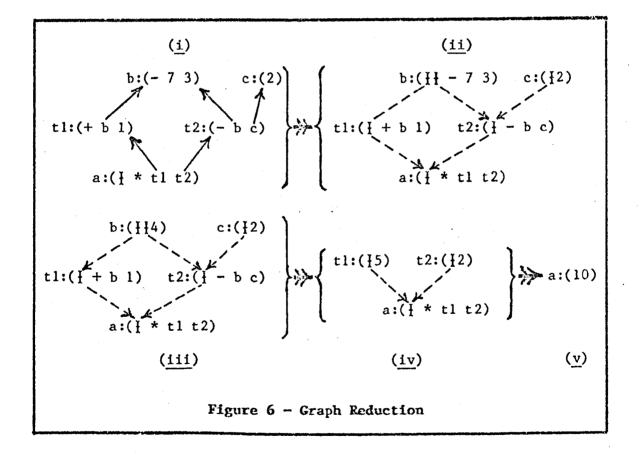

There are two forms of expression representation and manipulation found in reduction architectures, referred to as string reduction and graph reduction. In string reduction, as illustrated in Figure 5(i), an expression is represented as a string of symbols comprising operators, operands and references to other definitions, with structure represented by delimiter symbols ( and ). As the expression is evaluated the referenced definitions are copied into the string. In graph reduction, as illustrated in Figure 6(i), the components of an expression are always separate definitions, referenced by the expression. Referenced definitions are executed in place rather than being copied into the referencing expression.

Figure 5 shows some stages in the execution of a string reduction program. At (i) the evaluation of a is required, indicated by an activity at its outermost instruction, the multiplication. The evaluation of an instruction, such as the multiplication, demands the evaluation of its operands, indicated in (ii) by activities at their operators, and then suspends until their evaluation is complete. Where an operand is a reference to a separate definition, such as the references **b** and **c** in (ii), a copy of the definition is taken, replacing the reference, and its evaluation is then demanded (iii). Where an instruction has purely literal operands, as in the first subtraction in (iii), it is executed and replaced by its result so that the result is stored directly as a literal into the instruction using it (iv). When all an instruction's operands have become literals it is re-enabled and executed as shown in (iv) - (vii).

Figure 6 shows some stages in the execution of a graph reduction program. At (i) the evaluation of a is required, indicated by an activity at its operator. The evaluation of an instruction demands the evaluation of instructions referenced by its input arguments, and then suspends. In (ii) such demands for evaluation have thus propagated throughout the program. Each activity at an instruction represents a demand for its result and the dotted arc represents the source of that demand which has to be re-enabled when the demanded instruction has been evaluated. A demanded instruction with purely literal operands, such as **b** in (ii), is executed and replaced by its result so that the instructions, **tl** and **t2**, referencing it then reference the actual values for their operands (iii). Those instructions are re-enabled, their operands loaded, and the instructions replaced with the results, as shown in (iv). Any instructions which are no longer referenced, such as **b** and **c** in (iv) are deleted. In (v) the evaluation of **a** is complete, and all intermediate results in that evaluation have been deleted.

These examples have illustrated concurrent evaluation of reduction programs, the concurrency being achieved by simultaneously demanding both operands of an operator. However reduction programs can just as well be executed without concurrency in which case the second operand is not demanded until the first has been evaluated.

### 2.1.4. Discussion

Each of the various operational models presented in this Section has particular advantages and disadvantages which are largely a result of the particular mechanisms used for organising the flows of data and control through a program[14]. A <u>data mechanism</u> defines how an argument can be accessed by a number of instructions and three such mechanisms can be identified:

- by-literal (in all models) an argument's value is known at compile time and is included in each accessing instruction

- 2 <u>by-value</u> (in data flow and string reduction) an argument is evaluated at run-time when a separate copy of its value is stored in each accessing instruction

- 3 <u>by-reference</u> (in control flow and graph reduction) an argument is evaluated at run-time and its value is shared by each accessing instruction having a reference to it

A <u>control mechanism</u> defines how one instruction causes the execution of other instructions, and again three mechanisms can be identified:

- 1 <u>sequential</u> (in conventional and multi-thread control flow) a thread of control signals an instruction to execute and passes from one instruction to its implicit successor

- 2 parallel (in data flow and parallel control flow) control signals the availability of (control or data) arguments with an instruction being executed when all its arguments are available

The relationship of these mechanisms to the operational models is summarised in Figure 7.

|            |                                          | Data Mechanisms  |                                                        |  |

|------------|------------------------------------------|------------------|--------------------------------------------------------|--|

|            | by-value (& -literal) by-reference (& -1 |                  | by-reference (& -literal)                              |  |

| Control    | sequential                               |                  | conventional control flow<br>multi-thread control flow |  |

| Mechanisms | parallel                                 | data flow        | parallel control flow                                  |  |

| mechanisms | recursive                                | string reduction | graph reduction                                        |  |

|            |                                          |                  | L                                                      |  |

### Figure 7 - Control and Data Mechanisms

All models have the by-literal mechanism in some form since otherwise all constant data would have to be provided as run-time input. Each model also has one or other of the by-value and by-reference data mechanisms. The advantage of by-value compared with by-reference is that the data is directly available in the instruction using it and thus the extra step of loading data from a separate memory is avoided. The corresponding disadvantage is that there is a separate copy of a value (or its definition) for every instruction using it.

Each model has just one of the sequential, parallel and recursive control mechanisms. The sequential and parallel control mechanisms are in a sense opposites in that the former is best suited for programs that are mainly sequential whereas the latter is best suited for programs

3

that are highly concurrent. For sequential execution the "implicit successor" of the sequential control mechanism is more efficient than the explicit propagation of tokens required by the parallel control mechanism. Conversely, using separate instructions, such as FORK and JOIN, for organising concurrency is relatively inefficient when there is concurrency at the level of individual instructions.

The recursive control mechanism is not primarily concerned with concurrent execution. The major benefit of the recursive control mechanism is that instruction execution is only initiated when actually needed thus conserving machine resources and to some extent freeing the programmer from that consideration.

The particular combination of by-reference data mechanism and recursive control mechanism found in graph reduction allows it to support "Lazy Evaluation" [22,23] in which only the minimum necessary computation is actually performed. In both string and graph reduction the recursive control mechanism means that a computation is not performed unless its result is actually needed. In string reduction the by-value data mechanism means that a shared definition is evaluated more than once, as in the multiple evaluation of (-73) in Figure 5 (iii)-(v). In graph reduction however the by-reference data mechanism allows such a shared definition to be evaluated only once, as in Figure 6(ii)-(iii). The operations discussed so far, such as addition, are "strict" which means that the result always depends on the value of all operands. For a program with only strict operations all instructions will always need to be executed and thus there is no real advantage to the recursive control mechanism and lazy evaluation. However these are at an advantage in handling non-strict operations for which one or other of the operands will not be needed in a particular case. The most common example of non-strictness is in conditional instructions, to be discussed in the next Section.

An important difference between control flow, data flow and reduction is the extent to which an instruction interacts with other instructions during its execution. In the case of data flow, an instruction receives all its inputs before it starts executing, processes them completely and then outputs its results. This form of execution is referred to as "atomic" since to the external environment execution appears as a single indivisible operation. In control flow and reduction execution is non-atomic due to memory accesses in the former and acceptance of results demanded from other instructions in the latter.

The non-atomicity in control flow generally has undesirable consequences. For example consider a program which contains the three instructions - **i1: a:=1**, **i2: a:=2**, **i3: a:=a-a** - and has a program design constraint that the content of location **a** should always be non-negative. Each instruction individually preserves that property, but in executing them concurrently there is a possible ordering of the five separate accesses to **a** which would result in **a** having a final value of -1 (the storing of **2** in **a** by **i2** occurring between the two loads from **a** by **i3**). Such undesirable consequences cannot however occur with reduction since changing a location's content only changes the representation of its fixed value, rather than changing its value. Furthermore, non-atomic execution can be beneficial in increasing concurrency and allowing the termination of programs that would not terminate with atomic execution. To illustrate the potential benefits of non-atomic execution consider a logical OR operator in for example C = A OR B. If, say, the value True were received first for B, then the value True could be produced for C before the value for A had been calculated. This would result in additional concurrency between the evaluation of A and those parts of the program which depend on C. Also it might be possible for the program to produce its final result despite non-termination of the evaluation of A. The differences between atomic and non-atomic execution are important not only in individual instructions but also in groupings of instructions as functions and procedures, as will be discussed in the next Section.

### 2.2. Program Organisation

The term program organisation is here being used to cover the way programming requirements are supported by an architecture's machine code. This Section discusses how control flow, data flow and reduction architectures support data structures, conditionals, procedures, iteration, and non-determinacy.

### 2.2.1. Data Structures

Most general-purpose architectures allow the representation and manipulation of data structures. In control flow this is generally achieved by allowing explicit program control over storage allocation and the ability to apply ordinary arithmetic operators to addresses. Components of a structure can be stored in contiguous memory cells with the whole structure represented by a reference to the first component and any other component accessed by for example adding a displacement to that reference. In data flow and reduction architectures however storage allocation is not under explicit program control and special facilities are provided to support data structures.

In a data flow architecture supporting data structures (not all do so) there are special operators for structure manipulation, such as the **append** and **select** operators of Id[24] which respectively extend a data structure with a new component and select a specific component from within a data structure. The result of an **append** operator is a slightly modified copy of the input data structure and this result is communicated as a single (large) data token to those instructions (selects or

- 24 --

further appends) which use it.

A reduction architecture typically provides the CONS, CAR and CDR operators of LISP[25] which respectively form two (simple or structured) values into a two-component structure and select one or other of the components from such a structure. In string and graph reduction architectures data structures are represented in different ways, corresponding to the different ways expression structures are represented. In string reduction a data structure is represented as a string of data items with structure being represented by delimiters, as in for example ((A11, A12), (A21, A22)). An operator such as CDR ("second component") operates on whole data structures -

->> ... (A21, A22) ...

In graph reduction a data structure is represented using references to its components and an operator such as CDR manipulates references -

The by-reference data mechanism of control flow and graph reduction means that a data structure can be efficiently communicated and manipulated using references whereas the by-value data mechanism of data flow and string reduction means that, at least in principle, the whole data structure has to be copied and manipulated. In practice some data flow

- 25 -

architectures use control flow concepts to support data structures with structures being stored in separate memory and references being passed as tokens[26].

A particular benefit of graph reduction is that (in conjunction with lazy evaluation) it can support unbounded data structures. These are data structures for which there is no explicit specification of actual or maximum size. The data structure is defined in terms of a notionally infinite number of components and is incrementally generated as components are actually needed in the computation. Consider for example a data structure **Primes**, defined as a (probably infinite) list of the prime numbers -

### Primes = P(2)

### where $P(x) \equiv CONS(x, P(Next(x)))$ where Next(p) $\equiv (...)$

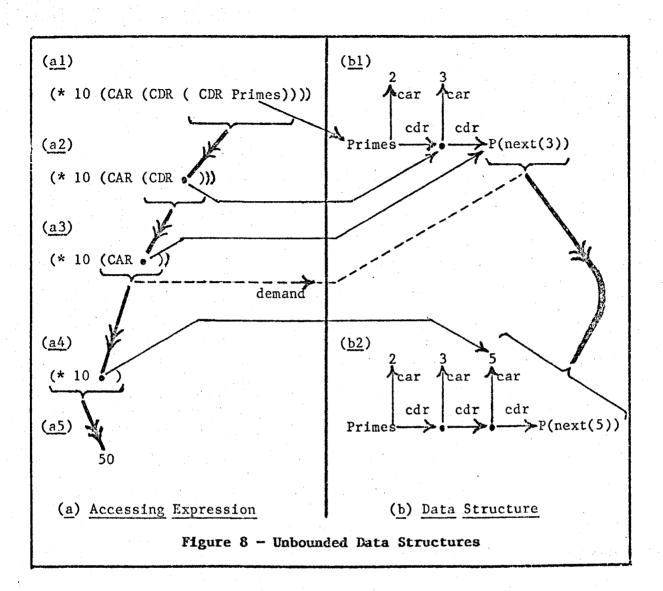

This definition uses a recursive function P (recursive functions will be discussed in more detail later). This function has a prime as its parameter, x, and notionally returns a list of all primes including and following that parameter. This is achieved by CONStructing a list with x as the first component and the remainder of the components being the sub-list returned by the recursive call P (Next (x)). In this call of Pthe Next (x) returns, as the call's parameter, the next prime after x. The list is actually incrementally generated as its components are accessed, as shown in Figure 8. In (b) is shown two stages in the partial generation of the Primes structure, namely that before (b1) and after (b2) the evaluation of an accessing expression shown in (a).

The expression in (al) accesses a particular prime by selecting the appropriate node in the **Primes** structure using **CDR** and **CAR** operators. The initial stages of evaluation ((al) - (a3)) select existing nodes of the structure in (bl) and so do not require any further generation of that structure. From stage (a3), further evaluation of the expression requires the actual value of **CAR( P( Next(3) ) )**. Thus the evaluation of the expression **P ( Next(3) )** is demanded in order for the first component (CAR) of its data structure result to be accessed. As shown in (b2) the execution of that data structure expression will cause it to be replaced by a node for which the car arc points to 5 and the cdr arc points to the next recursive call. The required operand, 5, is now available and is used in the original expression ((a4) - (a5)) without requiring further generation of primes. The same technique could be used in string reduction, but the lack of lazy evaluation would mean that every time a particular prime was needed, all the primes up to that point would have to be re-generated.

#### 2.2.2. Conditionals

Every general-purpose architecture provides some form of conditional instruction to select between alternatives. In a control flow architecture there will be a conditional branch instruction which has two alternative successor instructions. When executed it selects one or other of the alternatives thus, so to speak, switching an incoming flow of control onto one of two output paths.

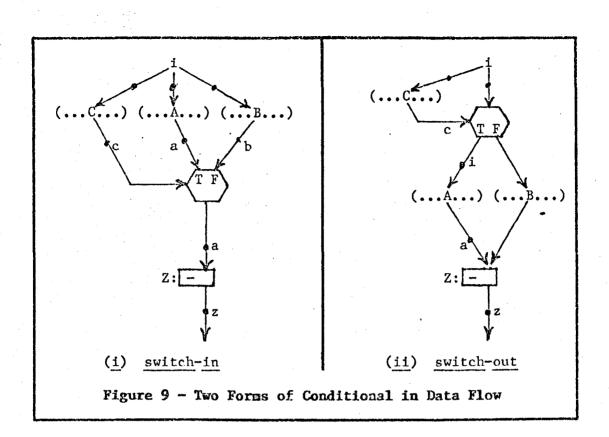

In data flow architectures there are two possible forms of conditionals - one with conditional selection of values to be used and the other with conditional selection of instructions to be executed. Both are shown in in Figure 9 using as an example z = - (if c then a else b) where a, b and c are computed from i by program fragments A, B and C. The first form (value selection) uses an instruction with a conditional operator, referred to as a "switch-in" instruction. This is illustrated in Figure 9(i) with the switch-in represented as a hexagonal node. Like all pure data flow instructions, the switch-in executes when all its inputs (a, b and c) are available. It then outputs for use by Z either the a or the b depending on whether c is True or False.

- 28 -

The second (instruction selection) form of data flow conditional, illustrated in Figure 9(ii), uses a "switch-out" instruction which controls the flow of data through the program. Here the hexagonal node is a switch-out instruction which switches the i input onto one or other of its output arcs, depending on the value of the c input. The instruction causes either **A** or **B** to be activated and thus determines whether **Z** receives **a** or **b**. In (ii), taking c as True, **B** is not executed even though its only input, **i**, is available. This departure from pure data availability is to avoid unnecessary computation and is essential if recursion is to be supported. (If this example were part of a recursion, with c the termination condition and **B** the recursive call, then the pure data availability of (i) would result in non-termination which is avoided in (ii).) In reduction there is a single conditional construct, namely a conditional operator which selects between alternative values and also, due to the recursive control mechanism, selects between alternative instructions. A conditional operator, if, will be part of a conditional instruction such as (if C then A else B). This is executed by first demanding the evaluation of C and then, depending on the result c, demanding the evaluation of either A or B and replacing the whole expression with that result, either a or b.

An important consideration in the organisation of conditionals is the extent to which unnecessary computation may be performed. This can be illustrated by considering the following two alternative conditional structures for computing a value r -

(a) a:= ( ... A ... ); b:= ( ... B ... ); r:= (if cl then a else b) \* (if c2 then a else d);

and -

(b) r:= (if cl then ( ... A ... ) else ( ... B ... )) \* (if c2 then ( ... A ... ) else d);

In both control flow and data flow either of these structures is possible. (In data flow, (a) is conditional value selection as in Figure 9(i) and (b) is conditional instruction selection as in Figure 9(ii).) If cl and c2 are both True then, using structure (a), B would be unnecessarily evaluated, whereas using structure (b) A would be executed twice. Thus for either choice of structure there is the possibility of unnecessary computation being performed. In string reduction the copying of definitions means that B might be executed twice. Craph reduction, using lazy evaluation, is the only model for which unnecessary computation can always be avoided for this type of exemple.

# 2.2.3. Procedures and Iteration

An essential requirement for any general-purpose computer is to allow one program fragment (e.g. procedure) to be executed many times using different sets of data values (e.g. parameters) each time. The term "environment" will be used for the data values and other information which are different for different executions of the same program There are two ways of obtaining such multiple execution in fragment. conventional control flow, namely procedure calls and iterations. (The term procedure will be used to cover both procedures with side effects and functions which return their results.) With (recursive) procedure calls several nested environments for the same procedure will coexist. Consequently there must be mechanisms for keeping the environments separate and allowing a single reference in the shared procedure code to identify data within different environments. This is achieved by using a stack to store environment information (parameters, local variables and return links) and indirect addressing via a register which references the current environment within the stack. In iteration each execution of the repeated code is completely finished before the next exe-Consequently the successive environments can share cution starts. storage and there is no need for any special storage and addressing techniques.

Data flow architectures can also support both procedures and iteration (although not all do so). With procedures (even without recursion) there may be several concurrent executions of the same procedure. The environment for each execution consists of data tokens for the parameters, internal partial results (corresponding to local variables in

- 31 -

control flow) and the return links. Whereas in control flow the byreference data mechanism allows data for each environment to be stored in a separate area of memory accessed via a reference, this is not possible with the by-value data mechanism. Instead a scheme of labelling tokens is used to separate environments. Each active environment has a distinct identifier which is used to label all tokens associated with that environment. An individual instruction in the procedure may execute many times in different environments. Each execution takes a set of input tokens with the same environment identifier and uses that identifier to label its output tokens.

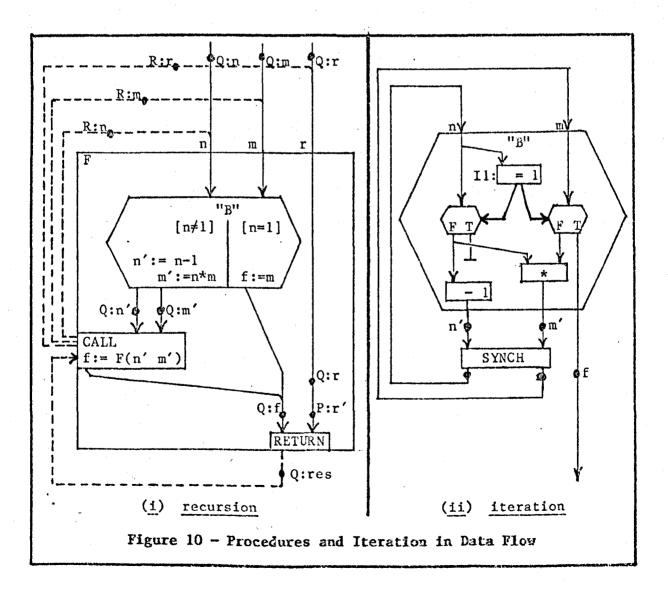

Figure lC(i) shows the operation of this scheme using as an example the procedure F in the following definition for factorial (which is somewhat unusual as it will also be used to illustrate iteration) -

Factorial  $(n) \equiv F(n, 1)$

$F(n, m) \equiv if n=1$  then m else  $F(n-1, n^{4}m)$

The inputs to the procedure graph are the parameters n and m and the return link r. These inputs are tokens labelled with an environment identifier (the Q in e.g. Q:n). The B represents the graph to compute the partial results n' and n' as parameters for the next call. (If the termination condition n=1 holds then B will instead pass m as the final result f to the RETURN instruction – the actual construction of B is shown in (ii).) The tokens output from B are labelled with the same environment identifier, Q, as the input tokens from which they are produced. The CALL instruction allocates an environment identifier R to label a new set of input tokens for the nested procedure call and sends those tokens back to the top of the graph. Eventually the nested call

produces a result token Q:res which becomes the output Q:f of the CALL instruction. The RETURN instruction requires two inputs, f which is the result value and r which indicates the CALL instruction to which the result token is sent and the environment identifier with which it is labelled. There are actually three tokens shown which are available to this instruction, the Q:f and Q:r for this call and the P:r' from some other call (such as an outer level of this recursion). The effect of the labelling scheme is to enable the correct pairing of the tokens available to a particular instruction - in this case Q:f being paired with the Q:r rather than with the P:r' which would have arrived earlier.

Like an individual instruction, a data flow procedure is atomic. All its parameters must be produced before it starts executing and if it has more than one result all of them must be produced before any can be used. This can restrict the potential concurrency in a data flow graph. In this example the evaluation of  $\mathbf{n}'$  does not depend on the value of the second parameter,  $\mathbf{m}$ , and so in principle the procedure could start executing with just its first parameter,  $\mathbf{n}$ , evaluating  $\mathbf{n}'$  concurrently with the evaluation of the second parameter,  $\mathbf{m}$ , by the caller.

There are two general approaches to supporting iteration in data The simpler is that illustrated in Figure 10(ii) for the Facflow. torial example. The body B of the iteration is the same as in the equivalent procedure. Il is a comparison instruction, testing for the termination condition and controlling two switches. If Il gives False then the switches send n and m to the subtraction and multiplication instructions which calculate  $\mathbf{n}'$  and  $\mathbf{m}'$  as the next values for the itera-Alternatively if Il gives True then the switches send m out as tion. the final value f and discard n (indicated by a |). Each iteration completely terminates before the next one starts, this being achieved by a synchroniser instruction (SYNCH) which requires both n' and m' as inputs but performs no computation on them, just passing them back for the next iteration. If the synchronisation were omitted then the subtraction instruction might generate successive values of n faster than the multiplication instruction could consume them and without additional mechanisms there is no way to pair the m with the correct n.

In the alternative scheme for supporting iteration the synchronisation is omitted and there is some additional mechanism to order the

- 34 -

tokens on an arc. In Irvine Dataflow[24] this ordering is achieved by labelling every token with a sequence number (similar to the environment identifier used for procedures). This is incremented at the end of each iteration. In the DDM1 data flow architecture[27] the ordering is obtained by associating a first-in-first-out queue or "stream" of tokens with each input of an instruction.

Whereas in control flow and data flow the basic operational models have to be extended to accommodate procedures this is not the case for reduction, which is based on function applications (corresponding to procedure calls). Figure 11 shows a string reduction sequence for calculating the factorial of **3** using the same definition for **F** as above.

|                 | $F(n,m) \equiv if n=1$ then m else $F(n-1,n*m)$                                     |

|-----------------|-------------------------------------------------------------------------------------|

| ( <u>1</u> )    | $\dots$ F(3,1) $\dots$                                                              |

| ( <u>ii</u> )   | (if 3=1 then 1 else F(3-1, 3*1) )                                                   |

| ( <u>111</u> )  | •••• F(3-1,3*1) •••                                                                 |

| ( <u>iv</u> )   | (if (3-1)=1 then 3*1 else F((3-1)-1,(3-1)*(3*1)) )                                  |

| ( <u>v</u> )    | F((3-1)-1,(3-1)*(3*1))                                                              |

| ( <u>vi</u> )   | (if ((3-1)-1)=1 then (3-1)*(3*1)<br>else F( ((3-1)-1)-1 , ((3-1)-1)*((3-1)*(3*1)) ) |

| ( <u>vii</u> )  | ((3-1)*(3*1))                                                                       |

| ( <u>viii</u> ) | ) 2*3                                                                               |

| ( <u>ix</u> )   | 6                                                                                   |

Figure 11 - Procedures in String Reduction

The initial call in (1) is the instruction F(3,1) which is as usual executed by replacing the reference F by a copy of the referenced definition, and in doing so formal parameters are replaced by actual parameters giving (ii). The conditional is evaluated and replaced by the selected alternative (iii) which is another call with different parameters giving (iv). This process continues until the final result is produced in (ix).

Any iteration can easily be transformed into an equivalent recursive procedure. Thus it is not necessary to support a separate iteration mechanism in addition to that for recursion, and reduction does not do so. In control flow and data flow, iteration is where possible used in preference to an equivalent recursion in order to avoid passing the final result back up through all the levels of recursion (compare Figure 10(i) and 10(ii)). However with the reduction model this advantage is automatically obtained in the execution of those procedures (known as "tail recursive") which are directly equivalent to iteration. This is illustrated in Figure 11 where the result (ix) calculated when the recursion terminates (vii) has been returned directly to that part of the program from which the original call was made in (i).

An important aspect of the reduction model is its ability to support "higher order functions" (procedures), that is procedures which have procedures rather than data values as parameters and/or results. This is illustrated in Figure 12 for a higher order procedure **Bindl(g)** which has procedures as its parameter and result. In (v) there is a call of **Bindl** for which the parameter is a two-parameter procedure **G** (just the addition operator), and the result is the one-parameter procedure **H**. In the definition of **Bindl** (iv) **H** is obtained by binding the first parameter of **G** to a particular value (**Pl**), leaving **G**'s second - 37 -

parameter free as H's only parameter. When procedure H is called in (vi) with parameter P2 the effect (viii) is as though procedure G had been called with parameters P1 and P2.

> $P1 \equiv 10$ (i)(ii)  $P2 \equiv 20$  $(\underline{iii}) G(p1,p2) \equiv (+)$ (iv)  $Bindl(g) \equiv (g (P1))$  $H(p2) \equiv Bindl(G)$ (v) (H (P2)) (vi) ->> ((Bind1(G)) (P2)) (<u>vii</u>) ->> ((G (P1)) (P2)) (viii) ->> (((+) (P1)) (P2)) ->> ( +10 (P2)) (<u>ix</u>) (x) ->> 30 (xi) Figure 12 - Higher Order Procedures in Reduction

The "trick" to this technique is that all procedures and operators have at most one argument. Thus the expression (P1) + (P2) must be represented, as shown in (ix), as (((+) (P1)) (P2)). The operator + has one argument, P1 with value 10, and returns as its result (x) the operator +10. This operator has one argument, P2 with value 20 and adds 10 to that argument to produce the result 30 (xi).

The significance of higher order procedures lies in their ability to encapsulate a general pattern of program execution in a procedure (function) definition which need only be programmed once. This is illustrated in the example below where a procedure **Incgen** is used to encapsulate the general pattern of incremental data structure generation used in Figure 8.

Incgen ( generator, initialvalue ) =

CONS ( initialvalue, Incgen ( generator, generator ( initialvalue )))

P ( init ) = Incgen ( Next, init )

Next ( val ) = (....)

Primes = P ( 2 )

2.2.4. Non-Determinacy

Any concurrent program is non-deterministic at least in the (operational) sense that the exact order of events in its execution is not pre-determined. I will use the term "non-determinate" in the more limited (functional) sense of the final output of a program (or part of a program) being not uniquely defined by just the program and the inputs it is processing. Although non-determinacy is usually an undesirable characteristic of a program there are situations in which the use of a non-determinate program is necessary. The most common example is in the management of access to shared resources, such as files, within a multi-processing operating system. To ensure the integrity of the shared resource the non-determinacy must be controlled, typically by grouping a number of related individual accesses by one process into one "transaction" for which the process has exclusive use of the resource.

To support non-determinate programming some primitive mechanisms for allowing and controlling non-determinacy must be provided. In concurrent control flow non-determinacy is implicit in the basic opera-

- 38 -

tional model where two concurrent instruction executions can simultaneously update the same memory cell with different values. There is usually some additional explicit mechanism, such as a "test and set" instruction, for controlling that non-determinacy.

In the data flow model there is a similar potential for implicit non-determinacy in that two instruction executions could emit tokens with different values for the same input of another instruction, with the result of the program depending on which arrived first. However the data flow code generated by a compiler is always constructed so as to avoid such implicit non-determinacy. For example in Figure 10(ii) the synchroniser instruction is included to prevent non-determinacy in the execution of the multiply instruction; in Figure 9(ii) the switch-out instruction ensures that only one of **A** and **B** sends a token to the single input of **Z**, even though both could do so.

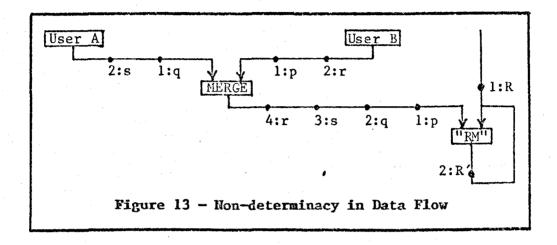

There is only one data flow architecture[24] which provides expli-This architecture uses the technique of a cit non-determinacy. "resource manager" to control non-determinate access to a sharable resource, as shown in Figure 13. The resource manager RM is a form of procedure which has two inputs, the resource R (e.g. a file) and a complete transaction (p, q, r or s) to be processed. The result of one call is a modified version of the resource, R', which is fed back as input to the next call. The arcs carry sequences or "streams" of tokens and each token is labelled with a "stream number", 1, 2, 3 etc. These numbers serve the same role as the environment identifiers in the procedure call example, ensuring that the resource manager itself is determinate. The non-determinacy and its control are combined in the explicit MERCE operator which merges its two input streams into one output stream. On each execution it takes a token from either input, ignoring the input stream numbers, and outputs it labelled with the next output stream number.

In reduction the only form of update is to replace an expression with the result of evaluating it. This cannot lead to non-determinacy, as can the less constrained form of update found in control flow. If non-determinacy is required it must be introduced with some special operator. Non-determinate operators that have been proposed are the "AMBiguity operator" [28], and more recently FRONS [29]. An example of an expression using AMB is

# $\mathbf{r} \equiv ((A) AMB (B))$

The result of the whole expression is the result of evaluating one or other of its operands, (A) or (B). Operationally, demanding the value of r causes both (A) and (B) to be demanded and computed concurrently. When one computation, say (A), has terminated its result a replaces the whole definition. The other computation is then no longer needed and thus forcibly terminated. AMB can be used to program a merge procedure which then forms the basis for resource management in the same style as in Figure 13. Although necessary for resource management, the inclusion of non-determinacy destroys some of the desirable properties of determinate reduction programs, such as referential transparency. For example the definition  $\mathbf{x} \equiv \mathbf{r} - \mathbf{r}$  would give  $\mathbf{x}$  the value zero for any value of  $\mathbf{r}$ , but replacing the reference  $\mathbf{r}$  by the defining expression above gives

$\mathbf{x} \equiv ((A) \text{ AMB} (B)) - ((A) \text{ AMB} (B))$

In this expression the two distinct AMB operators may give different , results and thus a non-zero x.

There are uses for non-determinacy other than in the resource manager type of application. An example is when there are two algorithms (A) and (B) for computing a value r and one or other may be very inefficient or fail to terminate for particular cases which are difficult or impossible to predict. The expression  $r \equiv ((A) \land MB (B))$  will always terminate with a result for r if either algorithm terminates. Furthermore (assuming machine resources are divided fairly between  $(\Lambda)$ and (B)) its execution time in a particular case will be proportional to that for the more efficient of the two algorithms for that particular case. In this example concurrency in evaluation of r's operands is essential to the logic of the program. (The use of concurrency in this way is explored at some length in [30].) However for other examples of potential concurrency, such as in  $r \equiv ((A) * (B))$ , the logic of the program is not dependent on there being actual concurrent execution. For reduction architectures which do not support operators such as AMB the exploitation of potential concurrency is entirely an implementation issue. As discussed in the next Section, some reduction implementations do exploit concurrency and some do not.

# 2.3. Machine Organisation and Implementations

The term machine organisation is being used to cover the way a machine's resources are configured and allocated. This Section starts by identifying the different classes of machine organisations used for control flow, data flow and reduction, and then outlines some particular implementations.

### 2.3.1. Classification

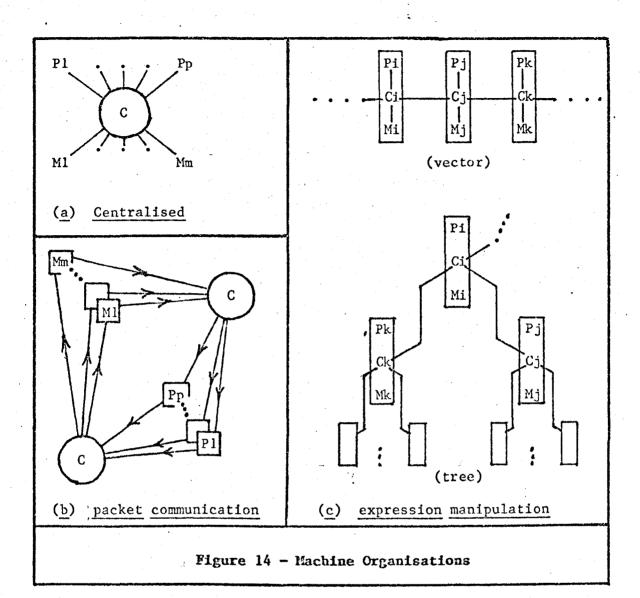

Three classes of machine organisation can be identified which are referred to here as the centralised, packet communication, and expression manipulation organisations. These organisations, illustrated in Figure 14, are principally distinguished by the organisation of communication(C) between processor(P) and memory(M) resources.

<u>Centralised</u> - This organisation consists of one or several processors and one or several memory units with a central communication system providing each processor with direct access to all memory. In this organisation a program (or part of a program) being executed by one processor has one active instruction, the execution of which typically requires several communications with the global memory.

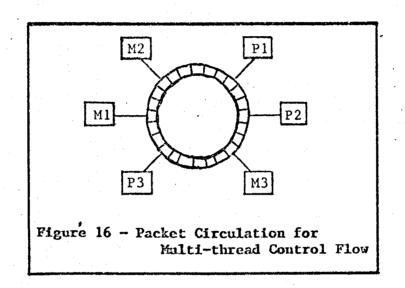

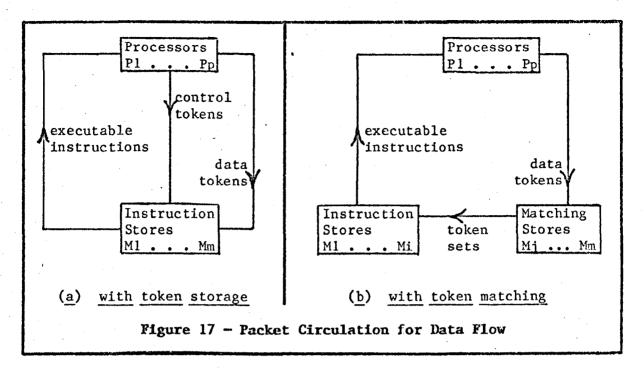

<u>Packet Communication</u> - This organisation consists of a circular instruction execution pipeline of separate resources in which processors and memories are interspersed with "pools of work" through which they communicate. Parallelism can be obtained by having a number of identical resources between successive pools as shown; or by replicating and connecting the circular pipelines. In this organisation an executing

program consists of a large number of independent self-contained items or work packets (e.g. individual instructions and tokens) which split and merge and move into different work pools for different stages of processing. The operation cycle for a resource is to take a packet from an input pool, process it in isolation from other resources, and produce a modified packet in an output pool.

<u>Expression Manipulation</u> - This organisation consists of a large number of resources, referred to as "computing elements", each being a complete microcomputer with local processor and memory and a capability for communicating with a small number of other computing elements. The communications capabilities are used to connect the computing elements into some regular structure such as a vector or tree. In this organisation an executing program consists of one large program structure ("expression") with logically related parts of the program being allocated to physically related computing elements. Some components of this structure are active whilst some are inactive. Each computing element examines its part of the overall program structure looking for active items to execute. Executing an item will involve communications with the other items that it references. Programs generally exhibit considerable "locality of reference" which means that references tend to be between items closely related in the logical structure. Consequently most communications are internal to one computing element or between close neighbours.

A major motivation for the novel packet communication and expression manipulation organisations is to alleviate the communication problems that arise in a centralised organisation as the number of processors increases. In a centralised organisation the performance of a processor is dependent on the transit time of a memory access through the global communication system (including in "transit time" any queueing for access to the communications system). In the packet communication organisation however (provided there is sufficient concurrency) performance is not dependent on the transit time of a packet through the communication system but only on the total communication bandwidth being sufficient to match the total throughput of the processors. Whereas the transit delay must eventually increase as system size and load increases, there are communication systems organisations[31] where the

bandwidth per processor remains substantially constant as the system is extended to accommodate more processors and memories. In the expression manipulation organisation locality of reference is relied on to overcome the global communication problem.

Modern computer designs often incorporate adaptations to their basically centralised (single-processor) machine organisation which to an extent overcome the similar processor-memory communication problems that arise from increasing processor power. These adaptations are the pipelining of instruction execution, producing a similar effect to that of a packet communication organisation, and the introduction of memory caches, to exploit locality as in an expression manipulation organisation. The approach of pipelining conventional architectures (introducing some parallelism) is restricted however by the limited number of pipeline stages that can be introduced and the need to support a strictly sequential operational model. A multi-processor machine organisation incorporating a local cache with each processor would in effect be a form of expression manipulation organisation.

Most of the machine organisations described above are at least being investigated for the implementation of each different class of architecture, as shown in Figure 15. The rest of this Section discusses some of these proposed implementations.

- 46 -

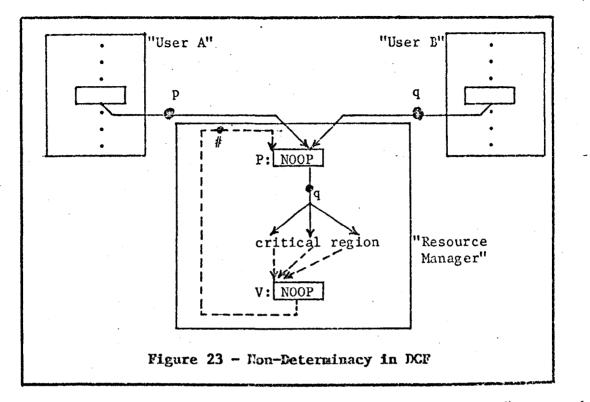

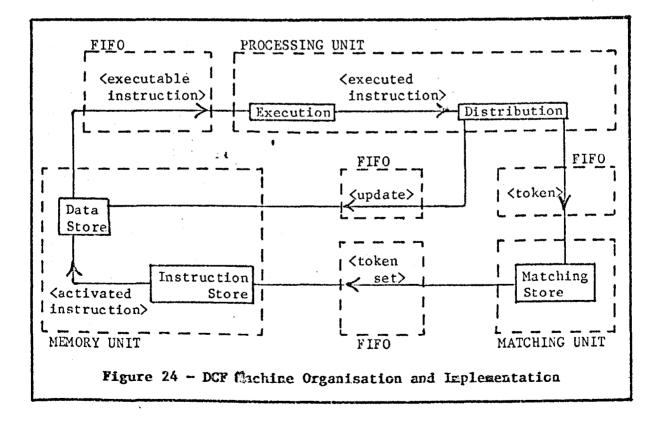

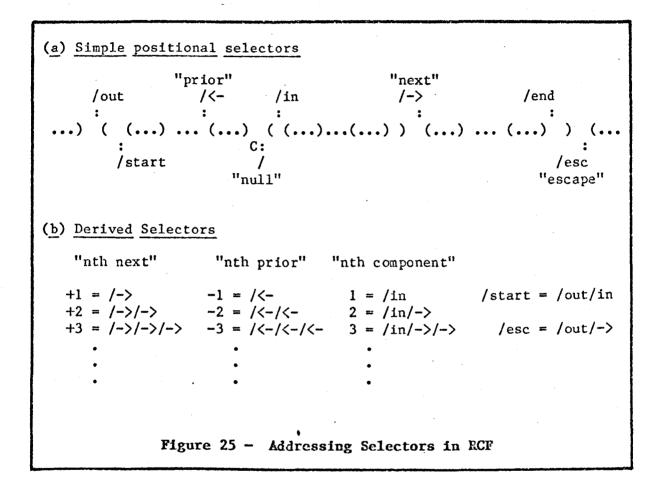

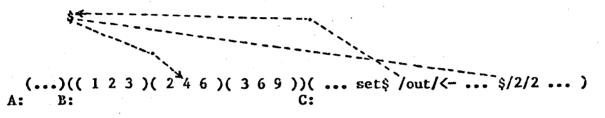

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | concurrent<br>control<br>flow | data<br>flow | reduct<br>string | tion<br>graph |  |  |