# Reconfigurable Time Interval Measurement Circuit Incorporating a Programmable Gain Time Difference Amplifier

A Thesis Submitted for the Degree of Doctor of Philosophy in the Faculty of Engineering

By

Ahmed N. Alahmadi

School of Electrical and Electronic Engineering

Newcastle University

Newcastle upon Tyne

United Kingdom

October-2012

#### Abstract

As further advances are made in semiconductor manufacturing technology the performance of circuits is continuously increasing. Unfortunately, as the technology node descends deeper into the nanometre region, achieving the potential performance gain is becoming more of a challenge; due not only to the effects of process variation but also to the reduced timing margins between signals within the circuit creating timing problems. Production Standard Automatic Test Equipment (ATE) is incapable of performing internal timing measurements due, first to the lack of accessibility and second to the overall timing accuracy of the tester which is grossly inadequate. To address these issue 'on-chip' time measurement circuits have been developed in a similar way that built in self-test (BIST) evolved for 'on-chip' logic testing.

This thesis describes the design and analysis of three time amplifier circuits. The analysis undertaken considers the operational aspects related to gain and input dynamic range, together with the robustness of the circuits to the effects of process, voltage and temperature (PVT) variations. The design which had the best overall performance was subsequently compared to a benchmark design, which used the 'buffer delay offset' technique for time amplification, and showed a marked 6.5 times improvement on the dynamic range extending this from 40 ps to 300ps. The new design was also more robust to the effects of PVT variations.

The new time amplifier design was further developed to include an adjustable gain capability which could be varied in steps of approximately 7.5 from 4 to 117. The time amplifier was then connected to a 32-stage tapped delay line to create a reconfigurable time measurement circuit with an adjustable resolution range from 15 down to 0.5 ps and a dynamic range from 480 down to 16 ps depending upon the gain setting. The overall footprint of the measurement circuit, together with its calibration module occupies an area of 0.026 mm<sup>2</sup>

The final circuit, overall, satisfied the main design criteria for 'on-chip' time measurement circuitry, namely, it has a wide dynamic range, high resolution, robust to the effects of PVT and has a small area overhead.

#### Acknowledgements

It is a great pleasure to express my greatest gratitude to the people who have helped and supported me throughout my PhD. I owe sincere and earnest thankfulness to Dr. Gordon Russell for his continuous support for this research, without him this work could not have been completed. Special thank of mine goes to Prof. Alex Yakovlev who supported and shared his personal experience with me.

A special thank to my friends in Newcastle for their encouragement and for all the wonderful times they shared with me.

I am truly indebted and thankful to my loving parents, wife and each member of my family for their unlimited love and support. Finally, I would like to show my gratitude for the financial support of Umm Al-Qura University.

## **Table of Contents**

| Abstract                                                           | ii       |

|--------------------------------------------------------------------|----------|

| Acknowledgements                                                   | iii      |

| Table of Figures                                                   |          |

| Table of Tables                                                    | xi       |

| Chapter 1 Introduction                                             | 12       |

| 1.1 Background                                                     | 12       |

| 1.2 Process Variation and Manufacturing Defects                    | 13       |

| 1.2.1 Causes of Delay Faults                                       | 14       |

| 1.3 Timing Anomalies                                               | 17       |

| 1.4 On Chip Time Measurement                                       | 19       |

| 1.5 Research Contribution                                          |          |

| 1.6 Thesis Roadmap                                                 | 22       |

| 1.7 References                                                     | 24       |

| Chapter 2 Time Measurement Techniques                              | 27       |

| 2.1 Introduction                                                   | 27       |

| 2.2 Counter Based Method [10, 11]                                  | 28       |

| 2.3 Time to Voltage Conversion Technique [12-15]                   | 29       |

| 2.4 Signal Conditioning                                            |          |

| 2.4.1 Pulse Stretching [10, 16]                                    |          |

| 2.4.2 Time Difference Amplifier                                    |          |

| 2.5 Delay Lines                                                    |          |

| 2.5.1 Fixed Delay Line [22]                                        |          |

| 2.5.2 Adjustable Delay Line                                        |          |

| 2.5.3 Pulse Shrinking Technique                                    |          |

| 2.6 Vernier Method                                                 |          |

| 2.6.1 Vernier Delay Line (VDL) [3-5, 21]                           |          |

| 2.6.2 Vernier Oscillator (VO) [6, 10]                              |          |

| 2.7 The Combination of Coarse and Fine Delay Method [8]            |          |

| 2.7.1 The Combination of Coarse and Fine Delay Line [8]            |          |

| 2.7.2 The Combination of Coarse and Fine VO [7]                    |          |

| 2.8 Implementation of Time Measurement Circuitry Using FP          |          |

| 2.8.1 Process Variation Based TDC [36]                             |          |

| 2.9 Summary                                                        |          |

| 2.10 References                                                    |          |

|                                                                    |          |

| Chapter 3 Time difference amplifier design with improved performan |          |

| parameters                                                         |          |

| 3.2 Analysis of the Time Difference Amplifier                      |          |

| 3.2.1 Buffer Delay Offset Design                                   |          |

| 3.3 Unbalanced Active Capacitive Load Design                       | 65<br>67 |

| 3.4 Unbalanced Active Charge Pump Load Design                      |          |

| 3.5 NAND Gate with Additional Resistance Technique                 |          |

| 3.6 Programmable Time Amplifier                                    |          |

|                                                                    |          |

| 3.7 Summary and Conclusions                               | 84  |

|-----------------------------------------------------------|-----|

| 3.8 References                                            | 85  |

|                                                           |     |

| Chapter 4 A Comparison of the Time Amplifier Circuits     |     |

| 4.1 Introduction                                          |     |

| 4.2 Worst Case-corner and Monte Carlo Analysis Techniques |     |

| 4.3 Time Amplifier Process Variation Analysis             |     |

| 4.3.1 Gain Variation Analysis                             |     |

| 4.3.2 The Linearity and Gain Variation Analysis           |     |

| 4.4 Time Amplifier Temperature Variation Analysis         |     |

| 4.5 Time Amplifier Power Supply Variation Analysis        |     |

| 4.6 Conclusion                                            |     |

| 4.7 References                                            | 111 |

| Chapter 5 Reconfigurable Time Measurement Circuit         | 112 |

| 5.1 Introduction                                          | 112 |

| 5.2 Reconfigurable TIM Circuit Overview                   | 113 |

| 5.2.1 Reconfigurable TIM Circuit                          |     |

| 5.2.2 Calibration Circuit                                 | 120 |

| 5.2.3 Calibration Process                                 | 135 |

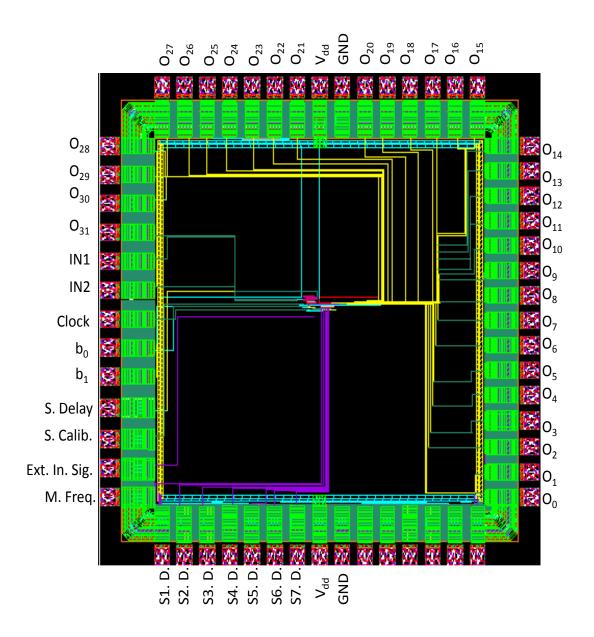

| 5.3 Design of Chip Layout                                 | 140 |

| 5.4 Conclusion                                            | 144 |

| 5.5 References                                            | 146 |

| Chapter 6 Conclusions and Future Work                     | 148 |

| 6.1 Introduction                                          |     |

| 6.2 Summary of the Thesis                                 |     |

| 6.2.1 Time Amplifier                                      |     |

| 6.2.2 Time Amplifier and Process Variation Effects        | 150 |

| 6.2.3 The Reconfigurable TIM                              | 151 |

| 6.3 Conclusion                                            | 152 |

| 6.4 Future Work:                                          | 154 |

| 6.5 References                                            | 157 |

| Appendix A                                                | 158 |

| Annendix R                                                | 161 |

# **Table of Figures**

| Figure 1.1: Common interconnect defects (a) shorting of metal lines owin unexposed photoresist (b) metallization defect causing a short between the lines (c) shorts and breaks of metal lines due to a scratch in the photores (d) shorting among several metal lines as a result of a solid-state particle the metal mask (e) Inter-layer short between two interconnects (f) short among several metal lines due to a metallization defect [13] | wo<br>ist<br>e on |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Figure 1.2: Gate-Oxide-Short (short between polysilicon gate and underly silicon surface).                                                                                                                                                                                                                                                                                                                                                         | -                 |

| Figure 1.3: Cross-talk causing (a) a pulse, (b) cross-talk speed-up and (c) cross-talk slow-down.                                                                                                                                                                                                                                                                                                                                                  |                   |

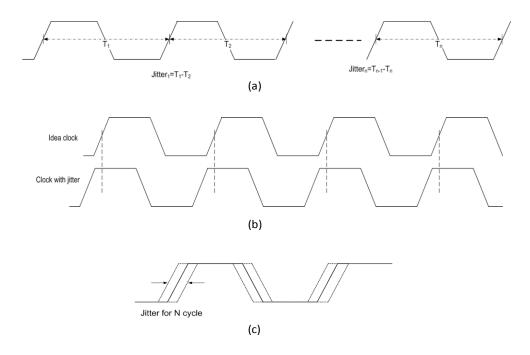

| Figure 1.4 (a) Cycle to cycle jitter, (b) Period jitter, and (c) Long-term jitt                                                                                                                                                                                                                                                                                                                                                                    |                   |

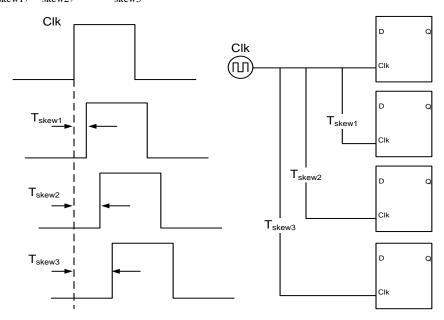

| Figure 1.5: Clock skew signals                                                                                                                                                                                                                                                                                                                                                                                                                     | 18                |

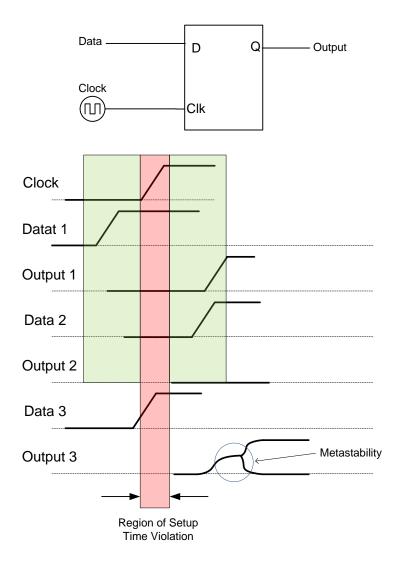

| Figure 1.6: The responses of the flip-flop output to the different temporal relationships between data and clock signal                                                                                                                                                                                                                                                                                                                            |                   |

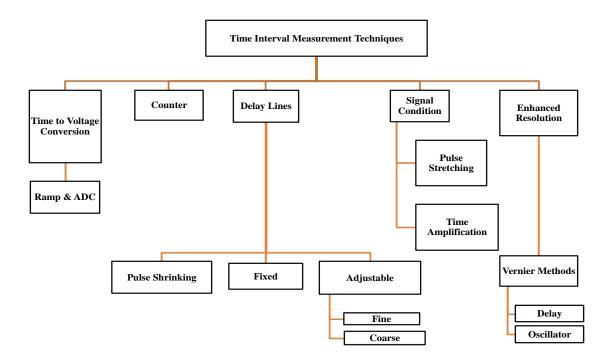

| Figure 2.1: Taxonomy of time interval measurement techniques [9]                                                                                                                                                                                                                                                                                                                                                                                   | 27                |

| Figure 2.2: Time interval measurement using counter technique                                                                                                                                                                                                                                                                                                                                                                                      | 29                |

| Figure 2.3: Time to voltage converter circuit [14]                                                                                                                                                                                                                                                                                                                                                                                                 | 30                |

| Figure 2.4: The generated pulse width equal to the time difference betwee start and stop signal.                                                                                                                                                                                                                                                                                                                                                   |                   |

| Figure 2.5: Pulse stretching circuit [10].                                                                                                                                                                                                                                                                                                                                                                                                         | 32                |

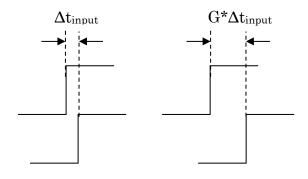

| Figure 2.6: The concept of time amplifier                                                                                                                                                                                                                                                                                                                                                                                                          | 32                |

| Figure 2.7: Time difference amplifier using analog circuit [20]                                                                                                                                                                                                                                                                                                                                                                                    | 33                |

| Figure 2.8: Time difference amplifier circuit [17]                                                                                                                                                                                                                                                                                                                                                                                                 | 34                |

| Figure 2.9: MUTEX circuit                                                                                                                                                                                                                                                                                                                                                                                                                          | 34                |

| Figure 2.10: time difference amplifier characteristicsError! Bookmot defined.                                                                                                                                                                                                                                                                                                                                                                      | ark               |

| Figure 2.11: Time difference amplifier, buffer delay offset design [19]                                                                                                                                                                                                                                                                                                                                                                            | 36                |

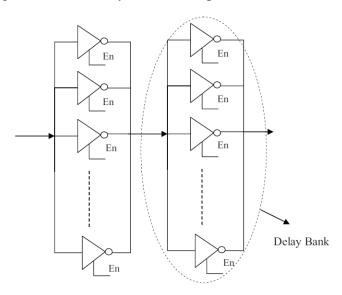

| Figure 2.12: Block diagram of a tapped delay                                                                                                                                                                                                                                                                                                                                                                                                       | 37                |

| Figure 2.13: A simple adjustable coarse delay line [9].                                                                                                                                                                                                                                                                                                                                                                                            | 38                |

| Figure 2.14: Adjustable fine delay line using a bank of parallel NMOS capacitances [9]                                                                                                                                                                                                                                                                                                                                                             | 39                |

| Figure 2.15: 2x16 inverter matrix [9]                                                                                                                                                                                                                                                                                                                                                                                                              | 39                |

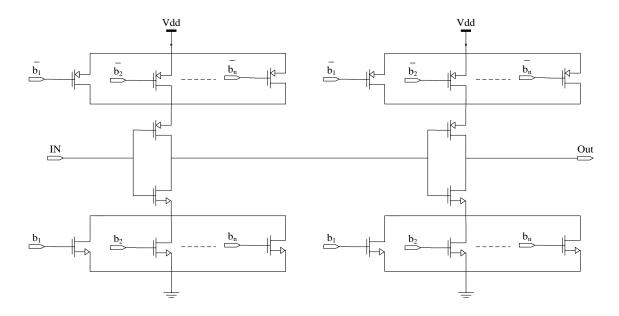

| Figure 2.16: The differential digital-control delay cell [7]                                                                                                                                                                                                                                                                                                                                                                                       | 40                |

| Figure 2.17: Current starved delay elements [27].                                                                                                                                                                                                                                                                                                                                                                                                  | 41                |

| Figure 2.18: TDC pulse shrinking method [31]                                                                                                                                                                                                                                                                                                                                                                                                       | 42                |

| Figure 2.19: Pulse shrinking delay element circuit                                                                                                                                                                                                                                                                                                                                                                                                 | 42                |

| Figure 2.20: All-digital pulse shrinking delay element [2]43                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.21: Block diagram of VDL                                                                                                                                             |

| Figure 2.22: Time measurement using VO [10]45                                                                                                                                 |

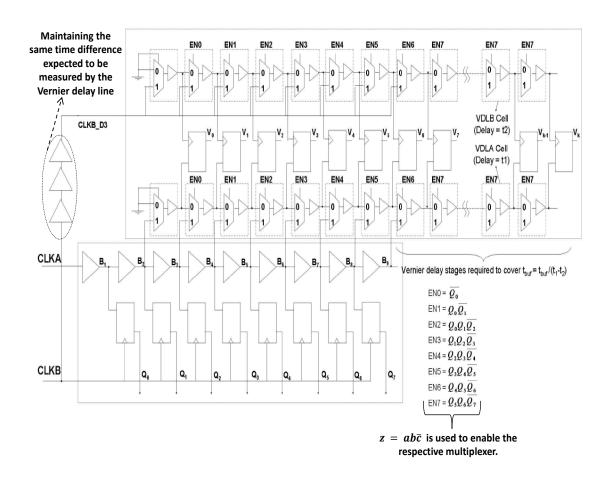

| Figure 2.23: The combination of coarse and fine delay using tapped delay method with vernier delay line [8]47                                                                 |

| Figure 2.24: The combination of coarse and fine delay using VO [7]48                                                                                                          |

| Figure 2.25: Comparison of the measurement speed between Dual resolution VO (DVO) and single resolution VO [7]48                                                              |

| Figure 2.26: Process variation based TDC [36]                                                                                                                                 |

| Figure 2.27: The value of each counter against time51                                                                                                                         |

| Figure 2.28: The value of each counter against time51                                                                                                                         |

| Figure 3.1: MUTEX circuit59                                                                                                                                                   |

| Figure 3.2: The behaviour of the output of the MUTEX circuit during metastability60                                                                                           |

| Figure 3.3: The relationship between the input and the output time differences of the latch circuit in the metastable state60                                                 |

| Figure 3.4: The plot of equations (4) and (5)                                                                                                                                 |

| Figure 3.5: The plot of Equation (6) showing the linearity region around zero                                                                                                 |

| Figure 3.6: Time amplifier, buffer delay offset design [4]64                                                                                                                  |

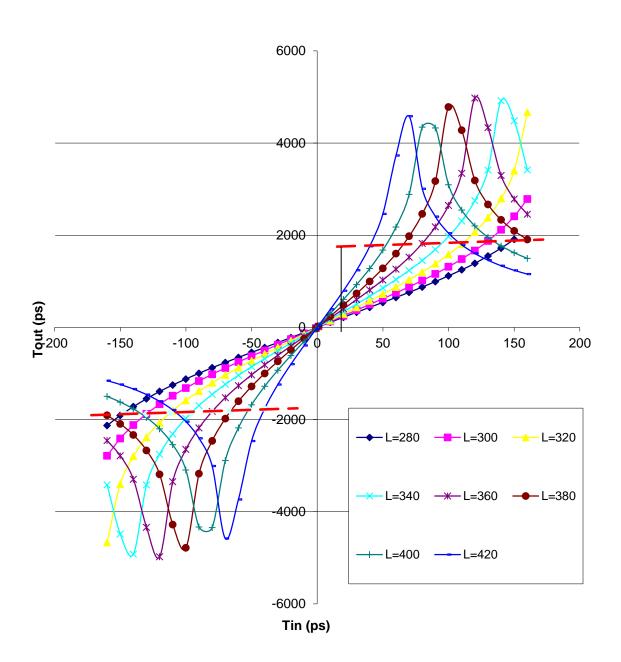

| Figure 3.7: The effect of changing the capacitance value on the gain and the dynamic input range                                                                              |

| Figure 3.8: Upper latch circuit of TDA, buffer delay offset design65                                                                                                          |

| Figure 3.9: (a) The equivalent circuit of the upper latch before the arrival of IN1 and IN2. (b) The equivalent circuit when each capacitance starts discharging              |

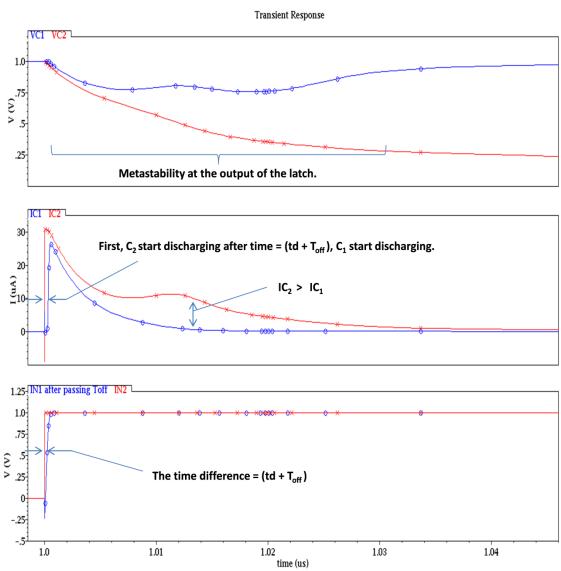

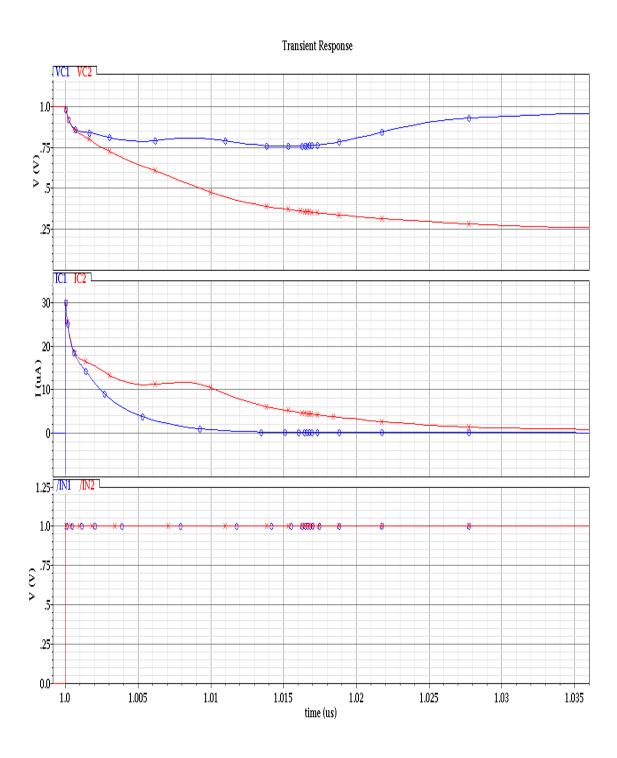

| Figure 3.10: The behaviour of $C_1$ and $C_2$ , and their discharge currents during the arrival of IN1 and IN2, for buffer delay offset design68                              |

| Figure 3.11: Time amplifier characteristics for buffer delay offset design and unbalanced active capacitive load design                                                       |

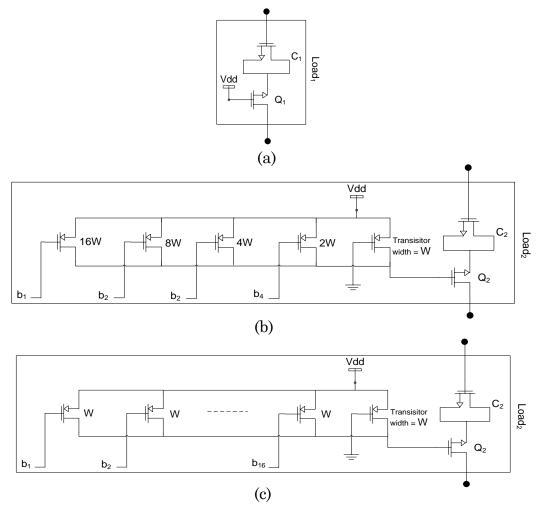

| Figure 3.12: Time amplifier with unbalanced active capacitive loads design.                                                                                                   |

| 69                                                                                                                                                                            |

| Figure 3.13: The behaviour of C <sub>1</sub> and C <sub>2</sub> , and their discharge currents during the arrival of IN1 and IN2, for unbalance active capacitive load design |

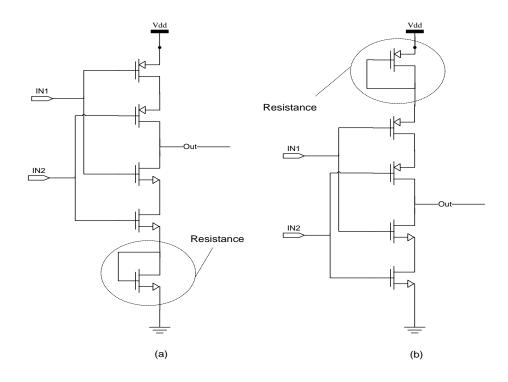

| Figure 3.14: (a) Time amplifier using unbalanced active load design. Unbalanced active charge pump load using (b) $C_1 > C_2$ and (c) $L_{Q1} > L_{Q2}$ 72                    |

| Figure 3.15: The behaviour of $C_1$ and $C_2$ , and their discharge currents during the arrival of IN1 and IN2, for unbalance active charge pump load design.                 |

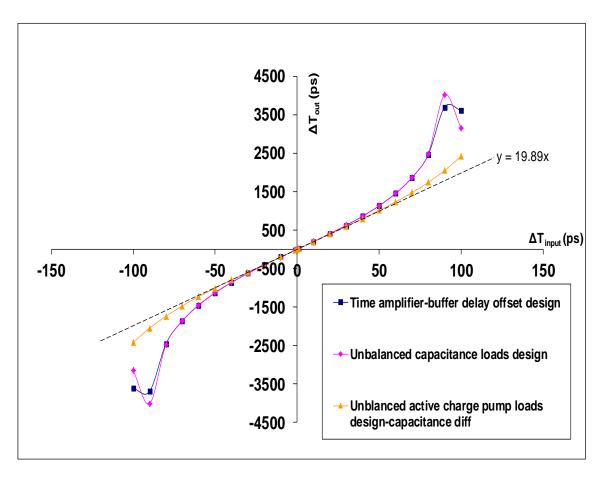

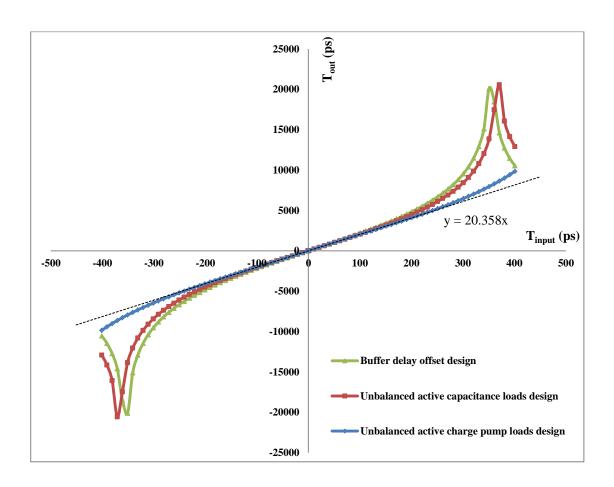

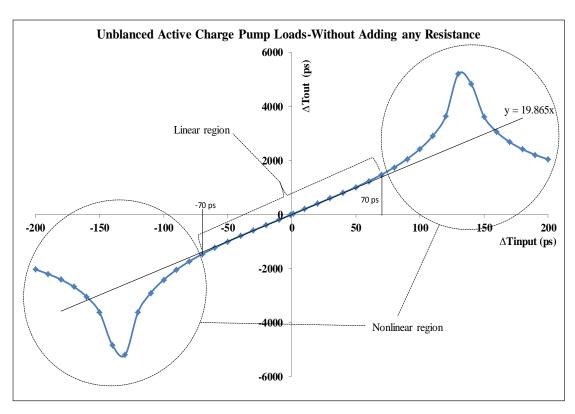

| Figure 3.16: The characteristics for the three time amplifier designs74                                                                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

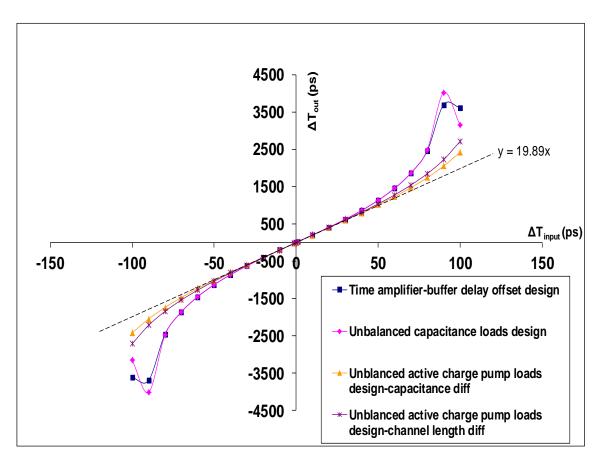

| Figure 3.17: The characteristics for the four time amplifier designs75 $$                                                                                                                                    |

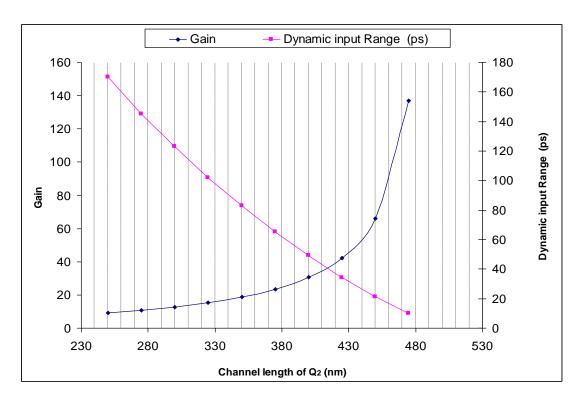

| Figure 3.18: The amplification gain and range of the time amplifier with respect to the change in $L_{Q2},L_{Q1}$ is fixed to $0.5\mu m$                                                                     |

| Figure 3.19: NAND gate with added resistance                                                                                                                                                                 |

| Figure 3.20: The behaviour of $C_1$ and $C_2$ , and their discharge currents during the arrival of IN1 and IN2, for buffer delay offset design using a NAND gate with added resistance in the discharge path |

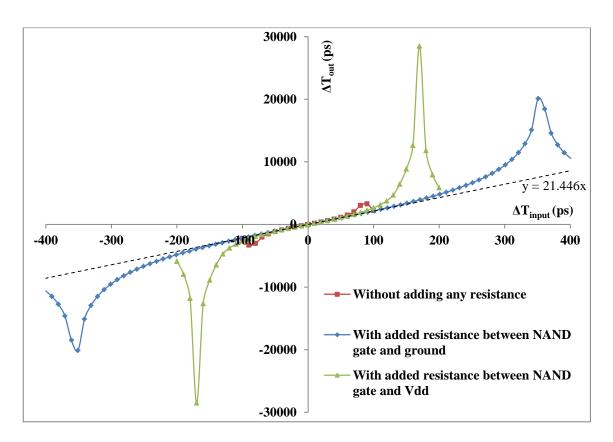

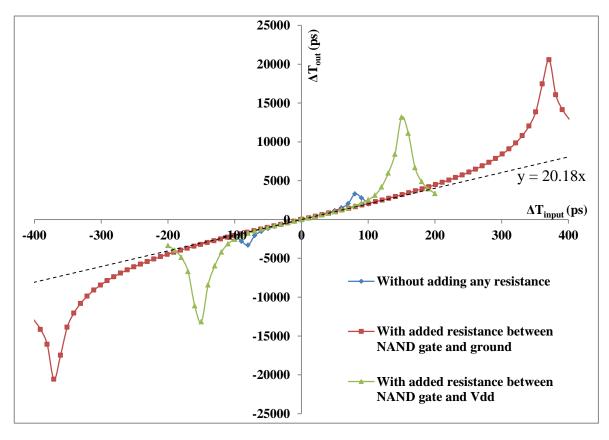

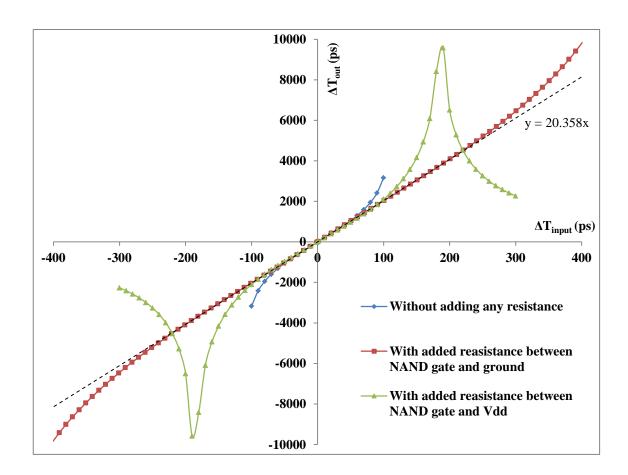

| Figure 3.21: Time amplifier characteristics for the buffer delay offset with and without added resistance                                                                                                    |

| Figure 3.22: Time amplifier characteristics for the unbalanced active capacitive load with and without added resistance                                                                                      |

| Figure 3.23: Time amplifier characteristics for the unbalanced active charge pump load with and without added resistance                                                                                     |

| Figure 3.24: Time amplifier characteristics for three circuit implemented using NAND gate with added resistance                                                                                              |

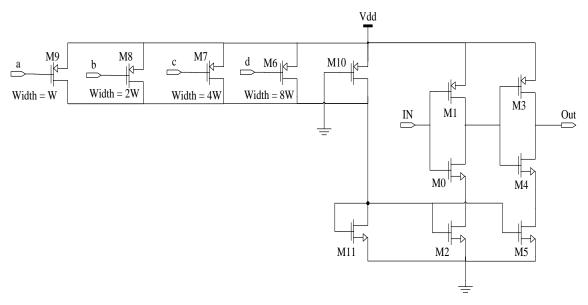

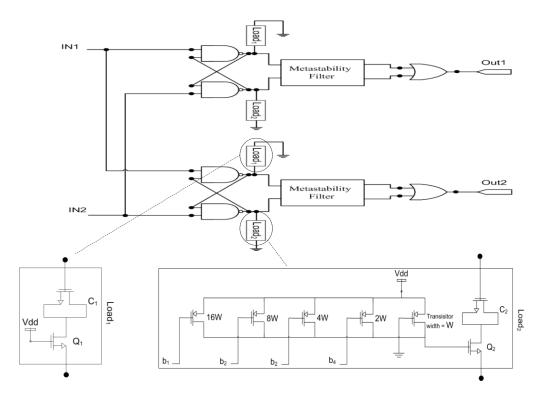

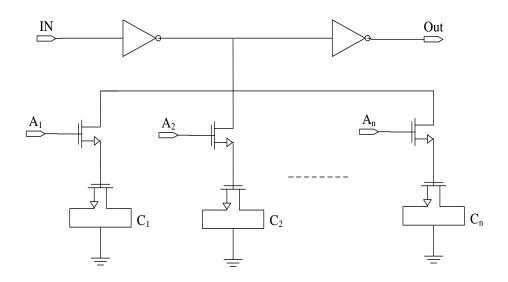

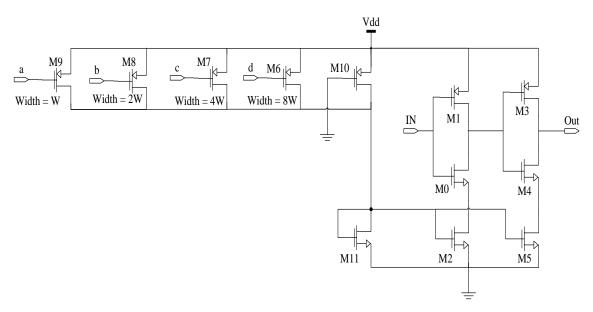

| Figure 3.25: Programmable time amplifier active loads                                                                                                                                                        |

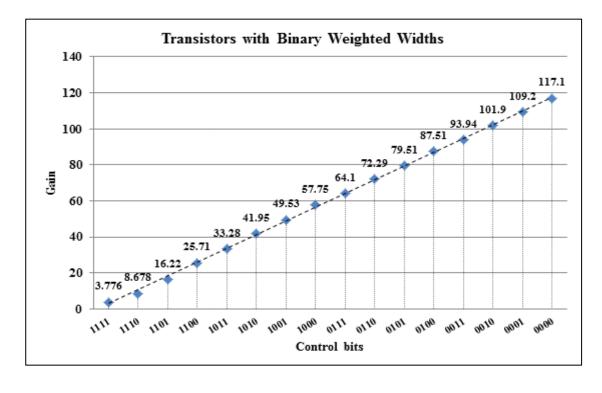

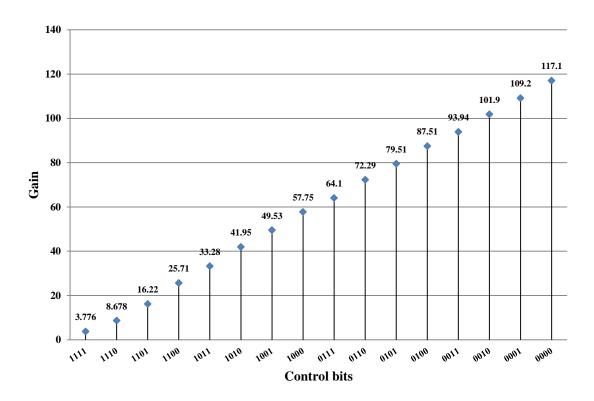

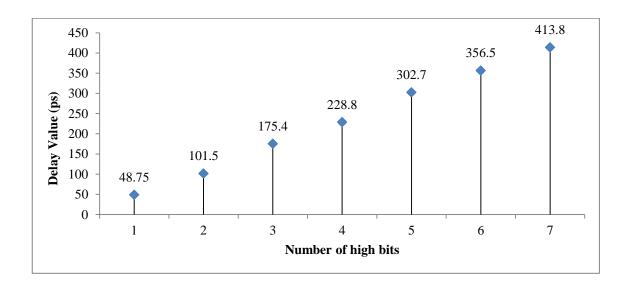

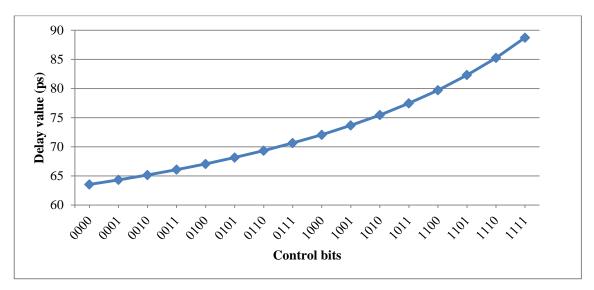

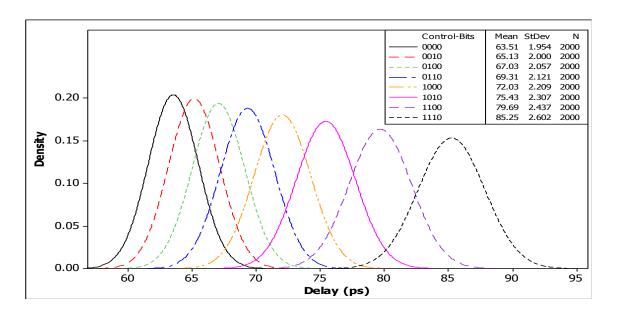

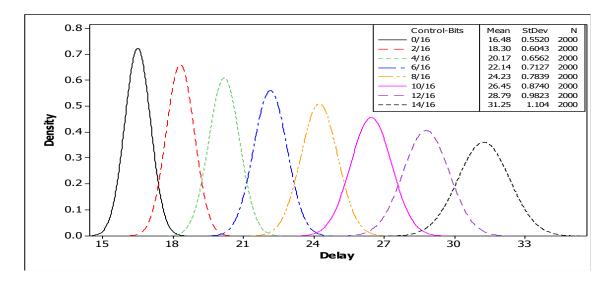

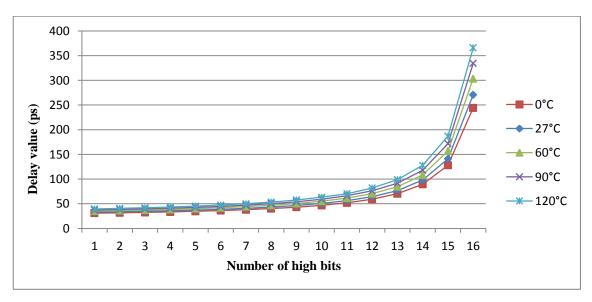

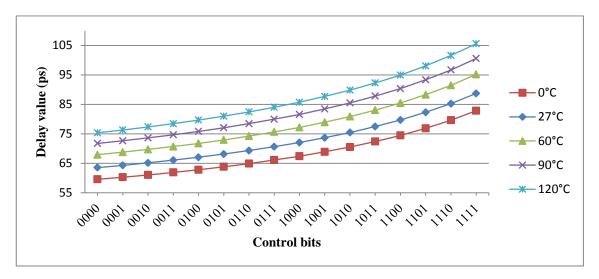

| Figure 3.26: Programmable time amplifier gain versus input bit pattern83 $$                                                                                                                                  |

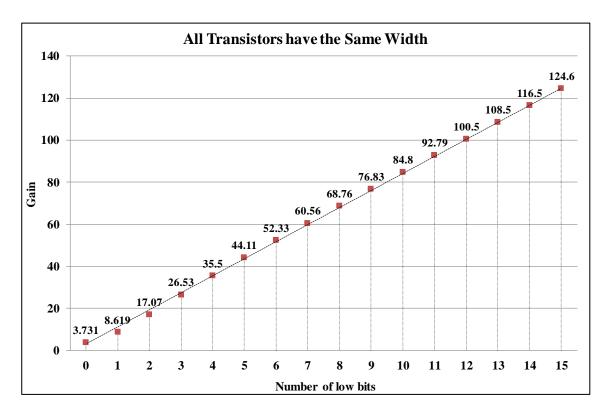

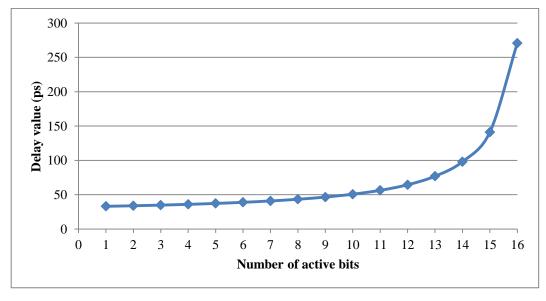

| Figure 3.27: Programmable time amplifier gain versus number of low bits.                                                                                                                                     |

| 84                                                                                                                                                                                                           |

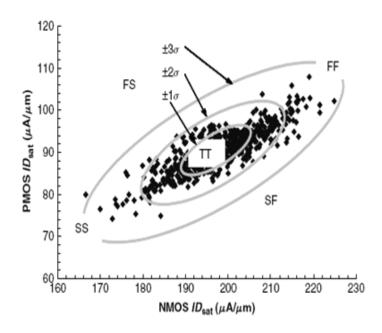

| Figure 4.1: Process variation map for N and P-MOSFET devices [5]87                                                                                                                                           |

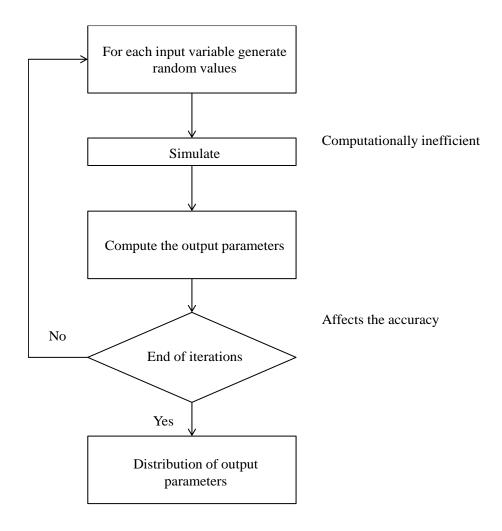

| Figure 4.2: Monte Carlo analysis [6]                                                                                                                                                                         |

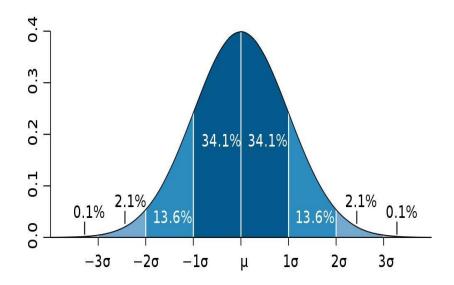

| Figure 4.3: One, two and three σ ranges within the normal distribution graph [7]90                                                                                                                           |

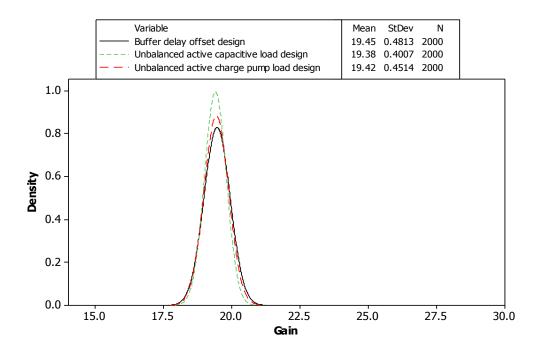

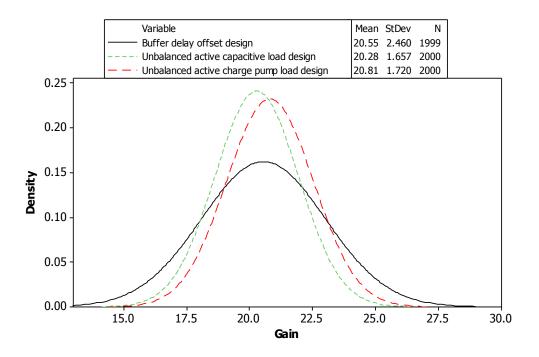

| Figure 4.4: Histogram plots for the gain against process variation for the gain of the three time amplifier circuits                                                                                         |

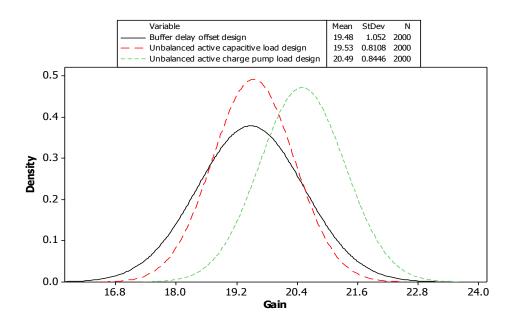

| Figure 4.5: Histogram plots for the gain against process variation for the three time amplifier circuits implemented using the NAND gate with added resistance in the discharge path                         |

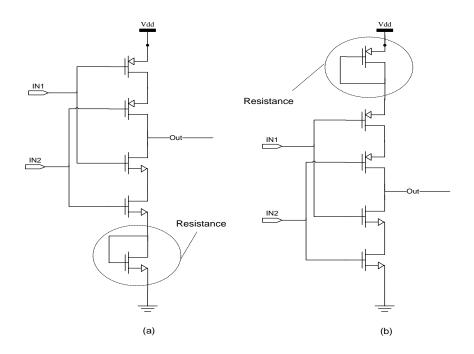

| Figure 4.6: NAND gate with added resistance93                                                                                                                                                                |

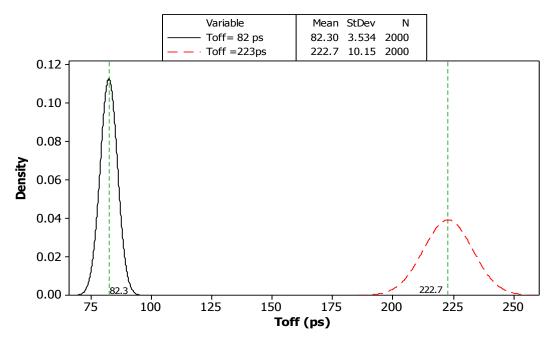

| Figure 4.7: Histogram plots for two values of $T_{\text{off}}$ , implemented using two inverters, against process variation                                                                                  |

| Figure 4.8: Histogram plots for the gain against process variation for the three time amplifier circuits implemented using the NAND gate with added resistance between Vdd and the NAND gate96               |

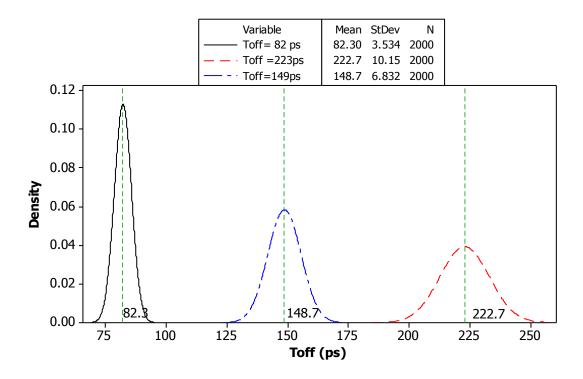

| Figure 4.9: Histogram plots for the values of $T_{\text{off}}$ , implanted using two inverters, against process variation                                                                                    |

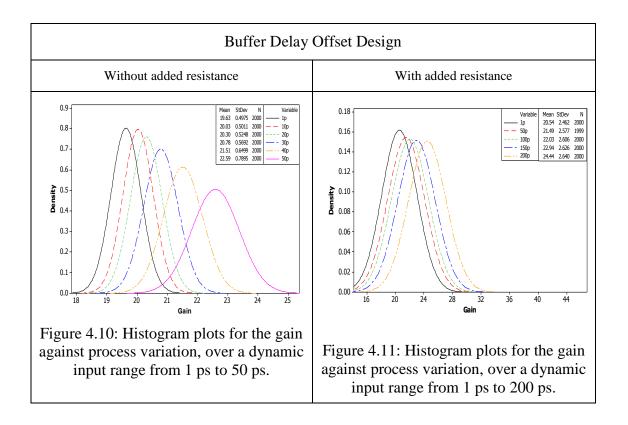

| Figure 4.10: Histogram plots for the gain against process variation, over a dynamic input range from 1 ps to 50 ps                                                                                           |

| Figure 4.11: Histogram plots for the gain against process variation, over a dynamic input range from 1 ps to 200 ps                                                                                          |

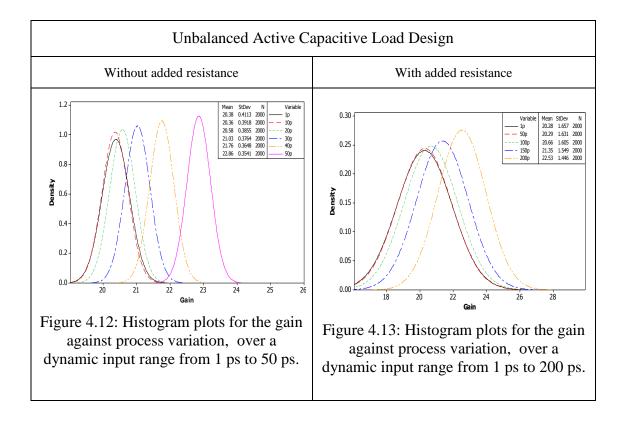

| Figure 4.12: Histogram plots for the gain against process variation, over a dynamic input range from 1 ps to 50 ps99                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 4.13: Histogram plots for the gain against process variation, over a dynamic input range from 1 ps to 200 ps99                                            |

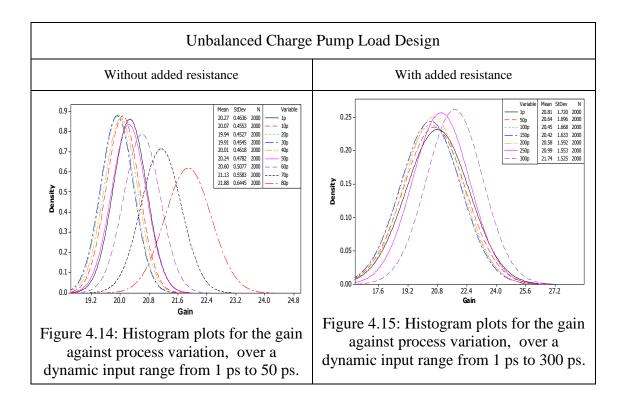

| Figure 4.14: Histogram plots for the gain against process variation, over a dynamic input range from 1 ps to 50 ps                                               |

| Figure 4.15: Histogram plots for the gain against process variation, over a dynamic input range from 1 ps to 300 ps                                              |

| Figure 4.16: The characteristics for the time amplifier100                                                                                                       |

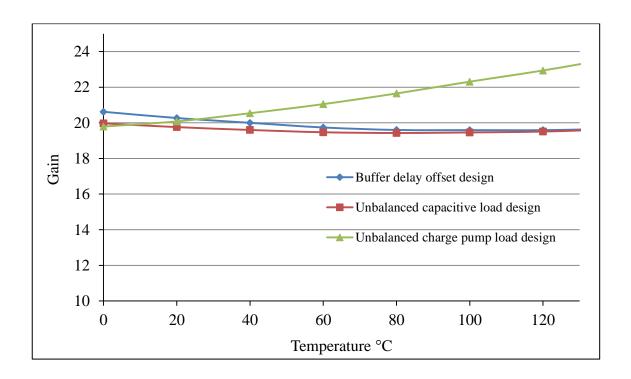

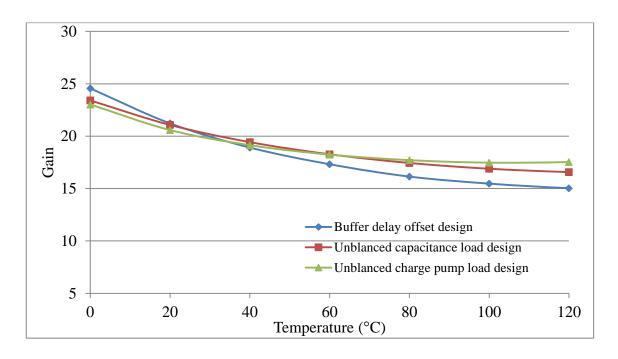

| Figure 4.17: Variation of gain for the three time amplifier circuits against temperature.                                                                        |

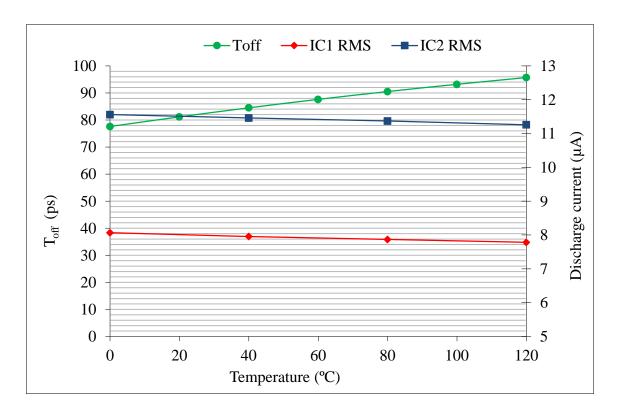

| Figure 4.18: $T_{\text{off}}$ and the discharge currents against the temperature-buffer delay offset design                                                      |

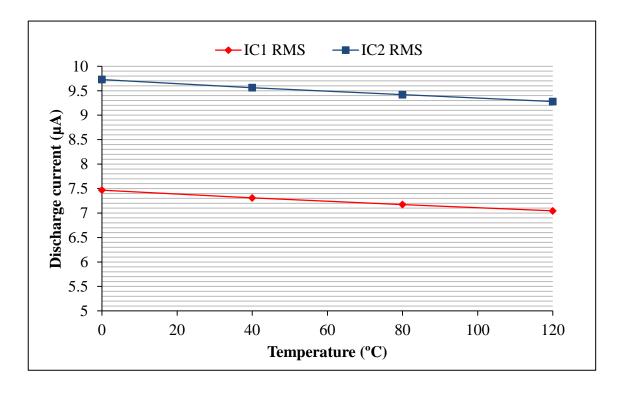

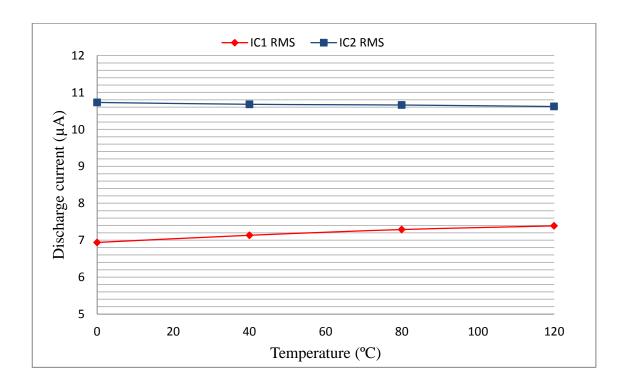

| Figure 4.19: The discharge currents against the temperature-unbalanced capacitance load design                                                                   |

| Figure 4.20: (a) Time amplifier using unbalanced active load design. Unbalanced active charge pump load using (b) C1> C2 and105                                  |

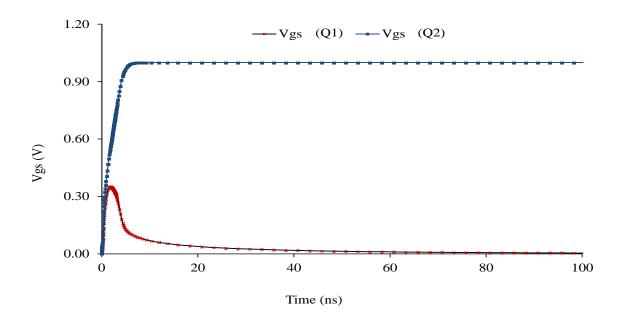

| Figure 4.21: $V_{gs}$ for $Q_1$ and $Q_2$ , during discharge time                                                                                                |

| Figure 4.22: The discharge currents against the temperature-unbalanced charge pump load design                                                                   |

| Figure 4.23: Variation of gain against temperature for the three time amplifier circuits using NAND gate with added resistance technique107                      |

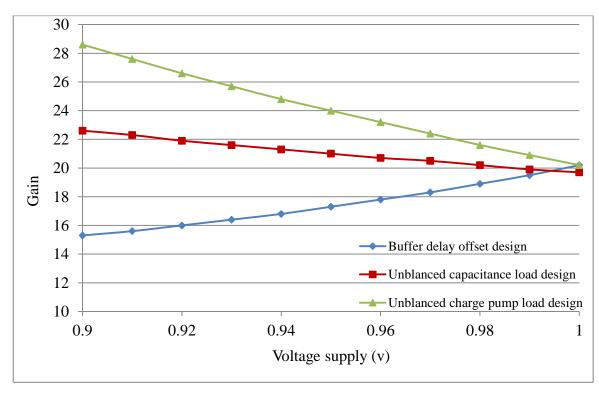

| Figure 4.24: Variation of gain against the change in the supply voltage for the three time amplifier circuits                                                    |

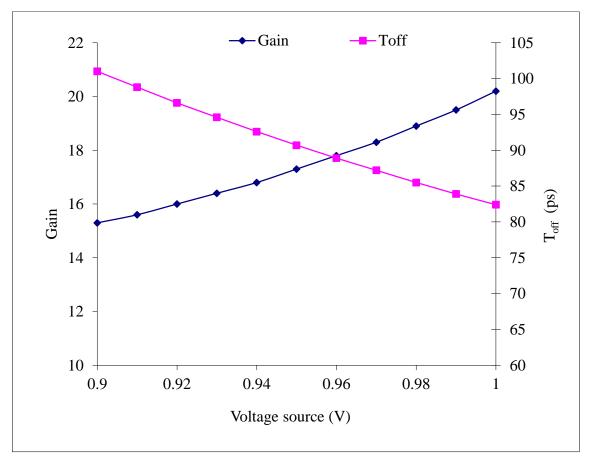

| Figure 4.25: Variation in $T_{\rm off}$ and the gain against the voltage source-buffer delay offset design without using added resistance109                     |

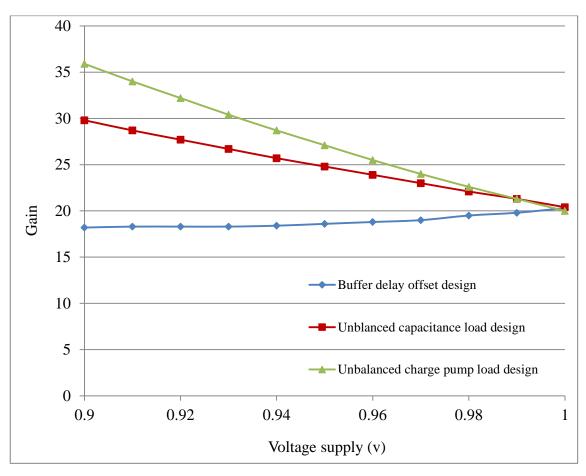

| Figure 4.26: Variation of gain against the change in the voltage source for the three time amplifier circuits using NAND gate with added resistance technique110 |

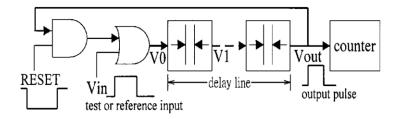

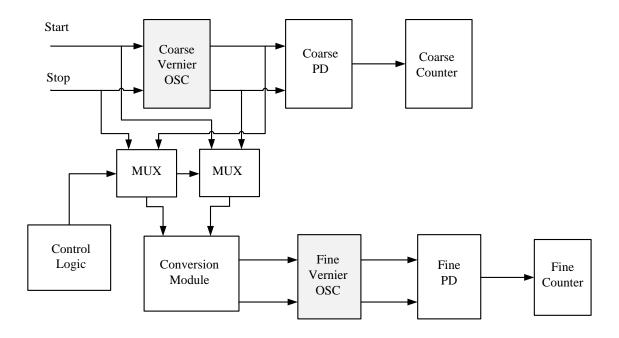

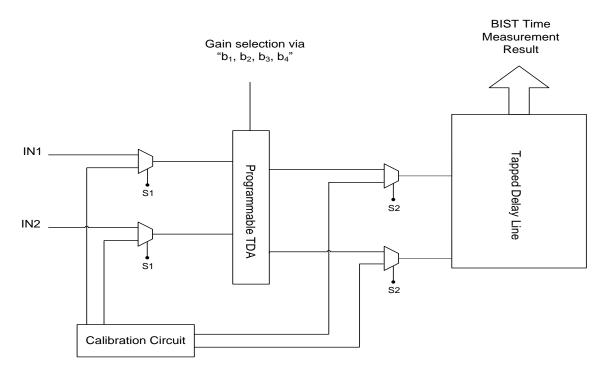

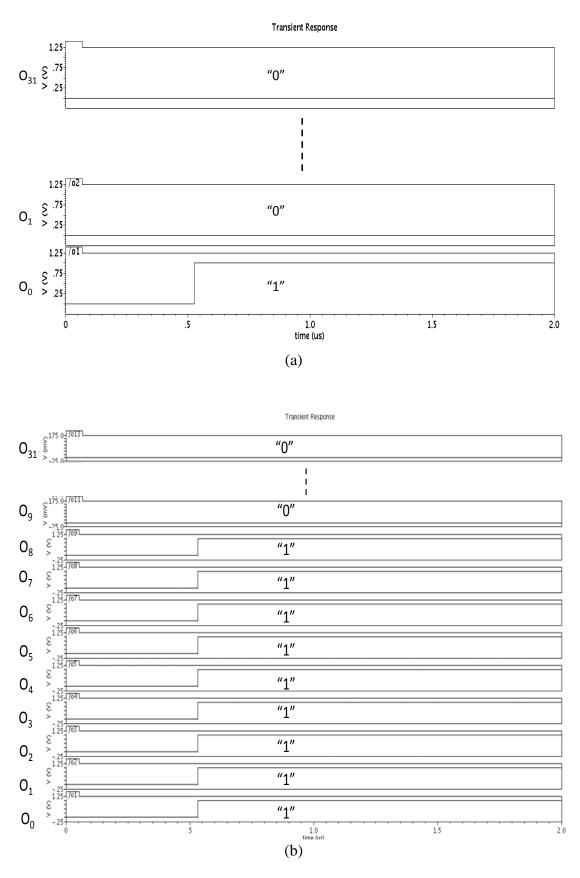

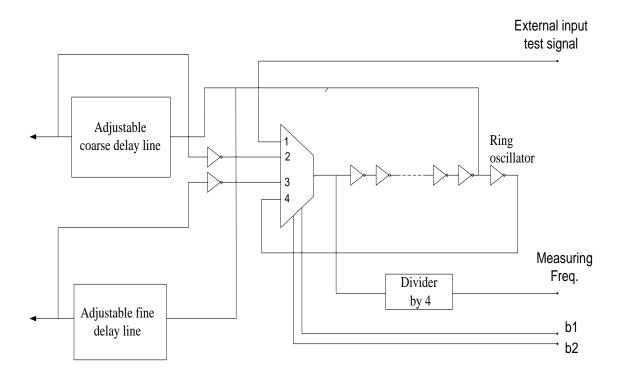

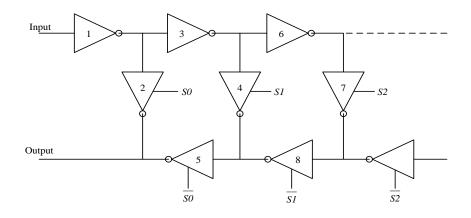

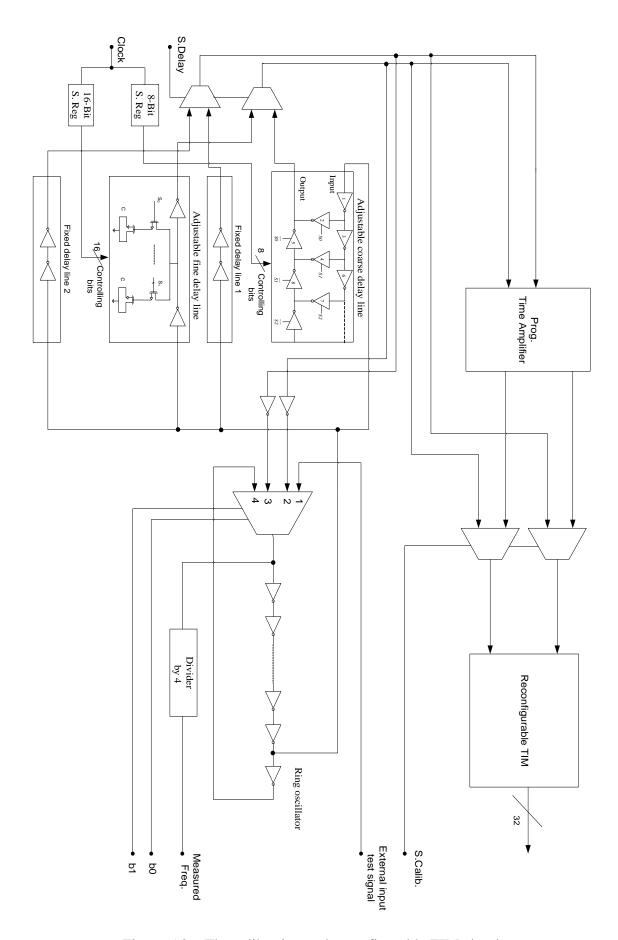

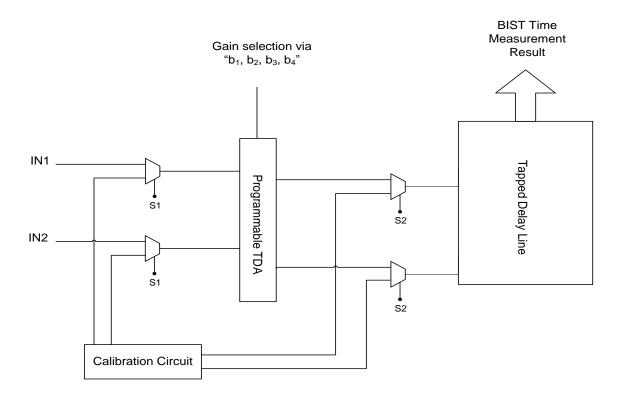

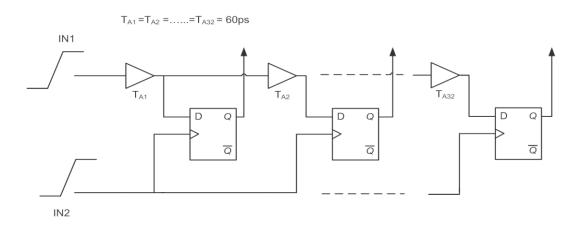

| Figure 5.1: Block diagram of the reconfigurable TIM113                                                                                                           |

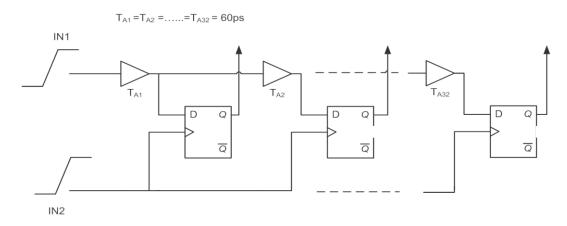

| Figure 5.2: Block diagram of the tapped delay line114                                                                                                            |

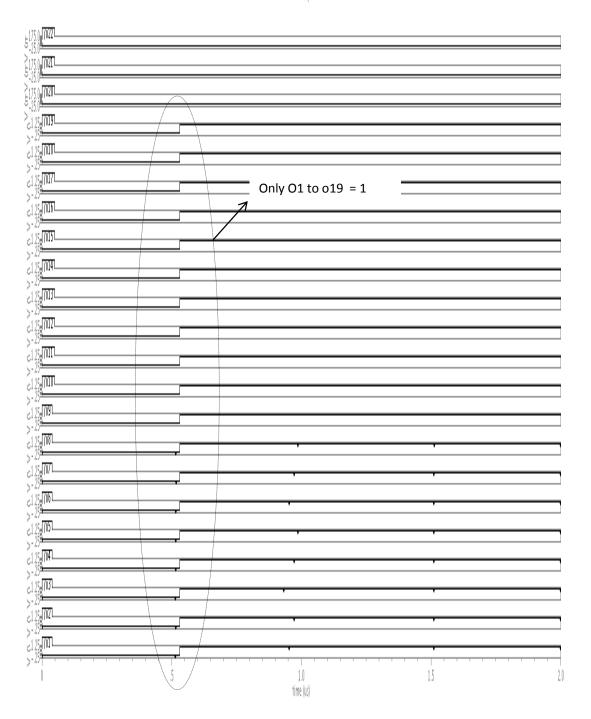

| Figure 5.3: The simulation results of the IN1 as it is propagated through the delay line                                                                         |

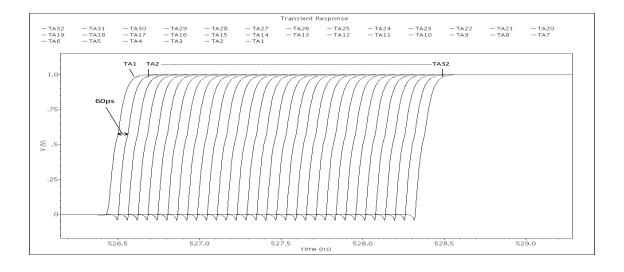

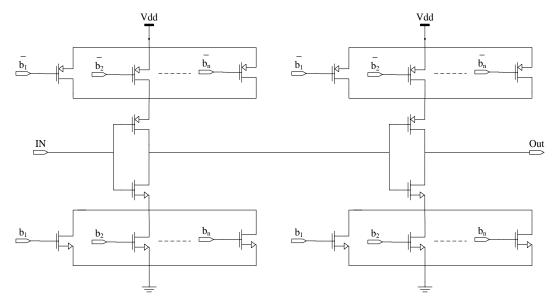

| Figure 5.4: Programmable time amplifier circuit115                                                                                                               |

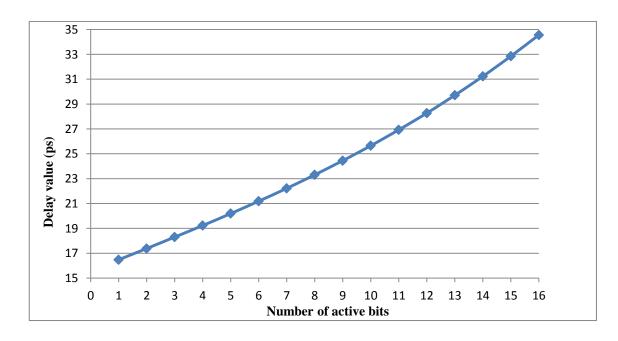

| Figure 5.5: Programmable time amplifier gain versus Control Bit Pattern.                                                                                         |

|                                                                                                                                                                  |

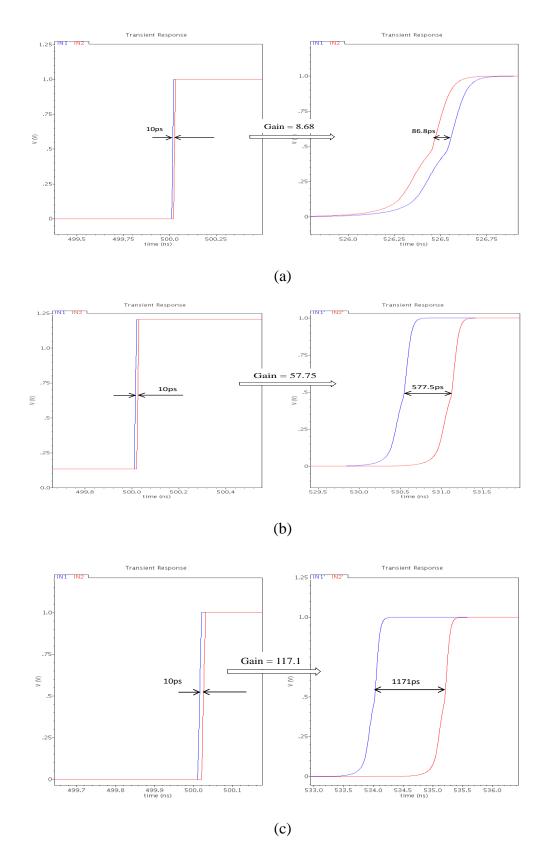

| Figure 5.6: The result of the time amplifier for three gain values                                                                                               |

| Figure 5.7: TIM result for $\Delta T_{input}$ =10ps and gain value (a) 8.68 and (b) 57.75                                                                        |

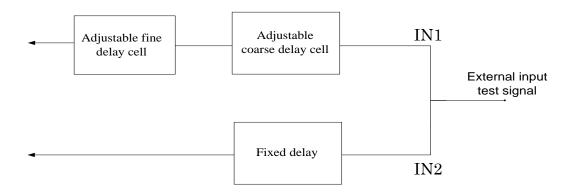

| Figure 5.8: Block diagram of the calibration circuit                                                                                                             |

| Figure 5.9: A simple adjustable coarse delay line [15]122                                                                                                        |

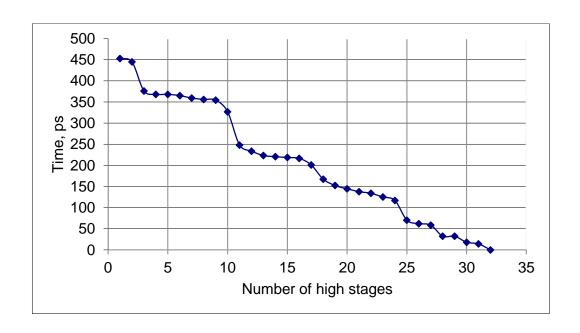

| Figure 5.10: Simulation results for the adjustable coarse delay line                                                                                             |

| Figure 5.11: Adjustable fine delay line using parallel NMOS capacitances[15].                                                   |

|---------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                 |

| Figure 5.12: Linearity plot for the adjustable fine delay line using parallel NMOS capacitances                                 |

| Figure 5.13: The differential digital-control delay cell [9]                                                                    |

| Figure 5.14: The result of the adjustable fine delay line using the differential digital-control delay                          |

| Figure 5.15: Current starved delay element [13]                                                                                 |

| Figure 5.16: Linearity plot for the adjustable fine delay line using the current starved delay elements                         |

| Figure 5.17: Histogram plots for the delay step of the differential digitally-controlled delay method against process variation |

| Figure 5.18: Histogram plots for the delay step of the current starved delay method against process variation                   |

| Figure 5.19: Histogram plots for the delay step of the parallel NMOS capacitances method against process variation.             |

| Figure 5.20: Variation of the delay for the differential digital-control delay against temperature                              |

| Figure 5.21: Variation of the delay for the current starved delay circuit against temperature.                                  |

| Figure 5.22: Variation of the delay for the parallel NMOS capacitances against temperature.                                     |

| Figure 5.23: Variation of delay against the changes in the supply voltage for the differential digital-control delay circuit.   |

| Figure 5.24: Variation of delay against the changes in the supply voltage for the parallel NMOS capacitances circuit            |

| Figure 5.25: Variation of delay against the changes in the supply voltage for the current starved delay circuit.                |

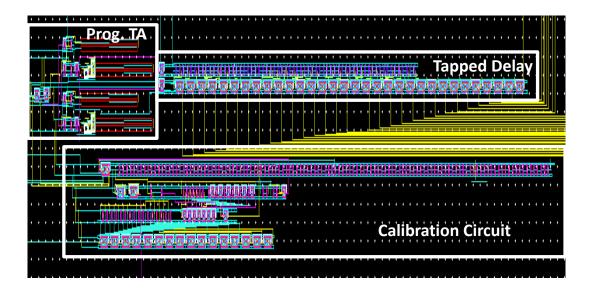

| Figure 5.26: The calibration and reconfigurable TIM circuits                                                                    |

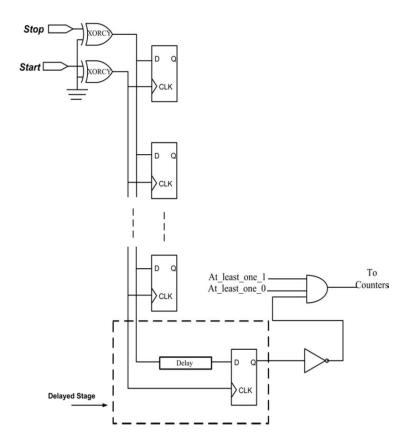

| Figure 5.27: Block diagram of coarse delay block                                                                                |

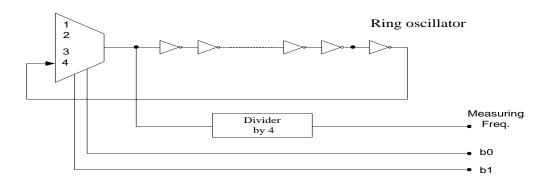

| Figure 5.28: Calibration circuit configured to measure ring oscillator frequency136                                             |

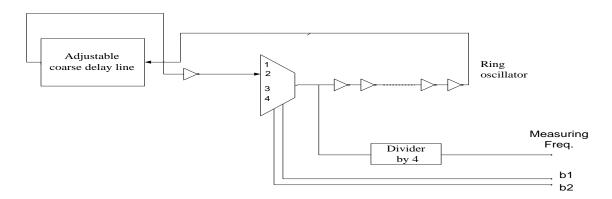

| Figure 5.29: Calibration circuit configured to incorporate the effect of delay line 136                                         |

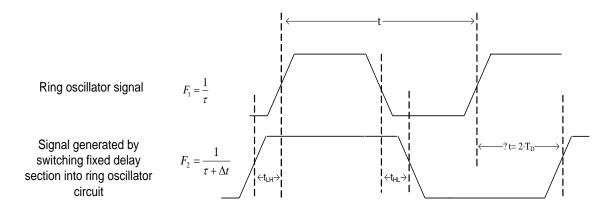

| Figure 5.30: The effect of adding a delay section into the ring oscillator loop137                                              |

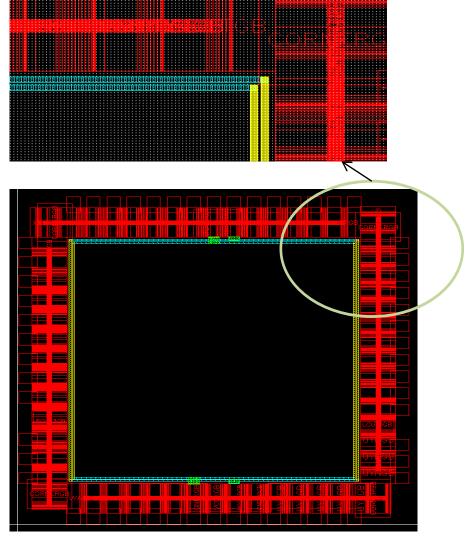

| Figure 5.31: All around two thick wires are used for voltage supply and ground141                                               |

| Figure 5.32: Reconfigurable TIM layout                                                                                          |

| Figure 5.33: The layout of the reconfigurable TIM chip                                                                          |

| Figure 6.1: The block diagram of the reconfigurable TIM                                                                         |

| Figure 6.2: Block diagram of delay line                                                                                         |

| Figure 6.3: Block diagram for the LOC                                                                                           |

| B1 TIM result for ΔTinput=10ps and gain value 117.1.                                                                            |

## **Table of Tables**

# Chapter 1

### Introduction

#### 1.1 Background

Recently, Integrated Circuits (ICs) have seen large advances in terms of performance and functionality per unit area to address the demands of market forces. Typically, these advances have been achieved by scaling down the size of the transistors, which also has reduced the cost per transistor, as a large number of scaled-down transistors can occupy a smaller area [1]. In addition, the reduction in transistor size will continue and is expected to reach 10 nm by 2015 [2]. However, as the scaling down of technology has been increased to meet the demands of market forces, the effect of random variations in the fabrication process has also increased, causing a reduction in the robustness and reliability of the designs [3-5].

Process variation is a challenging problem in very deep sub-micro CMOS process technologies. As the device dimensions are scaled down, design parameter variability is producing increasingly unpredictable consequences in circuit performance. As a result, maintaining the correct timing relationships between signals in an IC is becoming problematic and, ultimately, can cause a functional failure. However, it is becoming more difficult to measure the temporal relationship between signals in an IC using Standard Automatic Test Equipment (ATE) due to the lack of measurement resolution and accessibility, resulting in the need for on-chip time measurement circuitry [6, 7], which is the objective of this project as discussed later.

This chapter continues with an overview of manufacturing defects in Section 1.2, while Sections 1.3 describes some timing anomalies which occur in circuits such as jitter, clock skew and metastability which need to be measured. Section 1.4 outlines the design criteria to be satisfied for an effective implementation of an "on-chip" time measurement scheme. The Chapter concludes with the contributions made to this area of research and a road map of the thesis, in sections 1.5 and 1.6.

#### 1.2 Process Variation and Manufacturing Defects

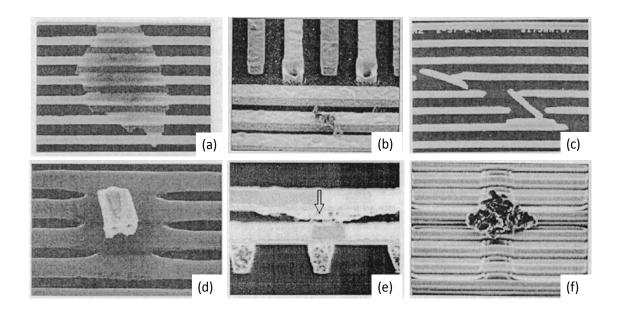

The manufacture of present day ICs is a complex process requiring an excess of 900 steps and 34 masking levels. At any stage a scratch on a mask as a contaminant can result in open or short circuit occurring in the interconnections. In addition, the variability in doping, etching, oxidation, metallisation, and other fabrication steps produces a random variation in transistor and interconnect parameters [8-10]. The effect of random variations in the fabrication process has increased as scaling technology has reached the nanometre regime [3, 4]. For example, the ultra-thin gate oxide layer, in the range of 1-3 nm, in the extremely deep sub-micron CMOS process, has become very sensitive to very small variations in the fabrication process [3]; the effect of process variations on gate oxide has a direct impact on the electrical characteristics of the transistor. As another example, with the reduction in the transistor size the amount of dopant atoms has decreased and the subsequent impact of random dopant fluctuation has been magnified [11]. This variation on the electrical characteristics of the transistors has an influence on the overall circuit performance [12]. Figure 1.1 shows examples of the effect on interconnect resulting from defect in the manufacture process.

Figure 1.1: Common interconnect defects (a) shorting of metal lines owing unexposed photoresist (b) metallization defect causing a short between two lines (c) shorts and breaks of metal lines due to a scratch in the photoresist (d) shorting among several metal lines as a result of a solid-state particle on the metal mask (e) Inter-layer short between two interconnects (f) short among several metal lines due to a metallization defect [13].

#### 1.2.1 Causes of Delay Faults

As the device size is continuously scaled down, both the speed of the device and its packing density are increased, which leads to an increase in IC performance. However, high performance ICs have a lower timing budget. The time budget is the smallest margin of time in the clock pulse which is necessary to ensure the correct temporal operation of a circuit, for example, latching data into a register. This narrow margin must take into account all the system delays, clock skew and clock jitter, and must be calculated as narrow as possible if the performance of the circuit is to be optimal. As the timing budget is decreased, the discrepancies in the temporal relationships between signals on the chip have become a major design issue, especially in synchronizer circuits where a clock or multiple clocks control the performance and function of the circuits. The faulty behaviour in the timing relationships between signals are typically caused by defects in the manufacturing process or the operating conditions in the circuit as described below.

a) Delays resulting from fabrication defects: Defects during manufacture which cause delay faults can be categorised into two main groups, namely, transistor and interconnect. Transistor defects can either decrease or increase the switching

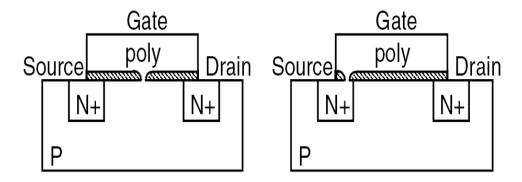

speed of the device. For instance, the Gate-Oxide-Short is one of the transistor defects which has a large impact on the transistor structure affecting the electrical properties of a device [14, 15]. A Gate-Oxide-Short occurs when the integrity of the gate oxide is compromised, due to the lithographic defects or gate oxide growing defect, causing a short circuit between the gate and drain, source or transistor channel, as shown in Figure 1.2. This short circuit between the polysilicon gate and underlying silicon surface creates a resistance depending upon the defect size. The Gate-Oxide-Short increases the delay fault by an amount depending upon the value of the resistance which is created by this defect. In addition, there are several transistor defects causing a delay faults such as defective p-n junctions, transistor with incorrect threshold voltages due to the affects of process variations [14]. On the other hand, delay defects can be caused by the imperfections occurring, during fabrication of interconnect creating resistive opens and shorts [13, 14].

Figure 1.2: Gate-Oxide-Short (short between polysilicon gate and underlying silicon surface).

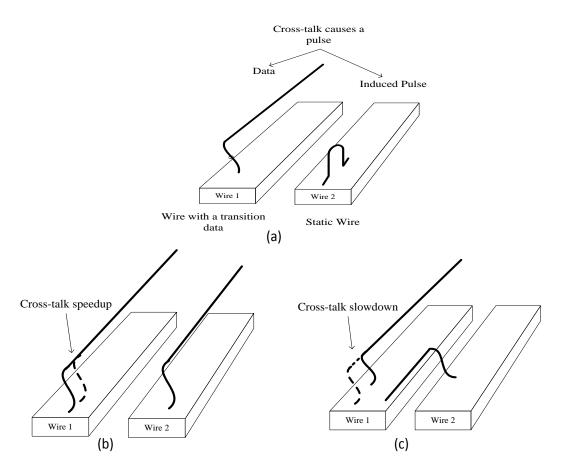

b) Delays resulting from the operating conditions: Intensive mixing of different circuits, which are composed of storage elements, dynamic gates, latches, and so on, combines with the defects in the transistors and interconnects create devices with different driving strengths and load mismatches, which leads to cross-talk and internal noise between elements. Cross-talk, according to its effect, can cause either a pulse or a delay [15-19]. The first type occurs when one of the wires is static, and transitions, through capacitive coupling, on the neighbouring wires cause a pulse on it, as shown in Figure 1.3 (a). The second type results from two neighbouring wires having transitions in the same or opposite directions. However, as shown in Figure 1.3 (b), if both transitions propagate in the same direction, the transition delay is reduced. This is called cross-talk

speed-up. By contrast, if both transitions propagate in the opposite directions, the transition delay is increased, as shown in Figure 1.3 (c) and is referred to as cross-talk slow-down.

Figure 1.3: Cross-talk causing (a) a pulse, (b) cross-talk speed-up and (c) cross-talk slow-down.

Delay faults can also occur during normal operation due to variations in power supply voltage and temperature [8, 20, 21]. The difference in temperature within the die is one of the challenges for high speed ICs [21]. As shown in Equation (1) [22], the inverter delay is a function of the supply voltage and also the drain saturation current  $I_{D(S)}$ , which itself is affected by supply voltage and temperature [21].

$$T_{P} = \left[ \frac{\frac{V_{TH}}{V_{DD}} + \alpha}{1 + \alpha} - \frac{1}{2} \right] \cdot T_{IN} + \frac{C_{T} \cdot V_{DD}}{2 \cdot I_{D(s)}} - (1.1)$$

Where  $v_{TH}$  = the threshold voltage,  $\alpha$  is the velocity saturation index  $(1 \le \alpha \le 2)$   $C_T$  is the total capacitance discharged,  $T_{IN}$  is the input rise/fall time, and  $I_{D(s)}$  is the drain saturation current.

Delay faults as a result of fabrication defects and operating conditions cause discrepancies in the temporal relationships between signals, which are the main reasons for the occurrence of clock jitter and clock skew.

#### **1.3 Timing Anomalies**

The main timing anomalies which can occur within a circuit associated with clock signals are jitter, skew and metastability.

a) Clock jitter: Clock jitter can be defined as a variation or displacement in the phases of the clock from their ideal position. Jitter, depending upon how it is measured, can be classified as: cycle to cycle jitter, period jitter, and long-term jitter [23-27], as shown in Figure 1.4. Cycle to cycle jitter is the change in the cycle phase compared with the previous cycle; period jitter is the change in the clock phase compared with the fixed ideal position, where normally a reference clock represents the ideal clock. Long-term jitter is related to the change in the clock phases compared with their ideal position for a large number of cycles. Jitter values are represented either as an average value of the variation in the clock phases, the peak-to-peak value which is the maximum and minimum variation in the clock phases, or a combination of both.

Figure 1.4 (a) Cycle to cycle jitter, (b) Period jitter, and (c) Long-term jitter.

b) Clock skew: Clock skew is defined as the differences in the arrival of the clock to several elements at different times which would cause a functional error [28, 29]. Figure 1.5 shows a clock skew which is caused by the delay in clock routing T<sub>skew1</sub>, T<sub>skew2</sub>, and T<sub>skew3</sub>.

Figure 1.5: Clock skew signals.

c) Metastability: The metastability [30, 31] occurs in synchroniser circuits, such as flip-flops and latches, when the arrival-time differences between the data and clock violates the minimum set-up time leading the output to go into a metastable state. In this state, the output voltage remains in the middle between

the high and low values, where after a certain time the output settles to either a high or low value, the output becomes difficult to be predicted. This issue is normally avoided, as the output is estimated to be stable after each clock cycle. Figure 1.6 describes the behaviour of the flip-flop with variations in the arrival times of the data and clock, and the responses of the output.

Figure 1.6: The responses of the flip-flop output to the different temporal relationships between data and clock signal.

#### 1.4 On Chip Time Measurement

Since many of the timing anomalies occur within an IC, standard ATE cannot be used due not only to accessibility issues but also due to a lack of measurement resolution, necessitating in the use of "on-chip" time measurement schemes. The requirements to be met by the "on-chip" time measurement scheme depends upon the application and hence are quite diverse. However, there are five main design parameters which must be

considered; namely, measurement resolution, measurement dynamic range, time measurement, measurement error and calibration technique. These are described blow in more detail.

- a) Measurement resolution: This term defines the minimum difference in the time interval which can be measured. The value of the measurement resolution depends on the requirements of the application. For example, jitter measurement requires a higher resolution than one used for some physical experiment, such as particle identification in Time-of-Flight (TOF) detectors, where a resolution of few tens of picoseconds is sufficient to attain a result [32].

- **b) Dynamic range:** The dynamic range is the difference between the maximum and minimum values of the time intervals that can be measured. Defining the dynamic range also depends on the applications requirements.

- c) Measurement time: This is the time taken to perform the measurement. However, this parameter is linked to the measurement dynamic range and the technique used for the time measurement.

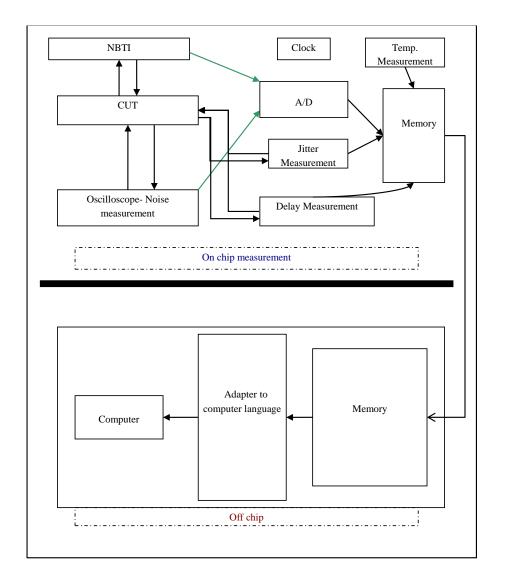

- d) Measurement error: The accuracy of a given measurement technique is affected by process, power supply and temperature variations. Moreover, as the device sizes are scaled down, the measurement error is increased owing to the increase in sensitivity to the variations of process, temperature and power supply. In addition, interconnects in the time measurement circuit can cause an additional delay between the two input signals, which leads to an error in the measurement. Therefore, an accurate calibration technique is required to reduce these defects.

- e) Calibration technique: This is the method used to maintain the accuracy of the measurement. There are several methods of calibration, such as comparison with a standard measurement [33] or a statistical method [34]. The calibration technique not only impacts on a measurement technique in terms of the measurement accuracy, power consumption and area overhead but also in terms of the time taken and the complexity of the procedure itself.

The importance of each of the above criteria depends upon the application. When the various measurement schemes are reviewed in Chapter 2, the advantages and disadvantages of each, regarding the above design attributes, will be outlined.

#### 1.5 Research Contribution

The following paragraphs outline the main research contributions described in this thesis:

#### a) Improvements to time resolution:

As clock speeds increase improvement in time measurement resolution are required. The use the concept of "time amplification" is a way of achieving this improvement. However, using a time difference amplifier in time measurement meets a major limitation due to the narrow dynamic input range of the time difference amplifier. In this work a time difference amplifier has been developed incorporating three techniques to improve the circuit and dynamic range. The first technique uses Unbalanced Active Capacitance Loads which have the same result as the buffer delay offset design (current method) [35], with a reduce area overhead and increased robustness to the effects of process variation, as discussed in Chapters 3 and 4. The second method uses Unbalanced Active Charge Pump Loads, in this design, the dynamic input range is extended by approximately 75% compared with the buffer delay offset design, as described in Chapter 3. The third technique uses NAND Gate with Added Resistance which can be use in conjunction with the buffer delay offset, the unbalanced capacitance load and the unbalanced charge pump load circuits extending their dynamic range, as highlighted in Chapter 3. For example, the dynamic input range of the unbalanced charge pump load design is extended from 70 ps to 300 ps using NAND gate with added resistance.

#### b) Programmable time difference amplifier:

The programmable time difference amplifier circuit is an all-digital wide dynamic input range time difference amplifier with adjustable gain as described in Chapter 3. The programmable time difference amplifier is designed to have a variable gain ranging from 4 to 117 with a very wide dynamic input range.

#### c) Analysis of the effects of process variation:

The robustness to effects of power supply, temperature and process variations was analysed on the buffer delay offset, unbalanced capacitance loads, unbalanced charge pump loads and NAND gate with added resistance techniques as described in Chapter 4. These studies were undertaken with the

aim of minimising the effects of the process variation on the time different amplifier circuits. The results show that unbalanced active capacitive load and unbalanced active charge pump load designs are more robust than the buffer delay offset design in terms of gain variation. In addition, although, implementing the three time difference amplifier circuits using NAND gate with added resistance creates a huge improvement in terms of the dynamic input range, the gain sensitivity to the process variations is increased. Moreover, the gain of the buffer delay offset design when implemented using the NAND gate with added resistance was significantly affected by the process variation compared with the unbalanced active capacitive load and unbalanced active charge pump load designs.

#### d) A reconfigurable time measurement circuit:

A reconfigurable time measurement circuit was designed with an adjustable resolution range of 15 down to 0.5 ps and a measurement dynamic range of 480 to 16 ps to perform a variety of time related measurements which require different test specifications; such as set-up and hold time measurements and jitter measurement. It is considered that a reconfigurable measurement system will occupy less chip area than a range of measurement circuits designed for one specific test. The reconfigurable time measurement consists of two parts, a programmable time difference amplifier and a 32 cell tapped delay line. The programmable time difference amplifier is designed to have a gain ranging from 4 to 117 with a very wide dynamic input range.

It is considered that the above contributions make an advancement to the state of art related the on-chip time measurement techniques. In addition, during this work, a journal and a conference papers have been published [36, 37].

#### 1.6 Thesis Roadmap

The motivation, background and need for this work have been discussed in the previous sections, the roadmap of the remainder of the thesis is outlined below.

The techniques currently used for time measurement are reviewed in Chapter 2. In addition, the advantages and disadvantages of each method are discussed comparing the following parameters: measurement resolution, dynamic range, measurement time,

measurement error and calibration technique. The chapter is sectionalized depending on the methodology that has been used.

In Chapter 3, three techniques to improve the dynamic range of the time difference amplifier are outlined. In addition, the analysis of the buffer delay offset design is discussed and compared with the new techniques. Gain and amplification range are the main parameters which are compared. The chapter concludes with a description of the design of the programmable time difference amplifier.

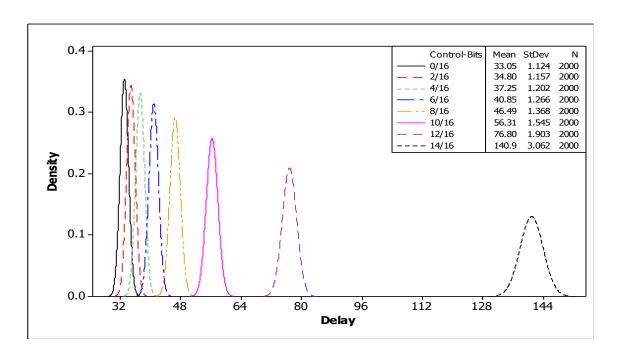

In Chapter 4, the reliability of the buffer delay offset, unbalanced active capacitive load, unbalanced active charge pump load and NAND gate with added resistance techniques are discussed. In this study, Monte Carlo (MC) analysis is used, as it is more pragmatic to study the process variations effect than using multiple corner analyses [37]. The MC was run considering the process variation of  $3\sigma$  with 2000 samples at Vdd = 1V and  $27^{\circ}$ C. Moreover, the effect of the voltage supply and temperature variation is discussed.

In Chapter 5, the design of a reconfigurable time measurement scheme with adjustable resolution and dynamic range is described. The reconfigurable time measurement scheme is first configured to measure the time difference between two signals. After performing the measurement, the time measurement circuit can be reconfigured to different resolution and dynamic range in order to be reused for other time measurements, such as jitter, set-up and hold times etc. The time measurement circuit with reconfigurable resolution and dynamic range can be considered to consume less area overhead compared to the fixed resolution time measurement, as the same circuit is used for different functions. In addition, in this Chapter, the calibration circuit for the reconfigurable time measurement is discussed. The calibration procedure is based on calibrating the tapped delay line to known delay values thereafter the gain of the time amplifier is measured using the calibrated tapped delay line. The reconfigurable time measurement circuit was designed in a 90nm CMOS technology where the chip layout is implemented as a full custom design. The area occupied by reconfigurable TIM circuit is 379.5 µm x 67.5 µm.

Finally, Chapter 6 outlines the summary and conclusions to this work and the possible future works.

#### 1.7 References

- [1] S. E. Thompson and S. Parthasarathy, "Moore's law: the future of Si microelectronics," *Materials Today*, vol. 9, pp. 20-25, Jun 2006.

- [2] M. LaPedus. *Intel: EUV late for 10-nm milestone*. Available: <a href="http://www.eetimes.com/electronics-news/4213628/Intel--EUV-misses-10-nm-milestone">http://www.eetimes.com/electronics-news/4213628/Intel--EUV-misses-10-nm-milestone</a>

- [3] K. Bernstein, D. J. Frank, A. E. Gattiker, W. Haensch, B. L. Ji, S. R. Nassif, E. J. Nowak, D. J. Pearson, and N. J. Rohrer, "High-performance CMOS variability in the 65-nm regime and beyond," *IBM Journal of Research and Development*, vol. 50, pp. 433-449, Jul-Sep 2006.

- [4] K. Agarwal and S. Nassif, "Characterizing process variation in nanometer CMOS," 2007 44th ACM/IEEE Design Automation Conference, Vols 1 and 2, pp. 396-399, 2007.

- [5] S. Nassif, M. Orshansky, and D. Boning, *Design for manufacturability and statistical design : A constructive approach*: US Springer, 2008.

- [6] Y. Zorian, S. Dey, and M. J. Rodgers, "Test of future system-on-chips," *Iccad* 2000: *IEEE/ACM International Conference on Computer Aided Design*, pp. 392-398, 2000.

- [7] S. Tabatabaei and A. Ivanov, "Embedded timing analysis: A SoC infrastructure," *IEEE Design & Test of Computers*, vol. 19, pp. 24-36, May-Jun 2002.

- [8] M. Alioto and G. Palumbo, "Impact of supply voltage variations on full adder delay: Analysis and comparison," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 14, pp. 1322-1335, Dec 2006.

- [9] B. H. Calhoun, Y. Cao, X. Li, K. Mai, L. T. Pileggi, R. A. Rutenbar, and K. L. Shepard, "Digital circuit design challenges and opportunities in the era of nanoscale CMOS," *Proceedings of the IEEE*, vol. 96, pp. 343-365, Feb 2008.

- [10] D. Sylvester, K. Agarwal, and S. Shah, "Variability in nanometer CMOS: Impact, analysis, and minimization," *Integration-the VLSI Journal*, vol. 41, pp. 319-339, May 2008.

- [11] H. Mahmoodi, S. Mukhopadhyay, and K. Roy, "Estimation of delay variations due to random-dopant fluctuations in nanoscale CMOS circuits," *Solid-State Circuits, IEEE Journal of*, vol. 40, pp. 1787-1796, 2005.

- [12] S. Kang, Y. Leblebici, *CMOS Digital Integrated Circuits*, 2ed.: Mc-Graw Hill, 1999.

- [13] R. Rajsuman, "Iddq testing for CMOS VLSI," *Proceedings of the IEEE*, vol. 88, pp. 544-566, Apr 2000.

- [14] J. M. Soden and C. F. Hawkins, "Electrical properties and detection methods for CMOS IC defects," in *European Test Conference*, 1989., *Proceedings of the 1st*, 1989, pp. 159-167.

- [15] J. Briaire and K. S. Krisch, "Principles of substrate crosstalk generation in CMOS circuits," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 19, pp. 645-653, Jun 2000.

- [16] C. Wei-Yu, S. K. Gupta, and M. A. Breuer, "Test generation for crosstalk-induced delay in integrated circuits," in *Test Conference*, 1999. Proceedings. International, 1999, pp. 191-200.

- [17] A. Rubio, N. Itazaki, X. O. Xu, and K. Kinoshita, "An Approach to the Analysis and Detection of Crosstalk Faults in Digital VLSI Circuits," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 13, pp. 387-395, Mar 1994.

- [18] A. K. Goel and Y. R. Huang, "Modeling of Crosstalk among the Gaas-Based VLSI Interconnections," *Iee Proceedings-G Circuits Devices and Systems*, vol. 136, pp. 361-368, Nov 1989.

- [19] R. Anglada and A. Rubio, "An Approach to Crosstalk Effect Analysis and Avoidance Techniques in Digital Cmos VLSI Circuits," *International Journal of Electronics*, vol. 65, pp. 9-17, Jul 1988.

- [20] S. Borkar, T. Kamik, S. Narendra, J. Tschanz, A. Keshavarzi, and V. De, "Parameter variations and impact on circuits and microarchitecture," *40th Design Automation Conference, Proceedings* 2003, pp. 338-342, 2003.

- [21] R. Kumar and V. Kursun, "Impact of temperature fluctuations on circuit characteristics in 180nm and 65nm CMOS technologies," 2006 IEEE International Symposium on Circuits and Systems, Vols 1-11, Proceedings, pp. 3858-3861, 2006.

- [22] M. M. Mansour and N. R. Shanbhag, "Simplified current and delay models for deep submicron CMOS digital circuits," 2002 IEEE International Symposium on Circuits and Systems, Vol V, Proceedings, pp. 109-112, 2002.

- [23] K. Taylor, B. Nelson, A. Chong, H. Nguyen, H. Lin, M. Soma, H. Haggag, J. Huard, and J. Braatz, "Experimental results for high-speed jitter measurement technique," *International Test Conference 2004, Proceedings*, pp. 85-94, 2004.

- [24] A. Zanchi, A. Bonfanti, S. Levantino, and C. Samori, "General SSCR vs. cycleto-cycle jitter relationship with application to the phase noise in PLL," 2001 Southwest Symposium on Mixed-Signal Design, pp. 32-37, 2001.

- [25] T. J. Yamaguchi, M. Soma, D. Halter, R. Raina, J. Nissen, and M. Ishida, "A method for measuring the cycle-to-cycle period jitter of high-frequency clock signals," *19th IEEE VLSI Test Symposium, Proceedings*, pp. 102-110, 2001.

- [26] M. Shimanouchi, "An approach to consistent jitter modeling for various jitter aspects and measurement methods," *International Test Conference 2001, Proceedings*, pp. 848-857, 2001.

- [27] F. Herzel and B. Razavi, "A study of oscillator jitter due to supply and substrate noise," *IEEE Transactions on Circuits and Systems II-Analog and Digital Signal Processing*, vol. 46, pp. 56-62, Jan 1999.

- [28] S. Lin and C. K. Wong, "Process-Variation-Tolerant Clock Skew Minimization," 1994 IEEE/ACM International Conference on Computer-Aided Design Digest of Technical Papers, pp. 284-288, 1994.

- [29] S. Pullela, N. Menezes, and L. T. Pillage, "Reliable Nonzero Skew Clock Trees Using Wire Width Optimization," *30th Design Automation Conference: Proceedings* 1993, pp. 165-170, 1993.

- [30] A. Cantoni, J. Walker, and T. D. Tomlin, "Characterization of a flip-flop metastability measurement method," *IEEE Transactions on Circuits and Systems I-Regular Papers*, vol. 54, pp. 1032-1040, May 2007.

- [31] C. Dike and E. Burton, "Miller and noise effects in a synchronizing flip-flop," *IEEE Journal of Solid-State Circuits*, vol. 34, pp. 849-855, Jun 1999.

- [32] M. Mota, J. Christiansen, S. Debieux, V. Ryjov, P. Moreira, and A. Marchioro, "A flexible multi-channel high-resolution time-to-digital converter ASIC," in *Nuclear Science Symposium Conference Record*, 2000 IEEE, 2000, pp. 9/155-9/159 vol.2.

- [33] M. A. Abas, G. Russell, and D. J. Kinniment, "Design of sub-10-picoseconds on-chip time measurement circuit," *Design, Automation and Test in Europe Conference and Exhibition, Vols 1 and 2, Proceedings*, pp. 804-809, 2004.

- [34] N. Minas, D. Kinniment, K. Heron, and G. Russell, "A high resolution flash time-to-digital converter taking into account process variability," *Async 2007:* 13th IEEE International Symposium on Asynchronous Circuits and Systems, pp. 163-172, 2007.

- [35] L. Minjae and A. A. Abidi, "A 9 b, 1.25 ps Resolution Coarse-Fine Time-to-Digital Converter in 90 nm CMOS that Amplifies a Time Residue," *Solid-State Circuits, IEEE Journal of*, vol. 43, pp. 769-777, 2008.

- [36] A. N. M. Alahmadi, G. Russell, and A. Yakovlev, "Time difference amplifier design with improved performance parameters," *Electronics Letters*, vol. 48, pp. 562-563, May 10 2012.

- [37] A. N. M. Alahmadi, G. Russell, and A. Yakovlev, "Reconfigurable time interval measurement circuit incorporating a programmable gain time difference amplifier," in *Design and Diagnostics of Electronic Circuits & Systems* (DDECS), 2012 IEEE 15th International Symposium on, 2012, pp. 366-371.

- [37] C. S. Amin, N. Menezes, K. Killpack, F. Dartu, U. Choudhury, N. Hakim, and Y. I. Ismail, "Statistical static timing analysis: How simple can we get?," *42nd Design Automation Conference, Proceedings* 2005, pp. 652-657, 2005.

# Chapter 2

# **Time Measurement Techniques**

#### 2.1 Introduction

Time measurement has become an area of interest for researchers as it can be used in several applications such as distance measurement, particle physics, astronomy, nuclear physics and dynamic testing of ICs. A wide range of methods have been proposed for time measurement in order to improve the resolution, dynamic range, and reduce area overhead, complexity of the calibration procedure and measurement time [1-8]. However, defining each of these parameters depends on the requirements of the wide range of time measurement applications. Figure 2.1 classifies the range of time measurement techniques based on their methodology.

Figure 2.1: Taxonomy of time interval measurement techniques [9].

In this chapter a review is undertaken of examples of each of the cited generic time measurement techniques shown in Figure 2.1, highlighting the advantages and disadvantages of each. The subsequent sections of this Chapter comprise a description of the counter based method in section 2.2, followed in section 2.3 with an outline description of the time to voltage conversion technique. In section 2.4, the signal condition technique is discussed, followed, in section 2.5, by the description of the delay line method. The Vernier method and the combination of coarse and fine delay techniques are described in sections 2.6 and 2.7 respectively. A description of the time measurement in Field Programmable Gate Arrays (FPGA) is given in section 2.8, followed by a summary of the attributes of the techniques in section 2.9.

#### 2.2 Counter Based Method [10, 11]

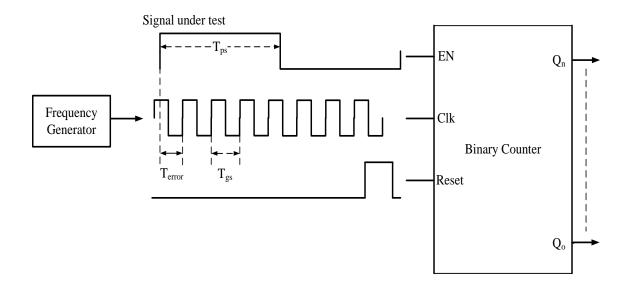

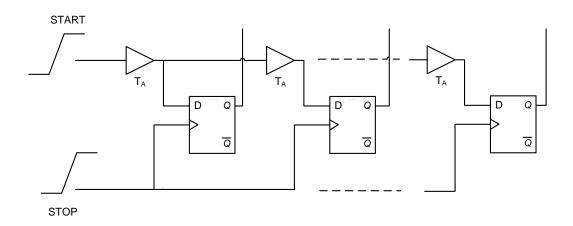

The counter based method is a basic and simple technique used to measure time intervals, it comprises two main parts, a counter and a frequency generator. It can be seen from Figure 2.2 that the generated frequency  $F_{gs}$  (or  $1/T_{gs}$ ) must be much larger than the frequency of the signal under test  $(1/T_{ps})$  as the resolution of the measurement is equal to  $T_{gs}$ . The rising edge of the signal to be measured is used to enable the counter, which is subsequently disabled by the falling edge. The measurement result is achieved by multiplying the value stored in the counter  $(N_m)$  by  $T_{gs}$ , that is  $T_{ps}$  (measured) =  $N_m \cdot T_{gs}$ . The magnitude of the error, as shown in Figure 2.2, depends upon the relative phase different between the rising edge of  $T_{ps}$  and  $T_{gs}$ . This error can be reduced provided that  $T_{gs} << T_{ps}$ . However, if  $T_{ps}$  is quite short, to ensure an acceptable measurement accuracy a high performance counter would be required. Alternatively, the effect of the error ( $T_{error}$ ) can be minimised by repeating the measurement several times whilst  $T_{ps}$  is calculated as the average result of several measurements. However, the disadvantage of averaging is the increase in the overall measurement time.

Figure 2.2: Time interval measurement using counter technique.

The main advantages of the counter technique are the simplicity of the method and the long dynamic range, although the method suffers from the low resolution unless a high frequency clock is used.

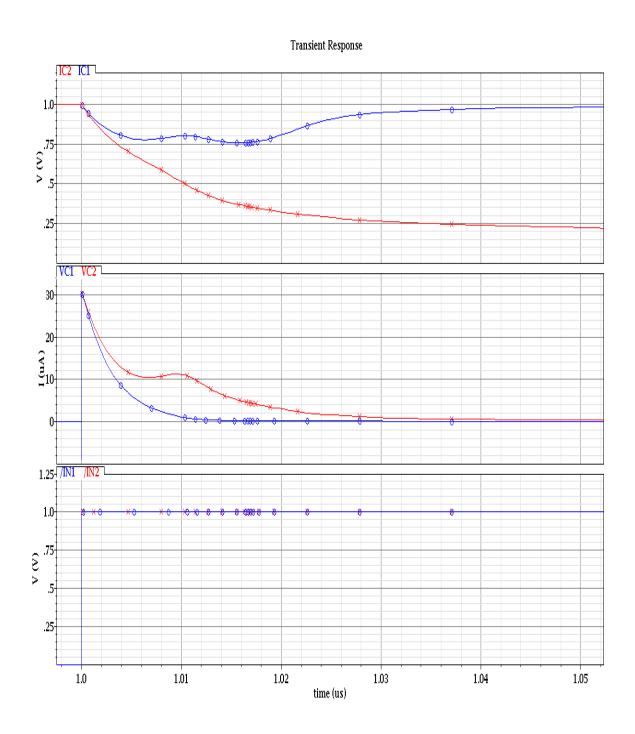

#### 2.3 Time to Voltage Conversion Technique [12-15]

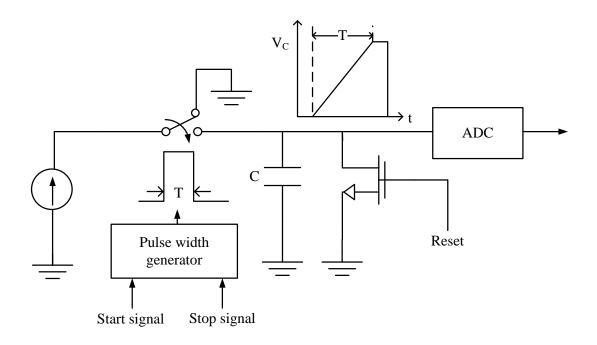

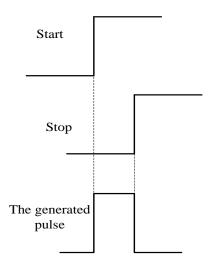

The time to voltage conversion technique is based on converting the time interval into voltage which is subsequently digitised. The main components used in this technique are a time to digital converter and an analogue to digital converter (ADC), as shown in Figure 2.3. The rising edges of the two signals whose time difference is to be measured are used, shown in Figure 2.4, as start and stop signals to the pulse width generator creating an output pulse T whose duration is equal to the temporal difference between the two input signals. This pulse switches on the current source to charge the capacitance with a constant current value (I), for the duration of the pulse T. The subsequent output voltage,  $V_C$ , given by Equation (1), is then passed to the ADC.

$$V_C = (I_o / C) \cdot T - (2.1)$$

Once the conversion is completed the capacitor is discharged and the measurement can be repeated.

Figure 2.3: Time to voltage converter circuit [14].

Figure 2.4: The generated pulse width equal to the time difference between start and stop signal.

It can be seen from Equation (1), the accuracy of the conversion is highly dependent on the ratio of the current  $I_0$  and the capacitance C which is required to be constant and stable. Therefore the accuracy is sensitive to process variation, temperature and power supply voltage, although a high resolution can be achieved by this method (1ps to 20 ps) [10]. In addition this method depends on analogue circuitry which is more sensitive to noise, temperature and power supply variation compared to the digital technique which will be discussed later.

#### 2.4 Signal Conditioning

Signal conditioning is a technique used to enhance the resolution of time measurements by stretching the input time interval. Signal conditioning techniques can be divided into those which use a pulse stretching technique [10, 16] and those which use time difference amplification [17-20]. A combination of one of these techniques and a time measurement method can improve, greatly, the resolution of the time measurement system. For example, in the counter based method, whilst the resolution is low and limited to the value of the frequency generator, as described in section 2.2, a combination of the pulse stretching method and counter method can increase the resolution to higher value [16], as will be discussed later. Both pulse stretching technique and a time difference amplification techniques are described in detail below.

#### 2.4.1 Pulse Stretching [10, 16]

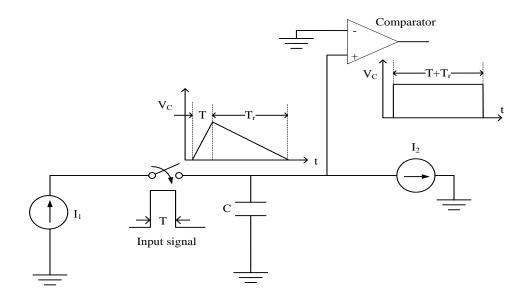

The principle of the pulse stretching method depends on stretching the input time interval using the difference between the charge and discharge time of a capacitance, as shown in Figure 2.5. The current  $I_2$  is designed to be much smaller than the current  $I_1$ . As a result, when an input signal with a pulse period, T, is applied to switch  $S_1$ , the capacitance starts charging with a time duration, T, and with a large current equal to  $(I_1-I_2)$ , where  $I_1 >> I_2$ . However, during discharge,  $S_1$  is switched off while the capacitance is discharged with a smaller current  $I_2$  resulting in a longer discharge time  $(T_r)$  greater than the charge time (T). The relationship between T and  $T_r$  is nearly linear and is given by Equation (2).

$$T_r = A \cdot T - (2.2)$$

Where A is the stretching factor and can be calculated as

$$A = (I_1 - I_2)/I_2 - (2.3)$$

Figure 2.5: Pulse stretching circuit [10].

As mentioned previously, the pulse stretching method can be combined with the counter method to achieve a high resolution time measurement system where the resolution is calculated as  $T_g/(A+1)$  [10]. However, this method suffers from long time conversion, as the capacitor (C) is required to be charged and discharged for each single measurement, which limits the technique to be used for a low frequency or single shot applications.

#### 2.4.2 Time Difference Amplifier

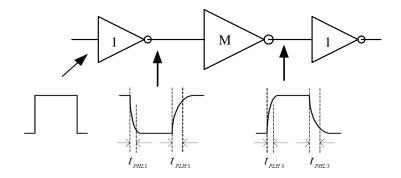

A time difference amplifier is another way to increase the resolution of the time measurement. The principle of the time difference amplifier, which was first proposed in [17], is to amplify the time difference between the two input signals ( $\Delta T_{input}$ ) with a constant gain (G), as shown in Figure 2.6. Time difference amplification can be achieved using either analogue or digital circuitry.

Figure 2.6: The concept of time amplifier.

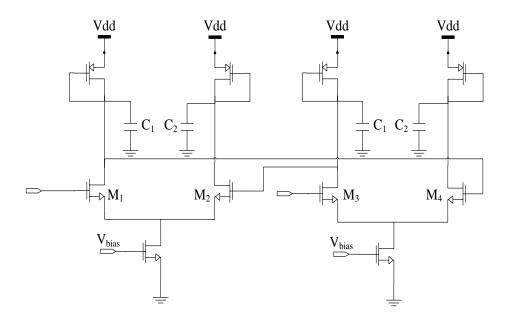

a) Time difference amplifier using analogue circuitry: Two time difference amplifiers have been proposed which use analogue circuitry [18, 20]. The first time difference amplifier is designed using two cross-coupled differential pairs, as shown in Figure 2.7. The amplification in this technique is based on the charging and discharging between C<sub>1</sub> and  $C_2$  in each differential pair. The time difference between the outputs ( $\Delta T_{out}$ ) of the coupled differential circuits is proportional to the time input difference ( $\Delta T_{input}$ ). The main advantage of this design is the higher gain which reaches 180 with a wide range of the input time differences, about several hundred picoseconds. However, this design requires a bias voltage to be set to a specific constant value in order to create the amplification between the two cross-coupled differential pairs. Therefore any variation in the value of the bias voltage affects the circuit stability and performance. In addition, as the design is analogue, it is highly sensitive to noise, variations in temperature, process and power supply voltage. However, this technique will not be discussed further, as this design is an analogue technique which is more sensitive to noise, temperature and power supply variation compared to the digital technique, thus this thesis is focused on the digital time difference amplification techniques.

Figure 2.7: Time difference amplifier using analog circuit [20].

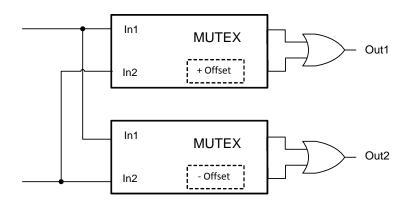

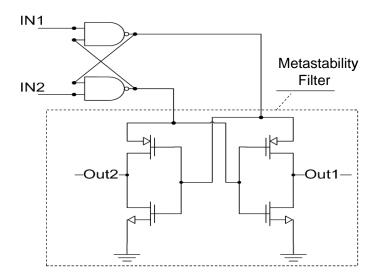

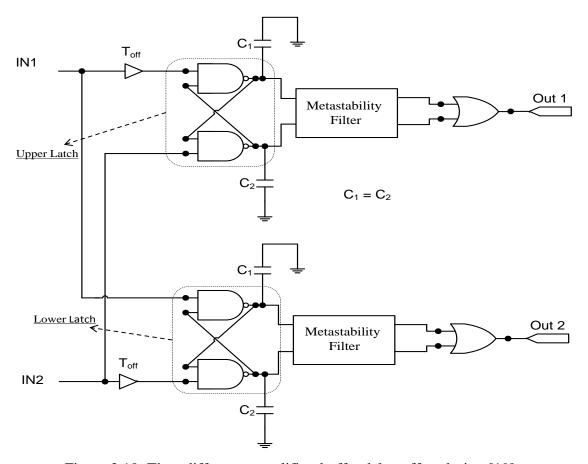

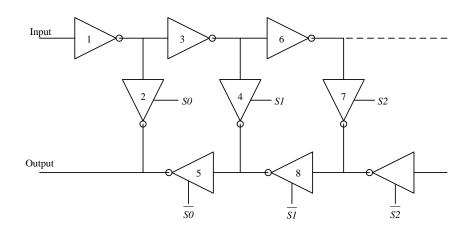

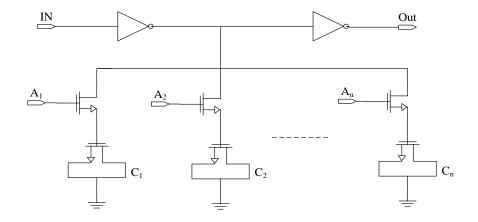

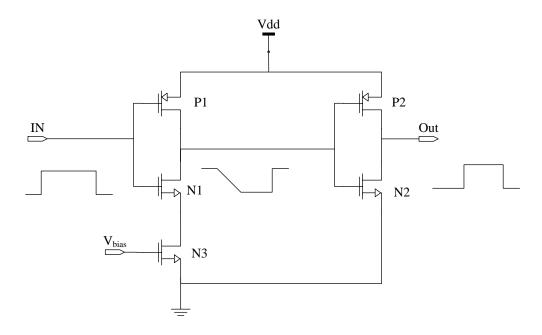

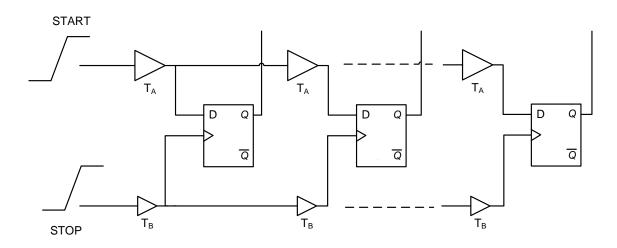

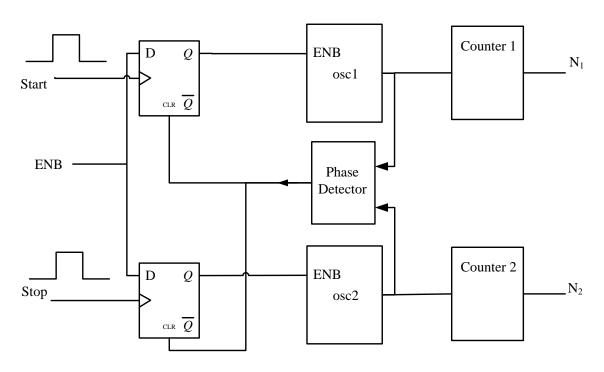

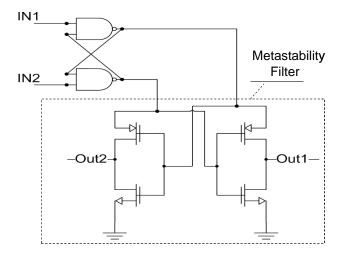

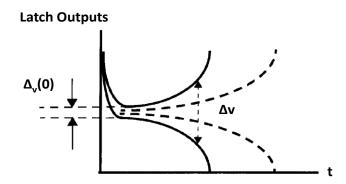

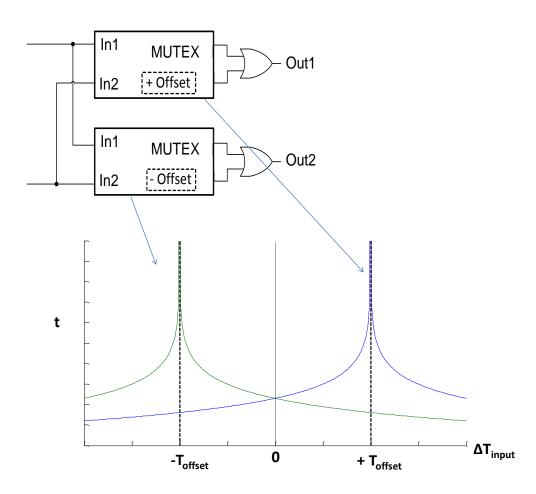

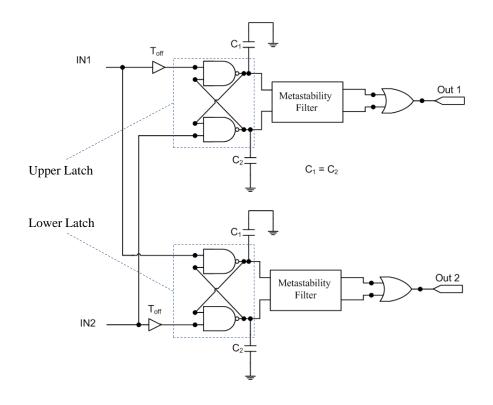

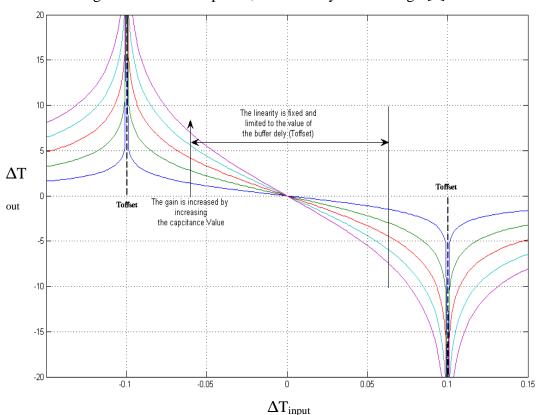

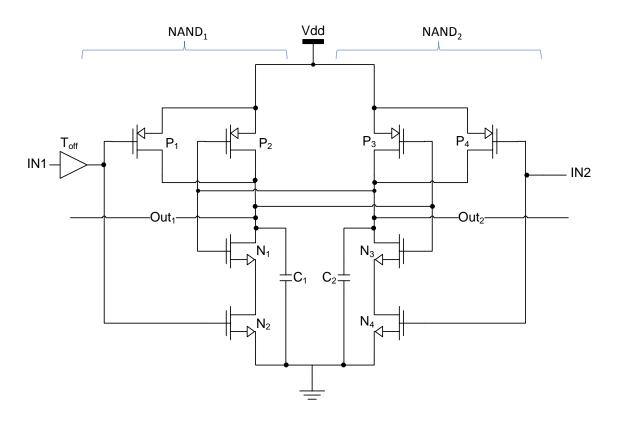

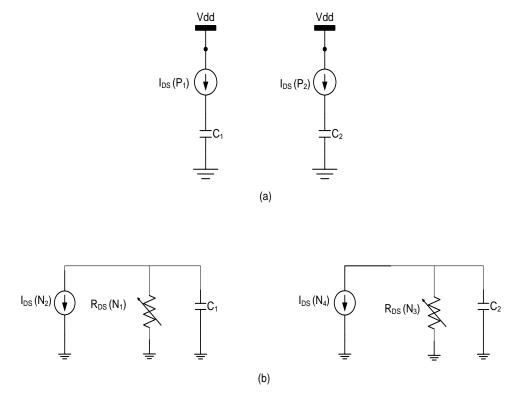

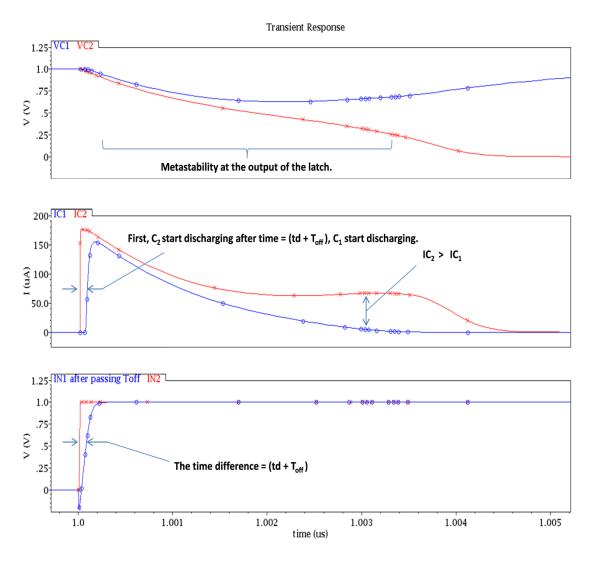

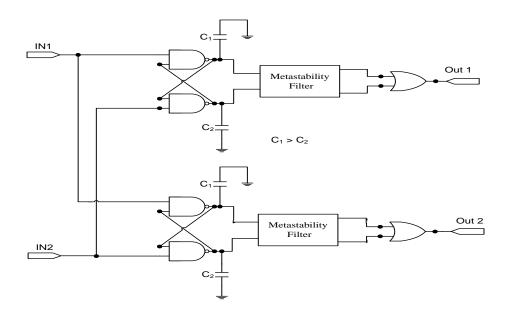

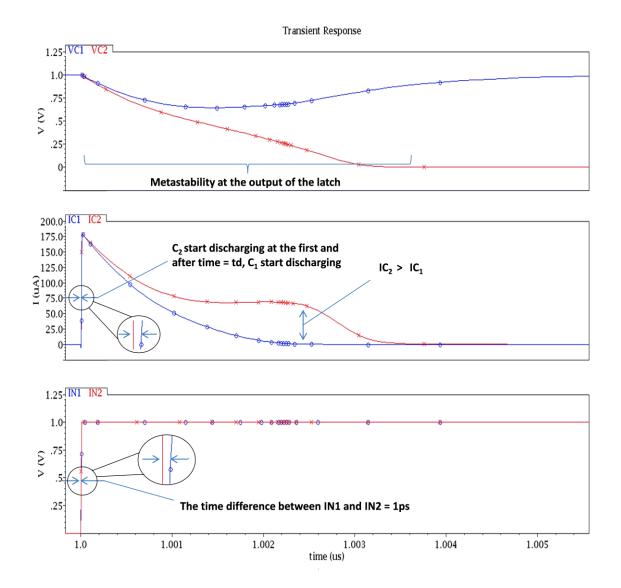

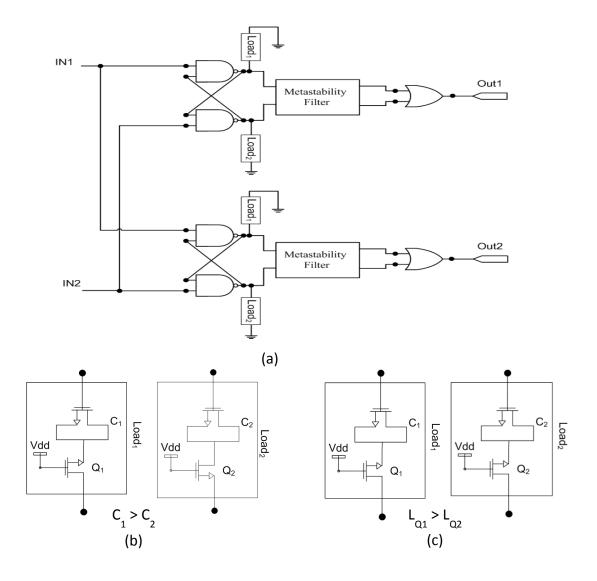

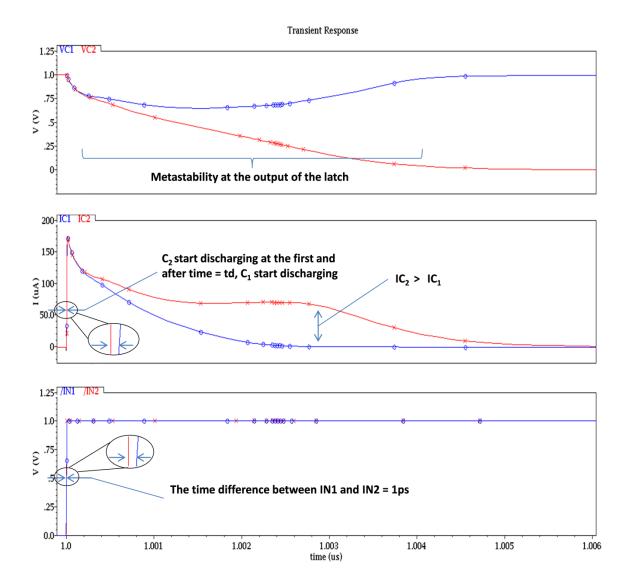

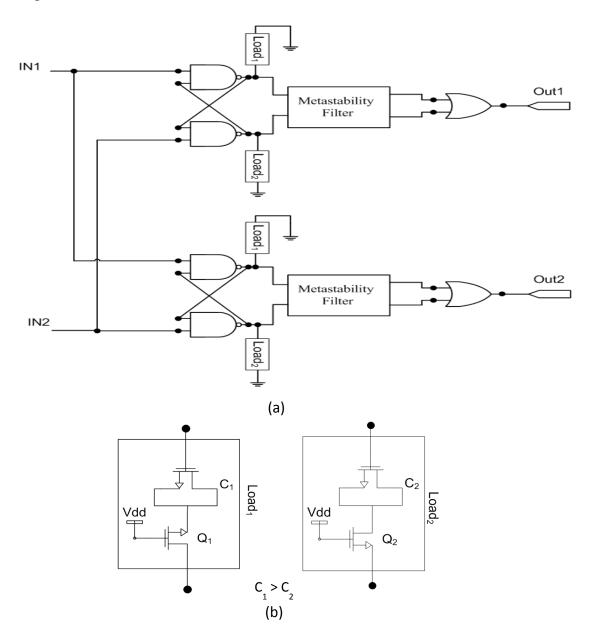

**b) All Digital Time Difference Amplifier:** The time difference amplifier can also be implemented using digital circuitry [17] comprising two MUTEX circuits, as shown in Figure 2.8. A MUTEX consists of an S-R latch followed by a metastability filter circuit consisting of two inverters, whose inputs also act as power sources, as shown in Figure

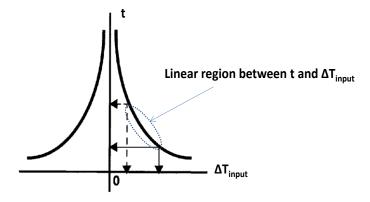

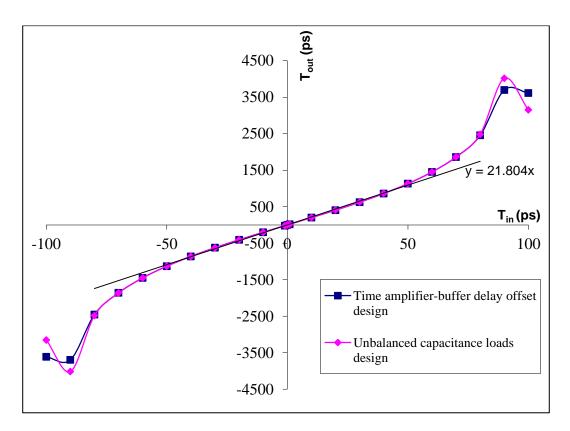

2.9. A MUTEX is normally used to determine which of the two inputs arrives first. However, when the inputs of a MUTEX arrive with a very small time difference, the output goes into a metastable state, a condition which is normally avoided. This metastable condition produces a delay dependent upon the time difference between the input signals. Based on this behaviour a time difference amplifier can be designed by using two MUTEX circuits with opposite offsets, as shown in Figure 2.8. The offset is created by increasing or decreasing the transistors size of the NAND gates. The equation for amplification gain is given in Equation (4).

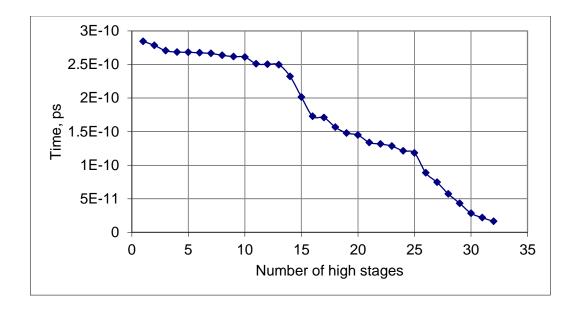

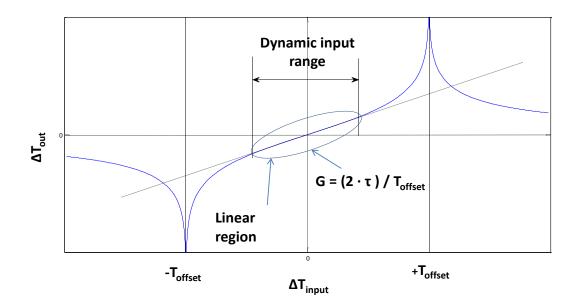

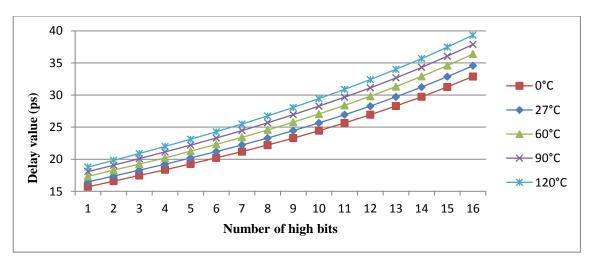

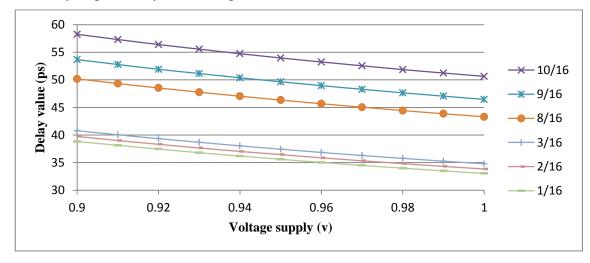

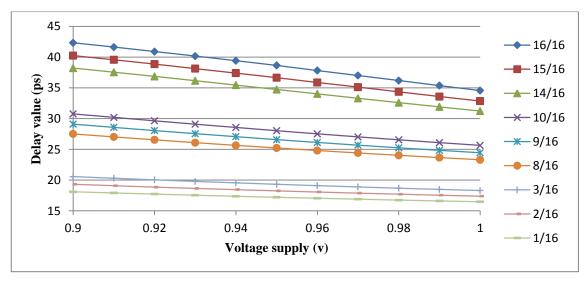

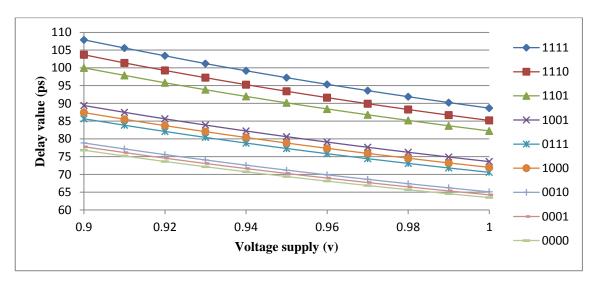

$$\Delta T_{out} / \Delta T_{input} = (2 \cdot \tau) / T_{offset} - (2.4)$$