UNIVERSITY OF NEWCASTLE UPON TYNE DEPARTMENT OF COMPUTING SCIENCE

PhD Thesis

## Run-time Support for Parallel Object-Oriented Computing

The NIP Lazy Task Creation Technique and the NIP Object-based Software Distributed Shared Memory

> by Savas Parastatidis

Supervisor Dr. Paul Watson

September 2000

## ABSTRACT

Advances in hardware technologies combined with decreased costs have started a trend towards massively parallel architectures that utilise commodity components. It is thought unreasonable to expect software developers to manage the high degree of parallelism that is made available by these architectures. This thesis argues that a new programming model is essential for the development of parallel applications and presents a model which embraces the notions of object-orientation and implicit identification of parallelism. The new model allows software engineers to concentrate on development issues, using the object-oriented paradigm, whilst being freed from the burden of explicitly managing parallel activity.

To support the programming model, the semantics of an execution model are defined and implemented as part of a run-time support system for object-oriented parallel applications. Details of the novel techniques from the run-time system, in the areas of lazy task creation and object-based, distributed shared memory, are presented.

The tasklet construct for representing potentially parallel computation is introduced and further developed by this thesis. Three caching techniques that take advantage of memory access patterns exhibited in object-oriented applications are explored. Finally, the performance characteristics of the introduced run-time techniques are analysed through a number of benchmark applications.

## **ACKNOWLEDGEMENTS**

I would like to start by expressing my gratitude to my supervisor, Dr. Paul Watson. I consider myself extremely fortuned to have had Dr. Watson as my guide in this research work. He has endured numerous long sessions of discussions without ever showing signs of tiredness and his insights were always accurate. He has been a great source of inspiration and support throughout. I do not think I would have ever been able to bring this thesis to completion if it was not for his paradigmatic supervision. Thank you Paul.

Next, I would like to thank the other two members of my thesis committee Prof. Pete Lee and Dr. Chris Phillips for their valuable input to my research work. Special thanks to Prof. Lee because, in his capacity as leader for the HiPPO research project, he has been extremely patient with me whilst trying to complete this thesis.

My friend, fellow PhD student, and officemate Jim Webber deserves a special mention. His company and support through the years have made this work possible. He has contributed greatly to my integration into British society, culture, and to the more colloquial aspects of the language. I consider myself tremendously lucky to have met him and privileged to be able to call him 'mate.'

To other friends: Kostas Amoiridis, Fefi Axiotidou, Grigoris Lampakis, Panagiotis Karambatzakis, Dr. Lindsay Marshall, Baggelis Skarlatos, Bassilis Theodoridis, Stamatis Xouxos, Colette Wabnitz, I offer my sincerest thanks.

Finally, I would like to dedicate this thesis to my family: my mother Fotini, my father Giorgos, and my brother Filippos. If it were not for their continuing encouragement and support throughout the years, I would not have managed to complete my academic studies and this research work. Tous  $\varepsilon$   $\varepsilon$   $\chi$   $\alpha$   $\rho$   $\tau$   $\delta$   $\lambda$   $\delta$ .

# TABLE OF CONTENTS

| Abstract                                                        | i    |

|-----------------------------------------------------------------|------|

| Acknowledgements                                                | iii  |

| Table of Contents                                               | v    |

| Table of Figures                                                | ix   |

| Table of Tables                                                 | xiii |

| Table of Codes                                                  | XV   |

| 1. Introduction                                                 | 1    |

| 1.1. High-Performance Computing                                 | 2    |

| 1.1.1. Application Area Trend                                   | 2    |

| 1.1.2. Architectural Trends                                     | 4    |

| 1.1.3. Trend Synopsis                                           | 6    |

| 1.2. Parallelism                                                | 6    |

| 1.2.1. Definition                                               | 7    |

| 1.2.2. Hardware Support                                         | 7    |

| 1.2.3. Programming and Execution Models                         | 8    |

| 1.3. Possible Future Directions for Parallel Computing          | 9    |

| 1.3.1. Microprocessor Technology                                | 9    |

| 1.3.2. Architectures                                            | 10   |

| 1.3.3. Software                                                 | 10   |

| 1.4. Research Goals                                             | 11   |

| 1.4.1. Motivation                                               | 11   |

| 1.4.2. Contributions to Knowledge                               | 11   |

| 1.5. Remaining Thesis Structure                                 | 12   |

| 2. Parallelism and the NIP Programming and NIP Execution Models | 14   |

| 2.1. Models and Abstraction                                     | 15   |

| 2.1.1. Programming Model                                        | 15   |

| 2.1.2. Execution Model                                          | 15   |

| 2.1.3. Computational Model                                      | 16   |

| 2.1.4. Lack of Abstraction Causes Confusion                     | 16   |

| 2.1.5. Towards Two New Abstract Models                          | 17   |

| 2.1.6. Layered Approach to the Parallel Computing Paradigm      | 17   |

| 2.2. Hardware                                                | 18 |

|--------------------------------------------------------------|----|

| 2.3. Operating Systems                                       | 19 |

| 2.4. Run-time System                                         | 20 |

| 2.5. Programming Language                                    | 20 |

| 2.5.1. Auto-parallelisation Compilers                        | 21 |

| 2.5.2. Software Libraries                                    | 22 |

| 2.5.3. Language Extensions/Integration                       | 22 |

| 2.5.4. Implicit Parallelism                                  | 23 |

| 2.5.5. Transition Towards Implicit Programming Languages     | 23 |

| 2.6. Common Programming Models                               | 24 |

| 2.6.1. Serial                                                | 25 |

| 2.6.2. Message Passing                                       | 26 |

| 2.6.3. Shared Memory                                         | 27 |

| 2.6.4. Functional                                            | 29 |

| 2.7. Common Execution Models                                 | 30 |

| 2.7.1. Message Passing and Shared Memory                     | 30 |

| 2.7.2. Dataflow                                              | 31 |

| 2.7.3. Functional                                            | 31 |

| 2.8. NIP Programming Model                                   | 32 |

| 2.9. NIP Execution Model                                     | 33 |

| 2.9.1. Model Requirements                                    | 34 |

| 2.9.2. Run-time Environment                                  | 35 |

| 2.9.3. Run-time Environment on Diverse Architectures         | 35 |

| 2.9.9. Run une Environment on Diverse Mentectures            | 55 |

| 3. NIP Lazy Task Creation                                    | 37 |

| 3.1. The Granularity Problem                                 | 38 |

| 3.1.1. The 'Expert' Programmer Solution                      | 38 |

| 3.1.2. The 'Clever' Compiler Approach                        | 38 |

| 3.1.3. A Run-time Solution                                   | 39 |

| 3.2. Lazy Task Creation                                      | 39 |

| 3.2.1. Concept                                               | 40 |

| 3.2.2. Implementation                                        | 41 |

| 3.2.3. Weaknesses                                            | 41 |

| 3.3. Lazy Threads                                            | 43 |

| 3.3.1. Concept                                               | 43 |

| 3.3.2. Implementation                                        | 44 |

| 3.3.3. Weaknesses                                            | 45 |

| 3.4. Other Run-time Techniques                               | 45 |

| 3.4.1. WorkCrews                                             | 46 |

| 3.4.2. LeapFrogging                                          | 46 |

| 3.5. On Potentially Parallel Calls and their Representations | 46 |

| 3.5.1. The Problem with Iterative Computations               | 47 |

| 3.5.2. A Solution                                            | 48 |

| 3.6. NIP Lazy Task Creation                                  | 48 |

| 3.6.1. The Tasklet                                           | 48 |

| 3.6.2. Tasklet Internals and the Tasklet Availability Queue  | 50 |

| 3.6.3. Use of Tasklets                                       | 52 |

| 3.6.4. Function Calls                                        | 52 |

| 3.6.5. Iterative Computations                                | 53 |

| 3.6.6. Recursive Computations                                | 58 |

| 3.6.7. Implementation                                        | 60 |

| <b>r</b>                                                     | 00 |

| 3.7. Discussion                                          | 61 |

|----------------------------------------------------------|----|

| 4. NIP Software-Based Distributed Shared Memory          | 63 |

| 4.1. The Shared Memory Abstraction                       | 64 |

| 4.2. The Design Considerations for DSM Systems           | 65 |

| 4.2.1. Structure, Sharing Unit, and Granularity          | 65 |

| 4.2.2. Memory Consistency                                | 66 |

| 4.2.3. Data Access                                       | 67 |

| 4.2.4. Implementation                                    | 68 |

| 4.2.5. Heterogeneity                                     | 68 |

| 4.2.6. Efficiency                                        | 68 |

| 4.2.7. Discussion                                        | 69 |

| 4.3. Existing Relaxed Memory Consistency Models          | 69 |

| 4.3.1. Release and Lazy Release Consistency              | 70 |

| 4.3.2. Entry Consistency                                 | 71 |

| 4.4. Existing DSM Systems                                | 72 |

| 4.4.1. Influential Systems                               | 72 |

| 4.4.2. Midway                                            | 72 |

| 4.5. NIPDSM Design Considerations                        | 75 |

| 4.5.1. Design Requirements                               | 75 |

| 4.5.2. Design Choices                                    | 76 |

| 4.5.3. NIP Entry Consistency                             | 77 |

| 4.5.4. Coupling the Synchronisation and Cache Management | 79 |

| 4.6. NIPDSM Implementation                               | 81 |

| 4.6.1. Node Managers, Read and Write Proxies             | 81 |

| 4.6.2. Object Representation and NIPDSM Reference        | 82 |

| 4.6.3. NIPDSM Virtual Object Table                       | 83 |

| 4.7. Introducing Caching Techniques in NIPDSM            | 85 |

| 4.7.1. Temporal Locality                                 | 85 |

| 4.7.2. Spatial Locality                                  | 85 |

| 4.7.3. Dynamic Data Structures and Access Patterns       | 86 |

| 4.7.4. Recurring Access to Objects                       | 87 |

| 4.8. Implementation of the NIPDSM Caching Optimisations  | 88 |

| 4.8.1. Cache Block                                       | 88 |

| 4.8.2. Object Grouping Based on Location                 | 88 |

| 4.8.3. Object Grouping Based on Associations             | 89 |

| 4.8.4. Object Grouping Based on Access History           | 90 |

| 4.9. Discussion                                          | 92 |

| 4.9.1. Why Objects                                       | 92 |

| 4.9.2. Consistency Semantics                             | 92 |

| 4.9.3. Caching                                           | 92 |

| 4.9.4. Midway and NIPDSM                                 | 93 |

| 5. The NIP Run-time System                               | 95 |

| 5.1. The NIP Execution Model as a Run-time System        | 96 |

| 5.2. Design                                              | 97 |

| 5.2.1. Intended Use                                      | 97 |

| 5.2.2. Overall Structure and the NIP Node                | 97 |

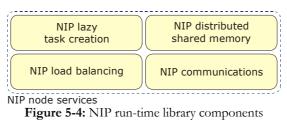

| 5.2.3. NIP Node Service                                  | 98 |

| 5.3. Implementation Overview                             | 98 |

| 5.3.1. Service Task and Workers                          | 98 |

| 5.3.2. The Portability Issue               | 99  |

|--------------------------------------------|-----|

| 5.4. NIP Communications                    | 99  |

| 5.4.1. Design                              | 99  |

| 5.4.2. Communication Between NIP Nodes     | 99  |

| 5.4.3. Implementation                      | 100 |

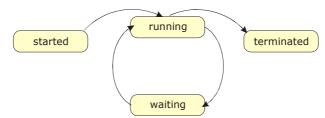

| 5.5. NIP Load Balancing                    | 101 |

| 5.5.1. Design                              | 101 |

| 5.5.2. Tasks and the Load of NIP Nodes     | 102 |

| 5.5.3. Implementation                      | 103 |

| 5.6. NIP Lazy Task Creation                | 104 |

| 5.6.1. The NIP Tasklet Interface           | 104 |

| 5.6.2. The Tasklet Availability Queue      | 106 |

| 5.6.3. The NIP Tasklet Library             | 106 |

| 5.7. NIP Distributed Shared Memory         | 107 |

| 5.7.1. Allocation of Objects in the NIPDSM | 107 |

| 5.7.2. Efficiency                          | 107 |

| 5.7.3. Object Access                       | 108 |

| 5.8. Discussion                            | 109 |

|                                            |     |

| 6. Performance Evaluation                                    | 111 |

|--------------------------------------------------------------|-----|

| 6.1. Introduction                                            | 112 |

| 6.1.1. Evaluation Objectives                                 | 112 |

| 6.1.2. Real-System Execution vs. Simulation                  | 112 |

| 6.2. Experimental Set-up                                     | 113 |

| 6.2.1. Hardware Environment                                  | 113 |

| 6.2.2. Software Environment                                  | 114 |

| 6.3. Cost of Primitive Operations                            | 114 |

| 6.3.1. Operating System Primitive Operations                 | 114 |

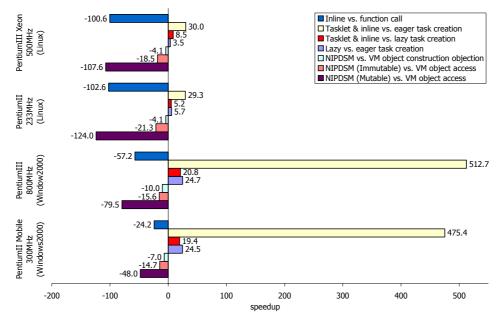

| 6.3.2. NIP Run-time Primitive Operations                     | 115 |

| 6.4. NIPLTC Micro-Benchmarks                                 | 118 |

| 6.4.1. Iterative Tasklet – Parallel Map – APP                | 118 |

| 6.4.2. Iterative Tasklet – Parallel Map – SMP                | 124 |

| 6.4.3. Recursive Tasklet – Grain                             | 125 |

| 6.5. NIPDSM Micro-Benchmarks                                 | 127 |

| 6.5.1. Object Grouping Based on Location – Parallel Map      | 129 |

| 6.5.2. Object Grouping Based on Associations – TreeSum       | 131 |

| 6.5.3. Object Grouping Based on Access History – Tree Search | 134 |

| 6.6. Applications                                            | 137 |

| 6.6.1. Matrix Multiply                                       | 137 |

| 6.6.2. Barnes-Hut                                            | 141 |

| 6.6.3. Travelling Salesperson Problem                        | 148 |

| 6.7. Discussion                                              | 150 |

| 7. Conclusions and Discussion                                | 153 |

| 7.1. Object-Oriented Parallel Computing                      | 154 |

| 7.2. Run-time Support                                        | 154 |

| 7.3. Potential NIPDSM Enhancements                           | 156 |

| 7.4. Future Research Directions                              | 157 |

| 7.5. Concluding Remarks                                      | 158 |

| References                                                   | 159 |

## References

## TABLE OF FIGURES

| Figure 1-1: Application area evolution of the top 500 high-performance computers based on data from<br>"TOP500 list' (TOP500 List 2000; TOP500 List Authors 2000) |       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Figure 1-2: Evolution of the total computational power (in Gflop/s) per application area of the top 500                                                           |       |

| high-performance computers based on data from the 'TOP500 list' (TOP500 List 2000; TOP500                                                                         |       |

| Authors 2000)                                                                                                                                                     |       |

| Figure 1-3: Evolution of the computational power (in Gflop/s) of the fastest computer for each applica                                                            |       |

| area of the top 500 high-performance computers based on data from the 'TOP500 list' (TOP500                                                                       |       |

| 2000; TOP500 List Authors 2000)                                                                                                                                   |       |

| Figure 1-4: Evolution of hardware architecture of the top 500 high-performance computers based on da                                                              |       |

| from the 'TOP500 list' (TOP500 List 2000; TOP500 List Authors 2000)                                                                                               |       |

| Figure 1-5: Evolution of the computational power (in Gflop/s) of the fastest computer for each hardwa                                                             |       |

| architecture of the top 500 high-performance computers based on data from the TOP500 list'                                                                        |       |

| (TOP500 List 2000; TOP500 List Authors 2000)                                                                                                                      | 5     |

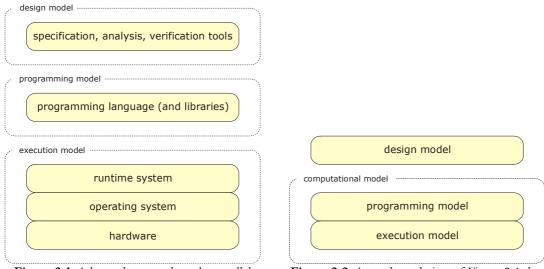

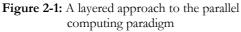

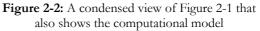

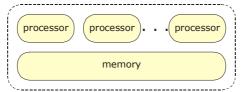

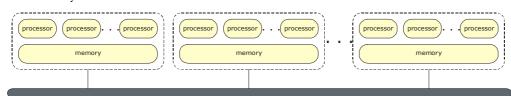

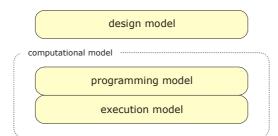

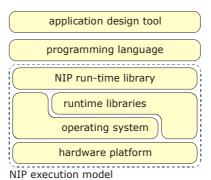

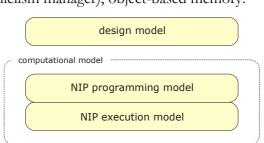

| Figure 2-1: A layered approach to the parallel computing paradigm                                                                                                 | 17    |

| Figure 2-2: A condensed view of Figure 2-1 that also shows the computational model                                                                                |       |

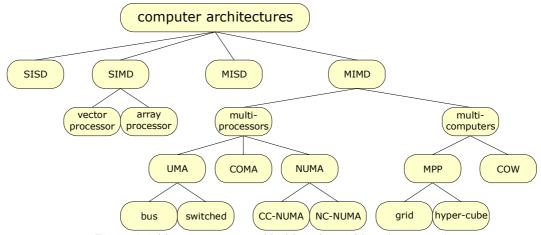

| Figure 2-3: Taxonomy proposed by Tanenbaum (Tanenbaum 1999)                                                                                                       |       |

| Figure 2-4: The conceptualisation of a computer system by the serial programming model                                                                            |       |

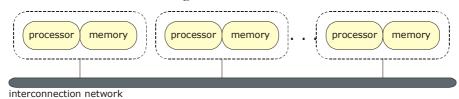

| Figure 2-5: The conceptualisation of a computer system by the message-passing programming model                                                                   |       |

| Figure 2-6: The conceptualisation of a computer system by the shared-memory programming model                                                                     | 27    |

| Figure 2-7: The conceptualisation of a shared-memory/message-passing computer system                                                                              | 29    |

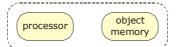

| Figure 2-8: The conceptualisation of a computer system by the NIP programming model                                                                               | 32    |

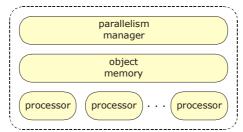

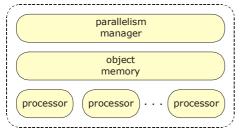

| Figure 2-9: The major components of the abstract machine as suggested by the NIP execution model                                                                  |       |

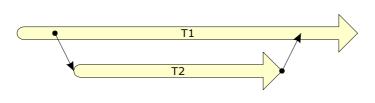

| Figure 3-1: The parallel call pattern                                                                                                                             |       |

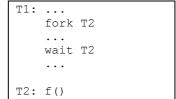

| Figure 3-2: The parallel loop pattern                                                                                                                             | 55    |

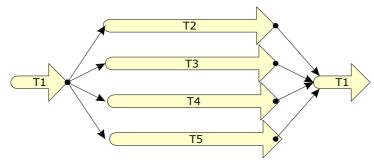

| Figure 3-3: The parallel recursion pattern                                                                                                                        | 58    |

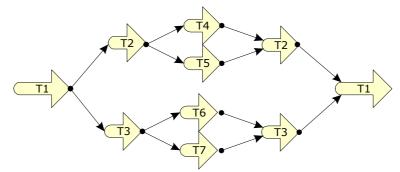

| Figure 3-4: Operations on the queue maintained by recursive tasklets                                                                                              | 60    |

| Figure 4-1: The NIPDSM VOT table                                                                                                                                  |       |

| Figure 4-2: Caching based on spatial locality information                                                                                                         |       |

| Figure 4-3: Object representations and their list of NIPDSM references of the associated objects                                                                  |       |

| Figure 4-4: Caching based on locking history information                                                                                                          |       |

| Figure 4-5: Examples of the locking history list                                                                                                                  |       |

| Figure 5-1: The parallel computing paradigm as introduced in Chapter 2                                                                                            |       |

| Figure 5-2: The different layers that are hidden by the NIP run-time library, which is an implementation                                                          |       |

| the NIP execution model semantics                                                                                                                                 |       |

| Figure 5-3: Intended use of the NIP run-time library                                                                                                              |       |

| Figure 5-4: NIP run-time library components                                                                                                                       | 98    |

| Figure 5-5: The four task states as considered by the NIP load-balancing service                                                                                  | . 102 |

| Figure 6-1: The speedup and slowdown of NIP primitive operations over the corresponding operating                                                                 |       |

| system operations on four different configurations                                                                                                                |       |

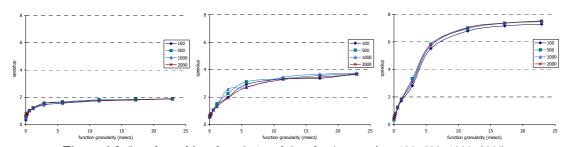

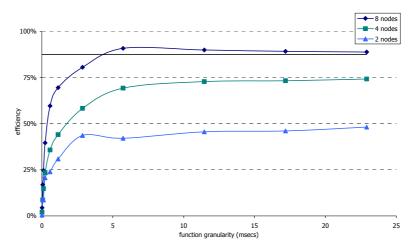

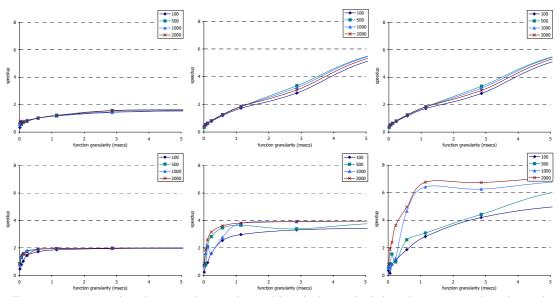

| Figure 6-2: Speedup achieved on 2, 4, and 8 nodes (vector size: 100, 500, 1000, 2000)                                                                             |       |

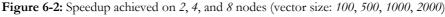

| Figure 6-3: Efficiency achieved on 2, 4, and 8 nodes (vector size: 2000)                                                                                          |       |

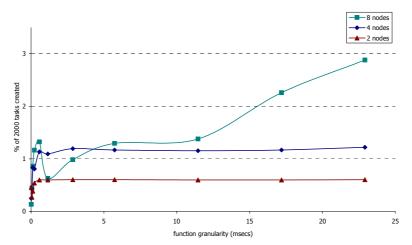

| Figure 6-4: % of tasks created out of 2,000 possible for different function granularities and for different                                                       |       |

| number of nodes used (non-optimised iterative tasklet)                                                                                                            | . 120 |

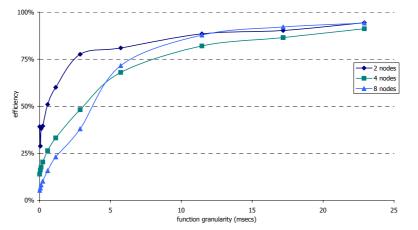

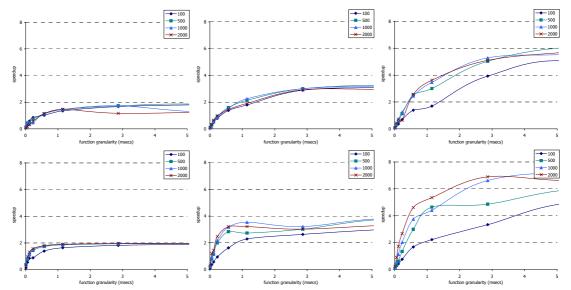

| Figure 6-5: Comparison between the speedups achieved when a single iteration (top row) is stolen and what a group of iterations (bottom row) is stolen, for 2, 4, and 8 nodes and for fine granularities of the function (vector size: 100, 500, 1000, 2000)                         |             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Figure 6-6: % of tasks created out of 2,000 possible for different function granularities and for different                                                                                                                                                                          |             |

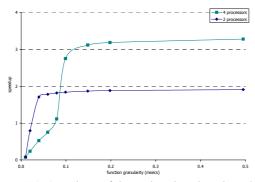

| number of nodes used (optimised iterative tasklet)<br>Figure 6-7: Speedups of the parallel map micro-benchmark on the 4-way SMP for the original (top row) a<br>grouping-capable (bottom row) iterative tasklet (2 and 4 processors, vector size: 100, 500, 1000, 20                 | and<br>100) |

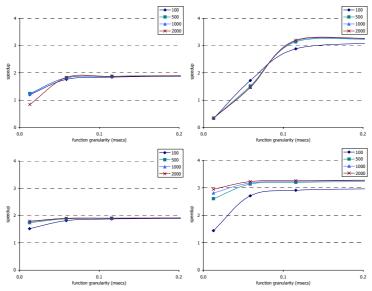

| Figure 6-8: Speedups of the grain micro-benchmark on the APP                                                                                                                                                                                                                         | 127         |

| Figure 6-9: Speedups of the grain micro-benchmark on the SMP                                                                                                                                                                                                                         | 127         |

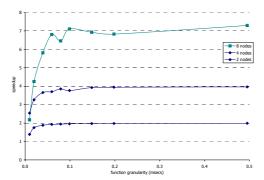

| Figure 6-10: Comparison between the speedups achieved when a caching technique is not used (top row) and when a object grouping based on location (bottom row) is used (number of nodes: 2, 4, 8; vect size: 100, 500, 1000, 2000)                                                   | tor         |

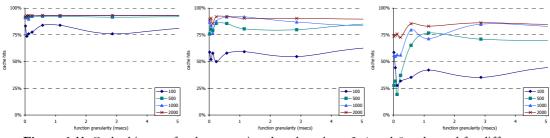

| Figure 6-11: Cache-hit rates for the map micro-benchmark on 2, 4, and 8 nodes and for different granularities of the function (vector size: 100, 500, 1000, 2000)                                                                                                                    |             |

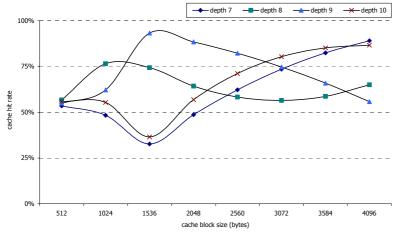

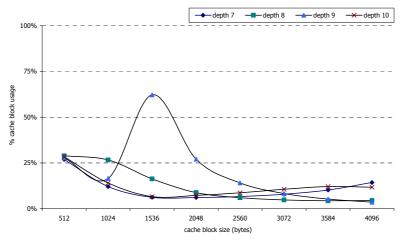

| Figure 6-12: Cache-hit rate for the treesum micro-benchmark for different tree depths and cache block si                                                                                                                                                                             | izes        |

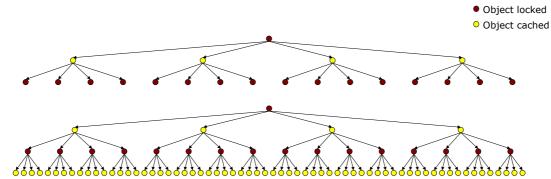

| Figure 6-13: Example of object grouping based on relations and the association between the tree-depth a the number of cache hits                                                                                                                                                     | ınd<br>132  |

| Figure 6-14: Cache block usage for the treesum benchmark                                                                                                                                                                                                                             |             |

| Figure 6-15: Object associations in order to improve the cache-hit rate                                                                                                                                                                                                              | 133         |

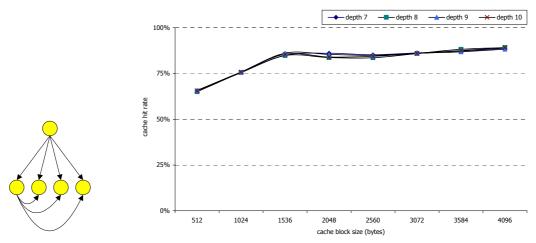

| Figure 6-16: Cache-hit rate for the optimised treesum micro-benchmark for different tree depths and cac<br>block sizes                                                                                                                                                               | 133         |

| Figure 6-17: An example of a list data structure and the associations between nodes                                                                                                                                                                                                  | 134         |

| Figure 6-18: Cache-hit rate for the list-iteration micro-benchmark (number of elements in the list: <i>1,000</i> , <i>5,000</i> , <i>10,000</i> , <i>20,000</i> )                                                                                                                    |             |

| Figure 6-19: Example of locking operations in the tree search micro-benchmark                                                                                                                                                                                                        | 135         |

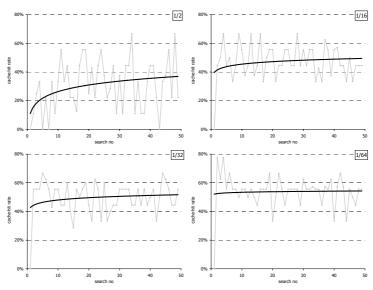

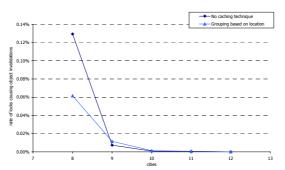

| Figure 6-20: Cache-hit rates of object grouping based on access history for the tree search micro-benchm (binary tree leaves: 1,024; random objects used as criteria for the search algorithm are selected from the ½ ½ ½ ½ ½ ½ 100 the set of leaves)                               | n           |

| Figure 6-21: Cache-hit rates of object grouping based on access history for the tree search micro-benchm                                                                                                                                                                             | ıark        |

| for the first 50 repetitions of the search algorithm (binary tree leaves: 1,024; random objects used a criteria for the search algorithm are selected from the $\frac{1}{2} \frac{1}{16} \frac{1}{32} \frac{1}{128}$ of the set of leaves)                                           | ıs          |

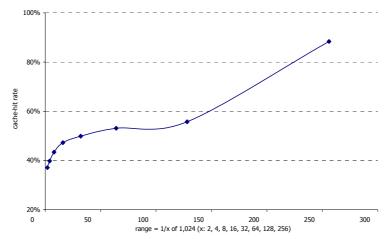

| Figure 6-22: Evolution of the cache-hit rate when the range from which the random objects are chosen becomes narrower                                                                                                                                                                | 136         |

| Figure 6-23: Series of locking operations when accessing a Matrix element                                                                                                                                                                                                            |             |

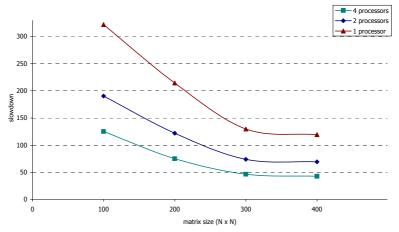

| Figure 6-24: Execution slowdowns of the matrix multiplication application on the SMP due to object locking when compared to the sequential C++ version                                                                                                                               |             |

| Figure 6-25: Execution slowdowns of the matrix multiplication application on the APP when compared t<br>the sequential C++ version (number of nodes: 2, 4, 8; vector sizes: 100, 200, 300)                                                                                           | to          |

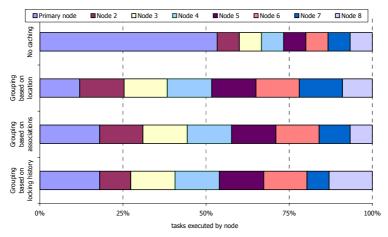

| Figure 6-26: % of tasks executed at each node (vector size: 250x250, number of nodes: 8)                                                                                                                                                                                             |             |

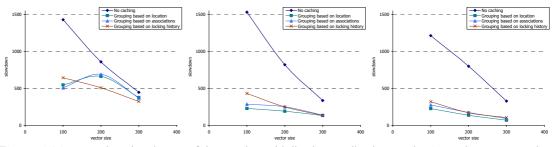

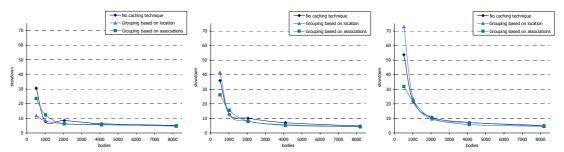

| Figure 6-27: Slowdowns of the NIP version of the Barnes-Hut application on the APP for different cach techniques (each graph represents a different number of nodes: 2, 4, 8; number of bodies: 512, 102 2048, 4096, 8192; object and cache block sizes are presented in Table 6-14) | ing<br>24,  |

| Figure 6-28: Slowdowns of the NIP version of the Barnes-Hut application on the APP for different cach techniques (each graph represents a different number of nodes: 2, 4, 8; number of bodies: 2048, 40                                                                             | ing         |

| 8192; object and cache block sizes are presented in Table 6-14)                                                                                                                                                                                                                      |             |

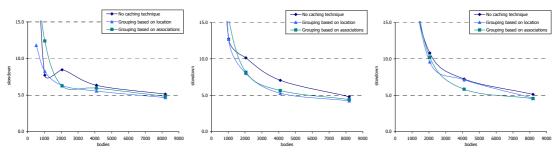

| Figure 6-29: Cache-hit rates of the NIP version of the Barnes-Hut application on the APP for different                                                                                                                                                                               |             |

| caching techniques (each graph represents a different number of nodes: 2, 4, 8; number of bodies: 512, 1024, 2048, 4096, 8192; object and cache block sizes are presented in Table 6-14)                                                                                             | 143         |

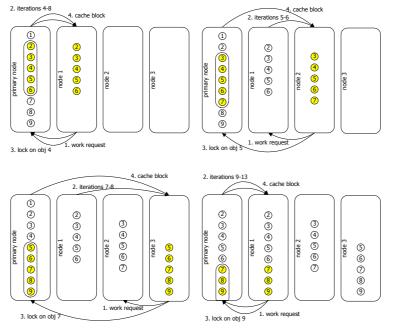

| Figure 6-30: Caching of bodies on a parallel platform of four nodes when the object grouping based on location technique is enabled                                                                                                                                                  |             |

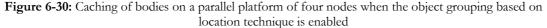

| Figure 6-31: Locks causing object invalidations from the execution of the Barnes-Hut application on 8                                                                                                                                                                                | 1 I I       |

| nodes (number of bodies: 1024, 2048, 4096, 8192; object and cache block sizes are presented in Ta<br>6-14, page 2)                                                                                                                                                                   |             |

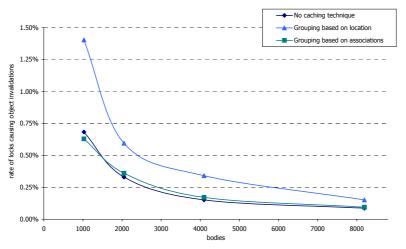

| Figure 6-32: Write locks executed on each node during the execution of the Barnes-Hut application on 8                                                                                                                                                                               |             |

| nodes (each graph represents a different number of bodies: 1024, 8192; object and cache block size                                                                                                                                                                                   | es          |

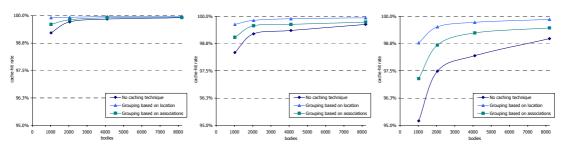

| are presented in Table 6-14, page 2)<br>Figure 6-33: Speedup improvement of the Barnes-Hut application on <i>8</i> nodes with the object grouping                                                                                                                                    | 143         |

| based on location caching technique enabled (number of bodies: 8192, 16384, 32768; 65536; object                                                                                                                                                                                     |             |

| and cache block sizes are presented in Table 6-14, page 2)                                                                                                                                                                                                                           | 14/         |

| Figure 6-34: Slowdowns of the Barnes-Hut application on the SMP workstation (number of bodies: 512,       |

|-----------------------------------------------------------------------------------------------------------|

| <i>1024</i> , <i>2048</i> , <i>4096</i> , <i>8192</i> , <i>16384</i> , <i>32768</i> )147                  |

| Figure 6-35: Speedup the NIP version of the TSP application on the APP (each graph represents a different |

| number of nodes: 2, 4, 8; number of cities: 8, 9, 10, 11, 12; object and cache block sizes are presented  |

| in Table 6-16)                                                                                            |

| Figure 6-36: Rate of invalidations in the execution of the NIP version of TSP on the APP (number of       |

| nodes: 8; number of cities: 8, 9, 10, 11, 12; object and cache block sizes are presented in Table 6-16)   |

|                                                                                                           |

| Figure 7-1: The major components of the abstract machine as suggested by the NIP execution model154       |

| Figure 7-2: The parallel computing paradigm with the NIP programming and execution models                 |

# TABLE OF TABLES

| Table 1-1: How to perform an activity faster in real life and in computing (Pfister 1998)                    | 7    |

|--------------------------------------------------------------------------------------------------------------|------|

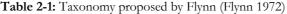

| Table 2-1: Taxonomy proposed by Flynn (Flynn 1972)                                                           |      |

| Table 2-2: Legend of acronyms presented in Figure 2-3                                                        | 18   |

| Table 2-3: Summary of the examined parallel programming model properties (Skillicorn and Talia 1998)         | ) 21 |

| Table 2-4: Properties a programming model should have (Skillicorn and Talia 1998)                            | 24   |

| Table 2-5: Properties of the serial programming model                                                        | 26   |

| Table 4-1: A synopsis of the most influential all-in-software DSM systems                                    | 72   |

| Table 4-2: The fields of the object representation data structure                                            | 83   |

| Table 4-3: A synopsis of the unique features of the NIPDSM and the way it compares to Midway                 | 93   |

| Table 6-1: Profiles of the hardware platforms used for the experiments                                       | 113  |

| Table 6-2: The elapsed time in <i>useus</i> and the corresponding cost in processor cycles of some operating |      |

| system primitive operations                                                                                  |      |

| Table 6-3: The elapsed time in users and the corresponding cost in processor cycles of some NIP primiti      | ive  |

| operations                                                                                                   |      |

| Table 6-4: The execution overhead introduced due to NIP run-time related operations as a percentage of       |      |

| the execution time of sequential version of the computation presented in Code 6-1                            |      |

| Table 6-5: The execution overhead introduced due to NIP run-time related operations as a percentage of       |      |

| the execution time of sequential version of the computation presented in Code 6-3                            |      |

| Table 6-6: Average of the tasks stolen from the repeated execution of the tests (number of nodes used:       |      |

| vector size: 2000, function granularity: ~23msecs)                                                           | 123  |

| Table 6-7: The execution overhead introduced due to NIP related operations as a percentage of the            |      |

| execution of sequential version of the grain micro-benchmark for the an APP workstation and th               |      |

| SMP workstation for different granularities                                                                  |      |

| Table 6-8: Percentage of tasks created out of 65,536 possible on the APP                                     |      |

| Table 6-9: Percentage of tasks created out of 65,536 possible on the SMP                                     |      |

| Table 6-10: Cost of NIPDSM operations                                                                        |      |

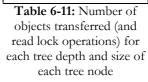

| Table 6-11: Number of objects transferred (and read lock operations) for each tree depth and size of ea      |      |

| tree node                                                                                                    |      |

| Table 6-12: NIP references required for representing the layout of a matrix                                  |      |

| Table 6-13: Percentage of cached objects that were invalidated                                               |      |

| Table 6-14: Sizes of the body and cell objects and the NIPDSM cache block                                    |      |

| Table 6-15: Percentage of lazily created tasks per step out of the maximum possible (number of nodes:        |      |

| object and cache block sizes are presented in Table 6-14, page 2)                                            |      |

| Table 6-16: Sizes of the body and cell objects and the NIPDSM cache block                                    | 149  |

|                                                                                                              |      |

## TABLE OF CODES

| Code 3-1: First version of parallel map                                                                  | 42    |

|----------------------------------------------------------------------------------------------------------|-------|

| Code 3-2: Second version of parallel map                                                                 |       |

| Code 3-3: Public interface of a tasklet in pseudo-code                                                   |       |

| Code 3-4: Tasklet private data members                                                                   | 50    |

| Code 3-5: A tasklet can be reused within the same scope                                                  | 51    |

| Code 3-6: Pseudo-code for T1 and T2                                                                      | 52    |

| Code 3-7: Pseudo-code of a tasklet that exposes a function call as a potentially parallel call           | 53    |

| Code 3-8: The NIP lazy task creation version of the pseudo-code in Code 3-6                              | 53    |

| Code 3-9: Relation between an iterative computation and its tasklet representation                       | 54    |

| Code 3-10: Two closure representations of the same iterative computation                                 | 54    |

| Code 3-11: Serial version of the application of a function onto the elements of a vector                 | 55    |

| Code 3-12: NIP lazy task creation version of the application of a function onto the elements of a vector | 55    |

| Code 3-13: Design and implementation of the MapTasklet type                                              | 56    |

| Code 3-14: The serial version of <i>nfib</i>                                                             |       |

| Code 3-15: The NIP lazy task creation version of nfib using simple tasklets                              |       |

| Code 3-16: The NIP lazy task creation version of <i>nfib</i> using a recursive tasklet                   | 59    |

| Code 4-1: The implicit enclosure of a method call around lock operations                                 |       |

| Code 4-2: Consecutive method calls may result in several state updates                                   | 79    |

| Code 4-3: Consecutive method calls of the same access mode and on the same object can be grouped         |       |

| together                                                                                                 | 79    |

| Code 4-4: Type information can be used by a compiler to deduce associations between objects              |       |

| Code 5-1: C++ interface of the NIPTasklet                                                                | . 105 |

| Code 5-2: C++ template classes for common patterns of parallelism                                        | .107  |

| Code 5-3: Part of the NIPRef interface                                                                   | .108  |

| Code 6-1: Pseudo code for an iterative computation                                                       | . 118 |

| Code 6-2: The resulting pseudo code from the translation of Code 6-1 consistent to the NIP execution     |       |

| model semantics without object memory                                                                    | . 119 |

| Code 6-3: Optimised version of the pseudo code presented in Code 6-2                                     |       |

| Code 6-4: The grain pseudo code consistent to the NIP programming model semantics                        |       |

| Code 6-5: The grain pseudo code converted to be consistent with NIP execution model semantics            | . 126 |

| Code 6-6: Pseudo code for the parallel map micro-benchmark consistent with the NIP execution model       |       |

| semantics                                                                                                | . 129 |

| Code 6-7: The Matrix class                                                                               |       |

| Code 6-8: Pseudo code for the sequential version of TSP                                                  | . 148 |

| Code 6-9: Pseudo cost for the NIP version of TSP                                                         | . 148 |

## CHAPTER 1 INTRODUCTION

The research work presented in this thesis was inspired by the emergence of high-performance computing architectures built around affordable, commodity-based hardware. The assessment of existing software-based, run-time support tools for the execution of parallel applications on such architectures and the proposition of solutions to possible drawbacks were originally set as the primary objectives for this thesis.

This chapter presents in detail the motivation for the research work undertaken and lists the contributions to knowledge that the rest of the thesis claims to make. The field of high-performance computing is explored and the application area and hardware trends are studied.

The discipline of parallelism is seen as being very closely interrelated to high-performance computing. The basic requirements for development models and software tools to support parallelism on the emerging high-performance architectures are set and the scope for the chapters that follow is established.

## 1.1. High-Performance Computing

There have always been applications with requirements that exceeded the available computational power at any particular period in time. The effort to meet the needs of these performance-hungry applications has been the driving force in designing and building faster computers.

In the early years of high-performance computing (HPC), applications with excessive demands in processing power were limited to the area of scientific computation (weather prediction, cosmology, particle simulation, etc.). As the processing power made available to scientists increased, the urge to run larger and/or more difficult problems continued and it is still the same today. In addition to scientists, computer practitioners in other application areas started to realise the benefits of harnessing more processing power. Applications in areas such computer vision and graphics, computer-aided design, databases, have all benefited from high-performance computing architectures since the '80s—and still do. Today, performance-critical application areas include computer animation (in 1995, 'Toy Story' was the first full-featured, computer-generated film with many others following it), aerospace, geophysics, World Wide Web (WWW), gaming, finance, bioinformatics, education, healthcare, to name only a few. One can observe a shift from scientific to primarily industrially oriented HPC applications.

The last statement is further supported by the recent growth of the WWW. Performance-critical web applications have emphasised the demand for industry-based HPC platforms. As an example, one only needs to examine the strategies for their future products that the two largest software companies in the world, namely Microsoft and Oracle, have drawn. Both are suggesting a return to the old server-based style of computing (Microsoft 2000; Oracle 1999). The requirements of the multimedia-rich, computationally intensive, network-centric applications that are to be supported by the re-proposed server-based models of computing point to HPC architectures.

With the majority of the application areas being industry-oriented during the last decade, the interest in the HPC field and the high rate of investment were unsurprising. As it will soon be shown, systems with an improved cost/performance ratio attracted most of the attention and architectures based on commodity hardware are becoming more popular due to their ability to offer good performance for a relative low cost.

A study of the HPC field cannot and should not neglect the required application development models and support tools as well as their enabling execution environments.

Additionally, the discipline of parallelism is seen by this thesis as being closely coupled with that of HPC, as the foremost purpose of parallelism is the improvement of performance. To that extent, this thesis considers different models and support tools for parallelism as being the enabling factors for high-performance computing.

Before the discussion moves to parallelism related issues, the application area and hardware trends in the field of high-performance computing are considered. It is hoped that the current and future requirements for development and execution paradigms will be better understood.

## 1.1.1. Application Area Trend

Analysis of the list of the 500 fastest supercomputers in the world (TOP500 List Authors 2000) reveals a number of trends in the HPC field. The 'TOP500 list' (TOP500 List 2000) is published twice a year, every June and November, and it records the fastest computers in the world based on the results obtained from the execution of the LINPACK benchmark (Dongarra 1994).

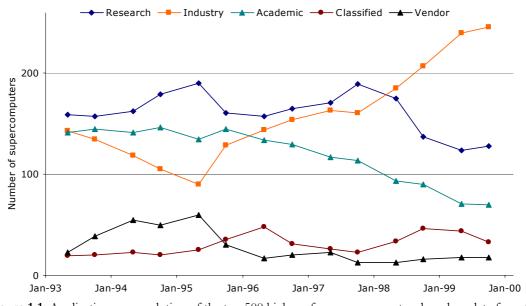

Figure 1-1: Application area evolution of the top 500 high-performance computers based on data from the 'TOP500 list' (TOP500 List 2000; TOP500 List Authors 2000)

The graph of Figure 1-1, which is based on all the published TOP500 lists until November 1999, is illustrative of the transition towards industry-driven high-performance computing. In 1996, the number of computers in the TOP500 list used in the industry exceeded those installed in the academia and two years later those used by research institutes. However, while the graph of Figure 1-1 strengthens the argument about the growing interest of industry in high-performance computing, it does not reveal any particular characteristics about the TOP500 systems.

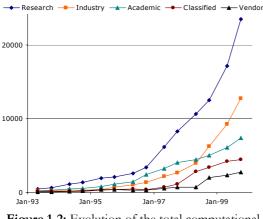

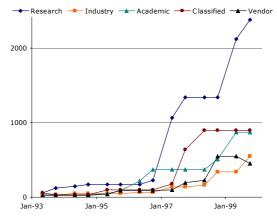

**Figure 1-2:** Evolution of the total computational power (in Gflop/s) per application area of the top 500 high-performance computers based on data from the 'TOP500 list' (TOP500 List 2000; TOP500 List Authors 2000)

Figure 1-3: Evolution of the computational power (in Gflop/s) of the fastest computer for each application area of the top 500 high-performance computers based on data from the 'TOP500 list' (TOP500 List 2000; TOP500 List Authors 2000)

When the achieved computational power, expressed in Gflop/s<sup>1</sup>, of all the supercomputers in the TOP500 list is added together on per application area basis, it is revealed that the industry-based systems are lagging behind in overall performance when compared to the systems employed by the other application areas (Figure 1-2). Despite their great number, as shown in Figure 1-1, the total computational power of the industry-installed TOP500 high-performance computers at the end of 1999 is almost half of the equivalent computational power of research-based supercomputers (Figure 1-2). As a result, the high-performance computers in the TOP500 list that are used in industry are the slowest on average when compared to any other application area.

The investment in exceptionally fast, number-crunching platforms seems to be exclusively research-driven, as suggested by Figure 1-3 which shows the evolution of the fastest of the supercomputers in the TOP500 list for each application area. Again, it is clear that industry does not invest in the highest performing solutions possible. Instead, there is an indication that industry is mostly concerned with the cost/performance ratio.

Although costing information about the supercomputers in the TOP500 list is not made available, it is safe to assume that in the general case the cost/performance ratio becomes significantly high at the top of the TOP500 list. The excessive computational requirements of the scientific applications result in investments on fewer but at the same time faster high-performance architectures. It is for this reason the number of supercomputers in research has been decreasing (Figure 1-1) while their performance has been continuously increasing (Figure 1-2 and Figure 1-3). In contrast and despite the manifested interest of industry in high-performance computing, the lack of

<sup>&</sup>lt;sup>1</sup> Flop (Floating Operations): Unit used in the measurement of computational power.

industry-installed supercomputers from the top of the TOP500 list suggests that the investment on new platforms is not purely performance-driven but, instead, cost/performance-driven.

## 1.1.2. Architectural Trends

The computer industry has been experiencing a tremendous rate of advances in VLSI technology, especially during the last decade. Microprocessors and memory have been becoming faster and cheaper, interconnection networks have been being built with more available bandwidth and shorter latency, and local and wide area networking technology has been advancing, mostly due to the exponential growth of the Internet.

Massively Parallel Processing (MPP) and Symmetric Multi-Processing (SMP) computers are now much cheaper to manufacture because they can be based partially or even completely on general-purpose, commodity hardware. An MPP consists of a great number of processing elements with their own private memory. The processing nodes may be interconnected through a variety of existing topologies (*e.g.*, rings, buses, cubes, hyper-cubes, etc.). An SMP consists of a usually small number—when compared to MPP architectures—of processing elements that all share the same physical memory.

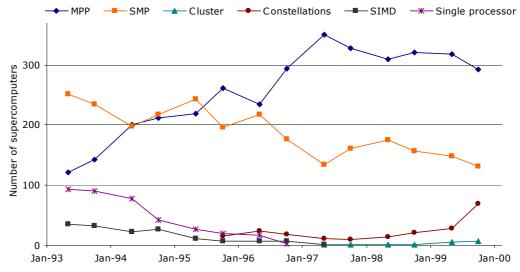

If the reasoning of the previous section about the shift towards inexpensive high-performance computing was accurate, then MPP and SMP architectures should lead the TOP500 list in terms of numbers. Indeed, the graph of Figure 1-4 confirms the latter hypothesis by presenting the evolution of the TOP500 hardware architectures since November 1993.

Due to the scalability limitations of the SMP architectures, further improvements in performance are usually difficult and/or extremely costly to achieve. It can be suggested that the combination of the costing and scalability considerations is the reason the number of SMP architectures is in decline. Furthermore, the eclipse of architectures based on Single Instruction Multiple Data (SIMD) processors or just one very expensive but specialised single processor (Figure 1-4) can also be attributed to their unfavourable cost/performance ratio and their scalability limitations.

Figure 1-4: Evolution of hardware architecture of the top 500 high-performance computers based on data from the 'TOP500 list' (TOP500 List 2000; TOP500 List Authors 2000)

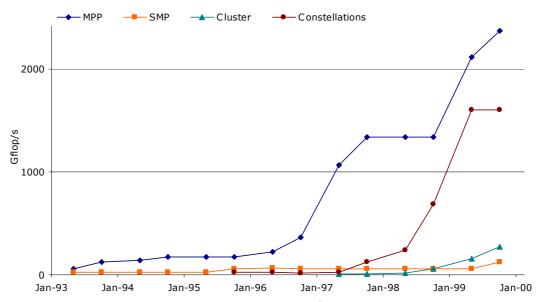

In contrast, the architectural shift towards MPP architectures can be justified by their excellent scalability and the achieved performance. Since the first publication of the TOP500 list, an MPP supercomputer has always been the fastest. Figure 1-5 shows the evolution of the computational power, in Gflop/s, of the best performing supercomputer per architecture. The fastest computer in the world in November 1999, according to the TOP500 list, was the ASCI Red, located at the Sandia National Labs, US, which consisted of an impressive number of 9,472 Intel PentiumII<sup>TM</sup> processors. The ASCI Red is probably the best demonstration of the way commodity hardware—in this case the PentiumII<sup>TM</sup> microprocessors—can be incorporated in a supercomputer that is capable of achieving record-breaking performances.

Figure 1-5: Evolution of the computational power (in Gflop/s) of the fastest computer for each hardware architecture of the top 500 high-performance computers based on data from the 'TOP500 list' (TOP500 List 2000; TOP500 List Authors 2000)

The shift towards commodity-based HPC is also indicated by the relatively recent appearance in the TOP500 list of a new type of computer architecture that is based on numbers of workstations interconnected by fast interconnection networks. The cluster architecture, as it is known, has been gaining momentum mostly due to its extremely advantageous cost/performance ratio.

Finally, the general interest for inexpensive HPC is also indicated by the increasing popularity of constellation architectures. Such architectures leverage collections of existing, most often older, supercomputers for the execution of high-performance applications. It should not be of any surprise that in November 1999 industry was the main user of constellations due to the cost savings that can be achieved from the reuse of old platforms.

### 1.1.3. Trend Synopsis

It is evident that in the last few years, industry has emerged as the main user of HPC. Computational power requirements are no longer exclusive to scientific-oriented applications. The field of general-purpose, high-performance computing is gaining momentum, as the list of HPC applications suggests (page 1). The notable increase in the number of TOP500 supercomputers used in industry is yet another indication of the great interest and investment in HPC. It seems, though, that the focus is mainly on the cost/performance ratio of the platforms employed rather than just on performance. That would explain the inferior computational power that is achieved by HPC platforms used

in industry when compared to those used in the other application areas and especially in research.

In contrast, due to the excessive computational requirements of scientific applications, the maximum achievable performance is pursued for the HPC systems that are deployed in research. Often, the focus on performance dramatically increases the implementation and support costs for a platform and, as a result, there has to be a concentration on fewer but faster installations.

There also seems to be a drive towards HPC systems that are based, partially or completely, on commodity hardware, especially off-the-self microprocessors. The incorporation of commodity hardware into HPC results in more affordable systems without necessarily sacrificing their performance.

Finally, it is clear that parallelism is the main enabling factor for HPC. The prime goal of parallelism is to improve the execution performance of applications. Since supercomputer architectures based on single, specialised, expensive processors have been eclipsed (Figure 1-4), it is reasonable to consider parallelism as the facilitating force for high-performance computing.

All the current HPC architectures are built upon aggregations of processing elements that collaborate. The definition of a processing element may vary between HPC architectures. For example, it may be a microprocessor, a whole workstation, an SMP computer, or even a supercomputer in the case of constellations. Nevertheless, in any case the concept is the same: a number of processing-capable components that work simultaneously having as a purpose the faster execution of an application.

Having recognised the importance of parallelism in the HPC field, this thesis embarks in the investigation of issues related to the field of parallel computing.

## 1.2. Parallelism

For almost six decades, the computer model based on a single processor, memory, bus, and peripherals—the von Neumann architecture (Burks et al. 1962)—has been the dominant architectural model upon which computers have been built. Nevertheless, even during the '60s, the HPC community began to realise that traditional computers based on the von Neumann model were unable to produce the computational power required. With parallelism, the traditional model of computing could be extended to achieve better performance.

## 1.2.1. Definition

According to Pfister (Pfister 1998), there are three ways to perform an activity faster in life: work harder, work smarter, or get help. Pfister observes an analogy with the computer world (Table 1-1). The execution performance of applications may be improved when the components of the computer architecture (*e.g.*, processor, memory, bus, etc.) are enhanced. Additionally, an implementation of the same application based on a better algorithm may also improve the execution performance. However, if more than one processing elements work on the same problem, execution performance may be dramatically increased when compared to the two previous approaches.

| Work harder                             | -   | Processor speed                          |

|-----------------------------------------|-----|------------------------------------------|

| Work smarter                            | -   | Algorithms                               |

| Get help                                | -   | Parallel processing                      |

| 1 1. I Jour to parto up an activity for | tou | in real life and in accounting (Distor 1 |

Table 1-1: How to perform an activity faster in real life and in computing (Pfister 1998)

Almasi and Gottlieb define a parallel computer as "a large collection of processing elements that can communicate and cooperate to solve large problems fast" (Almasi and Gottlieb 1994). However, as they also observe, the definition raises many questions: How large should the collection of processing elements be? How do they communicate? What means do they use to cooperate? How large a problem should be? In answering these questions, computer architects and software developers have come up with a variety of solutions since the '60s, descriptions of which can be found in (Almasi and Gottlieb 1994; Culler and Singh 1999; Lewis and El-Rewini 1992; Pfister 1998; Tanenbaum 1999).

Finally, based on the definition by Almasi and Gottlieb, Culler and Singh believe that a parallel architecture is just *"the extension of conventional computer architecture to address issues of communication and cooperation among processing elements"* (Culler et al. 1993b). However, this definition does not capture the essence of parallel computation, which according to this thesis is speedup. As it was suggested earlier in this chapter, the foremost purpose of parallelism is the faster execution of applications and for that reason the definition by Almasi and Gottlied is perceived as more accurate for the purposes of this thesis.

#### 1.2.2. Hardware Support

Since the 60's, there has been a plethora of research works and considerable progress in the field of parallel computer architecture. The rate of computational power increase, as shown by graphs presented in the previous section, is an indication of the strong hardware developments in the field. The four decades of advances have resulted in a great diversity of hardware platforms, as the discussion in Chapter 2 demonstrates where a taxonomy of existing architectures is also presented.

One may suggest, though, that despite the advances in hardware, application development and run-time support tools for the various parallel platforms have not received the same attention.

## 1.2.3. Programming and Execution Models

Tanenbaum describes a computer system in terms of a series of layers (Tanenbaum 1999). At the bottom of the organisational structure, there is the hardware layer and at the top the application layer. In between, layers like the programming language and the operating system exist. A layer in the organisational structure of a computer system should provide a simple, well-defined abstraction of the underlying ones (Chapter 2 presents a more detailed discussion on the layered approach to parallel computer system organisation). Perhaps more than other disciplines, in the case of parallel computing the performance is an extremely important characteristic of a layer. Consequently, it should be noted that efficiency should not be sacrificed in favour of abstraction.

Unfortunately, after observing the evolution of parallelism since the '60s, one notices that in practise there have not been significant advancements in the layered approach to parallel computer organisation. Parallel computing practitioners have been reluctant to explore new approaches to development and run-time support, as the hesitation in adopting innovative methods of programming and execution of applications on parallel computers suggests. The same troublesome—according to this thesis—methods have been used for decades now.

It is suggested that the absence of a clear distinction between a programming model and an execution model of parallel computing is to blame for the apparent lack of advancement in parallel computing practices. The former model represents the view of the parallel system as it is seen by the developer while the latter is the abstraction of a parallel system as it is perceived by the application. The two models are going to be defined and discussed in detail in Chapter 2.

The lack of a clear distinction between the programming and execution models has allowed hardware characteristics to be filtered up to the application developer. Programmers are required to write applications with the hardware configuration always in mind. The management of parallelism, synchronisation, communication, and other related issues, burden the application developers. As a result, the parallel software development and maintenance processes have become troublesome, time-consuming, and costly. The most popular models of parallel computing are message-passing and shared-memory. The two are considered both as programming and execution models. Developers have to reason about the implementation of algorithms with the architectural characteristics of the parallel platforms in mind. There is no attempt by either of the two models to hide architectural details from the programmers. There are, however, programming models that have been designed to abstract from the underlying architectures, such as the functional model. A synopsis of the main characteristics of all the above models are given below (a more detailed discussion is presented in Chapter 2):

- The message-passing programming and execution model do not provide an abstraction of the underlying parallel architecture. Application developers have to manage communication and synchronisation between processing elements. In most cases and when the programming primitives of the model are used appropriately, efficiency is not an issue. Modern operating systems, often in combination with optimised user-level libraries that vendors of parallel systems supply, provide good run-time support. However, using the message-passing programming primitives correctly in order to better utilise the parallel architecture is a huge task for the application developer.

- The abstraction that the shared-memory model provides is that of a computer with a collection of processing elements that have access to a common memory. The architecture of the underlying parallel system is not hidden from application developers, as they have to manage parallelism. As in the case of the message-passing model, efficiency can be achieved when the programming primitives of the model are used suitably for a specific architecture and with the appropriate operating system and/or user-level libraries support.

- Unlike the two previous models, the functional programming model manages to hide the details of the underlying parallel architecture. It requires an execution model that is not made visible to application developers, who are not burdened with the task of managing parallelism but, instead, they only need to concentrate on algorithmic issues. However, the model greatly depends on software tools (i.e., compilers, run-time systems) that have not been able to match the performance of the tools available for the message-passing and shared-memory models. The functional programming model appeared to be good alternative to the traditional models but it has not managed to gain a sufficient following in order to become a commercial success (Almasi and Gottlieb 1994).

It can also be suggested that the existing programming models have poor support for good software engineering practices (some to a lesser degree than others) like abstraction for managing complexity, structure reuse, maintenance, profiling/debugging, which are very important for the application development lifecycle.

## **1.3.** Possible Future Directions for Parallel Computing

An attempt to determine the future directions of parallel computing may provide an indication of those initiatives that must be undertaken today. It is not the purpose of this thesis to discuss and attempt to predict the future of parallel computing. Instead, using as a starting point the observations that have been made up to now in this chapter and based on the findings of a working group on 'Enabling Technologies for Petaflops Computing' (Sterling et al. 1995), this section attempts to identify those areas that are likely to influence the field of parallel computing in the future.

#### 1.3.1. Microprocessor Technology

There are indications that the remarkable rate of advances in microprocessor technology will be reduced as physical limits in their production process are reached. The vast manufacturing costs will probably yield the current processor manufacturing technologies commercially unviable (Moore 1965; Moore 1997; Moore 1998).

Exotic technologies are under investigation and they might provide alternatives to HPC architectures. For example, research on the use of technologies based on optics and superconductivity in processor architecture promise enormous availability of computational power. However, such technologies are unlikely to make an impact during the next two decades. Other promising areas of research such molecular and quantum computing are even more unlikely to make an impression in the near future. The findings of the working group on Petaflops computing confirm these observations (Sterling et al. 1995).

The use of huge numbers of microprocessors in massively parallel computer architectures is likely to become standard practise in the HPC field. Cost concerns appear to favour the use of commodity rather than special purpose microprocessors in such architectures. The hardware trends observed earlier in this chapter seem to confirm the last statement. Furthermore, in the analysis of the findings of the working group on 'Enabling Technologies for Petaflops Computing,' Sterling, Messina, and Smith make a very important remark that strengthens the arguments toward the use of commodity processors. The analysis also hints at the use of other commodity components in addition to microprocessors (*e.g.*, network interconnections, memory, etc.):

"The level of investment being applied to technology development by the commercial semiconductor marketplace is substantial and greatly exceeds any augmentation likely from government research programs. Thus, the opportunity to influence expensive development cycles is limited. This situation is exacerbated by the tight coupling between mass production and component cost. Specialty parts become significantly more costly than mass-produced commodity parts of equivalent complexity. Consequently, any initiative to develop a Petaflops computer will have to rely heavily (although not exclusively) on commercially-available components. By leveraging advances that occur as commercial by-products, development costs can be acceptable." (Sterling et al. 1995)

#### 1.3.2. Architectures

The findings of the working group on 'Enabling Technologies for Petaflops Computing' (Sterling et al. 1995) reinforce the argument that was presented earlier in this chapter about the shift towards parallel computer architectures that are focused on cost/performance ratio. The use of commodity hardware on such architectures is essential if the manufacturing costs are to be kept down. In (Sterling et al. 1995), it is also predicted that there will be a shift towards massively parallel architectures with tens of thousands processors. The hardware trend of Figure 1-4 (page 5) confirms the prediction.

However, the move towards architectures with massive numbers of processors will probably require new techniques to emerge, especially in the field of memory technology (Sterling et al. 1995). Such techniques will attempt to eliminate the latency in memory access, improve memory bandwidth, allow for faster communication between processing elements, etc.

#### 1.3.3. Software

The authors of 'Enabling Technologies for Petaflops Computing' reveal the lack of good programming models and software tools for parallel computing (Sterling et al. 1995). They predicted that for the Petaflops mark to be achieved, a degree of parallelism of up to one million would be required. Programmers cannot be expected to manage that degree of parallelism without adequate support from software.

In (Sterling et al. 1995), a series of areas where developments are required is proposed. The subset that is relevant to the topic of this thesis is presented bellow.

- **Global address space:** The available memory on a massively parallel architecture should be accessible in a uniform way.

- Latency hiding: Either via software or hardware means, the latency in memory operations should be hidden.

- Implicit and explicit parallelism: New models for developing parallel applications are required that allow programmers to concentrate on algorithm issues rather than the management of parallelism.

- Software support tools: New support tools for transparent resource management and automatic migration of data and tasks are required.

This thesis attempts to reflect on the requirements of software tools for well-organised, cost-effective, parallel application development and for efficient execution on the parallel architectures of the future.

## 1.4. Research Goals

The discussion to this point attempted to sketch the current state of parallel computing and hint on potential future developments. A need for new parallel programming and execution models and their required software support tools emerged. Furthermore, as the complexity of (parallel) applications grows, the implementation, debugging, and profiling stages of the application development process become increasingly troublesome. It is apparent that good software programming practices need be introduced in the development lifecycle of parallel applications.

In this section, the motivation for the research work undertaken is discussed. The objectives that were set and their augmentation are also presented. Finally, the contributions to knowledge that this thesis claims to make are outlined.

## 1.4.1. Motivation

This research work was originally inspired by the emergence of cluster architectures based on commodity hardware as parallel platforms. The considered clusters consisted of single-processor workstations that were interconnected via commodity networking equipment. The investigation of run-time techniques for the execution of parallel object-oriented applications on such affordable platforms was originally set as the primary objective. The main characteristics of the targeted platforms were their distributed, non-shared memory and their slow interconnections. However, it was clear even during the early stages of the research work that the original objectives were too narrow. There was no reason why the run-time techniques under investigation could not target other high-performance architectures as well. As a result, the goals were extended to target shared-memory multiprocessors and clusters of single-processor and/or multiprocessor architectures. The investigation into programming and execution models for parallel computing was also included in the set of objectives. The exploration of run-time techniques for parallel computing on shared- and distributed-memory architectures was maintained as part of the research goals.

## 1.4.2. Contributions to Knowledge

The exploration of the research goals resulted in the original work that the rest of this thesis presents. The list of the contributions to knowledge together with a synopsis of the main findings is presented below.

## NIP Programming Model

The NIP programming model attempts to satisfy the requirements of the parallel application development process as those were identified in this chapter and as Chapter 2 discusses in more detail. The main characteristics of the model are the abstraction from any underlying architectural details. The focus of the NIP programming model is on implicit parallelism and object-orientation. The programmer is not burdened with the tasks of identifying and managing parallelism in an application. Instead, developers are presented with a programming model that allows them to concentrate on the exploration of algorithmic issues only.

The NIP programming model combines the benefits of two programming paradigms, namely functional and object-orientation. The model is based on a previously introduced *functions plus objects* paradigm (Sargeant 1993).

#### **NIP** Execution Model

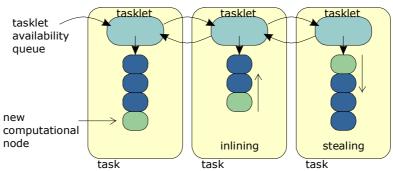

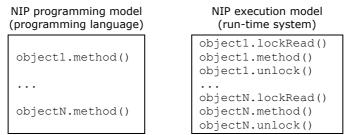

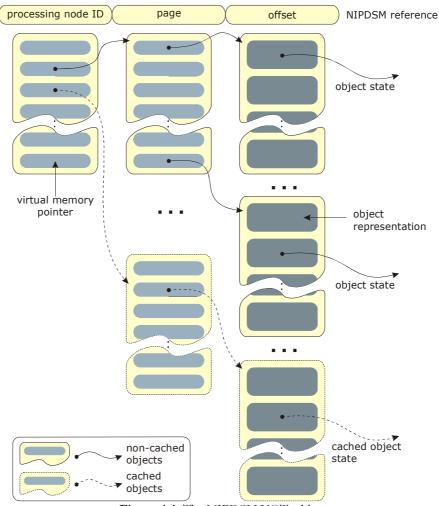

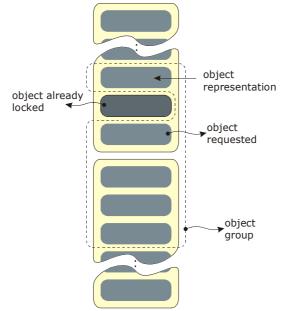

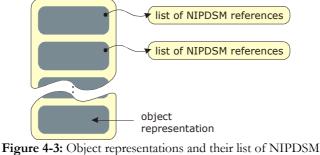

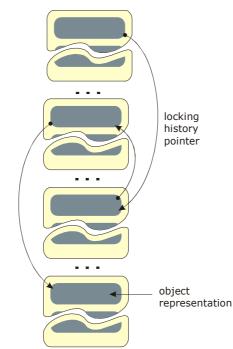

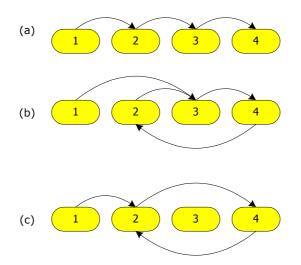

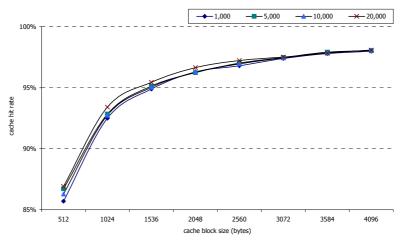

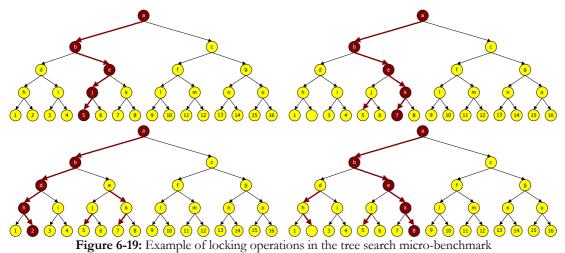

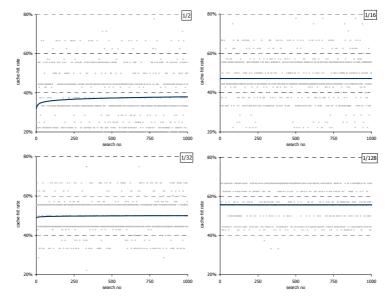

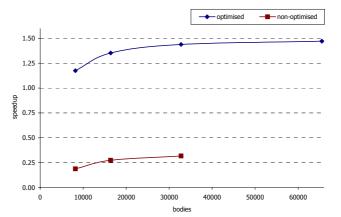

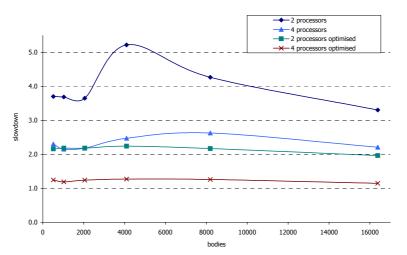

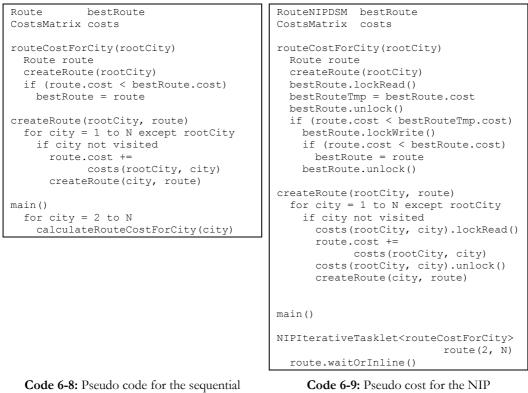

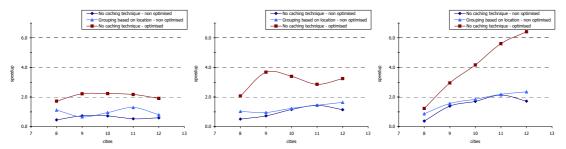

The NIP execution model was originally designed to provide the semantics around which run-time environments for the NIP programming model could be implemented. Nevertheless, the semantics of the model are such that even non-implicitly parallel programming models could target it through appropriate software tool support.