# FAST, AREA-EFFICIENT 32-BIT LNS FOR COMPUTER ARITHMETIC OPERATIONS

Rizalafande Che Ismail

A THESIS SUBMITTED FOR THE DEGREE OF DOCTOR OF PHILOSOPHY AT NEWCASTLE UNIVERSITY, UNITED KINGDOM

SCHOOL OF ELECTRICAL & ELECTRONIC ENGINEERING FACULTY OF SCIENCE, AGRICULTURE & ENGINEERING

September 2012

### ABSTRACT

The logarithmic number system has been proposed as an alternative to floating-point. Multiplication, division and square-root operations are accomplished with fixedpoint arithmetic, but addition and subtraction are considerably more challenging. Recent work has demonstrated that these operations too can be done with similar speed and accuracy to their floating-point equivalents, but the necessary circuitry is complex. In particular, it is dominated by the need for large lookup tables for the storage of a non-linear function.

This thesis describes the architectures required to implement a newly design approach for producing fast and area-efficient 32-bit LNS arithmetic unit. The designs are structured based on two different algorithms. At first, a new cotransformation procedure is introduced in the singularity region whilst performing subtractions in which the technique capable to generate less total storage than the cotransformation method in the previous LNS architecture. Secondly, improvement to an existing interpolation process is proposed, that also reduce the total tables to an extent that allows their easy synthesis in logic. Consequently, the total delays in the system can be significantly reduced.

According to the comparison analysis with previous best LNS design and floating-point units, it is shown that the new LNS architecture capable to offer significantly better in speed while sustaining its accuracy within floating-point limit. In addition, its implementation is more economical than previous best LNS system and almost equivalent with existing floating-point arithmetic unit.

### ACKNOWLEDGEMENTS

First of all, I would like to express my special gratitude to my great supervisor, Dr. Nick Coleman, deeply for giving me an opportunity to pursue in this research work. His excellent advice, priceless support and remarkable guidance as well as spending a great deal of time and energy for this thesis is gratefully appreciated. What I have learned from him will benefit me well beyond my graduation in my future research career.

I am greatly indebted in Dr. Robin Emery and Mr. Raa'ed Aldujaily for the support during the work especially with related to the Cadence and Synopsys design tools. I also want to thank to all colleagues at the Microelectronics Systems Design group in room E4.21, who contributed to the perfect working environment.

Special thanks go to Mr. Mark Wilmott and Mrs. Lisa Wong at the Rutherford Appleton Laboratory in Harwell campus, Oxford. They have not only offered invaluable technical advice, but also offered CAD tool support in my thesis work.

In addition, I want to thank my beloved wife, Farah Fadhlina, and my gorgeous children, Irdina Rizqin, Iwani Rifqah and Irfan Rasyeeq, very much for their loving care, understanding and moral support. They gave me the boundless encouragement and motivation and led me to finish this thesis. I would like to extend thanks to my wonderful parents for all the love and support given.

Thanks are also due to University Malaysia Perlis and Ministry of Higher Education Malaysia for granting a study leave, and for financial assistance.

Finally, to all named and unnamed, for their support and understanding towards the completion of this research, thank you very much. Life is good!

## LIST OF CONTENTS

| A  | BSTRA                          | лСТ                                         | i   |  |  |  |

|----|--------------------------------|---------------------------------------------|-----|--|--|--|

| A  | CKNO                           | WLEDGEMENTS                                 | .ii |  |  |  |

| 1. | . Introduction                 |                                             |     |  |  |  |

|    | 1.1.                           | Motivation for the Research                 | . 1 |  |  |  |

|    | 1.2.                           | An Overview of the LNS                      | . 2 |  |  |  |

|    | 1.3.                           | Contribution of the Thesis                  | .4  |  |  |  |

|    | 1.4.                           | Structure of the Thesis                     | . 5 |  |  |  |

| 2. | Bacl                           | kground and Previous Work                   | . 7 |  |  |  |

|    | 2.1.                           | Introduction                                | . 7 |  |  |  |

|    | 2.2.                           | Computer Arithmetic Unit                    | . 7 |  |  |  |

|    | 2.3.                           | Number Systems Representation               | 9   |  |  |  |

|    | 2.3.1                          | 1. Floating Point                           | 10  |  |  |  |

|    | 2.3.2                          | 2. Logarithmic Number System                | 12  |  |  |  |

|    | 2.4. Floating-Point Algorithms |                                             |     |  |  |  |

|    | 2.5.                           | Logarithmic Number System Algorithms        | 14  |  |  |  |

|    | 2.5.1                          | 1. Direct Lookup Table                      | 17  |  |  |  |

|    | 2.5.2                          | 2. Interpolation                            | 19  |  |  |  |

|    | 2.5.3                          | 3. Table Partitioning                       | 22  |  |  |  |

|    | 2.5.4                          | 4. Bipartite Tables                         | 24  |  |  |  |

|    | 2.5.5                          | 5. Co-transformation                        | 26  |  |  |  |

|    | 2.5.6                          | 6. Hybrid Architecture                      | 28  |  |  |  |

|    | 2.5.7                          | 7. Related Variant Number Systems           | 29  |  |  |  |

|    | 2.6.                           | Performance Analysis                        | 31  |  |  |  |

|    | 2.7.                           | LNS for Specific Applications               | 32  |  |  |  |

|    | 2.8.                           | Summary                                     | 36  |  |  |  |

| 3  | Met                            | rics for Measurement and Design Methodology | 37  |  |  |  |

|    | 3.1.                           | Introduction                                | 37  |  |  |  |

|    | 3.2.                           | Metrics for Measurement                     | 37  |  |  |  |

|    | 3.2.1   | Error Analysis                                                      |         |

|----|---------|---------------------------------------------------------------------|---------|

|    | 3.2.2   | 2. Functional Evaluation                                            | 41      |

|    | 3.2.3   | 3. Timing Evaluation                                                | 41      |

|    | 3.2.4   | 4. Area Estimation                                                  | 42      |

|    | 3.3.    | Design Methodologies                                                | 43      |

|    | 3.3.1   | I. Simulator Design Flow                                            | 44      |

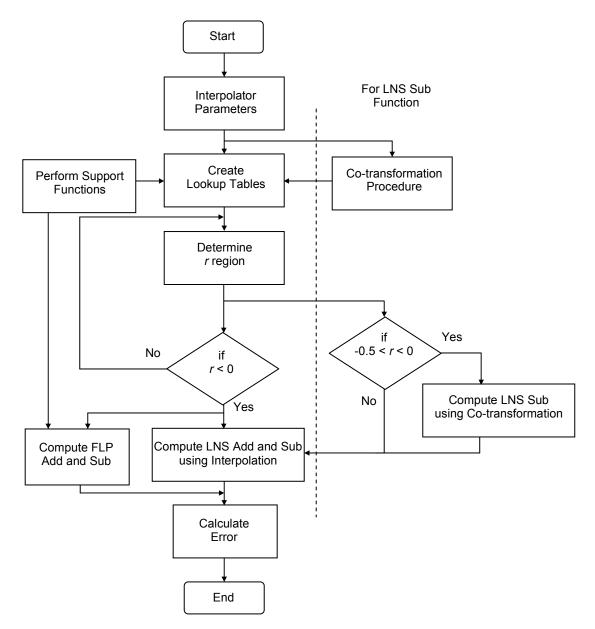

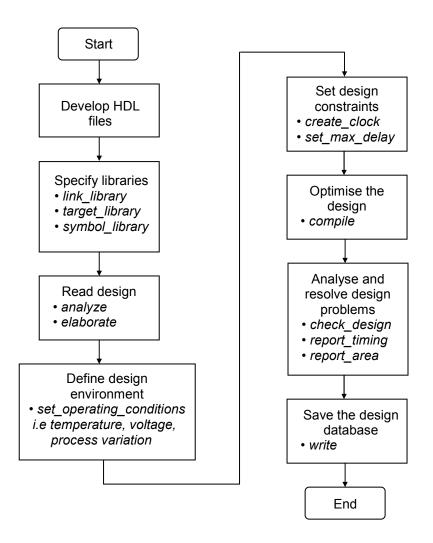

|    | 3.3.2   | 2. Circuit Design Flow                                              | 46      |

|    | 3.3.3   | 3. Synthesis Design Flow                                            | 48      |

|    | 3.4.    | Summary                                                             | 50      |

| 4. | Rece    | ent 32-bit Arithmetic Implementations                               | 51      |

|    | 4.1.    | Introduction                                                        | 51      |

|    | 4.2.    | Leading Published Design: ELM processor                             | 51      |

|    | 4.2.1   | ELM Interpolation: Error Correction Algorithm                       | 54      |

|    | 4.      | 2.1.1. Taylor Approximation                                         | 56      |

|    | 4.3.    | Simulation Results                                                  | 57      |

|    | 4.4.    | Design Summary                                                      | 57      |

|    | 4.5.    | Synthesis Results                                                   | 61      |

|    | 4.6.    | FLP Devices                                                         | 63      |

|    | 4.7.    | Comparison Analysis: ELM and FLP                                    | 64      |

|    | 4.8.    | Summary                                                             | 66      |

| 5. | Co-t    | ransformation Architecture for LNS Subtraction                      | 67      |

|    | 5.1.    | Introduction                                                        | 67      |

|    | 5.2.    | First-order Co-transformation Procedure for LNS Subtraction         | 67      |

|    | 5.3.    | Optimising Lookup Tables for LNS Subtraction                        | 70      |

|    | 5.3.1   | 1. The New Algorithm: Second-order Co-transformation Procedu        | are for |

|    | LNS     | Subtraction                                                         | 71      |

|    | 5.3.2   | 2. Function Approximation Scheme                                    | 76      |

|    | 5.3.3   | 3. Simulation Results                                               | 77      |

|    | 5.3.4   | 4. Design Summary                                                   | 77      |

|    | 5.4.    | Comparison Analysis: First-order and Second-order Co-transformation | tion    |

|    | with th | e Taylor Interpolator                                               | 80      |

|   | 5.5.    | Summary                                                        |        |

|---|---------|----------------------------------------------------------------|--------|

| 6 | Fune    | ction Approximation Scheme for LNS Addition and Subtraction    |        |

|   | 6.1.    | Introduction                                                   |        |

|   | 6.2.    | Function Approximation using Interpolation                     |        |

|   | 6.3.    | Linear Interpolation                                           |        |

|   | 6.3.    | Linear Taylor Interpolation                                    |        |

|   | 6.3.2   | 2. Linear Lagrange Interpolation                               |        |

|   | 6.3.3   | B. Linear Lagrange Interpolation – Modified Version            |        |

|   | 6.3.4   | 4. Comparison of Linear Interpolators                          |        |

|   | 6.4.    | Non-linear Interpolation                                       |        |

|   | 6.4.    | I. High-Order Degree Method                                    |        |

|   | 6.4.2   | 2. Error Correction Algorithm                                  |        |

|   | 6.4.2   | 2.1. Implementation of Error Correction Algorithm with Lagra   | ange   |

|   | Inter   | polation                                                       |        |

|   | 6.5.    | Improvement of Non-linear Lagrange Interpolation               |        |

|   | 6.5.    | Partitioning the Intervals                                     |        |

|   | 6.5.2   | 2. Minimising the Lookup Tables                                |        |

|   | 6.5.3   | B. Design Summary                                              |        |

|   | 6.6.    | Alternative Method: Minimax Interpolation                      | 109    |

|   | 6.7.    | ELM with the New Interpolator                                  |        |

|   | 6.7.    | I. Improved Lagrange Interpolation                             |        |

|   | 6.7.2   | 2. Minimax Interpolation                                       | 114    |

|   | 6.8.    | Comparison Analysis: First-order and Second-order Co-transform | nation |

|   | with th | e New Interpolator                                             |        |

|   | 6.9.    | Summary                                                        | 119    |

| 7 | Log     | arithmic Number System Arithmetic Unit                         |        |

|   | 7.1.    | Introduction                                                   |        |

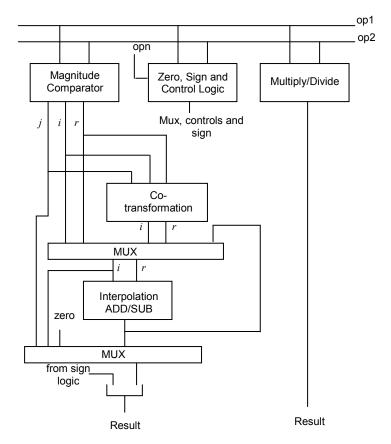

|   | 7.2.    | Arithmetic Unit Design                                         |        |

|   | 7.2.    | I. Multiply/Divide Unit                                        |        |

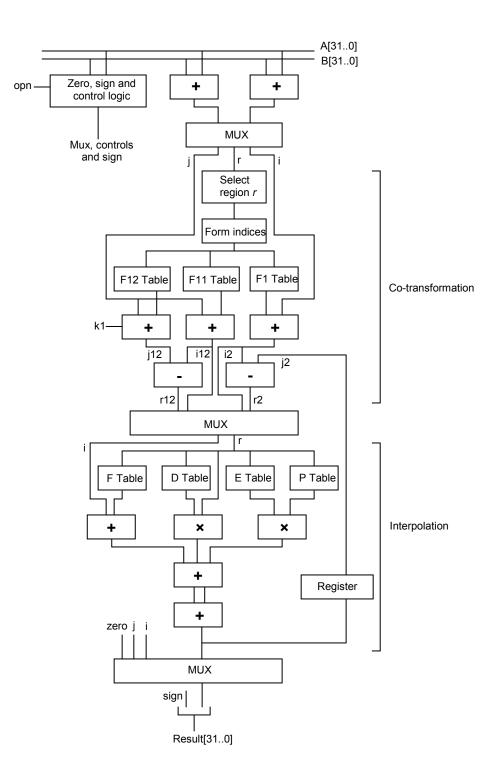

|   | 7.2.2   | 2. Add/Subtract Unit                                           |        |

|   | 7.3.    | Hardware Implementation of a 32-bit LNS System                 |        |

| 7                      | <i>'</i> .4.                                    | Synthesis Results                                              |       |  |

|------------------------|-------------------------------------------------|----------------------------------------------------------------|-------|--|

| 7                      | 7.5. Design Analysis                            |                                                                |       |  |

| 7                      | <i>'</i> .6.                                    | Summary                                                        | . 128 |  |

| 8.                     | Imp                                             | lementation with Long Word-length Number                       | . 130 |  |

| 8                      | 8.1.                                            | Introduction                                                   | . 130 |  |

| 8                      | 8.2.                                            | The LNS System in a 40-bit Format                              | . 131 |  |

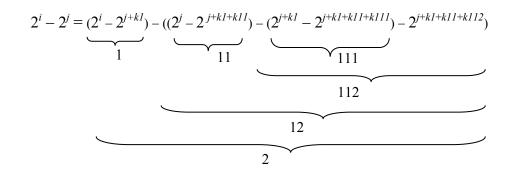

|                        | 8.2.1                                           | 1. Third-order Co-transformation Procedure for LNS Subtraction | . 131 |  |

|                        | 8.2.2                                           | 2. Interpolation                                               | . 136 |  |

|                        | 8.2.3                                           | 3. Design Summary                                              | . 138 |  |

| 8                      | 8.3.                                            | Design Implementation                                          | . 139 |  |

|                        | 8.3.1                                           | I. Synthesis Results                                           | . 139 |  |

| 8                      | 8.4.                                            | Performance Analysis                                           | . 141 |  |

| 8                      | 8.5.                                            | Summary                                                        | . 143 |  |

| 9.                     | Con                                             | clusions and Recommendations                                   | . 144 |  |

| 9                      | 9.1.                                            | Conclusions of the Study                                       | . 144 |  |

| 9.2. Future Extensions |                                                 | . 145                                                          |       |  |

| Ref                    | erence                                          | es                                                             | . 147 |  |

| A                      | Apper                                           | ndices                                                         | . 153 |  |

| A                      | <b>A</b> 1.                                     | Authored and Co-authored Publications                          | . 153 |  |

| A                      | A2.                                             | C Programming Language for 32-bit LNS Subtraction              | . 154 |  |

| A                      | A3. VHDL Model for 32-bit LNS Add/Subtract Unit |                                                                |       |  |

## **LIST OF FIGURES**

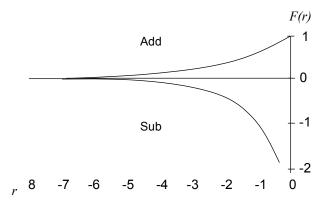

| Figure 1-1 : LNS addition and subtraction functions.                             | 3  |

|----------------------------------------------------------------------------------|----|

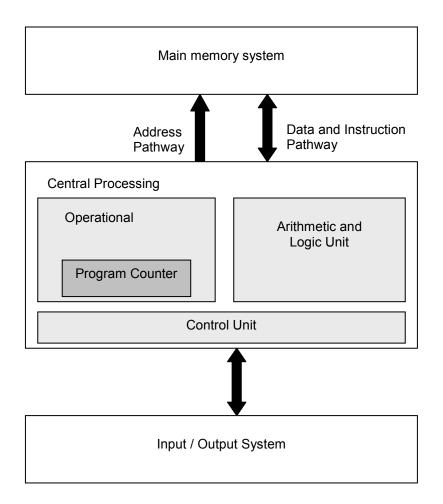

| Figure 2-1: Main components of typical computer architectures                    | 9  |

| Figure 2-2: Basic components of single-precision format.                         | 10 |

| Figure 2-3: LNS format [7].                                                      | 12 |

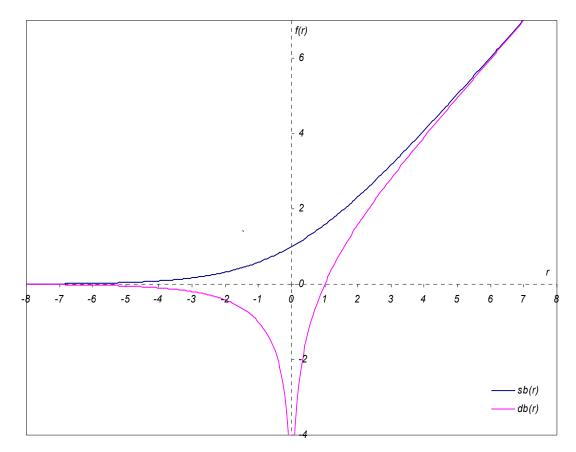

| Figure 2-4: Transcendental functions $s_b(r)$ and $d_b(r)$ .                     | 16 |

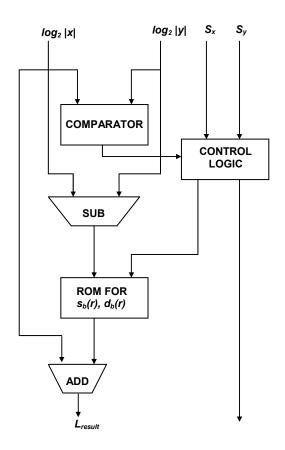

| Figure 2-5: LNS adder/subtractor based on direct lookup table                    | 18 |

| Figure 2-6: LNS adder implemented using linear interpolation                     | 20 |

| Figure 2-7: Coleman's LNS implementation.                                        | 24 |

| Figure 2-8: Bipartite table architecture                                         | 25 |

| Figure 2-9 : Concept of the hybrid number system processor                       | 29 |

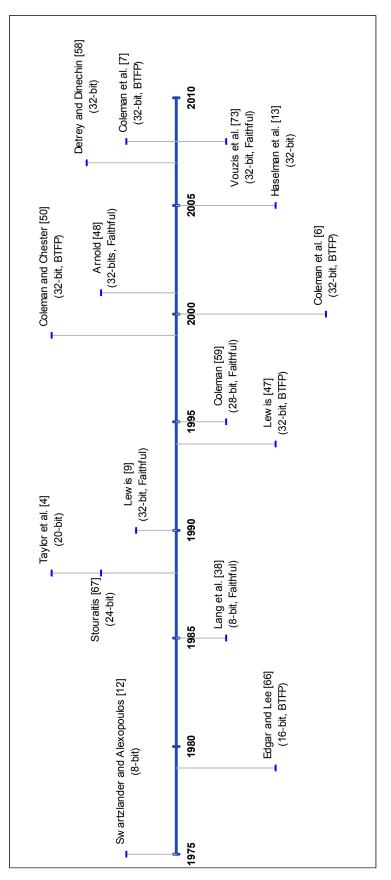

| Figure 2-10 : LNS trends vs time.                                                | 34 |

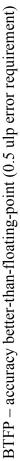

| Figure 3-1 : Simulator design for the LNS addition and subtraction.              | 46 |

| Figure 3-2 : Basic circuit design flow.                                          | 47 |

| Figure 3-3 : Synopsys synthesis design flow [78]                                 | 49 |

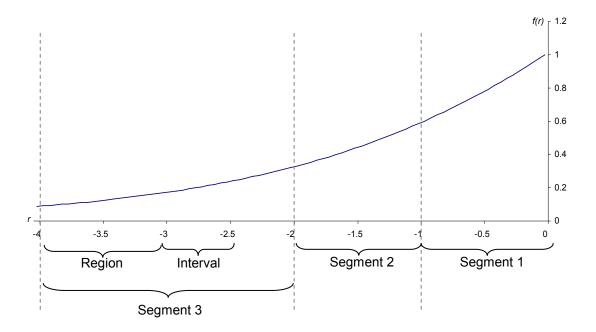

| Figure 4-1 : Partitioning concept for addition and subtraction functions         | 53 |

| Figure 4-2 : Descriptions of interval, region and segment                        | 53 |

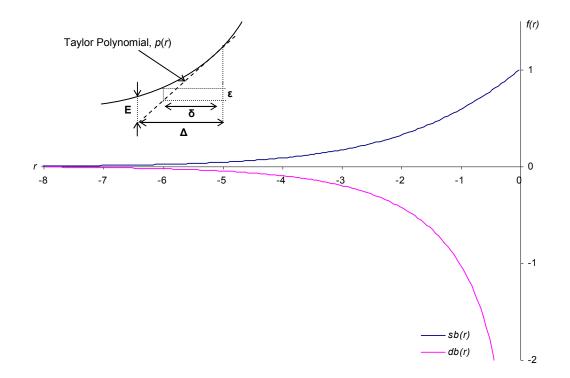

| Figure 4-3 : Function approximation method for ELM.                              | 55 |

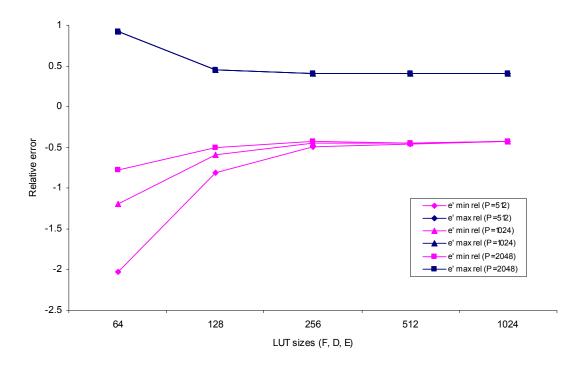

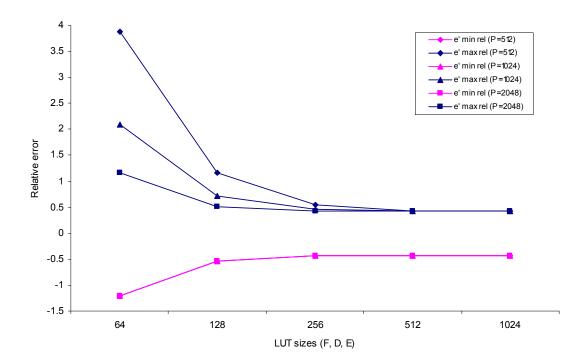

| Figure 4-4 : Approximation error for the addition operation of the ELM unit      | 59 |

| Figure 4-5 : Approximation error for the subtraction operation of the ELM unit   | 59 |

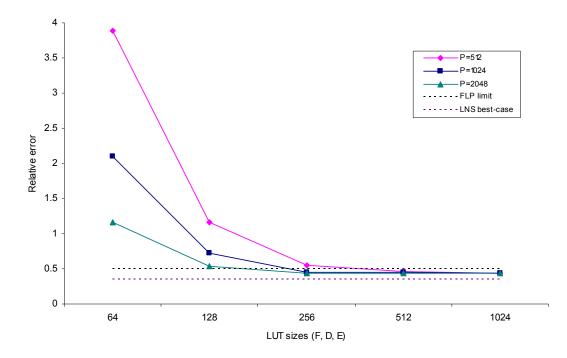

| Figure 4-6 : Worst-case error of the ELM unit                                    | 60 |

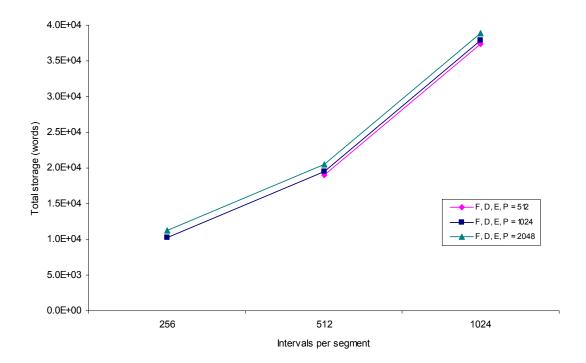

| Figure 4-7 : Total storage requirement for the worst-case error within FLP limit | 60 |

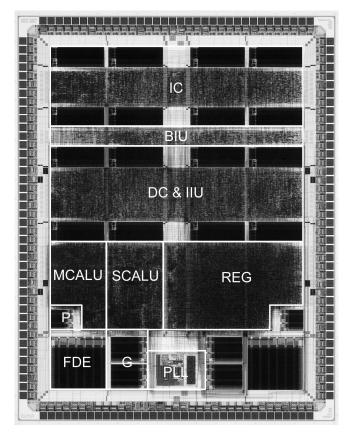

| Figure 4-8 : Die plot of ELM.                                                    | 62 |

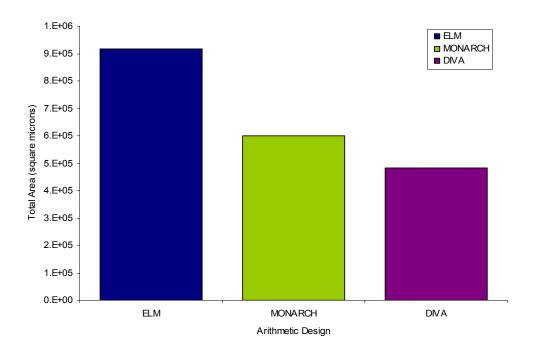

| Figure 4-9 : Total silicon area between ELM, DIVA and MONARCH                    | 65 |

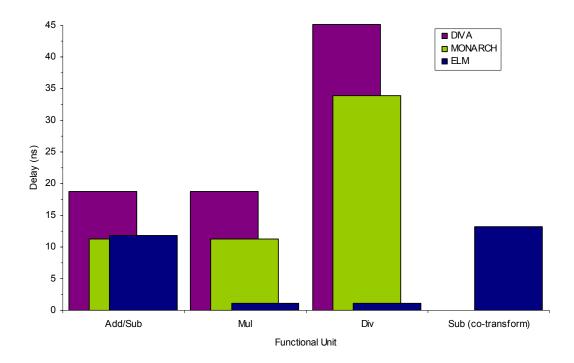

| Figure 4-10 : Delay between ELM, DIVA and MONARCH                                | 65 |

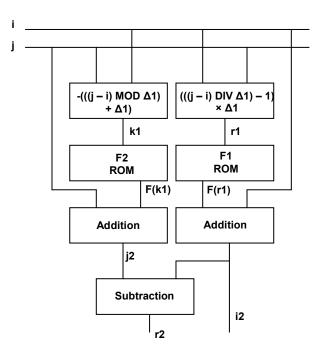

| Figure 5-1 : ELM's co-transformation architecture.                               | 68 |

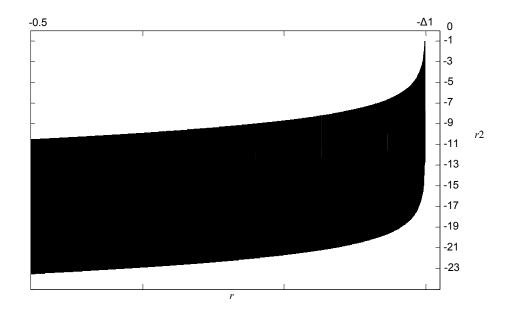

| Figure 5-2 : Value of $r2$ for $-0.5 < r < -\Delta 1$                            | 69 |

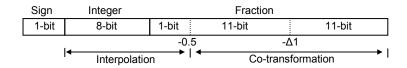

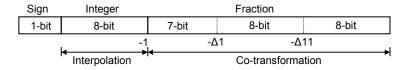

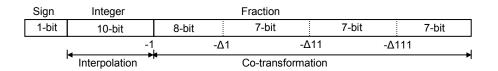

| Figure 5-3 : Bit partitioning scheme for first-order co-transformation           | 69 |

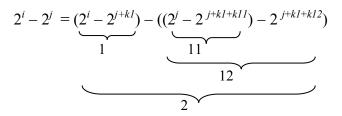

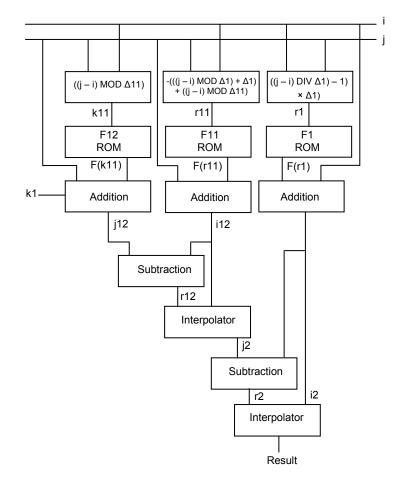

| Figure 5-4 : Conceptual arrangement of second-order co-transformation            | 73 |

| Figure 5-5: Bit partitioning scheme of second-order co-transformation           | 73    |

|---------------------------------------------------------------------------------|-------|

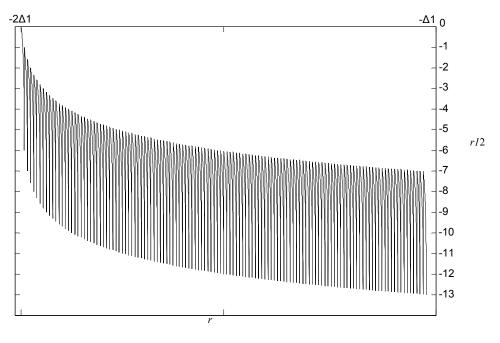

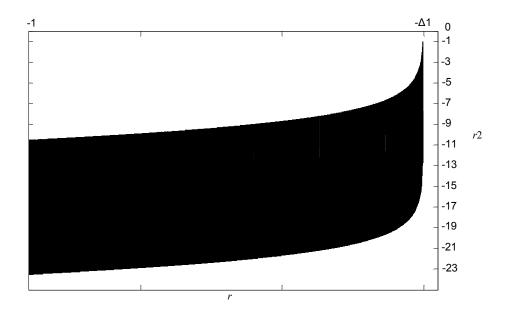

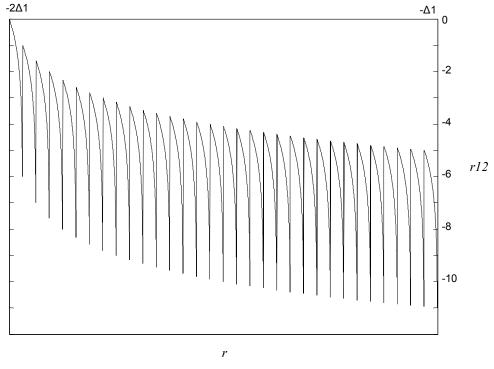

| Figure 5-6 : Value of $r12$ for $-2\Delta l < r < -\Delta l$ .                  | 75    |

| Figure 5-7 : Value of $r^2$ for $-1 < r < -\Delta I$                            | 75    |

| Figure 5-8 : The worst-case relative error of the proposed architecture.        | 79    |

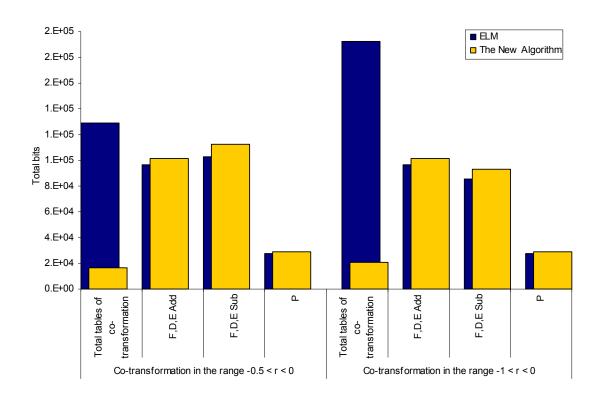

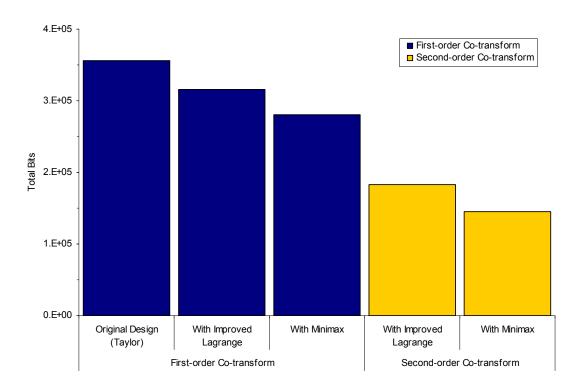

| Figure 5-9 : Comparison of the total tables between ELM and new algorithm       | 81    |

| Figure 5-10: Worst-case error between ELM and the new algorithm                 | 82    |

| Figure 5-11 : Delay between ELM and the new algorithm                           | 82    |

| Figure 6-1 : Linear interpolation.                                              | 86    |

| Figure 6-2 : Illustration of linear Taylor approximation error.                 | 88    |

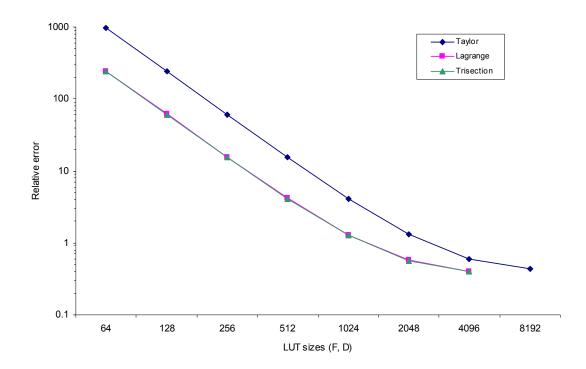

| Figure 6-3 : Worst-case error of linear Taylor approximation                    | 88    |

| Figure 6-4 : Illustration of linear Lagrange interpolation                      | 90    |

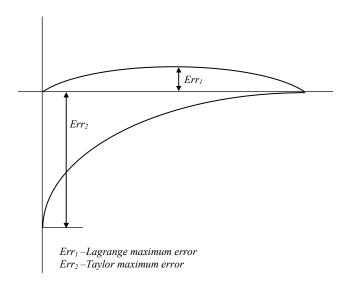

| Figure 6-5 : Comparison of maximum error in Taylor and Lagrange                 | 90    |

| Figure 6-6 : Worst-case error of linear Lagrange interpolation.                 | 93    |

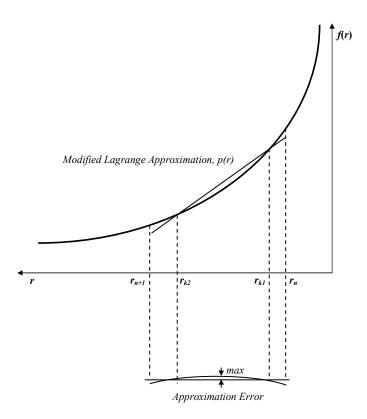

| Figure 6-7 : Illustration of modified linear Lagrange interpolation.            | 94    |

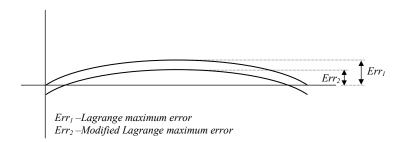

| Figure 6-8 : Illustration of maximum error between Lagrange and modified vers   | sion. |

|                                                                                 | 94    |

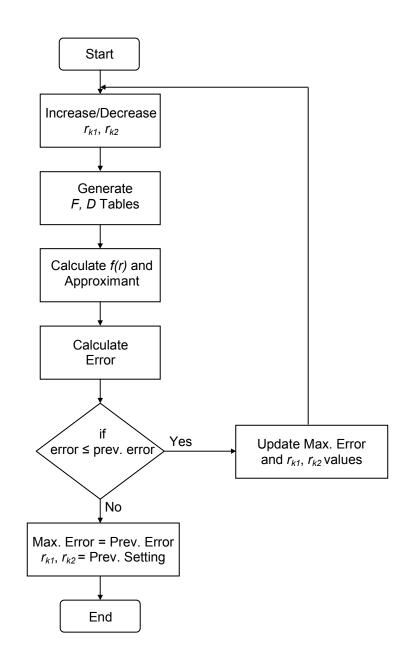

| Figure 6-9 : Flow diagram for selection of $r_{k1}$ and $r_{k2}$                | 95    |

| Figure 6-10 : Worst-case error of modified linear Lagrange interpolation        | 97    |

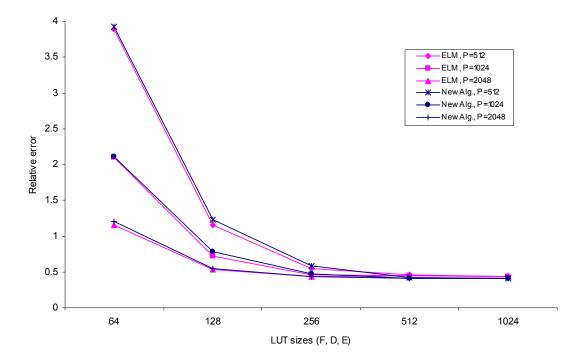

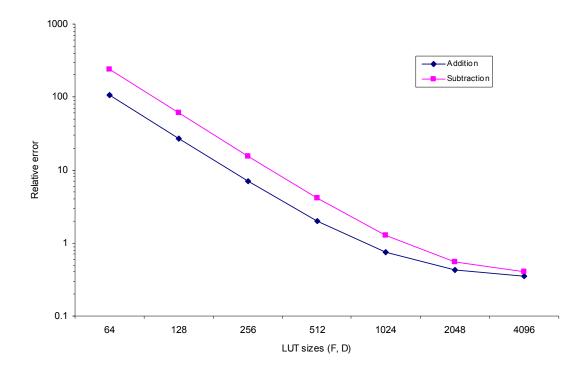

| Figure 6-11 : Worst-case error of linear interpolator.                          | 99    |

| Figure 6-12 : Worst-case error of Lagrange interpolation using error correction |       |

| algorithm.                                                                      | 104   |

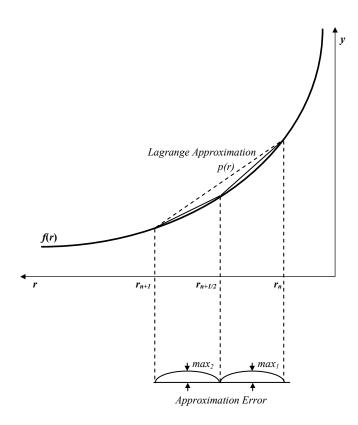

| Figure 6-13 : Partitioning the interval based on Lagrange interpolation         | 105   |

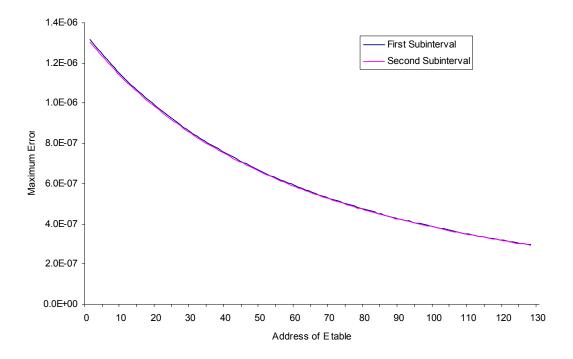

| Figure 6-14 : Maximum errors of two adjacent subintervals when executing        |       |

| subtraction in the region $-2 < r < -1$ .                                       | 106   |

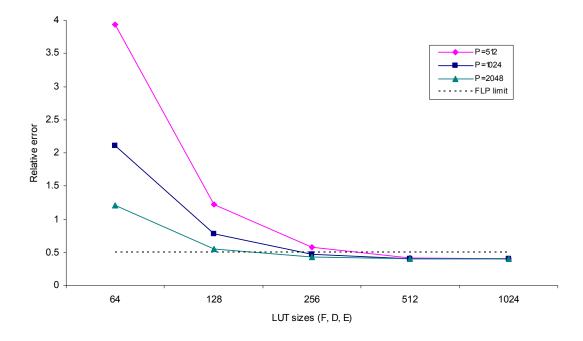

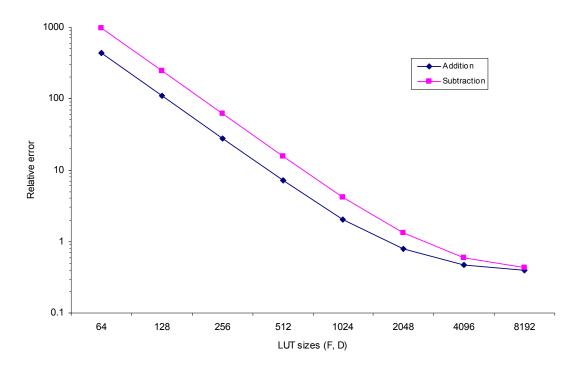

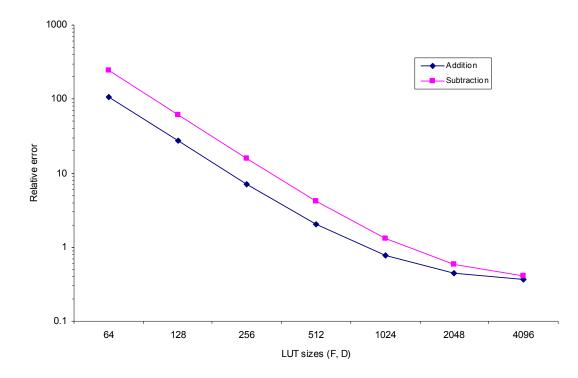

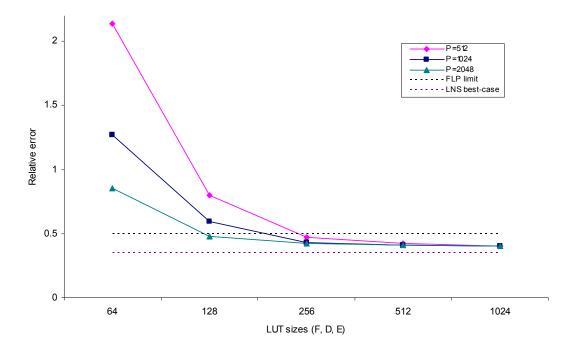

| Figure 6-15 : Storage requirement for 32-bit LNS addition and subtraction       | 116   |

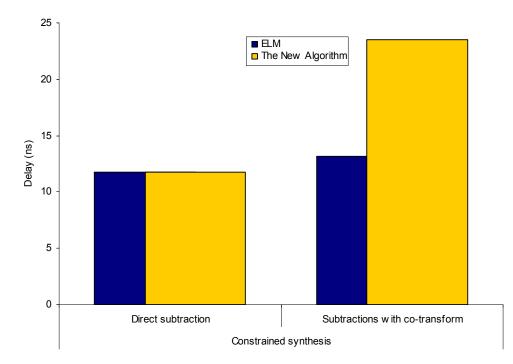

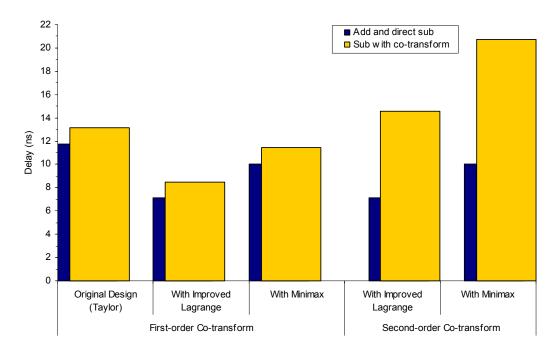

| Figure 6-16 : Delay times for 32-bit LNS addition and subtraction.              | 117   |

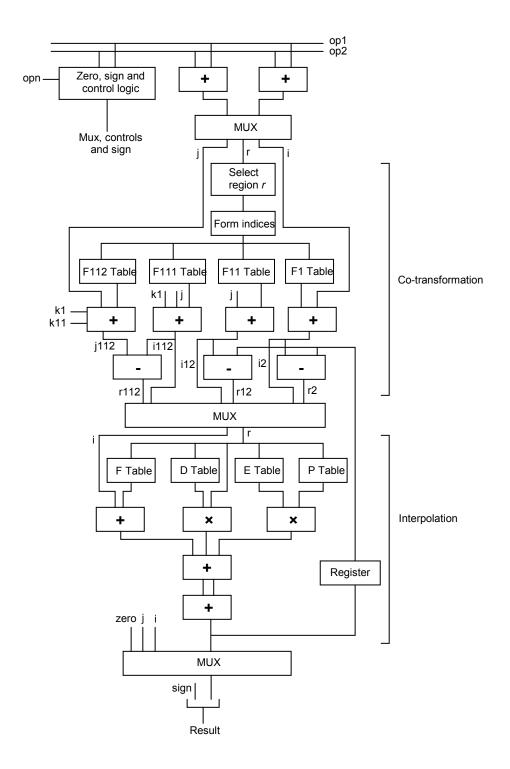

| Figure 7-1 : Conceptual arrangement of the LNS arithmetic unit                  | 121   |

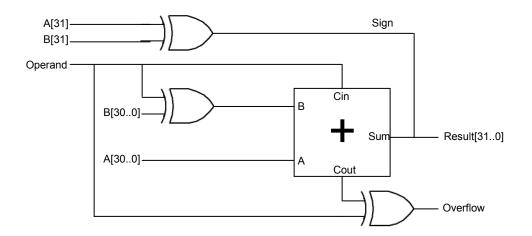

| Figure 7-2 : Multiply/Divide hardware implementation.                           | 122   |

| Figure 7-3 : The hardware implementation of the LNS add/sub unit.               | 124   |

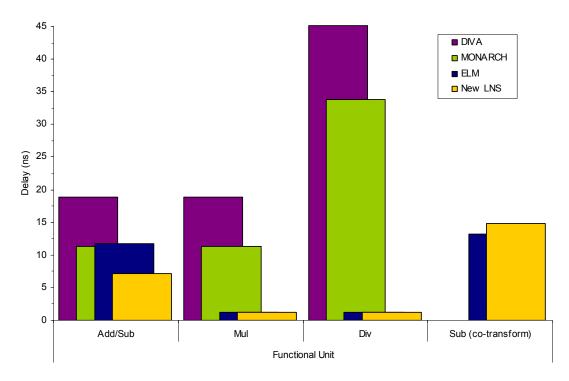

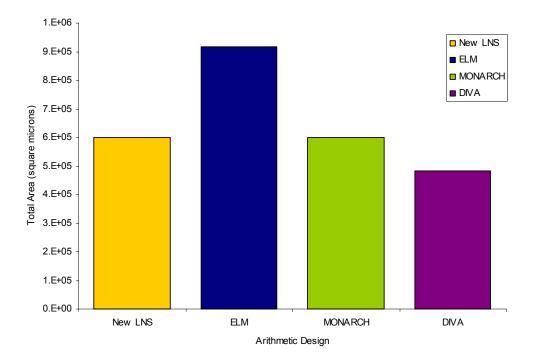

| Figure 7-4 : Delays in nanoseconds and cycles of four different arithmetic      |       |

| implementations.                                                                | 127   |

| Figure 7-5 : Silicon areas ( $\mu m^2$ ) in 32-bit arithmetic implementations   | 128 |

|---------------------------------------------------------------------------------|-----|

| Figure 8-1 : Conceptual arrangement of the third-order co-transformation concep | t.  |

|                                                                                 | 134 |

| Figure 8-2 : Bit partitioning scheme of the third-order format.                 | 134 |

| Figure 8-3 : Value of $r12$ for $-2\Delta l < r < -\Delta l$ .                  | 135 |

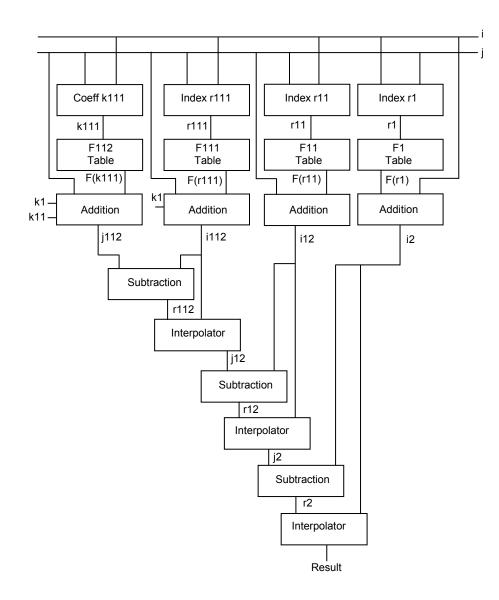

| Figure 8-4 : The hardware implementation of the LNS addition and subtraction ir | 1 a |

| 40-bit format                                                                   | 140 |

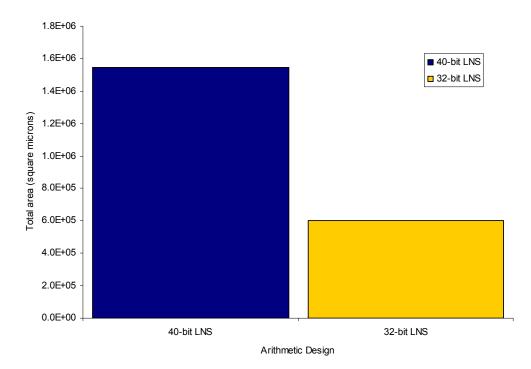

| Figure 8-5 : Delays of a 32-bit and 40-bit LNS designs                          | 142 |

| Figure 8-6 : Silicon areas in 32-bit and 40-bit LNS.                            | 142 |

## LIST OF TABLES

| Table 2-1: Values represented in the 32-bit FLP format                                | 1 |

|---------------------------------------------------------------------------------------|---|

| Table 2-2 : Summary of the LNS techniques.    3                                       | 3 |

| Table 3-1 : Best case theoretical errors.    4                                        | 0 |

| Table 3-2 : Simulation variables for the interpolator.    4                           | 5 |

| Table 3-3 : Operating conditions setting                                              | 8 |

| Table 4-1 : Segments and $\Delta$ in the ELM system                                   | 2 |

| Table 4-2 : The worst-case error of the ELM unit.    5                                | 8 |

| Table 4-3 : ELM interpolation memory requirements.    6                               | 1 |

| Table 4-4 : Delay times and total device area of ELM                                  | 3 |

| Table 4-5 : Delay and area of FLP arithmetic unit at 266 MHz                          | 4 |

| Table 5-1 : ELM co-transformation memory requirements.    7                           | 0 |

| Table 5-2 : Second-order co-transformation memory requirements.    7                  | 6 |

| Table 5-3 : The worst-case error of the optimised architecture.    7                  | 8 |

| Table 5-4: Total storage for the new algorithm                                        | 9 |

| Table 6-1 : Error of linear Taylor approximation                                      | 9 |

| Table 6-2 : Error of linear Lagrange approximation.    9                              | 2 |

| Table 6-3 : Error of modified linear Lagrange approximation                           | 6 |

| Table 6-4 : Linear interpolator storage requirements.    9                            | 8 |

| Table 6-5 : Error of Lagrange interpolation using error correction algorithm 10       | 3 |

| Table 6-6 : Error of non-linear Lagrange interpolator based on the E table sharing    |   |

| format                                                                                | 8 |

| Table 6-7 : Error of non-linear Lagrange interpolator in the region $-32 < r < -1610$ | 9 |

| Table 6-8 : Total storage using the improved interpolator                             | 0 |

| Table 6-9 : Error of the minimax interpolation.    11                                 | 1 |

| Table 6-10 : Total storage using the minimax arrangement                              | 2 |

| Table 6-11 : Error of ELM with improved Lagrange interpolator                         | 3 |

| Table 6-12 : Total storage of ELM with improved Lagrange interpolator                 | 4 |

| Table 6-13 : Error of ELM with minimax interpolator.    11                            | 5 |

| Table 6-14 : Total storage of ELM using the minimax arrangement                       | 5 |

| Table 7-1 : Delay times and total device area of 32-bit LNS arithmetic unit   | . 126 |

|-------------------------------------------------------------------------------|-------|

| Table 8-1 : Error of Lagrange interpolation.                                  | . 137 |

| Table 8-2 : Error of improved Lagrange interpolation.                         | . 137 |

| Table 8-3 : Total storage for the LNS 40-bit format.                          | . 138 |

| Table 8-4 : Delay times and total device area of a 40-bit LNS arithmetic unit | . 141 |

### **1. Introduction**

### **1.1. Motivation for the Research**

The need for high-performance digital signal processing (DSP) in the area of image processing, computer graphics and robotics is highly demanding. High speed architecture allows DSPs to execute many operations with the lowest delay [1]. Since performance is a driving factor behind the use of the DSP, advances in executing arithmetic functions are the key to advances in the performance of DSP processors. Consequently, techniques to improve the computation of arithmetic functions have always been an interesting topic of exploration, as expressed in [2].

Most of DSP algorithms need to be computed in real-time and require a wide dynamic range of numbers. During the early stages of DSP, the fixed-point (FXP) number system was employed as the maths unit inside the DSP processor. This system performs well for high-speed applications whenever only limited precision is required by the application. Nevertheless, this implementation has a major limitation because of restricted accuracy, which is the result of finite word-length effects. Floating-point (FLP) DSP has therefore become an alternative used to overcome this restriction of precision of FXP architectures. Despite having a wide dynamic range, there are established international standards for FLP system [3]. One of the most efficient basic operations in existing high-speed FLP unit is the multiplication process. However, complex operations such as division and square root are often executed by software routines, and are possibly much slower. Moreover, arithmetic operations in FLP require a variable length of time due to the need for exponent alignment. As a result of this, DSP researchers have recently proposed a microprocessor based on the logarithmic number system (LNS) [4-7][94], which would guarantee superior performance in many arithmetic functions such as multiplication, division and square root.

LNS provides major advantages over FLP in terms of speed and accuracy in computing multiplication and division operations. This is because of the similarity of the architectures to perform these functions to FXP addition and subtraction. However, this inherent advantage was offset by the difficulty of implementing LNS addition and subtraction. Furthermore, it is also slow. Several authors have proposed techniques to improve this trade-off, and as a result the LNS is now able to operate with similar speed and accuracy to its FLP equivalent [6-11], despite its larger area. Due to these considerable achievements, research into LNS systems has been active ever since. Thus, it is of interest further to improve the LNS system relative to a FLP arithmetic unit.

#### 1.2. An Overview of the LNS

Over the past four decades the LNS system has been a topic of continuing interest within the computer arithmetic area. As mentioned in previous section, multiplication and division operations become FXP addition and subtraction respectively. Unlike FLP counterparts, these operations are trivial and fast. Nevertheless, implementing addition and subtraction operations can be the main bottleneck, the evaluation of the non-linear functions (1.1) and (1.2). For  $i = \log_2 x$ ,  $j = \log_2 y$ , r = j - i, and assuming  $j \le i$ :

$$\log_2 \left(2^i + 2^j\right) = i + \log_2 \left(1 + 2^r\right) \tag{1.1}$$

$$\log_2 \left(2^i - 2^j\right) = i + \log_2 \left(1 - 2^r\right) \tag{1.2}$$

The functions  $\log_2 (1 \pm 2^r)$ , generically referred to as F(r), are illustrated in Figure 1-1. In the earliest LNS design which is up to about 20-bit, the addition and subtraction function values can be stored directly in the lookup table. Beyond this, memory requirements become prohibitive, and instead the function is stored at intervals with intervening values obtained by interpolation. Typically, in constructing the LNS system, the objective has always been to keep within an FLP- equivalent error of 0.5 LSB, but this has not always been achieved. The problem is compounded by the singularity in the subtraction function, where the rapidly changing derivative as r approaches zero requires the use of successively smaller interpolation intervals that need a significant increase in storage, often to the point of impracticality. As well as that, applying the interpolation alone may also increase the delay of the LNS system.

Figure 1-1 : LNS addition and subtraction functions.

However, as presented in 2000, an alternative approach was taken in a different interpolation technique. Dealing with 32-bit words and maintaining FLP-equivalent accuracy, it offered a much shorter delay path than using conventional interpolation architecture. In this approach, an interpolation was not used near the singularity. Instead, a co-transformation was used in the case of any subtraction with r close to zero (> -0.5), which it converted to an equivalent subtraction with r well away from zero. This 32-bit LNS system was based on the combination of the interpolation and the co-transformation procedure, and offered marginally better performance, in terms of both speed and accuracy, than a leading commercial FLP unit at that time. Nonetheless, two 2048 words of lookup tables were involved in the arrangement of the co-transformation architecture. Meanwhile, the interpolator itself then required 1024 words for one of its lookup tables. In practice, utilising these large lookup tables in the system could eventually introduce significant complications in floor planning. Hence, elimination of these components would not only yield a more compact architecture, but undoubtedly also a faster design.

Inspired by the above, therefore, the major objectives of this thesis can be summarised as follows:

- present a new development in the algorithm of the co-transformation procedure which can offer substantial improvement in area.

- enhance the interpolation architecture by exploring various existing techniques as to reduce the total storage and the delay of the system.

- demonstrate that the new LNS system will achieve much greater benefits in cost, speed and accuracy in comparison with FLP arithmetic units.

### **1.3.** Contribution of the Thesis

The following points summarise the main contributions of the thesis.

- A novel approximation method, known as a second-order cotransformation procedure, is introduced in the crucial singularity region for performing the LNS subtraction function. Apart from the capability to sustain the same accuracy as FLP, implementing this new approach in conjunction with the existing interpolator reduces the total tables to 73% of the former LNS design. However, the proposed technique suffers from an increase in delay because it requires the interpolator to be used twice.

- An improvement in the interpolator design by reworking Chester's experiments [84] is proposed when computing the LNS addition and direct (i.e. non- co-transformed) subtraction. When merged with the second-order co-transformation, it yields a further reduction in total tables to 51% of previous LNS design. Through this new arrangement, the tables can now be readily synthesised in logic as a result of being smaller in size, for not more than 512 words. Consequently, this can contribute to a reduction in delay to 60% of the original LNS design when computing addition and

direct subtraction. For subtractions with co-transformation, delay only increases by 12% compared to the previous work.

- An analysis is conducted between the new LNS design and equivalent FLP arithmetic units built using similar process technology. In terms of delay, the new LNS can be performed in 63% of the FLP time for executing addition and direct subtraction. Co-transformed subtractions require 131% of the FLP time but this is unlikely to be of great significance because it occurs in only a few percent of the total additive operations. Multiplication completes with 10% and division 3% of the FLP delays. In terms of total area, the new LNS can be built with fractionally less silicon, and worst-case accuracy is better than that of FLP arithmetic.

- At present, little work has been reported applying LNS design to wordlengths longer than 32-bit. The design and requirements of long format LNS arithmetic unit are therefore examined briefly in this thesis. The cotransform is developed further for this purpose.

### 1.4. Structure of the Thesis

The fundamental basis of computer arithmetic architecture and details of the FLP and LNS number systems are reviewed in Chapter 2. Previously published LNS designs are also discussed and analysed in terms of various aspects such as their design procedures, performance and suitability for DSP applications.

When evaluating and measuring the performance of the LNS system, several elements need to be considered, either the metrics required for measurement or the design methodology adopted to verify the design. Therefore, Chapter 3 explains the metrics involved for performance estimation during the simulation and synthesis processes. Besides that, the design flows of the simulation and synthesis procedures are also elaborated in detail.

In Chapter 4, the recent 32-bit arithmetic implementations are reviewed intensively. This includes exploring the leading published design of the LNS system before reconstructing the architecture using similar approaches as described in its original work. In addition, several FLP devices are also examined. These devices are independently designed and have been published. The performance of these arithmetic units is reported in this chapter, and later it will then be used for comparison with the new LNS system.

Chapter 5 presents a new development of the co-transformation architecture for executing LNS subtraction function, exploiting the previously published cotransformation concept and significantly elaborating on its architecture. The simulation and synthesis results of the proposed design are also reported in evaluating its efficiency in the light of previous work.

The different existing function approximation schemes are described in Chapter 6. An improved technique for the interpolator module is introduced. Accuracy and total area analyses are carried out and documented on the basis of worst-case error and total size of lookup tables respectively. It is shown that the improved version is able to provide a great reduction in total tables whilst sustaining accuracy within FLP limits.

The implementation of the suggested LNS arithmetic unit is explained in Chapter 7. The synthesis process is performed to determine the performance of the new LNS architecture in terms of speed and total silicon area, before a comparative study against FLP units and previous LNS design is discussed.

There is a lack of work on long word-length LNS, and a short survey of a possible long format system is therefore outlined in Chapter 8. This includes a proposal for another new co-transformation approach applicable to a long word-length system. Its implementation in logic gates and performance analysis against the standard 32-bit LNS number system are also described.

Finally, the main results of the thesis are summarised and conclusions are drawn in Chapter 9. Moreover, several possibilities for future work extending the present research are also offered.

# CHAPTER 2

### 2. Background and Previous Work

### 2.1. Introduction

In this chapter, the current body of knowledge relevant to the present research is extensively reviewed. The fundamental basis of the computer arithmetic unit is briefly described. An overview is given of FLP and LNS numbers formats, and computing arithmetic units based on these number systems are elaborated in detail. Previously published techniques used to execute the LNS addition and subtraction are discussed and compared in various respects, since these operations are the main bottlenecks in LNS system.

Speed, accuracy and area are the three crucial variables in the efficiency of LNS arithmetic unit. Thereby, the performance of existing LNS systems is evaluated so that the results could be used as a benchmark for the novel architecture introduced in this thesis. Finally, the LNS systems adopted in numerous DSP applications are concisely described.

### 2.2. Computer Arithmetic Unit

Conventionally, most computer architectures include three basic hardware subsystems, namely the central processing unit (CPU), main-memory system and input/output (I/O) system [12-14]. A CPU carries out instructions sequentially by performing two distinct procedures known as the fetch and execute cycles, where at least one operation is conducted at a time. The main-memory system plays the vital role of holding the programs that control the computer's operations. The I/O system represents the various devices that can exchange information with the outside world.

As presented in Figure 2-1, the computer arithmetic unit is a component of a CPU system. It is commonly combined with logic functions, hence constituting an arithmetic logic unit. This arithmetic unit deals with the arithmetic functions needed to support various computer instructions, and thus it is a very important part of digital computer organisation. Agrawal and Rao [15] describe the computer arithmetic unit as always having been considered the heart of a digital computer system. Among the arithmetic operations that can be computed are addition, subtraction, multiplication, division, square root, exponentiation, logarithmic functions, complementation (negation), incrementation or decrementation, equality and magnitude comparison and shift operations. These numeric functions, and especially adders and multipliers, are also implemented in diverse ways in the data paths of digital signal processors which then form dedicated integer units and multiply-accumulate (MAC) structures. Moreover, adders, incrementers or decrementers, and comparators are often used for address and flag generation purposes in controllers.

Because the applications of arithmetic operations are manifold, much effort has been devoted to designing hardware algorithms and circuits to enhance the speed of these numeric operations [7, 16-18]. More recently, since the inception of portable electronic devices which require small and lightweight units, the demand for not only reduction in power consumption, but also the total area of the systems has increased dramatically. Therefore, the development of algorithms that can reduce delays and total area in arithmetic operations is a matter of great concern in today's arithmetic architecture [19-21].

The four basic numeric operations (addition, subtraction, multiplication and division) of the computer arithmetic unit are critically investigated in this thesis. New algorithms based on LNS which aims specifically at addition and subtraction functions are introduced which can significantly improve the overall performance of an arithmetic system.

Figure 2-1: Main components of typical computer architectures.

#### 2.3. Number Systems Representation

Integers and real numbers, also expressed as fractions, are the most common number system representations used in digital computers [14]. Traditionally, integers have been represented using FXP number systems that offer limited range and precision. When dealing with money and inventories in business and commercial activities, the use of integer numbers is adequate in estimating the results of calculations given the fact that usually only two places to the right of the decimal point will be occupied. Furthermore, in control problems which deal with measurements in degrees, minutes and seconds, the ranges involved can also fit into the FXP system [22]. Conversely, difficulties arise in scientific applications such as those needed by astronomers,

engineers and physicists. The formulae used to represent length and mass, for instance, repeatedly consider differences between very large or very small numbers, and thus the FXP system fails [23]. In such situations real numbers have to be adopted to compute the functions.

Over the years, many computer manufacturers have implemented FLP system to represent real numbers [14, 24, 25]. An FLP system is capable of offering a wide dynamic range which can accommodate extremely large numbers and high precision for very small numbers. Nevertheless, over the last four decades, researchers have explored the use of LNS as an alternative to signify real numbers in computer systems [4, 6, 7, 26]. Despite the lack of standard formats, the accurate and inexpensive implementation of multiplication and division operations in LNS which only use FXP addition and subtraction, makes it more attractive compared to FLP [27]. In addition to higher speed, LNS has also been the subject of close attention for numerous applications as a result of its inherently better worst-case relative error compared to FLP [28].

In this thesis, LNS numbers are the main subject of the research, and the FLP format is also used for comparison purposes. Therefore, the basic fundamental features of both formats are described briefly below.

### 2.3.1. Floating Point

The IEEE 754 [3] is a standard used to represent FLP numbers and has been divided into single-precision format with 32-bit width, and double-precision format with 64-bit width. In this thesis, only single-precision format is considered. The three basic components of FLP numbers are the sign, exponent and mantissa as shown in Figure 2.2.

| Sign    | Exponent | Mantissa |

|---------|----------|----------|

| (1-bit) | (8-bit)  | (23-bit) |

Figure 2-2: Basic components of single-precision format.

The number denoted by the single-precision format is [29]:

value =

$$(-1)^{s}2^{e} \ge 1.f$$

(normalized) when  $E > 0$  else (2.1)

$$= (-1)^{s} 2^{-126} \times 0.f$$

(denormalized) (2.2)

where

The range of positive FLP numbers which can be split into normalized numbers (which preserve the full precision of the mantissa), and denormalized numbers (which occur when the exponent is all zeros, but the fraction is non-zero) are between  $\pm 2^{-126}$  to  $(2-2^{-23}) \cdot 2^{127}$  and  $\pm 2^{-149}$  to  $(1-2^{-23}) \cdot 2^{-126}$  respectively. Table 2-1 summarises the values than can be defined in the FLP system.

Table 2-1: Values represented in the 32-bit FLP format.

| S    | e     | f            | Value                                    |

|------|-------|--------------|------------------------------------------|

|      | 0     | 0            | +0                                       |

| 0    | Ŭ     | Any non-zero | Positive Denormal, $0 f \cdot 2^{-126}$  |

| Ŭ    | 1 254 | Any          | Positive Normal, $1 f \cdot 2^{e}$       |

|      | 255   | 0            | +∞                                       |

|      | 0     | 0            | -0                                       |

| 1    | Ū     | Any non-zero | Negative Denormal, $-0.f \cdot 2^{-126}$ |

| 1    | 1 254 | Any          | Negative Normal, $-1.f \cdot 2^{e}$      |

|      | 255   | 0            | -∞-                                      |

| Any  | 255   | 00'01 01'11  | SNaN                                     |

| inty | 200   | 10'00 11'11  | QNaN                                     |

#### 2.3.2. Logarithmic Number System

In contrast with FLP numbers, LNS includes neither an integer exponent nor separate linear mantissa. It is much simpler because it uses a single scaled exponent and can be represented by [30]:

$$X = (-1)^{s} \times 2^{mf}$$

(2.3)

where s, m and f indicate sign, integer and fractional bits respectively. Although there is no commonly accepted standard for the LNS format, the most widely used format is shown in Figure 2-3.

| Sign    | Fixed-Point Logarithmic Value |                  |  |

|---------|-------------------------------|------------------|--|

| (1-bit) | Integer                       | Fractional       |  |

| (1-011) | ( <i>m</i> -bit)              | ( <i>f</i> -bit) |  |

Figure 2-3: LNS format [7].

Typically, base-2 logarithms are used in LNS computations though in principle any base can be used. When the real numbers represented are signed, LNS has a maximum and minimum range between  $2^{-128}$  to  $\approx 2^{+128}$ ,  $\approx 2.9E - 39$  to 3.4E + 38. A special arrangement of bits is used to indicate the real number zero.

### 2.4. Floating-Point Algorithms

The basic algorithms for arithmetic operations using FLP numbers are conceptually simple. Nevertheless, careful attention must be paid during hardware implementations in order to ensure correctness and to prevent excessive loss of precision [31].

Addition and subtraction are a lot more complex than the other FLP operations. In the following description, elementary binary FLP addition is explained, since subtraction can be converted to addition merely by flipping the sign of the subtrahend. In theory, addition is defined as:

$$(\pm m_1 \times 2^{e_1}) + (\pm m_2 \times 2^{e_2}) = \pm m \times 2^{e_1}$$

(2.4)

where m,  $m_1$  and  $m_2$  are the mantissas and e, e1 and e2 are the exponents. Assuming  $e1 \ge e2$ , the exponents of the addends have to be made equal by right-shifting (divided by a power of two) the mantissa of the smaller number,  $m_2$ , by as many bits as its exponent, e2, is increased. Then the shifted mantissa,  $m_2$ , will be added to the other mantissa,  $m_1$ . After addition, the resulting mantissa is normalized back to the mantissa interval by multiplying it with the corresponding exponent, e1, as presented in (2.5) [32].

$$(\pm m_1 \times 2^{e_l}) + (\pm m_2 \times 2^{e_2}) = (\pm m_1 \times 2^{e_l}) + \left(\frac{\pm m_2}{2^{e_l - e_2}} \times 2^{e_l}\right)$$

$$= \left(\pm m_1 \pm \frac{m_2}{2^{e_l - e_2}}\right) \times 2^{e_l}$$

$$= \pm m \times 2^{e_l}$$

(2.5)

In contrast, binary FLP multiplication is a relatively straightforward procedure whereby the mantissas,  $m_1$  and  $m_2$ , are first multiplied together [23]. Then, the exponents, *e1* and *e2*, are added. After multiplication has been computed, the product obviously has twice as many digits as the original operands. Hence, postnormalization procedure is needed to adjust the mantissa and the exponent of the result. Generally, the normalization process is executed by left-shifting the mantissa until it reaches the first bit 1. Simultaneously, for each bit left-shifted, the exponent must be reduced by 1. Therefore, the binary FLP multiplication is described as:

$$(\pm m_1 \times 2^{e_1}) \times (\pm m_2 \times 2^{e_2}) = \pm (m_1 \times m_2) \times 2^{e_1 + e_2}$$

$$= \pm m \times 2^e$$

(2.6)

The operation of FLP division is like that of multiplication, conducted by dividing the mantissas and subtracting the exponents and therefore presented as:

$$(\pm m_1 \times 2^{el}) \div (\pm m_2 \times 2^{e2}) = \pm (ml \div m2) \times 2^{el \cdot e2}$$

$$= \pm m \times 2^e$$

(2.7)

In the case of division, the mantissas are first left-shifted according to their number of leading zeros. After being divided and subtracted for both mantissas and exponents, post-normalization is performed as in multiplication to produce the final result. Conceptually, division operations always consume a large proportion of area in any FLP system, therefore making it an inherently slow operation which should be used sparingly. Due to the fact that FLP division is an infrequent operation even in intensive FLP applications, many current architectures ignore its implementation [33, 34].

#### 2.5. Logarithmic Number System Algorithms

Typically, computer arithmetic unit conducts four major operations, namely addition, subtraction, multiplication and division. In LNS arithmetic, multiplication and division are trivial operations due to the fact that they have equivalent architectures to either FXP addition or subtraction as illustrated in (2.8) and (2.9). Moreover, these operations are more accurate and there is no quantization error, thus returning an exact result [35], where as FLP often yields a half-bit rounding error [36].

Generally in the LNS system, two real numbers, *x* and *y*, are used and can be represented by the FXP values  $i = \log_2 |x|$  and  $j = \log_2 |y|$ . In addition, an additional

bit is used to show the signs of x and y,  $S_x$  and  $S_y$ . Thus, multiplication and division are computed as:

Multiply:

$$L_1 = x \cdot y \rightarrow log_2 |L_1| = log_2 |x \cdot y| = log_2 |x| + log_2 |y| = i + j$$

(2.8)

where:  $S_{L1} = S_x \oplus S_y$

Divide:

$$L_2 = x \div y \rightarrow log_2 |L_2| = log_2 |x \div y| = log_2 |x| - log_2 |y| = i - j$$

(2.9)

where:  $S_{L2} = S_x \oplus S_y$

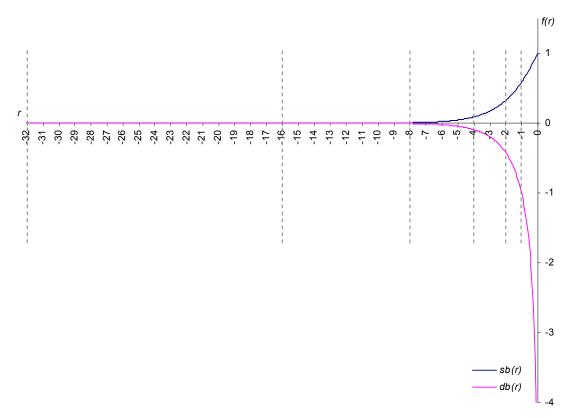

In contrast, LNS addition and subtraction become fairly complex procedures [26]. To perform these operations, Leonelli's algorithm [37] is used. The functions  $s_b(r)$ , for the addition algorithm (also known as Gaussian algorithm [38]), and  $d_b(r)$ , in the subtraction algorithm, are defined as:

$$s_b(r) = \log_2(1+r) = \log_2(1+2^r), \ r < 0 \tag{2.10}$$

$$d_b(r) = \log_2(1 - r) = \log_2(1 - 2^r), r < 0$$

(2.11)

Hence, these functions are plotted as in Figure 2-4.

Assuming that  $|x| \ge |y| > 0$  and let  $r = (log_2 |y| - log_2 |x|) = j - i$ , therefore addition and subtraction can be computed using:

Addition:

$$L_3 = x + y \rightarrow log_2 |L_3| = log_2 |x + y|$$

$$= log_2 |x (1 + (y/x))|$$

$$= log_2 |x| + log_2 |1 + (y/x)|$$

$$= log_2 |x| + log_2 |1 + (log_2 |y| - log_2 |x|)|$$

$$= i + log_2 |1 + 2^{i-i}|$$

$$= i + log_2 |1 + 2^r|$$

$$= i + s_b(r)$$

(2.12)

Figure 2-4: Transcendental functions  $s_b(r)$  and  $d_b(r)$ .

Subtraction:

$$L_4 = x - y \rightarrow log_2 |L_4| = log_2 |x - y|$$

$$= log_2 |x (1 - (y/x))|$$

$$= log_2 |x| + log_2 |1 - (y/x)|$$

$$= log_2 |x| + log_2 |1 - (log_2 |y| - log_2 |x|)|$$

$$= i + log_2 |1 - 2^{j-i}|$$

$$= i + log_2 |1 - 2^r|$$

$$= i + d_b(r)$$

(2.13)

It is clear that addition and subtraction operations are the main obstacle in an LNS system as a result of involving a lookup table in executing its non-linear function,  $s_b(r)$  and  $d_b(r)$ . Potentially, with an increase in the word-length of LNS numbers, it can suffer from the requirement of a large lookup table in computing the function.

Therefore, over three decades, different ways of improving the addition and subtraction functions have been proposed, and these can be classified into seven distinct categories as follows.

#### **2.5.1.** Direct Lookup Table

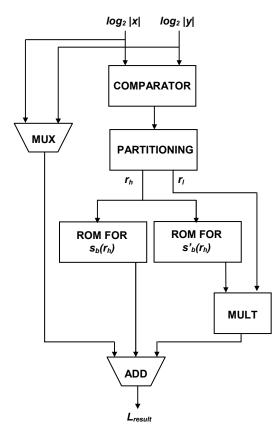

The earliest and simplest LNS architecture for addition and subtraction was introduced in 1975 [39]. This was a direct implementation of equations (2.12) and (2.13) using lookup tables or so called Read Only Memory (ROM) based hardware covering all possible values of  $s_b(r)$  and  $d_b(r)$ . The implemented structure based on this technique is as described in Figure 2-5.

In practice, the implementation of LNS add and subtract functions always has to limit the variable r to either positive or negative values. It is more usual to opt to restrict r to negative values because at a certain point (as shown in Figure 2-4), the functions of  $s_b(r)$  and  $d_b(r)$  have an output of zero or known as the *essential zero*. Consequently,  $s_b(r)$  and  $d_b(r)$  functions can yield a value that rounds to zero which is then easy to handle. As a result, the suggested procedure for addition and subtraction using the direct lookup table approach depends on two real numbers, x and y, as given below:

If

$$x \ge y \rightarrow r = j - i$$

:

Addition:  $L = i + log_2 | 1 + 2^r |$  (2.14)

Subtraction :  $L = i + log_2 | 1 - 2^r |$  (2.15)

If

$$y > x \rightarrow r = i - j$$

:

Addition :  $L = j + log_2 | 1 + 2^r |$  (2.16)

Subtraction :  $L = j + log_2 | 1 - 2^r |$  (2.17)

Figure 2-5: LNS adder/subtractor based on direct lookup table.

Using the technique considered here, the ROMs for  $s_b(r)$  and  $d_b(r)$  must each contain  $2^f$  words of *f* bits each, and hence the total storage required can be computed as  $f \cdot 2^{f+1}$ . With precision set to only 8-bit, a total of 4096 bits were achieved in [39] to compute LNS addition and subtraction. In evaluating the speed of the system, these operations were found to be approximately four times slower than conventional FLP methods. Although the direct lookup table approach has been successfully tested for a fast Fourier transform (FFT) application with the numbers rounded to 18-bit (plus sign bit) [40], it still yields an unreasonable size of ROM when it comes to long word-length numbers, especially at 32-bit, as a result of the required memory growing exponentially when the numbers increase linearly. In 1979, a state-of-the-art microcomputer, the FOCUS [41], was introduced that utilised the LNS system based on the direct lookup table method. It was reported that average execution cycles for 16-bit LNS add and subtract operations were 127 µsec and 125 µsec

respectively when the FOCUS system was implemented in an Intel 8085 processor. In addition, 23,632 bits were needed for storage requirements in this architecture.

### 2.5.2. Interpolation

The memory space limitations of LNS addition and subtraction using a direct lookup table approach makes its use questionable. In order to overcome this problem, another technique, interpolation, is often used.

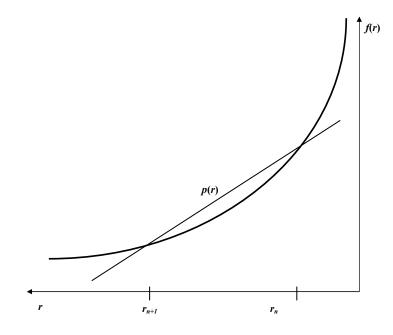

The direct interpolation technique [42] was first introduced to cater only for the addition algorithm,  $s_b$ , which requires a multiply unit in the hardware system. Using this technique, r is split into two parts,  $r_h$  and  $r_l$ , hence  $r = r_h + r_l$ .  $r_h$ encompasses the highest bits of the variable, whereas  $r_l$  represents the lowest bits. In the general case, the direct interpolation can be written as:

$$s_b(r) = s_b(r_h + r_l) \approx s_b(r_h) + C(r_h) \cdot r_l$$

(2.18)

where the slope  $C(r_h)$  can be chosen from various methods such as Lagrange. Memory usage can be reduced by increasing the lower bits,  $r_l$ , but the accuracy of the approximation decreases too. Likewise, when the size of  $r_l$  increases, the same will happen with the size of the required multipliers. In effect, the use of an FXP multiplier can actually produce much higher costs, in terms of speed and area, which along with the greater expense due to its size can make the system even slower and larger. Therefore, direct interpolation in LNS is often limited to either first- or second-order coefficients.

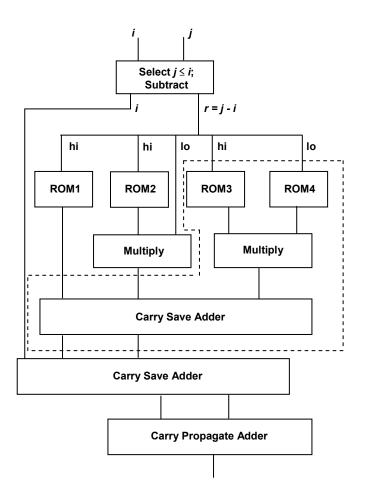

Another notable interpolation technique was proposed by Taylor in 1983 [43], which is referred to here as linear interpolation. Taylor approximates  $s_b(r)$  as:

$$s_{b}(r) = s_{b}(r_{b}) + s_{b}(r_{b}) \cdot r_{l}$$

(2.19)

As shown in Figure 2-6, with only addition operation shown for clarity, the linear interpolation method still needs a multiplier to compute the function. On top of that, two ROMs were introduced. Arnold *et al.* in 1988 [44] suggested a refined version of the interpolation procedure where they merge the direct interpolation method with the linear interpolation scheme. With the modified architecture, only one ROM is required and a shifter using powers of two is deployed as an alternative to the multiplier. However, once again, this technique is not feasible for the subtraction algorithm.

Figure 2-6: LNS adder implemented using linear interpolation.

A suggested interpolation procedure which can offer a wide dynamic range with an independently choosable signal-to-noise ratio was proposed by Henkel in 1989 [45]. The method was based on the Chebyshev approximation with unequally spaced partition points. This approach leads to significant memory reductions but still holds for the addition algorithm only. Note that there is a difference between the addition and subtraction algorithms in the  $s_b(r)$  and  $d_b(r)$  functions. While  $s_b(r)$  is well-behaved,  $d_b(r)$  has a singularity when r approaches zero (the function tends to - $\infty$ , as shown in Figure 2-4). This can cause a large memory to be required to approximate the  $d_b(r)$  function and it is therefore impractical to rely on the interpolation scheme to execute this operation. Furthermore, unacceptable error may also be introduced whenever interpolation is used in this particular region unless partitioning is applied.

A separate proposal in 1994 by Lewis [46] involved the use of a high-order coefficient in the interpolator function, also known as quadratic interpolation. In this technique, a novel scheme using an interleaved memory is introduced which can reduce the storage requirements when compared with linear interpolation. With design up to 32-bit and the accuracy of addition within FLP limits, the critical speed path of the architecture consists of a ROM, two multipliers, three barrel shifters and three stages of adders. Later in 2000, Coleman *et al.* [6] extended the idea of linear interpolation using an error correction algorithm for both addition and subtraction functions. This interpolation scheme for subtraction was incorporated with the newly proposed co-transformation method which will be further elaborated in Section 2.5.5 below. Using Coleman's technique, the speed path comprises of a ROM, a multiplier and three stages of addition process.

Aiming to minimise memory requirements and system complexity, therefore, Arnold [47] recommended in 2001 a multiple-of-four partitioning technique in quadratic interpolation. Nevertheless, even though the proposed address-generation circuit was simpler than that of Lewis and Coleman, this was unfortunately at the expense of a slight increase in approximation error. Still in 2001, Arnold [48] illustrated yet another improved version of Lewis's method [46], now with the advantage that only a single multiplication was required for addition and subtraction algorithms. The implementation of this technique is believed to have either similar or lower memory use than a previous interpolator [49], with corresponding accuracy better than linear interpolation. On the other hand, Fu et al. in [8, 28] described that the implementation of the minimax approximation for the interpolation process could significantly improve the total tables over Lewis and Coleman methods. However, its worst-case delay was higher than Coleman due to the speed path consists of a ROM, two multipliers and three levels of adders.

### 2.5.3. Table Partitioning

Generally, partitioning is often combined with an interpolation scheme. Instead of using a single uniform partition (direct lookup table approach) [39], the technique can be realised by segregating the ROM into various sizes of interval mapping with the domain function of addition and subtraction algorithms. These intervals are distributed in smaller regions with similar widths of partition endpoints, hence providing substantial savings in ROM area.

In 1998, Taylor *et al.* [4] suggested a 20-bit LNS processor using a table partitioning method for both addition and subtraction functions. The range of r was divided into a number of smaller intervals with partition endpoints set at integer multiple-of-one for all regions less than -1. For regions close to zero, the multiple-of-half format was employed (i.e -1 < r < -0.5, -0.5 < r < 0), resulting in two smaller sizes of ROM. In total, 10 ROMs were used to accommodate  $s_b(r)$  and  $d_b(r)$  functions with total size of about 83.55 kbits, which is 75% less than in the direct lookup table implementation. However, the large size of these tables makes the practical limit for logarithmic arithmetic about 12-16 bits of fractions. Using Taylor approach, it was estimated that LNS add and subtract operations could be completed in 92 ns, a similar value to equivalent FLP processors in those days.

Meanwhile, Stouraitis [50] produced an enhanced version of Taylor's architecture by compressing the table lookup address space and inserting pipelining registers in the addition and subtraction data path. Therefore, with suggestion at a 24-bit LNS processor, the time taken for addition and subtraction could be reduced to 40 ns. Nevertheless, this procedure required a hidden bit to locate the ROM address, which would have an impact on the total area of the system when extending its precision.

One of the most noteworthy partition techniques was presented by Lewis in 1990 [9] using a partitioning procedure concurrently with linear interpolation. An integer multiple-of-two format was adopted at each interval of r less than -1 for subtraction, and in all cases of region r for addition. For subtraction in the region -1 < r < 0, the powers of two format was proposed. As tabulated in [9], nearly 2660 kbits were required in total for a 32-bit LNS design, which was impractical for implementation in a single chip using the 3  $\mu$ m CMOS technology that was available at that time. The delay in the proposed method was assumed to be within two ROM accesses plus two FXP additions, which was slightly slower than the method in [4]. Thus, the implementation of this design might be unattractive for applications demanding high speed configuration.

In 1994, Lewis again [46] applied the table partitioning concept with an interleaved memory scheme. In the initial design, about 287 kbits of memory space were generated when using powers of two partition endpoints at each interval of r for addition and subtraction functions. Subsequently, an attempt was made by Lewis to minimise the area by rounding each table segment up to a multiple-of-eight, and thus only a total of 91 kbits of ROM were needed. Although efficient ROM size can be achieved through Lewis's technique, the introduction of two multipliers in this architecture can potentially increase the cost of the system, either in area or speed.

The other notable approach was suggested by Coleman *et al.* [6], using a partitioning scheme for error correcting interpolation with partition endpoints at powers of two for both addition and subtraction as depicted in Figure 2-7. For subtraction at the case -0.5 < r < 0, the co-transformation procedure was introduced. Using this architecture, 321 kbits of storage were required for a 32-bit LNS system. With application only to the addition algorithm, Arnold [47] presented the table partitioning method using a multiple-of-four format which then substantially diminished the total storage to one-third the size of Lewis [46] and one-sixth the memory of Coleman [6]. Regrettably, the implemented architecture exhibits a minor reduction in accuracy compared to a FLP system.

Figure 2-7: Coleman's LNS implementation.

# 2.5.4. Bipartite Tables

Another method developed as an alternative to conventional lookup tables and linear interpolation is based on bipartite tables [51-54]. Despite requiring a multiplier, this technique only uses two lookup tables which are accessed in parallel, together with an adder for approximating  $s_b(r)$  and  $d_b(r)$  functions. As claimed in [51], an LNS system that uses bipartite tables will require significantly less memory than one that uses conventional lookup tables. Moreover, apart from only involving an addition operation at the final stage, the technique often has shorter overall delays since the smaller tables have shorter access times too.

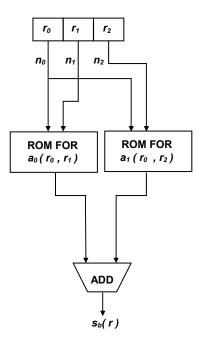

Theoretically, to approximate  $s_b(r)$  and  $d_b(r)$  functions using bipartite tables, the input operand *r* is divided into three parts, which are denoted as  $r_0$ ,  $r_1$  and  $r_2$ , and have lengths of  $n_0$ ,  $n_1$  and  $n_2$  respectively. Based on those three partitions, with the example of LNS addition, the function of  $s_b(r)$  is approximated as:

$$s_b(r) = s_b(r_0 + r_1 + r_2) \approx a_0(r_0, r_1) + a_1(r_0, r_2)$$

(2.20)

The coefficient  $a_0(r_0, r_1)$  for the first table will receive  $n_0 + n_1$  word-lengths, whereas  $n_0 + n_2$  will act as inputs to the second table that provides the coefficient  $a_1(r_0, r_2)$ . The outputs from the two tables will therefore be added to estimate the  $s_b(r)$  algorithm, as depicted in Figure 2-8.

Figure 2-8: Bipartite table architecture.

Among the initial work implementing bipartite tables was a study by Das Sarma and Matula in 1995 [51]. A technique was proposed where the input operand was partitioned into high, middle and low fields of sizes k+1, k, k. For example, in the case of a 6-bit operand, the partition will be in the order of 3, 2, 2 of high, middle

and low bits respectively. The partitioning concept presented was able to achieve substantial compression of lookup tables compared to the conventional direct lookup table approach, by factors over 4 with a 9-bit input operand. Further refinement of the bipartite table was achieved by Schulte and Stine in 1997 [55], utilizing the concept of symmetry in the table entries. Compared to a direct lookup table, this symmetric bipartite table was 5.6 times smaller with a 16-bit operand and 99.1 times smaller with a 24-bit operand, requiring an estimated total storage of nearly 35 kbits and 2031 kbits for 16-bit and 24-bit operands respectively. A separate proposal was illustrated by Dinechin and Tisserand in 2001 [56], where a multipartite table method was introduced. Instead of using dual tables, the technique employed multiple smaller tables to compute  $s_b(r)$  and  $d_b(r)$  functions. The synthesis results based on a parameterized library [57, 58] of LNS addition and subtraction using this technique proved that, even though the architecture is capable of achieving higher speed when compared with FLP, it was actually very bulky in size, and hence was limited in practice only to precisions up to 13-bit. Therefore, neither bipartite nor multipartite tables can realistically be considered for long word-length numbers. Furthermore, the multipartite method has the same issue with  $d_b(r)$  singularity found in interpolation.

#### 2.5.5. Co-transformation

As discussed earlier, most of the techniques presented so far have the problem of solving the  $d_b(r)$  function when r is close to zero. They tend to be either higher in cost, in terms of memory size, or else lower in accuracy. One technique which can overcome this situation uses the co-transformation procedure. The idea behind this technique is to convert the argument of  $d_b(r)$  into modified values that are guaranteed to avoid the singularity of the function.

The first noteworthy co-transformation technique was outlined by Coleman in 1995 [59], applying the concept in the region -0.5 < r < 0 for the  $d_b(r)$  function. When employing this technique, the need for interpolation in the region -0.5 < r < 0

can be eliminated, thus substantially reducing the size and complexity of the lookup tables required. Note that for the  $s_b(r)$  function, an interpolation scheme was applied through out all regions. In 2000, Coleman *et al.* [6] presented in details the implementation of this co-transformation together with interpolation in a 32-bit system. With significant improvements in accuracy over FLP, a total of 321 kbits were required in order to execute the LNS addition and subtraction. Recently, Coleman *et al.* [7] conducted an experiment to determine the feasibility of integrating the LNS system into a microprocessor based on the proposal in [6]. A chip of a 32-bit LNS microprocessor, named the European Logarithmic Microprocessor (ELM), was manufactured using 0.18 µm CMOS technology. This was compared with the existing FLP DSP device from Texas Instruments, which has one of the fastest speeds obtainable in 0.18 µm technology. Besides clearly verifying that the results were more accurate, the speed of the ELM was also substantially improved over the FLP device, at 24 ns whilst performing addition and direct subtraction, and 32 ns for subtraction using co-transformation.

A different but related co-transformation technique to Coleman's was given by Arnold *et al.* in 1999 [10]. Unlike Coleman's method, which transformed a value at the singularity to a negative argument of  $d_b$  that will fall in the region to the left of -0.5, Arnold's method avoids the singularity by transforming to a positive argument of  $s_b$  which does not have a singularity. Hence whenever r > 0, Arnold's technique is the most appropriate due to the positive value generated for the interpolation after being transformed. If r < 0, then Coleman's technique is the most natural to adopt because the transformed argument provided to the interpolation is negative. For that reason, Coleman's method is preferable given that many LNS researchers tended to apply a negative value of r, since this reduces the ROM size dramatically when approaching essential zero (as shown in Figure 2-4).

#### 2.5.6. Hybrid Architecture

A combination of two different data formats, including elements from both LNS and FLP systems, has been exploited a new form of processors known as hybrid number system processors. These allow the multiply and divide operations to be rapidly computed using the LNS format, whilst addition and subtraction are processed efficiently in FLP representation. The first hybrid processor design was presented by Taylor [60], named the (FU)<sup>2</sup>, which offered a 12-bit FLP datapath whose overall performance was found to demonstrate effectively when compared to that of the conventional FLP system.

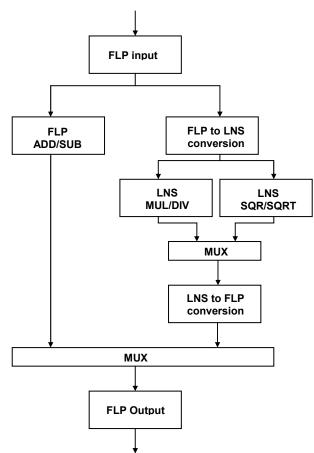

With an extension to the 32-bit operands, Lai and Wu [61] proposed a hybrid system architecture that executed multiplication, division, square root and square in a fast manner using LNS. In contrast, the FLP number system was applied to resolve the input, output, addition and subtraction functions. Due to the consuming nature of the overhead operations whilst converting FLP-to-LNS and LNS-to-FLP, lookup tables and linear interpolation algorithms were inserted, whereupon the routine of this processor appeared to compare favourably with a 32-bit FLP DSP device. Since the main obstacle in this hybrid processor was the overhead of converting between number systems, Stouraitis [62] proposed a hybrid technique using a combination of signed-digit (SD) number representation and LNS, called a SD/LNS arithmetic unit. The addition/subtraction was now accomplished even faster than in the classical LNS processor, because the SD adder/subtractor was largely free from serial carry propagation. Figure 2-9 shows the principal concepts of the hybrid number system

Figure 2-9 : Concept of the hybrid number system processor.

### 2.5.7. Related Variant Number Systems

Several other techniques have been suggested to minimise the architectural complexity in computing addition and subtraction operations. In 1990, Arnold *et al.* [63] proposed a new number system dubbed the dual redundant logarithmic number system (DRLNS) which was devised to mitigate the singularity issue in subtraction. As opposed to conventional LNS arithmetic, the DRLNS denotes a real number x in positive and negative components,  $X_p$  and  $X_n$ , similarly to a real number y which then gives  $Y_p$  and  $Y_n$ .

The exact values can then be represented as:

$$x = b^{X_p} - b^{X_n}$$

$$y = b^{Y_p} - b^{Y_n}$$

(2.26)

where *b* indicates the base number. The advantage of adopting the DRLNS was that addition and subtraction shared the same execution process without involving a subtraction logarithm,  $d_b(r)$ . Hence, the function can be expressed as:

$$R_{p} = X_{p} + Y_{p} \longrightarrow log_{2} |R_{p}| = log_{2} |X_{p} + Y_{p}| = i_{p} + log_{2} |1 + 2^{rI}|$$

=  $i_{p} + s_{b}(rI)$  (2.27)

$$R_{n} = X_{n} + Y_{n} \quad \rightarrow \quad \log_{2} |R_{n}| = \log_{2} |X_{n} + Y_{n}| = i_{n} + \log_{2} |1 + 2^{r^{2}}|$$

$$= i_{n} + s_{b}(r^{2}) \tag{2.28}$$

where

$$i_{p} = log_{2} |X_{p}|$$

$$i_{n} = log_{2} |X_{n}|$$

$$r1 = log_{2} |Y_{p}| - log_{2} |X_{p}|$$

$$r2 = log_{2} |Y_{n}| - log_{2} |X_{n}|$$

The subtraction function is completed simply by interchanging the sign of  $X_p$  and  $Y_p$  with  $X_n$  and  $Y_n$  accordingly followed by the addition logarithm. However, in spite of being a trivial operation, the DRLNS often loses considerable accuracy as a result of requiring lookup tables when accomplishing the multiplication function. Moreover, the division operation is also difficult to carry out using this procedure [63]. Given these weaknesses, the DRLNS actually did not offer considerable advantages compared to a contemporary LNS system.

The semi-logarithmic number system (SLNS), introduced by Muller *et al.* in [64], is another variant of the new class of number systems. Assuming that a number x in the FLP and LNS can be represented by:

$$x_{FLP} = (1-z) \cdot (-1)^{s_x} \cdot m_x \cdot 2^{e_x}$$

$$x_{LNS} = (1-z) \cdot (-1)^{s_x} \cdot 2^{L_x}$$

(2.29)

where *z* corresponds to zero, these two expressions can then be generalised in SLNS format by introducing new parameters:

$$x_{SLNS} = (1-z) \cdot (-1)^{s_x} \cdot \alpha m_x \cdot 2^{\beta e_x}$$

(2.30)

Conceptually, the SLNS constitutes a compromise between FLP and LNS. In the case of  $\alpha = \beta = 1$ , the FLP format was applied to perform the operations, whereas for  $\alpha = m_x = 1$  and  $0 < \beta \le 1$ , LNS was adopted. The advantages of the SLNS are that multiplication and division can be easily completed as in the LNS, and a reduction in lookup tables can be obtained to perform addition and subtraction. According to the authors, slightly lower accuracy compared to LNS and FLP was deemed to be the only drawback, but the scheme was still pragmatically good enough for various DSP applications analogous to those using traditional LNS procedure.

Instead of using binary numbers to represent values in the classical LNS system, another approach proposed by Arnold in 2005 [65] was called the Residue Logarithmic Number System (RLNS). Here the values used to approximate the LNS operations were based on the residue number system. Although multiplication and division can be faster than any other operations, like that of conventional LNS, the RLNS still experienced the same issue in addition of huge lookup tables being required. As well as that, without an evaluation of the performance of the subtraction operation, its overall efficiency remains uncertain.

#### 2.6. Performance Analysis

Three crucial elements dominate previous works when proposing new algorithms or architectures for an LNS system. Speed is always a key factor when producing any high performance LNS system. A high speed system can not only execute many operations with the lowest possible delay, but can also minimise the component and system related noise which occurs in DSP systems. Researchers have also strived to reduce the large areas involved in computing LNS addition and subtraction operations resulting from the lookup tables required to store the values for approximating the functions. However, an LNS system with high speed and reduced area but accuracy outside FLP limits would be worthless. Therefore, the accuracy of the results is of the utmost importance.

Based on the several different LNS techniques to compute addition and subtraction operations as discussed in Section 2.5, it can then be summarised as in Table 2-2. Obviously, it can be seen that by implementing the co-transformation approach with the interpolation process, less total storage can be achieved especially when subtractions near singularity region. Moreover, with significant improvements in accuracy, the worst-case delay in operating add and direct subtract functions was also found to be better than equivalent FLP units. Therefore, it can be concluded that this approach may now be the best technique to be used as a benchmark to improve further the LNS system. A summary of LNS designs over the years is also given in Figure 2-10.