#### Newcastle University School of Electrical and Electronic Engineering

## Design, Analysis and Implementation of Voltage Sensor for Power-Constrained Systems

By

Reza Ramezani

A thesis submitted for the degree of

Doctor of Philosophy

### **Abstract**

Thanks to an extensive effort by the global research community, the electronic technology has significantly matured over the last decade. This technology has enabled certain operations which humans could not otherwise easily perform. For instance, electronic systems can be used to perform sensing, monitoring and even control operations in environments such as outer space, underground, under the sea or even inside the human body. The main difficulty for electronics operating in these environments is access to a reliable and permanent source of energy. Using batteries as the immediate solution for this problem has helped to provide energy for limited periods of time; however, regular maintenance and replacement are required. Consequently, battery solutions fail wherever replacing them is not possible or operation for long periods is needed. For such cases, researchers have proposed harvesting ambient energy and converting it into an electrical form. An important issue with energy harvesters is that their operation and output power depend critically on the amount of energy they receive and because ambient energy often tends to be sporadic in nature, energy harvesters cannot produce stable or fixed levels of power all of the time. Therefore, electronic devices powered in this way must be capable of adapting their operation to the energy status of the harvester. To achieve this, information on the energy available for use is needed. This can be provided by a sensor capable of measuring voltage. However, stable and fixed voltage and time references are a prerequisite of most traditional voltage measurement devices, but these generally do not exist in energy harvesting environments. A further challenge is that such a sensor also needs to be powered by the energy harvester's unstable voltage. In this thesis, the design of a reference-free voltage sensor, which can operate with a varying voltage source, is provided based on the capture of a portion of the total energy which is directly related to

the energy being sensed. This energy is then used to power a computation which quantifies captured energy over time, with the information directly generated as digital code. The sensor was fabricated in the 180 nm technology node and successfully tested by performing voltage measurements over the range 1.8 V to 0.8 V.

### Acknowledgments

I would like to express the deepest appreciation to my supervisor Prof. Alex Yakovlev, who has the attitude and the substance of a genius: he continually and convincingly conveyed a spirit of adventure in regard to research. Without his guidance and persistent help this thesis would not have been possible.

I am also grateful to Dr. Fei Xia and Dr. Delong Shang for their fruitful discussions on various related topics. I would like to thank my friends and colleagues, Dr. Mohammed Alamin, Dr. Reza Rafiee, Dr. Maxim Rykunov, Dr. Ra'ed Al-Dujaily and Dr. Danil Sokolov for their inspiring discussions.

I would also like to thank my fiancé, Golnaz whose remarkable support helped me significantly throughout this research. The last but not the least; I would like to thank my parents; Ali Ramezani and Hamideh Baimani, my nanny Kefaiat, my sisters Leila and Sanaz and my brother Borzo, for supporting me spiritually throughout my life.

This work was supported by the Engineering and Physical Sciences Research Council (EPSRC) under Grant No. EP/G066728/1, "Next Generation Energy-Harvesting Electronics: Holistic Approach,".

### Contents

| Chapter 1. | Introduction                                               | 1  |

|------------|------------------------------------------------------------|----|

| 1.1 M      | Motivation                                                 | 1  |

| 1.2 E      | Energy-modulated quality of service                        | 2  |

| 1.3 T      | hesis main aim                                             | 4  |

| 1.4 C      | Contributions of the thesis                                | 4  |

| 1.5 C      | Organisation of the thesis                                 | 5  |

| Chapter 2. | Background                                                 | 8  |

| 2.2 V      | Voltage measurement techniques                             | 10 |

| 2.2.1      | Mode selector or POR                                       | 11 |

| 2.2.2      | Voltage sensing using comparators and reference generators | 13 |

| 2.2        | .2.1 Band-gap circuit                                      | 13 |

| 2.2.3      | ADC                                                        | 15 |

| 2.2        | .3.1 Voltage-to-time converter (VTC)                       | 15 |

| 2.2        | .3.2 Charge run down ADC                                   | 18 |

| 2.2        | .3.3 Successive-approximation register (SAR)               | 18 |

| 2.2        | .3.4 Delta-sigma ADC                                       | 21 |

| 2.2        | .3.5 Flash ADC                                             | 23 |

| 2.3 C      | Circuit energy consumption                                 | 25 |

| 2.3.1      | Asynchronous design                                        | 26 |

| 2.3.2      | Bundled data                                               | 27 |

| 2.3        | .2.1 Request signal                                        | 28 |

| 2.3.3      | Dynamic voltage scaling (DVS)                              | 30 |

| 2.3.4      | Dynamic frequency scaling (DFS)                            | 32 |

| 2.3.5      | Voltage converters                                         | 32 |

| 2.4 P      | ower platform designed by Maxim                            | 34 |

| 2.5 C      | Conclusion                                                 | 36 |

| Chapter 3. | Principle of capacitor charge to digital switching         | 37 |

| 3.1       | Introduction                                                      | 37 |

|-----------|-------------------------------------------------------------------|----|

| 3.2       | Capacitor discharging through dynamic digital switching           | 38 |

| 3.2.      | 1 Circuit model                                                   | 38 |

| 3.2.      | 2 Switching Index                                                 | 43 |

| 3.2.      | 3 Solution for super-threshold                                    | 46 |

| 3.2.      | 4 Solution for sub-threshold                                      | 50 |

| 3.3       | Asynchronous binary counter as the measurement tool               | 52 |

| 3.3.      | 1 Asynchronous counter using Toggle Logic                         | 53 |

| 3.3.      | 2 Switching activity vs. count (code)                             | 56 |

| 3.3.      | 3 Switching activity vs. input energy                             | 59 |

| 3.4       | Summery                                                           | 62 |

| Chapter 4 | 4. Design and implementation of the Reference-free voltage sensor | 64 |

| 4.1       | Voltage sensor implementation                                     | 64 |

| 4.1.      | 1 Voltage sensor with timing reference                            | 64 |

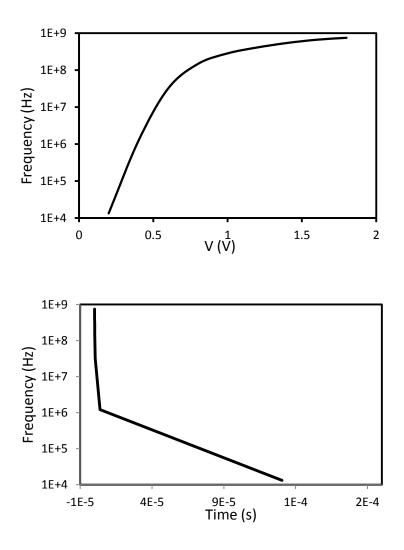

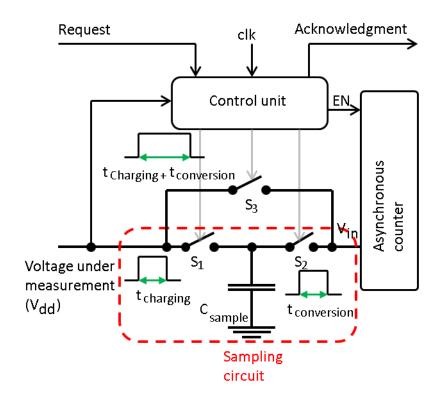

| 4.1.      | 2 Sensor operation                                                | 65 |

| 4.2       | Reference-free voltage sensor implementation                      | 68 |

| 4.2.      | 1 Control unit                                                    | 69 |

| 4.2.      | 2 Reference generator (RG)                                        | 72 |

| 4.2.      | 3 Comparator                                                      | 74 |

| 4.        | .2.3.1 Self-timed dynamic comparator                              | 76 |

| 4.2.      | 4 Controlling unit                                                | 78 |

| 4.2.      | 5 Sensor operation analysis                                       | 80 |

| 4.2.      | 6 Energy consumption of the sensor                                | 84 |

| 4.3       | Physical implementation of the proposed sensor                    | 86 |

| 4.3.      | 1 Measurement results                                             | 90 |

| 4.4       | Conclusion                                                        | 94 |

| Chapter 5 | 5. Case study of reference-free voltage sensor                    | 96 |

| 5.1       | Introduction                                                      | 96 |

| 5.1.      | Proposed power unit for computational load                        | 96 |

|        | 5.1.1.1 | Power management strategy                                 | 98  |

|--------|---------|-----------------------------------------------------------|-----|

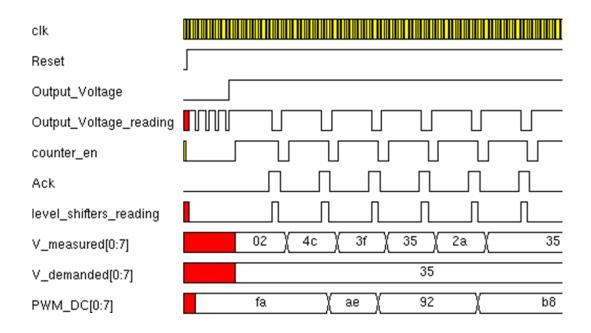

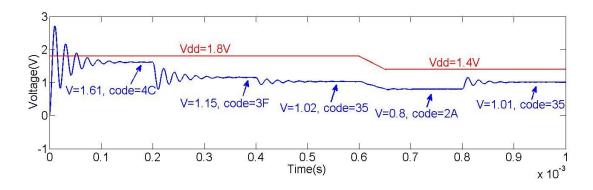

|        | 5.1.1.2 | System operation case study and discussion                | 99  |

| 5      | .1.2 P  | roposed power unit to provide controllable supply voltage | 102 |

|        | 5.1.2.1 | General architecture                                      | 103 |

|        | 5.1.2.2 | Circuit operation                                         | 104 |

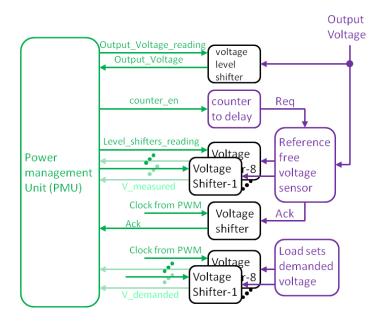

|        | 5.1.2.3 | Power management unit (PMU)                               | 108 |

|        | 5.1.2.4 | Voltage level shifter                                     | 111 |

|        | 5.1.2.5 | PWM generator                                             | 113 |

|        | 5.1.2.6 | System efficiency                                         | 115 |

| 5.2    | Concl   | usion                                                     | 120 |

| Chapte | er 6. C | onclusions                                                | 121 |

| 6.1    | Summ    | nary                                                      | 121 |

| 6.2    | Future  | e work                                                    | 124 |

|        | Bib     | liography                                                 | 126 |

|        | App     | pendix A                                                  | 134 |

|        | App     | pendix B                                                  | 138 |

|        |         | oendix C                                                  |     |

# List of Figures

| Figure 2-1 General block diagram of energy harvesting system [30]                                                                                                 | 8           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Figure 2-2 Energy-aware paradigm for an energy harvesting system [31]                                                                                             | 10          |

| Figure 2-3 Mode selector circuit [32].                                                                                                                            | 11          |

| Figure 2-4 Power on-reset signal [33].                                                                                                                            | 12          |

| Figure 2-5 Voltage sensing based on comparison to a reference                                                                                                     | 13          |

| Figure 2-6 Relationship between the $V_{BE}$ and $\Delta V_{BE}$ [37, 38]                                                                                         | 14          |

| Figure 2-7 A simple band-gap circuit.                                                                                                                             | 15          |

| Figure 2-8 Voltage to time and time to digital converters                                                                                                         | 16          |

| Figure 2-9 Voltage to time to digital using delay line                                                                                                            | 17          |

| Figure 2-10 Charge run down ADC.                                                                                                                                  | 18          |

| Figure 2-11 Simple block diagram of SAR ADC.                                                                                                                      | 19          |

| Figure 2-12 N-bit SAR-ADC based on charge redistribution.                                                                                                         | 21          |

| Figure 2-13 Delta-sigma ADC.                                                                                                                                      | 22          |

| Figure 2-14 Delta-sigma operation waveforms.                                                                                                                      | 23          |

| Figure 2-15 Block diagram of Flash ADC                                                                                                                            | 24          |

| Figure 2-16 Bundled data protocol                                                                                                                                 | 28          |

| Figure 2-17 Dual rail encoding                                                                                                                                    | 29          |

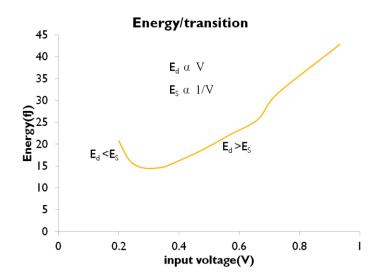

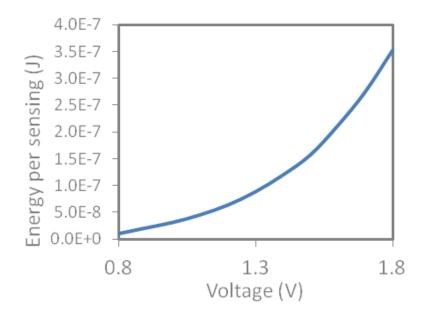

| Figure 2-18 Energy per transition for an 8-bit asynchronous countersimulation, energy consumption of the counter was measured under different of supply voltages. | fixed level |

| Figure 2-19 Block diagram of MAX17710 designed by MAXIM                                                                                                           | 35          |

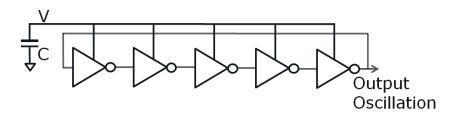

| Figure 3-1 Ring of inverters being powered by a capacitor                                                                                                         | 38          |

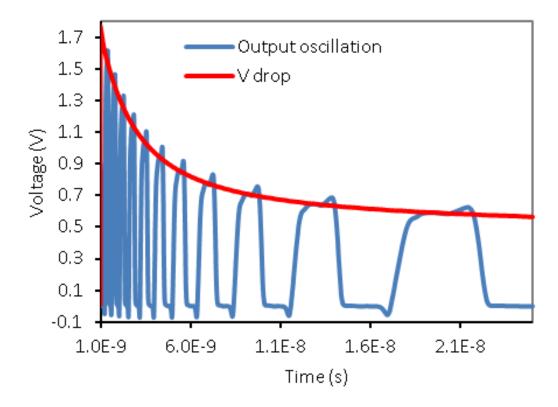

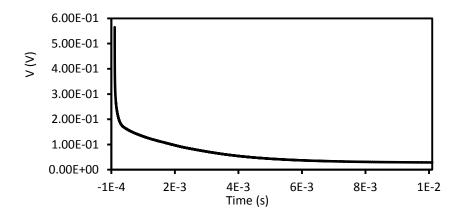

| Figure 3-2 Output oscillation and voltage drop of the ring oscillator. 18 technology library was used for this simulation.                                        |             |

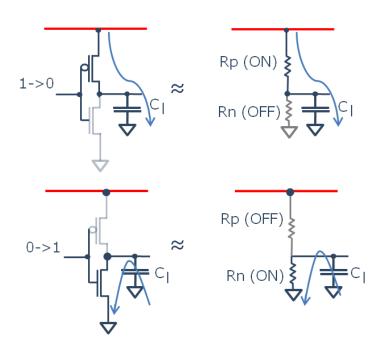

| Figure 3-3 Transistor switching in an inverter                                                                                                                    | 40          |

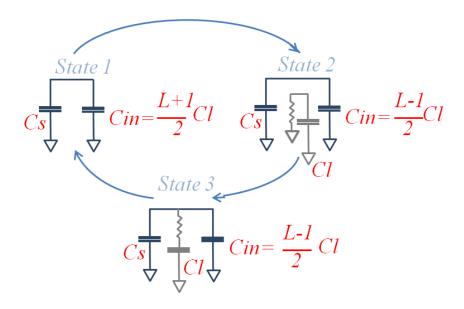

| Figure 3-4 Circuit state at dynamic switching, L is the number of inverters.                                                                                      | 41          |

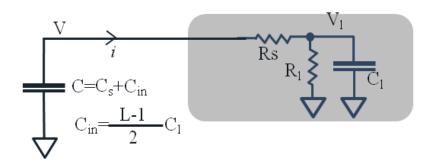

| Figure 3-6 RC model for ring oscillator in terms of power consumption                                                                                             | 41          |

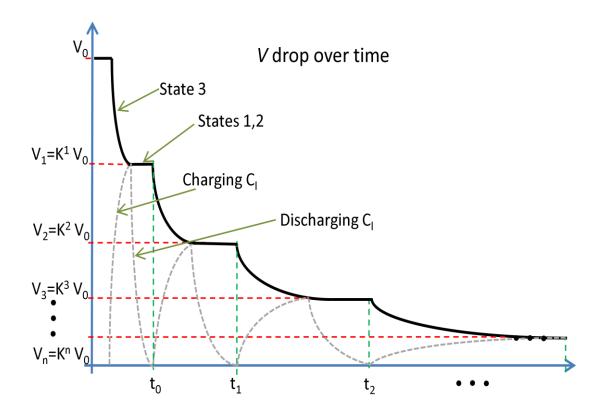

| Figure 3-7 Voltage drop over time                                                                                                                                 | 45          |

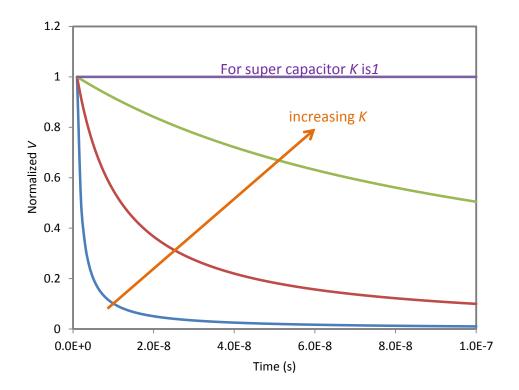

| Figure 3-8 Simulation of voltage drop from equation (3-15) with respect to K. For Cs as supercapacitor K is the one                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

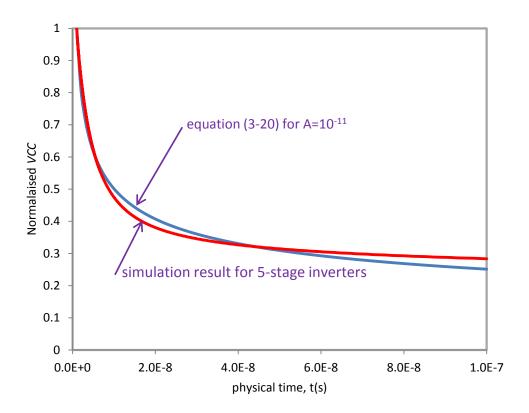

| Figure 3-9 Voltage drop at super-threshold region, general form. The simulation result was captured using 180nm UMC library                                                                                 |

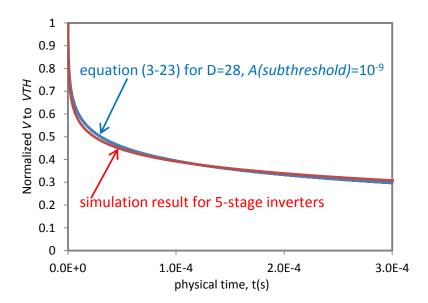

| Figure 3-10 Voltage drop at sub-threshold region                                                                                                                                                            |

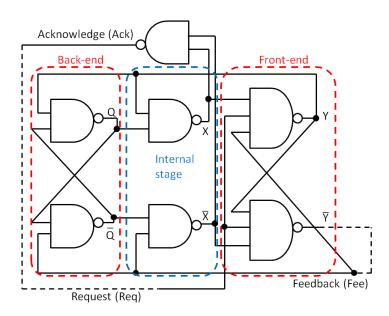

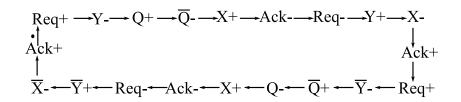

| Figure 3-11 Schematic of an asynchronous toggle circuit which is the basic building block for the charge-to-digital converter                                                                               |

| Figure 3-12 Signal Transition Graph (STG) describing the toggle circuit55                                                                                                                                   |

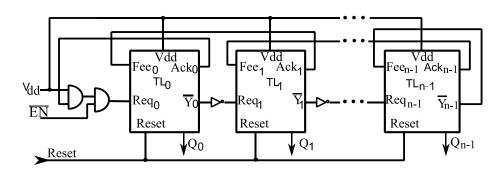

| Figure 3-13 A general n-bit asynchronous counter based on toggle logic. This counter serves the charge-to-digital purpose in a sensor application, if the input is connected to a sampling capacitor.       |

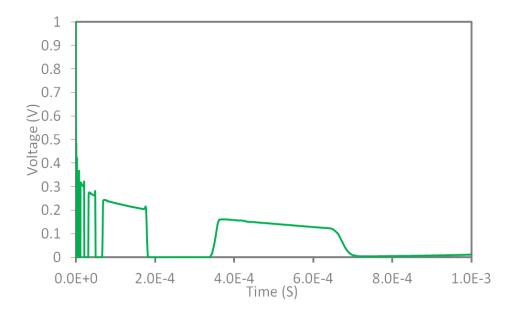

| Figure 3-14 LSB bit of the counter while the capacitor charge is decreasing and the voltage on the counter is degrading.                                                                                    |

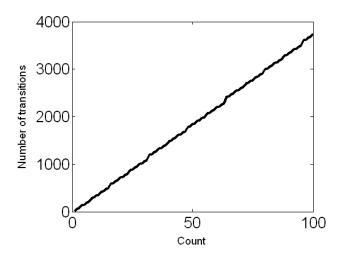

| Figure 3-15 The relationship between the output count of the counter and the number of gate transitions according to (3-29).                                                                                |

| Figure 3-16 Voltage drop as a function of time for counter as load                                                                                                                                          |

| Figure 3-17 Frequency as function of voltage and time of discharging61                                                                                                                                      |

| Figure 4-1 General architecture of the proposed sensor with timing reference65                                                                                                                              |

| Figure 4-2 The general architecture of the proposed sensor (with reference) was simulated using 180nm UMC library. In this figure the counter output during one complete cycle of conversion is shown       |

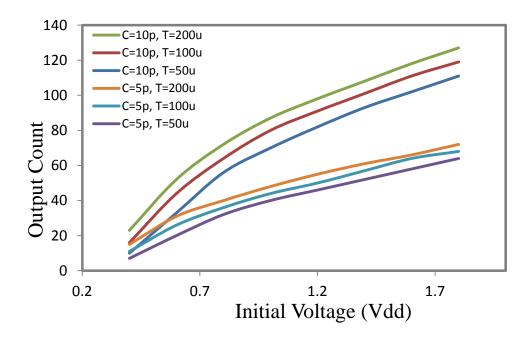

| Figure 4-3 The output count versus input voltage for two different values of capacitor and three different time lengths of sampling and conversion67                                                        |

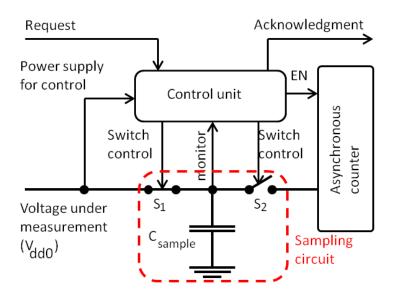

| Figure 4-4 Voltage sensor that samples a charge from the main energy supply and stores it in a small capacitor. This capacitor's voltage will be used as $V_{dd}$ input to the asynchronous counter circuit |

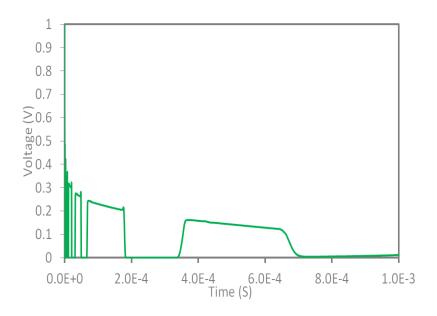

| Figure 4-5 LSB bit of the counter while the capacitor charge is decreasing and the voltage on the counter is degrading. As it can be seen, the output of the counter degrade to zero                        |

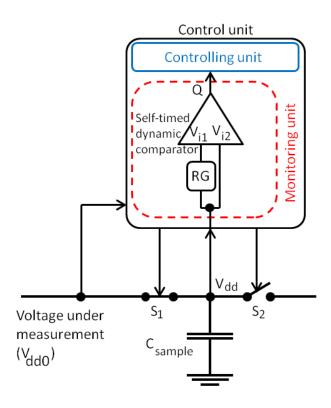

| Figure 4-6 Monitoring and controlling units block diagram                                                                                                                                                   |

| Figure 4-7 Schematic of reference generator73                                                                                                                                                               |

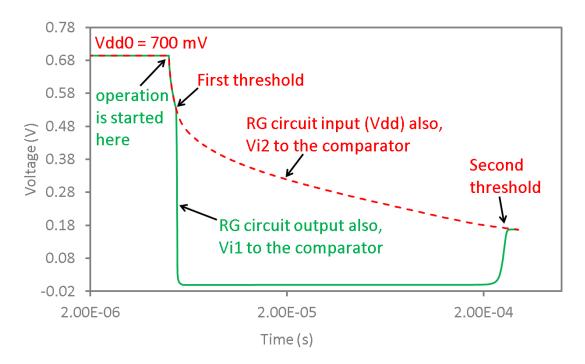

| Figure 4-8 Simulation results on reference generator circuit using Cadence tools at 180nm technology process. At low Vdd0 operation is started after the first threshold74                                  |

| Figure 4-9 The comparator design used in the self-timed dynamic comparator75                                                                                                                                |

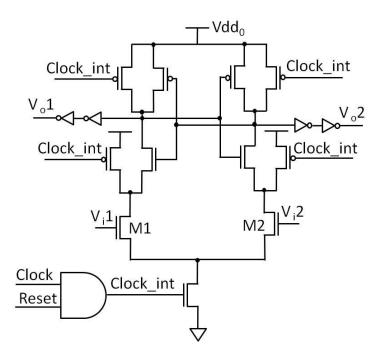

| Figure 4-10 Self-timed dynamic comparator                                                                                                                                                                   |

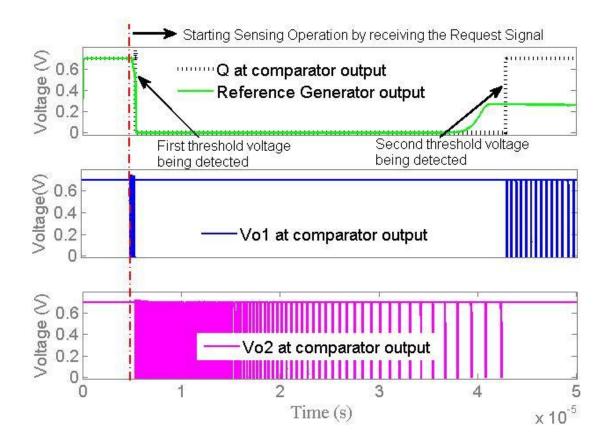

| this simulation, 180nm UMC technology librarye was used. This figure shows how the output voltage of the RG circuit changes the state of the comparator.                                                                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

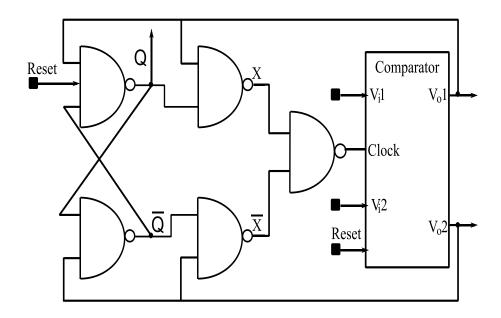

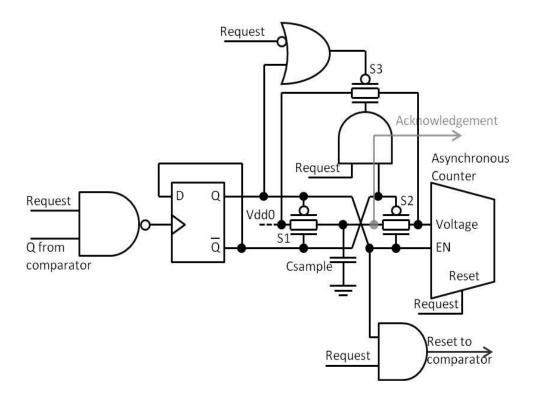

| Figure 4-12 Controlling unit in details.                                                                                                                                                                                                                                                                                                   |

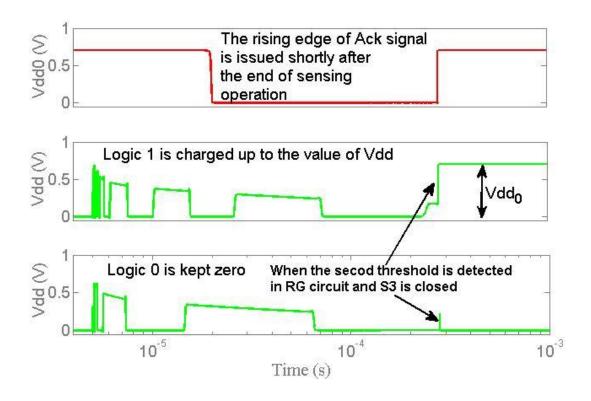

| Figure 4-13 The termination of sensing operation                                                                                                                                                                                                                                                                                           |

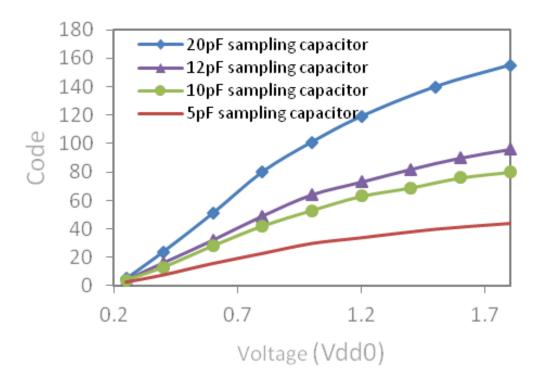

| Figure 4-14 The output code of sensor over a range of voltages ( $V_{dd0}$ ) from 0.25V to 1.8V                                                                                                                                                                                                                                            |

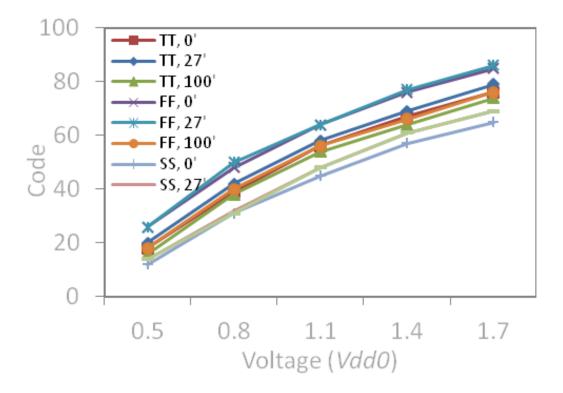

| Figure 4-15 Variation of the output code over process and temperature variations82                                                                                                                                                                                                                                                         |

| Figure 4-16 Monte Carlo simulation for 200 samples with $V_{dd0}$ =1.5 $V$ and $C_{sample}$ =5 $p$                                                                                                                                                                                                                                         |

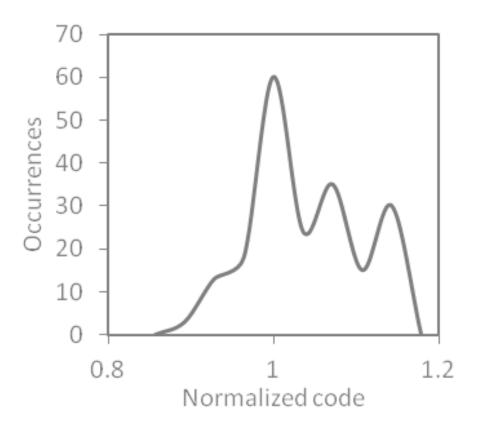

| Figure 4-17 The output code of the sensor against a) the real measured voltage, b) the predicted voltage as if the operation of the sensor is linear for C=20pf84                                                                                                                                                                          |

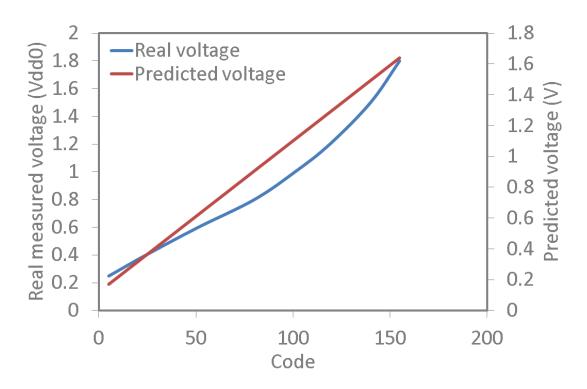

| Figure 4-18 Energy consumption of the sensor                                                                                                                                                                                                                                                                                               |

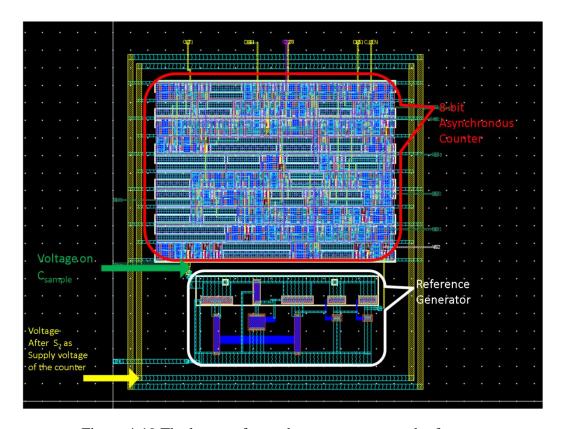

| Figure 4-19 The layout of asynchronous counter and reference generator87                                                                                                                                                                                                                                                                   |

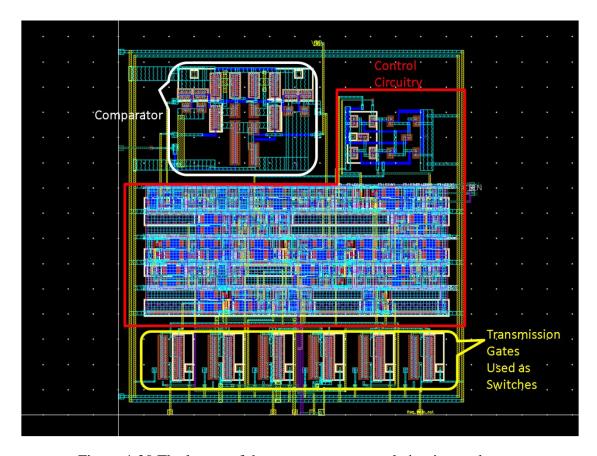

| Figure 4-20 The layout of the comparator, control circuitry and switches88                                                                                                                                                                                                                                                                 |

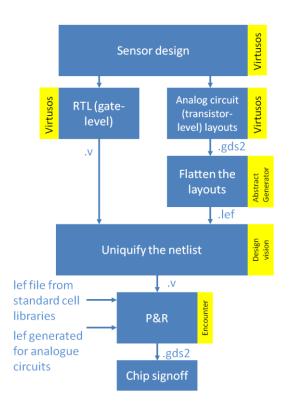

| Figure 4-21 Chip design flow                                                                                                                                                                                                                                                                                                               |

| Figure 4-22 The generated .lef file for transmission gate (TG) as analogue switch. The file is generated by abstract generator tool                                                                                                                                                                                                        |

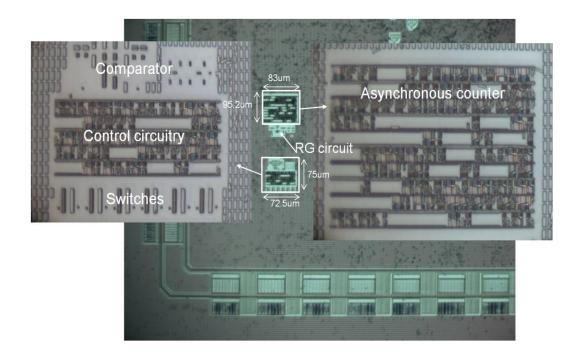

| Figure 4-23 Die micrograph of the voltage sensor in 180nm technology node92                                                                                                                                                                                                                                                                |

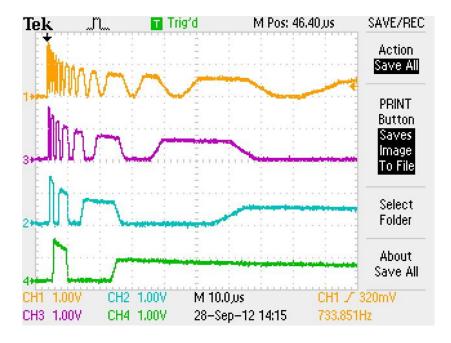

| Figure 4-24 Counting action of my proposed asynchronous counter while it is powered by the sampling capacitor = 1nF                                                                                                                                                                                                                        |

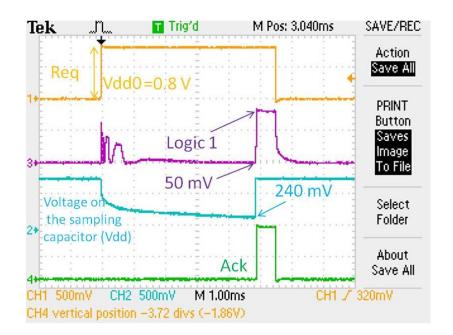

| Figure 4-25 Logic one at the output of the sensor.                                                                                                                                                                                                                                                                                         |

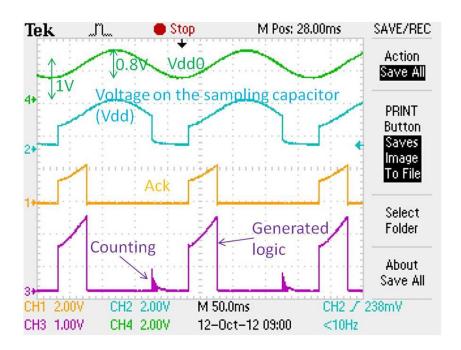

| Figure 4-26 Sensor operation under variable voltage.                                                                                                                                                                                                                                                                                       |

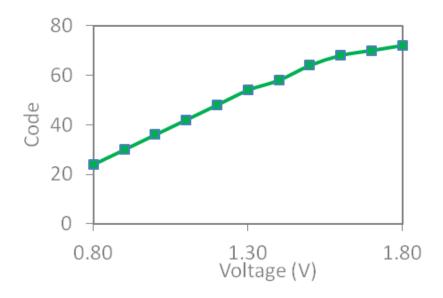

| Figure 4-27 Output code of the counter over a range of voltage from 0.8V to 1.8V94                                                                                                                                                                                                                                                         |

| Figure 4-28 Energy consumption of the sensor measured per each sensing94                                                                                                                                                                                                                                                                   |

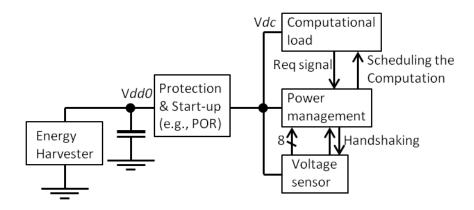

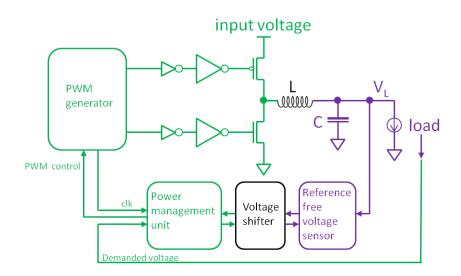

| Figure 5-1 Block diagram of the system using voltage sensor                                                                                                                                                                                                                                                                                |

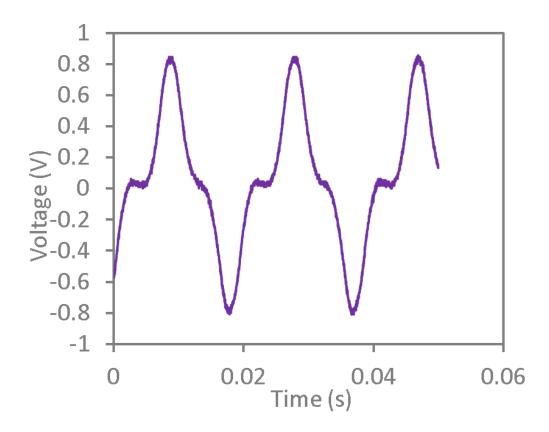

| Figure 5-2 Output of the harvester when the vibration frequency is $52.4$ Hz, $6$ k $\Omega$ load and $60$ mg acceleration                                                                                                                                                                                                                 |

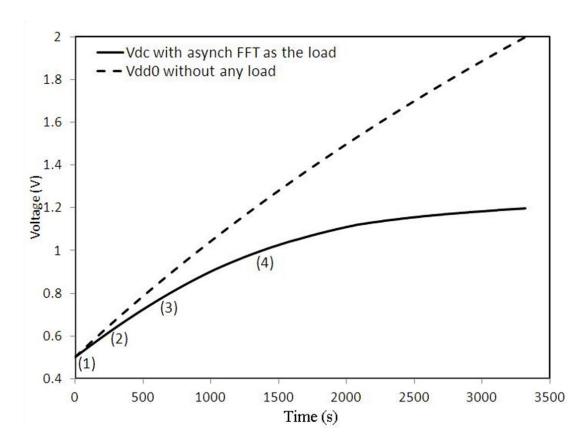

| Figure 5-3 The voltage of the source with and without the FFT, the performance of the FFT is controlled depend on the available energy. (1) Transformation size 512 precision 12 bits, (2) transformation size 512, precision 16 bits, (3) transformation size 1024, 8-bit precision and (4) transformation size 1024 and 12-bit precision |

| Figure 5-4 General architecture of the proposed power platform103                                                                                                                                                                                                                                                                          |

| Figure 5-5 PMU signalling                                                                                                                                                                                                                                                                                                                  |

| Figure 5-6 Waveforms for PMU                                                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 5-7 Output voltage of the converter over time, (codes are in Hex) for L=500uH and C=22nF                                                           |

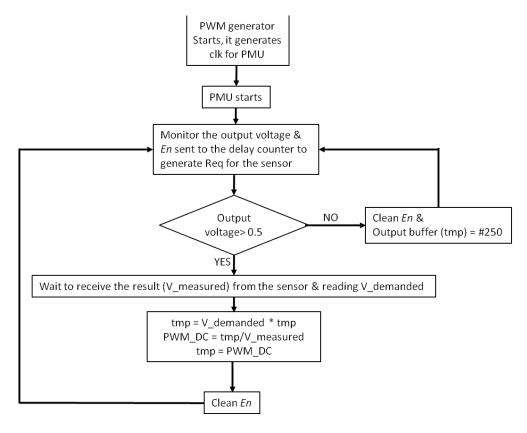

| Figure 5-8 Flowchart showing the operation of the PMU                                                                                                     |

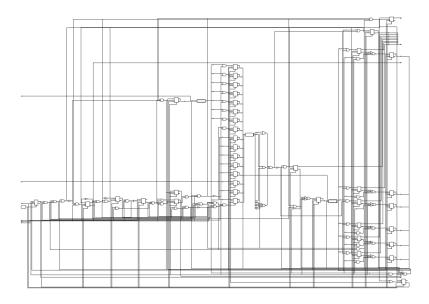

| Figure 5-9 The schematic of the PMU generated by the synthesis tool                                                                                       |

| Figure 5-10 Part of the report generated by the PrimeTime for worst case process corner timing analysis                                                   |

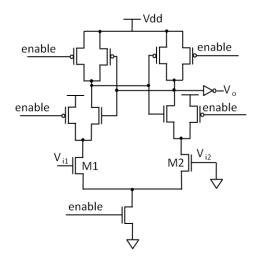

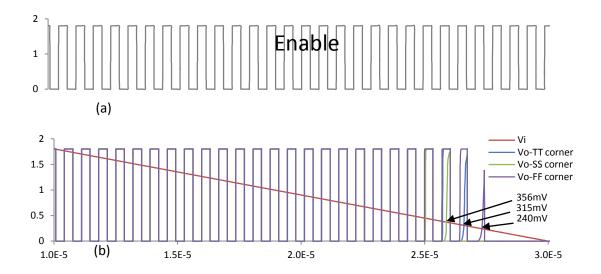

| Figure 5-11 Zero-bias current comparator to be used as voltage shifter111                                                                                 |

| Figure 5-12 Voltage shifter operation in different process corners, (a) enable signal, (b) operation with falling input, (c) operation with raising input |

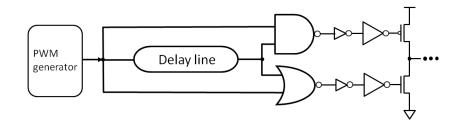

| Figure 5-13 Block diagram of the ascynchronous <i>PWM</i> generator                                                                                       |

| Figure 5-14 PWM generator operation at $V=1.8V$ , frequency of output PWM signal is 2.44MHz, $duty\ cycle = 0.88\ (PWM\_DC = \#240)$                      |

| Figure 5-15 Optimizing the size of the width of the transistors for the minimum loss, $W_N=30\mu$ and $W_P=50\mu$ .                                       |

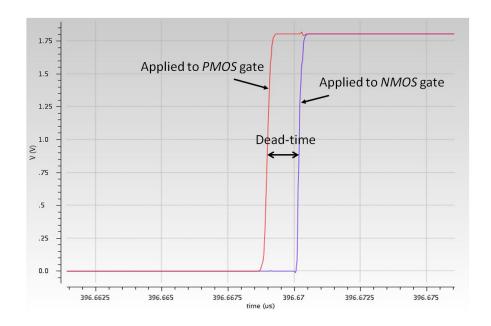

| Figure 5-16 Circuit solution to create a fixed dead-time                                                                                                  |

| Figure 5-17 The dead-time created to overcome timing error                                                                                                |

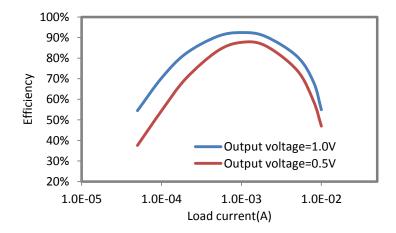

| Figure 5-18 Simulation result of the efficiency of the proposed converter for 2 different output voltages without considering the PWM                     |

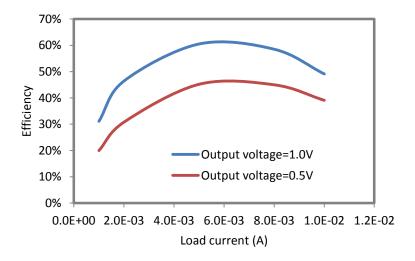

| Figure 5-19 Simulation result of the efficiency of the proposed converter for 2 different output voltages with PWM                                        |

## List of Tables

| Table 2-1 Four-bit thermometer code.                     | 17 |

|----------------------------------------------------------|----|

| Table 2-2 an overview of different ADC techniques        | 24 |

| Table 3-1 Analysis for super-threshold region            | 49 |

| Table 3-2 Analysis for sub-threshold region              | 52 |

| Table 3-3 Conversion from binary code to cumulative code | 57 |

### List of Abbreviations

Ack Acknowledgement

ADC Analog to digital converter

big-D Big digital

CMC Current mode control

CMOS Complementary metal—oxide—semiconductor

DAC Digital to analogue converter

DC Direct current

DFS Dynamic frequency scaling

DRC Design rule checking

DVFS Dynamic voltage frequency scaling

DVS Dynamic voltage scaling

EDA Electronic design automation

FET Field effect transistor

FF Fast-fast

FFT Fast fourier transform

gds Graphic database system

Hex Hexadecimal

LC Inductor-capacitor

LDO Low-dropout

lef Library exchange format

LSB Least significant bit

LVS Layout versus schematic

MEMS Microelectromechanical systems

MEP Minimum energy point

MPPT Maximum power point tracking

MS Mode selector

MSB Most significant bit

NAND Negated AND

NMOS N-channel metal-oxide semiconductor

NT Number of transitions

ODE Ordinary differential equation

P&R Place and route

PFM Pulse frequency modulation

PMOS P-channel metal-oxide semiconductor

PMU Power management unit

POR Power-on reset

PWM Pulse width modulation

QoS Quality of service

RC Resistor-capacitor

Req Request

RFID Radio-frequency identification

RTL Register transfer language

SAR Successive approximation register

small-A Small analogue

SS Slow-slow

STG Signal transition graph

TG Transmission gate

UMC United microelectronics corporation

VCO Voltage controlled oscillator

VTC Voltage to time converter

ZCS Zero current switching

ZVS Zero voltage switching

### List of symbols

uW

Microwatt

CCapacitor  $d_{i}$ Deadline to execute the task  $E_{c}$ Energy available  $e_i$ Energy consumption of the task Energy scavenged  $E_{s}$ **GNC** Ground Giga sample per second Gsps Hz Hertz  $I_c$ Collector current  $I_s$ Reverse saturation current  $I_t$ Technology-dependent scaling parameter K Coefficient of decaying voltage at each switching action  $K_b$ Boltzmann constant LTransistor length Effective channel length  $l_{\it eff}$ m Sub-threshold slope factor mAMilliampere MHz Megahertz mJ Millijoules Millimetre mm mVMillivolts **Switching Index** n nF Nanofarads Nanometer nm pF **Picofarads**  $P_{\text{max}}$ Maximum power Electrical charge R Resistor The time which each task should start being executed  $s_i$ Time Propagation delay of an inverter  $t_p$ uН Microhenry

$V_{BE}$  Base-emitter voltage

$V_{dd}$  Power supply

$V_{ds}$  Drain-source voltage

$V_{gs}$  Gate-source voltage

$V_T$  Thermal voltage

$V_{th}$  Threshold voltage

W Transistor width

α Activity factor

β Gain factor

γ Velocity saturation index

μeff Effective mobility

$\Omega \qquad \quad \text{Ohm}$

### List of publications

#### **Patent**

1. A. Yakovlev, R. Ramezani, and T. Mak, "APPARATUS AND METHOD FOR VOLTAGE SENSING," UK Patent Application no.1 005 372.6 Newcastle University, March 2010.

#### Journal publication

1. R. Ramezani, A. Yakovlev, F. Xia, J. Murphy and D. Shang, Voltage Sensing Using an Asynchronous Charge-to-Digital Converter for Energy-Autonomous Environments, IEEE Journal of Emerging and Selected Topics in Circuits and Systems (JETCAS), vol.3, No. 1, pp. 35-44, 2013.

#### **Conference publications**

- 1. R. Ramezani, D. Sokolov, F. Xia, and A. Yakovlev, "Energy-modulated quality of service: New scheduling approach," in *Faible Tension Faible Consommation (FTFC), IEEE*, 2012, pp. 1-4.

- 2. R. Ramezani and A. Yakovlev, "Capacitor Discharging Through Asynchronous Circuit Switching," in *Asynchronous Circuits and Systems* (ASYNC), 2013 IEEE 19th International Symposium on, pp. 16-22.

- 3. R. Ramezani and A. Yakovlev, "Reference Free Voltage Sensing Using an Asynchronous Charge-to-Digital Converter" IDTechEx Energy Harvesting Europe, 15-16 May 2012, Berlin, Germany.

#### **Technical reports**

- 1. R. Ramezani, A. Yakovlev, T. Mak, and D. Shang, "Voltage sensing using an asynchronous charge-to-digital converter for energy harvesting circuits," *NCL-EECE-MSD-TR-2010-161*, *Microelectronic System Design Group, School of EECE, Newcastle University*, December 2010.

- 2. D. Shang, R. Ramezani, F. Xia, A. Yakovlev, "Wide-Range, Reference-Free, On-Chip Voltage Sensor for Variable Vdd Operations", *NCL-EECE-MSD-TR-2010-159*, *Microelectronic System Design Group, School of EECE, Newcastle University*, October 2010.

### Chapter 1. Introduction

#### 1.1 Motivation

Continuous growth in demand for portable electronic devices has led to a great deal of attention being paid to circuit power consumption. Traditionally, portable electronics system are designed as battery-powered devices with efficient power control techniques applied to prolong battery life. Power or clock gating, dynamic voltage scaling (DVS) [1] and dynamic frequency scaling (DFS) [2] are the most conventional examples of techniques used to achieve maximum energy savings. While battery-operated devices are extremely common and incredibly popular, there are classes of applications where dependence on a battery is impractical. In such applications, when a continuous source of energy is required, replacing the battery may be either costly or highly inconvenient. For example, battery replacement in implanted medical devices [3-5] is significantly expensive or extremely risky. The limiting factor for these devices is the longevity of the battery sources. Using the current technology, battery powered devices can perform continuous operation between 5 to 10 years. After this time, the device should either be removed or the battery is replaced [6-8]. According to these researches, the patients who were using lithium battery powered pacemakers need reoperation every eight years.

RFID tags [9] and Micro-sensor networks [10-12] are another example of applications where due to the size and the weight of batteries they are rendered impractical. In RFID tags, the mean time for replacing battery, due to the energy density, shelf-life trends and the communication method, is only a year or two [13]. In micro/nano-sensor networks, containing large number of nodes, replacing batteries is next to impossible [14]. For these sensors the needed power is in the range of milli or even microwatt. However, the output power for a conventional rechargeable lithium-ion battery is in the range of hundreds of Watt [15].

The most promising alternative to power these applications is to harvest energy from the environment and to convert it into electrical energy. Advances in MEMS processing and materials technology have made it possible to produce electrical energy from mechanical [16], thermal [17, 18], light [19], kinetic [20] and electromagnetic [21] energy sources. These are mostly considered to be sporadic in nature but permanently available. In any system which uses these sources, energy can no longer be freely used if functionality is to be optimised in order to achieve the levels of performance demanded. In fact, the functionality should be tuned to match the energy status rather than being used to tune performance. Put simply, the amount of energy which flows into the system shapes or merely modulates the functionality, and therefore the performance, of the system. This is known as energy-modulated quality of service (QoS) [22].

#### 1.2 Energy-modulated quality of service

In electronic design nowadays, energy-aware systems have attracted huge interest among the designers of systems that have to operate in an energy-deficient environment. Within this environment, despite conventional assumptions which consider that data are the only unknown factor, energy is now an unknown parameter as well. However, the range of variation of energy is smaller, measurable and more predictable. This draws attention to the fact that systems can be equipped with means to measure energy (by simply measuring the voltage). This energy information then can be used to optimize system performance. Regardless of how this is achieved, a system which links energy information to system performance (which I simply call quality of service) can deliver an energy-modulated quality of service [23]. In this context, quality of service is simply the speed and the data precision of the operation (e.g. operation at 1MHz speed and 16-bit data precision delivers higher QoS compared to operation running at 500KHz and 8-bit data precision).

In real system implementation, in order to achieve energy-modulated quality of service, certain algorithms are employed. These algorithms regulate the operation of the system according to the energy information in a scenario of interest. For example, in a very conservative scenario, low-power operation (e.g. the power consumption of a particular operation becomes less than its nominal power consumption) is the main concern. Therefore, the system is always configured to operate at the minimum possible level of performance which is defined according to the energy information. Another interesting scenario is to configure the system for a specific level of performance at all times. In this scenario, the quality of system operation, for instance, the precision of computation is adjusted according to the energy information. As far as system operation is concerned, the most reliable algorithm would be the one which guarantees the survivability of the system. Such an algorithm should be able to arrange and prioritize tasks in a queue in order to produce meaningful results without wasting energy on possibly interminable task. Two slightly different classes of such algorithms are described below.

There are various different online or off-line scheduling algorithms [24-26] which optimize the functionality of a system according to the amount of energy available ( $E_c$ ), predictions of energy scavenged ( $E_s$ ), energy consumption of the task ( $e_i$ ), maximum possible performance (achieved at  $P_{max}$ ), and a deadline to execute the task ( $d_i$ ). These algorithms arrange queues of tasks according to the time which each task should start being executed ( $s_i$ ). To calculate the start time  $s_i$ , the above stated information ( $E_c$ ,  $E_s$ ,  $e_i$ ,  $P_{max}$  and  $d_i$ ) is employed.

Another class of algorithms [23] considers tasks as continuous actions. Therefore, any amount of progress towards completing a task can be meaningful and valuable. From this point of view, if the amount of energy available is not sufficient to finish the task,

the load can still use the energy and produce results which are less precise or otherwise deliver a lower quality of service. For instance, after spending insufficient energy, only part of the result is useless. The remainder of the result may be of a somewhat lower quality but is still meaningful and useful. It can be argued that such imprecision in terms of data is tolerable for a system operating in an energy-scarce environment.

Regardless of the mechanisms employed by any of these algorithms, information on the energy available for use is essential. Consequently, a circuit should be designed in order to measure the amount of available energy. The main challenge here is that the circuit is operating in the same environment as the rest of the system, and therefore it measures the energy which is also used as its own power supply. The next challenge is that, in an energy harvesting environment, stable or fixed references such as for voltage or time are not guaranteed. Therefore, a circuit is required which can robustly operate under conditions of energy variation but with no need for any such reference.

#### 1.3 Thesis main aim

The main aim for this research is to design a voltage sensor circuit which can reliably operate in energy harvesting systems. However, stable and fixed voltage references, a prerequisite of most traditional voltage measurement devices [27, 28] generally do not exist in energy harvesting environments [29]. Therefore, the main requirement for this sensor is to operate without the need for any references.

#### 1.4 Contributions of the thesis

In line with the requirements described in the previous sections the main contribution of this thesis is:

#### Reference-free voltage sensing:

This is based on the idea of capturing a portion of the total energy that is directly related to the voltage being measured or sensed. This energy is then used to power a computation which quantifies over time the energy captured and therefore the voltage sensed.

Following contributions are also been achieved throughout this research:

#### 1) The relationship between voltage drop and circuit switching:

The relationship is explored between the switching behaviour of a self-timed digital circuit and the dynamic characteristic of voltage on the capacitor while the circuit is powered by it.

#### 2) Sensor circuit design and silicon fabrication:

Following up on the specifications considered for this sensor, necessary circuits are carefully designed and tested over the range of voltage from super-threshold region down to subthreshold. The sensor was, then, fabricated on-chip using 180nm UMC technology.

#### 3) Energy harvesting power platform:

The sensor designed in this work can be simply employed to develop a power platform for any energy-aware systems. An example of such system is designed and successfully tested.

#### 1.5 Organisation of the thesis

The remainder of the thesis is organised as follows:

#### a) Chapter 2:

This chapter creates an in-depth insight into energy harvesting systems, different voltage measurement techniques and various techniques of low-energy circuit design.

#### b) Chapter 3:

The importance of the relationship between the switching behaviour of the self-timed counter and the dynamic characteristics of the voltage on the capacitor was explained before. This chapter contains research on exploring a closed-form expression of relationship between capacitor discharging and digital circuit switching. In this chapter a self-timed counter is also designed which will be used as the computational unit of the sensor.

#### c) Chapter 4:

This chapter describes the circuit details of an autonomous reference-free voltage sensor designed according to the principles of proposed charge-to-digital sensing method. The sensor, fabricated in the 180nm technology node, was tested successfully through performing measurements over the voltage range from 1.8V down to 0.8V.

#### d) Chapter 5:

The main aim for this chapter is to employ my designed sensor in an energy harvesting system. Using this sensor, a power platform designed in two main parts. The first part supplies less regulated voltage to the load with the assumption that the load is capable of working robustly under the voltage variation. The load is capable of modulating its functionality according to the energy information captured by the sensor. The second part of the power platform provides fixed and tuneable voltage for those parts of the load which require stable and controllable voltage for short period of times.

#### e) Chapter 6:

This chapter summarizes the results achieved in this research. It also discusses the main areas for future works based on the results of this study.

### Chapter 2. Background

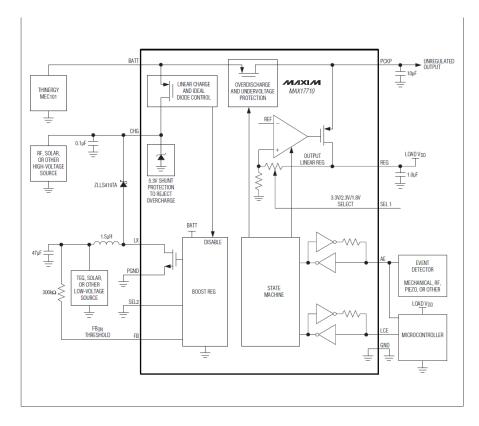

In this chapter, background information is provided on energy harvesting systems, voltage measurement and techniques for low-energy circuit design. The development of energy harvesting systems has started to attract the attention of industry, and several well-known companies have formed teams of experts to develop electronic solutions for problems in energy harvesting systems. One prominent example is the power platform, MAX17710, designed by the Maxim Company, which is described at the end of this chapter.

#### 2.1 Energy harvesting system design

Figure 2-1 depicts a general overview of an energy harvesting system. In this system, the harvester extracts energy from a source of energy in the environment and converts it into electrical form.

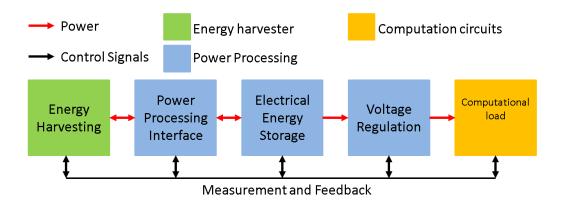

Figure 2-1 General block diagram of energy harvesting system [30].

The first stage, which is called the power processing interface, ensures that the efficiency of the harvester in terms of both harvesting and generating energy is maximized. For this purpose, techniques such as transducer frequency tuning, adaptive damping and maximum power point tracking (MPPT) are employed.

Part of the power processing is dedicated to solving the problem of the intermittent nature of the energy generating at the harvester and the energy consumption at the load. For that, once the energy accumulated in storage in a super-capacitor or a battery reaches sufficient level, the load can be triggered to start functioning.

The final stage of power processing is the voltage regulator. In this stage, the voltage on the storage component is converted into the voltage required by the load. Employing an appropriate tuneable voltage regulator is crucial to implementing techniques such as dynamic voltage scaling (DVS) and power gating. The main requirement in implementing these techniques is that the load has to have the intelligence to define a strategy by which the voltage regulator can be tuned. Depending on the efficiency and effectiveness of that strategy, the energy savings can be improved.

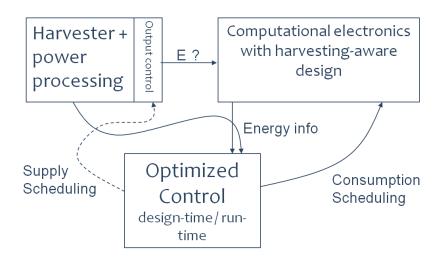

For energy-deficient environments, a more flexible strategy is that the intelligence of the load is used to tune not only the voltage regulator but also the functionality of the load according to the amount of energy available. This is a so-called energy-aware system [31]. Figure 2-2 depicts a simple system paradigm in which the load functionality can be tuned according to a measurement of the available energy. As stated in the previous chapter, different task scheduling algorithms can be used for this purpose.

Figure 2-2 Energy-aware paradigm for an energy harvesting system [31].

In this system, regardless of the strategy employed by the load, measuring energy resources is required. In the system shown in Figure 2-1, this information can be safely collected from the energy storage element. Considering the fact that the energy storage is in the form of a fixed capacitor (C), the energy (E) is obtained by simply measuring the voltage (V) on the capacitor  $(E = CV^2)$ .

It should be noted, however, that the energy harvesting systems provide a fundamentally different operating environment for electronics compared to conventional systems. For example, in terms of voltage measurement, the conventional assumption of having access to a reliable reference (in the form of voltage or time) is no longer valid. Of course, given that it is the supply voltage which varies; this is the unknown voltage which should be measured.

#### 2.2 Voltage measurement techniques

The importance of voltage measurement in the design of energy-aware systems to operate in energy harvesting environment has been discussed in the previous section. In this section, different techniques of voltage measurement are detailed.

#### 2.2.1 Mode selector or POR

Mode selectors (MS) [27, 28, 32] or power on-reset (POR) [33] circuits are designed mainly to control the mode of circuit or system operation by detecting certain voltage levels. In these circuits, the output voltage is held low while the input voltage is below a certain threshold. This can be used to guarantee that, at low voltage, the circuit does not enter into an unknown state. At a sufficiently high input voltage to guarantee robust circuit operation, the output voltage is set high. Examples of MS and POR circuits are described below.

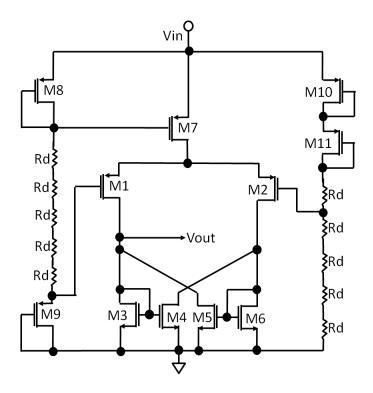

As can be seen in Figure 2-3, for a value of  $V_{in}$  higher than a certain threshold, the voltage on the gates of M1 and M2 is fixed. This configures the state of the cross-coupled latch (M3 and M4) so that  $V_{out}$  is set high. If  $V_{in}$  drops below that threshold, the state of the cross-coupled latch is inverted and  $V_{out}$  declines to zero.

Figure 2-3 Mode selector circuit [32].

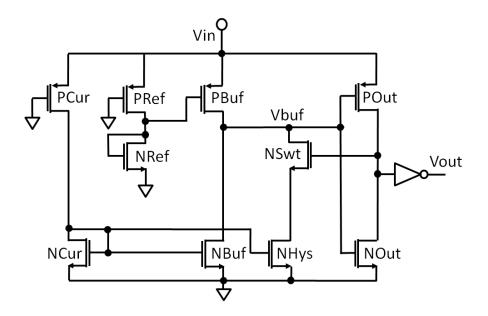

Figure 2-4 Power on-reset signal [33].

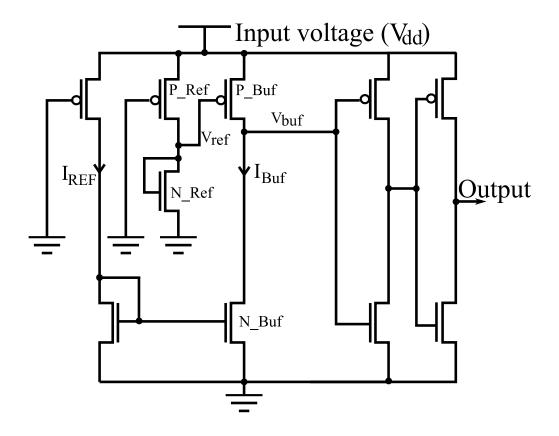

Figure 2-4 shows a simple implementation of a power on-reset circuit. In this circuit, the  $V_{ref}$  voltage generated as result of the voltage divider ( $P_{Ref}$  and  $N_{Ref}$ ) controls the current mirror ( $P_{Buf}$ ). For low  $V_{in}$ , the  $V_{Ref}$  is not sufficiently low to switch on the  $P_{Buf}$  transistor, and therefore  $V_{buf}$  is very small so that the output voltage consequently drops to zero. At sufficiently high  $V_{in}$ , the  $V_{ref}$  is low enough with respect to  $V_{in}$  to turn on the  $P_{Buf}$  transistor and therefore the current between  $P_{Buf}$  and  $N_{Buf}$  is copied from the  $P_{Cur}$  and  $N_{Cur}$  branch. As a result, a fairly high value of  $V_{buf}$ , ideally close to  $V_{in}$ , is generated and that sets the output voltage to be high. In principle, the circuit output voltage jumps from high to low and from low to high at the same value of input voltage. However, using  $N_{Swt}$  and  $N_{Hys}$  transistors, a hysteresis window is created. While the output voltage is high,  $N_{Swt}$  is in the off state, and while it is low  $N_{Swt}$  is on. This makes the low to high threshold voltage slightly bigger than the high to low threshold.

#### 2.2.2 Voltage sensing using comparators and reference generators

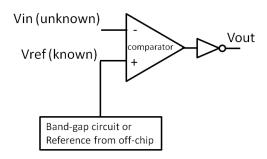

Another widely used method of voltage sensing, or even of measurement when it is called a Flash ADC, is based on the simple idea of comparing the unknown voltage with a known voltage reference [34]. In this method, the state of the output voltage is shown if the unknown voltage is higher or lower than the reference voltage. Figure 2-5 shows a general overview of such sensing techniques.

Figure 2-5 Voltage sensing based on comparison to a reference.

#### 2.2.2.1 Band-gap circuit

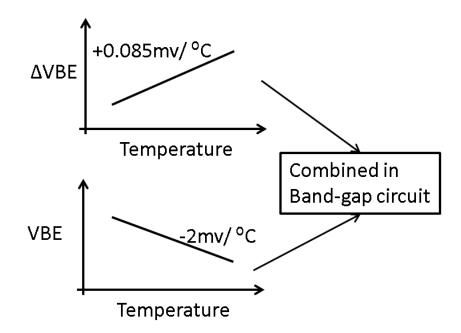

Band-gap circuits are probably the most commonly used circuits in the chip industry used to generate an on-chip fixed and stable reference voltage whenever it is needed [35, 36]. Their operation relies on the characteristics of bipolar transistors, and specifically the effect of temperature on the base-emitter junction. For this junction the relevant equations are:

$$V_{BE} = \ln\left(\frac{I_c}{I_s}\right) V_T$$

,  $V_T = \frac{K_b T}{q} \approx 26 mv \text{ at } 25^\circ$  (2 - 1)

Where  $I_c$  is the collector current,  $I_s$  is the reverse saturation current,  $V_T$  is thermal voltage,  $K_b$  is the Boltzmann constant and q is the electrical charge. Thermal voltage has a positive temperature coefficient and  $I_s$  is directly related to temperature. The

combination of these two effects establishes an inverse relationship between  $V_{BE}$  and temperature. On the other hand,  $\Delta V_{BE}$  is directly related to temperature:

$$\Delta V_{BE} = V_{BE2} - V_{BE1} = \ln \left( \frac{I_{c2}}{I_{c1}} \right) V_{th}$$

(2 - 2)

In a band-gap circuit,  $V_{BE}$  and  $\Delta V_{BE}$  are combined in a way that temperature variation effect on circuit operation is hugely eliminated.

Figure 2-6 Relationship between the  $V_{BE}$  and  $\Delta V_{BE}$  [37, 38].

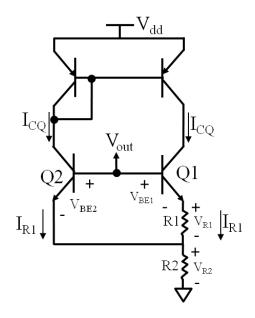

Figure 2-7 shows a simple band-gap circuit whose output voltage is relatively independent of temperature variation.

Figure 2-7 A simple band-gap circuit.

$$V_{R1} = V_{BE1} - V_{BE2} = \Delta V_{BE}$$

,  $I_{R1} = \frac{\Delta V_{BE}}{R1}$  (2 – 3)

$$V_{R2} = R_2 2 I_{R1} \implies V_{R2} = R_2 2 \frac{\Delta V_{BE}}{R1}$$

(2-4)

$$V_{out} = V_{BE2} + V_{R2} (2 - 5)$$

As can be seen, since  $V_{out}$  is a combination of  $V_{BE}$  and  $\Delta V_{BE}$ , it stays constant over a range of temperature variations.

#### 2.2.3 ADC

Converting analogue voltage into a digital value using the ADC is perhaps the most popular method of measuring on-chip voltage in the microelectronics industry. Several examples of widely used ADCs are detailed below.

#### **2.2.3.1** Voltage-to-time converter (VTC)

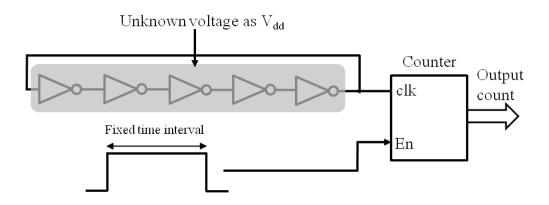

Reshaping an unknown voltage into a form of signal which is countable is the crux of this technique. For example, in a voltage-to-time converter, the voltage is applied to a voltage-controlled-oscillator (VCO) [39, 40] to generate a signal with a unique

frequency. In VCO, the output frequency is a function of the input voltage, so that the higher the voltage, the higher the frequency and vice-versa. In later stages, this frequency is counted within a fixed interval of time using a simple counter.

Figure 2-8 shows a simple implementation of the voltage to time and time to digital converter. The main issue with this method is that the output is not only a function of voltage but also of variations in process and temperature. This technique also requires a fixed time reference to enable and disable the counter.

Figure 2-8 Voltage to time and time to digital converters.

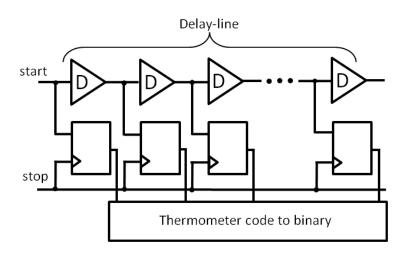

Figure 2-9 shows a block diagram of another implementation of the voltage-to-time-to-digital technique which uses a digital delay line to generate the thermometer code which is then converted into binary. In this implementation, the start signal is simply a rising edge and is fed into the delay line. A signal transition from "0" to "1" occurs at the output of each delay element which receives the start signal. After a fixed time interval, the stop signal is applied which samples the output of all of the delay elements. This output will be in the form of a thermometer code (for example, 11...100...0) which will be converted into binary code using combinational logics.

Figure 2-9 Voltage to time to digital using delay line.

In this technique, the delay line is powered by the voltage which is unknown. Therefore, the delay property of each delay element will be a function of the voltage under measurement. Thus, each value of the unknown voltage produces a unique thermometer code (unary code) at the output of the delay line [41]. As with the previous implementation, the delay line's operation is not only sensitive to the supply voltage but also to process and temperature variations. Therefore, additional logistics are required to make the design robust against unwanted variations. The following table shows the 4-bit thermometer code representation [42]:

Table 2-1 Four-bit thermometer code.

| N | Thermometer code |

|---|------------------|

| 0 | 0000             |

| 1 | 1000             |

| 2 | 1100             |

| 3 | 1110             |

| 4 | 1111             |

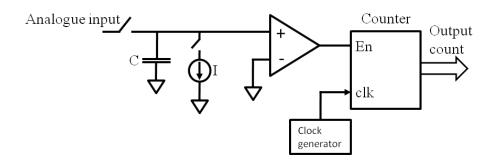

#### 2.2.3.2 Charge run down ADC

Figure 2-10 shows a simple block diagram of the run-down ADC [43]. In this ADC, the unknown analogue voltage is sampled into a capacitor. At the time of conversion, the capacitor is discharged through a constant current source (*I*). The voltage on the capacitor is constantly observed using a comparator for a certain threshold (in this case *GND*). While the capacitor is discharged, the output voltage of the comparator is high, and therefore the counter is enabled and counts a fixed clock frequency. At the point at which the voltage on the capacitor reaches the threshold voltage (capacitor is fully discharged), the comparator output drops to zero and this disables the counter. The count value of the counter is then the digital value of the input analogue voltage.

Figure 2-10 Charge run down ADC.

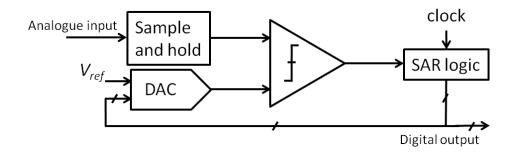

#### 2.2.3.3 Successive-approximation register (SAR)

Successive approximation technique converts the analogue voltage into a digital value using a method called binary search [44, 45]. The conversion in this technique can be simply explained in two phases. In the first phase, using a binary search algorithm, a binary combination is applied to a DAC. The DAC generates an analogue voltage which, in the second phase, is compared to my unknown input voltage using a simple comparator. The binary code which generates the closest value to my unknown voltage

is the digital output of the ADC. Figure 2-11 depicts the block diagram of a simple SAR ADC [46].

At the beginning of the conversion phase, the digital code generated by SAR logic is MSB='1' and the other bits are zero. This generates  $V_{ref}/2$  at the output of the DAC. This voltage is compared to the unknown input voltage. If it is greater, MSB is set to zero and if it is less, MSB is held high. Then SAR moves to the next bit down and performs the same procedure. At the end of the conversion phase, a digital combination is achieved which represents the value of the unknown input voltage. Since in the binary search method all possible quantization levels are generated and tested, this ADC is very slow in high resolution applications.

Figure 2-11 Simple block diagram of SAR ADC.

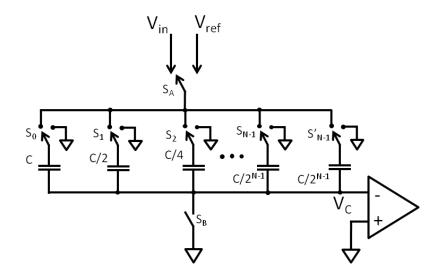

There exists another implementation for SAR ADCs called charge redistribution, which uses a charge scaling DAC architecture [47]. A simplified circuit of a charge redistribution implementation of these types of ADCs can be seen in Figure 2-12. The circuit operates in three modes; sample, hold and redistribution modes. In the sample mode, the switch  $S_A$  is connected to the input voltage  $(V_{in})$  and the switch  $S_B$  is closed. As a result,  $V_{in}$  is sampled on each capacitor in the network. In the hold mode,  $S_B$  is opened and  $S_0 \ldots S'_{N-1}$  are connected to the ground, therefore  $V_C$  becomes  $-V_{in}$  which means that the  $V_{in}$  has been sampled at the input of the comparator. In the redistribution

mode, the  $S_B$  is opened and the  $S_A$  switch is connected to the reference voltage  $(V_{ref})$ . In this mode the actual conversion is started by connecting the MSB switch  $(S_0)$  from the ground to the  $V_{ref}$ . The equivalent capacitor in the network is 2C, and therefore connecting C to the  $V_{ref}$  creates a 1:1 capacitor divider between C and the remaining capacitors in the network, which is also C. This produces a value of  $V_C$  equal to  $-V_{in}$ , which was charged to the network before, plus  $V_{ref}/2$  which is obtained as a result of the 1:1 capacitor divider. The value of the bit is determined by the operation of the comparator at this stage. For values of  $V_C$  lower than zero, which means that  $V_{in}$  is greater than  $V_{ref}/2$ , the comparator output jumps to high. This indicates that the MSB should be set to logic "1". Conversely, for values of  $V_C$  greater than zero, the comparator output stays low which indicates that the MSB should be set to logic "0". The conversion is carried out for all the bits in the same way until the value of LSB is produced.  $V_C$  for the LSB is  $-V_{in} + (MSB)V_{ref}/2 + (MSB-1)V_{ref}/4 + ... + (LSB)V_{ref}/2^N$ . According to the operation of this ADC, at the end of the conversion cycles,  $V_C$  should converge to zero.

Figure 2-12 N-bit SAR-ADC based on charge redistribution.

The major energy consumption involved in the charge redistribution implementation of SAR ADCs is due to the generation of a fixed voltage reference. There exist a number of clever SAR ADC designs in which the designer removes the requirement for a reference voltage [48, 49] by using differential configurations for the capacitor network. Furthermore, an extra capacitor is used to shift the input voltage to high and to create  $2V_{in}$  voltage. Then, the ADC will compensate for  $2V_{in}$  so that at the end of the conversion cycles  $V_C$  converges to  $V_{in}$ , as opposed to the conventional design in which  $V_C$  would converge to zero. However, although the requirement of a voltage reference is removed, the fixed clock frequency and accurate switching timing are still required [50].

### 2.2.3.4 Delta-sigma ADC

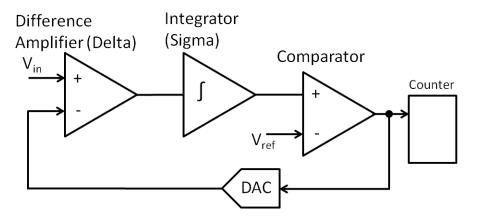

In this section, the operation of the delta-sigma ADC is studied largely from an experimental point of view [51]. A simple block diagram of such ADC is depicted in Figure 2-13. In this ADC, the unknown input voltage is differentiated from the output of the DAC (in the feedback loop) to provide the input to the integrator.

Figure 2-13 Delta-sigma ADC.

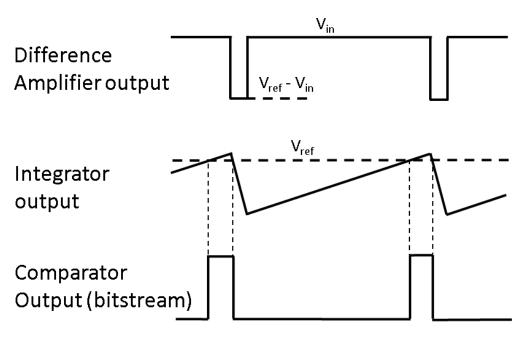

The integrator generates a ramp signal in response to the edges of the input pulses. The ramp signal is compared to the reference voltage at the comparator, generating a bitstream at its output. As shown in Figure 2-14, this bitstream is oversampled using a counter with a clock frequency of at least double the frequency of the bitstream (Nyquist rate). Usually, the output of the counter is applied to a low-pass filter to remove the effects of quantization error and oversampling noise.

Figure 2-14 Delta-sigma operation waveforms.

The delta-sigma ADC is capable of producing high resolution output; however, due to oversampling, it is fairly slow compared to other types of ADCs.

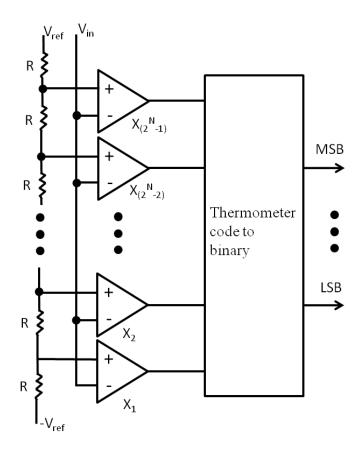

### 2.2.3.5 Flash ADC

In the flash ADC, the input voltage is simply compared to several pre-set values using a number of analogue comparators. For each voltage interval that the input analogue voltage is realized in, a binary code is generated using simple combinational logics. Flash ADCs are well known for their speed of conversion compared to other types of ADCs. However, a significant number of comparators, even for low levels of precision, is required. In order to mitigate this, a design has been reported which uses simple sense amplifier flip-flops instead of an analogue comparator [52].

Figure 2-15 Block diagram of Flash ADC.

Following table provides an overview of different analogue to digital converters in terms of speed, precision, power consumption and types of reference requirements:

Table 2-2 an overview of different ADC techniques.

| Type of ADC | Advantageous                                            | Disadvantageous                                                                                                                       | Reference required                      |

|-------------|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| SAR         | Medium to high<br>resolution (8-18 bits)<br>[46]        | Medium speed (up to 5Msps)                                                                                                            | Voltage and time reference              |

| Delta-Sigma | High resolution (16-24 bit), low power consumption [53] | Low speed due to<br>oversampling (typical<br>range of 100Ksps up<br>to 4Msps for<br>ADS1271 and<br>ADS1675 from Texas<br>Instruments) | Voltage reference and fixed clock pulse |

| Flash       | Very fast (Gsps) [53]                                   | Low resolutions (8-<br>bit), large power<br>consumption and area                                                                      | Voltage reference                       |

Table 2-2 shows that providing reference (voltage and time) for above ADC designs is essential. However, the above table contains only ADCs which are discussed in this thesis, there are no reference-free ADCs in the literature. Consequently, they will fail to operate in the energy harvesting environment.

It is intuitively obvious that, for any electronic circuit operating in an energy harvesting system, energy consumption is crucial. Note that, in these systems, designing low-energy consumption circuits is not the goal but a prerequisite. In the following section, the circuit energy consumption is analysed however, low-energy consumption techniques are described in Appendix A.

# 2.3 Circuit energy consumption

Energy in a circuit is consumed through dynamic (or switching), static (or leakage) and short circuit energy dissipation [54].

$$E_{Total} = E_{Dvnamic} + E_{static} + E_{short-circuit}$$

(2 - 6)

The energy consumption of a switching action is called dynamic energy consumption, which is quadratically related to  $V_{dd}$  [55]:

$$E_{Dynamic} = \alpha C V_{dd}^{2} \tag{2-7}$$

Where  $\alpha$  is the activity factor (the number of active nodes in the circuit per cycle), C is the switch capacitance and  $V_{dd}$  is the supply voltage. For supply voltages above threshold level, switching or dynamic energy consumption is dominant.

The next type of energy consumption in a circuit is static or leakage energy consumption. This type of energy consumption exists due to the current leakage in transistors which are not switching. Static energy consumption is given by [55]:

$$E_{static} = V_{dd}I_t e^{\frac{V_{gs} - V_{th}}{nV_T}} \left(1 - e^{-\frac{V_{ds}}{V_T}}\right) T \tag{2-8}$$

$$I_{t} = \mu_{eff} C_{ox} \frac{w}{l_{eff}} (m-1) V_{T}^{2}$$

(2-9)

Where  $I_t$  is a technology-dependent scaling parameter,  $V_{gs}$  is the gate-to-source voltage,  $V_{ds}$  is drain-to-source voltage,  $V_{th}$  threshold voltage,  $V_T$  thermal voltage,  $v_T$  is related to the subthreshold slope,  $v_T$  is the latency of computation,  $v_T$  is the effective mobility,  $v_T$  is the transistor width and  $v_T$  is the effective channel length.

When the input signal is applied to a circuit, there is a moment at which the NMOS and PMOS transistors are simultaneously on. At that moment a path is established from  $V_{dd}$  to GND. The current flowing through that path creates the short-circuit energy dissipation [56]:

$$E_{short-circuit} = \frac{\beta}{12} (V_{dd} - 2V_T)^3 \tau \tag{2-10}$$

Where  $\beta$  is the gain factor,  $\tau$  is the rise or fall time of the inputs of the inverter. Since the amount of short circuit energy dissipation is very small compared to the dynamic and static energy consumption, it is usually neglected in calculating total energy consumption [56].

Asynchronous circuits are mostly described as low-power circuits. The following section details the asynchronous design technique in terms of power consumption.

#### 2.3.1 Asynchronous design

Most digital circuits are designed using a global clock signal. This signal allows events in the circuit to be accurately timed. For example, the clock signal can be used to synchronize the necessary communication, and also to sequence the operations within

the circuit. From a design point of view, circuits which employ clock signals in their operations are called synchronous circuits, whereas asynchronous circuits are designed to be clockless. For the latter circuits, operations are timed relative to each other rather than to a global clock signal. For instance, a handshaking protocol can be used to configure the communication or sequence between operations in the circuit. Several of the most common such protocols are described below.

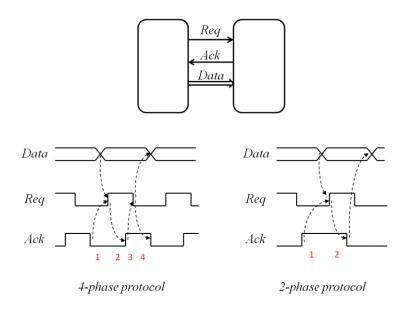

### 2.3.2 Bundled data

In this protocol, the data in normal Boolean format traverses between components using Req and Ack signals. This is typically implemented either in a 4-phase or 2-phase handshaking protocol. In 4-phase, when the data is ready the sender sets the Req high, where at this stage Ack is low. The receiver detects the high Req, samples the data and sets the Ack high. The sender notices the positive edge of the Ack signal and sets Req low. At the end, the receiver senses the low Req and so in response it sets the Ack low. This protocol is presented in Figure 2-16 using data, Req and Ack waveforms.

Figure 2-16 Bundled data protocol

The unnecessary transition to zero in 4-phase handshaking costs energy and reduces speed. In comparison, the 2-phase handshaking protocol does not create any transition to zero. Using simple waveforms, this protocol is shown in Figure 2-16. Note that here the signal events (or edges) on *Req* and *Ack* are used to complete the communication. In this protocol, once the receiver is ready to receive the data and the data is ready, the sender issues a signal event on the *Req* wire. The receiver detects this, absorbs the data and generates an event on the *Ack* wire which signals that the handshake is finished.

# 2.3.2.1 Request signal

In the bundled-data protocol, one of the critical assumptions is that the sender issues the *Req* signal after producing the data. As a result, different techniques and design methods have been explored to guarantee the appearance of the *Req* signal after the *data*. Some of these techniques are listed below:

a) The circuit is designed in such a way that it generates a completion signal at the end of its operation.

- b) The circuit is bundled to a delay line. The assumption is that the delay line is longer than the longest delay path in the circuit.

- c) In using a dual rail protocol, each logic bit is encoded into true and false signals as presented in Figure 2-17. A spacer stage which acts as completion signal is accommodated between two successive valid data items.

Figure 2-17 Dual rail encoding

Due to the removal of the clock signal in asynchronous circuits, they are classified into three different classes according to the quality of their operation with respect to the delay assumptions made:

- a) Self-timed or bundled delay circuits, which require extra effort and consideration in order to satisfy all timing assumptions so as to operate robustly.

- b) Speed-independent circuits, where the circuit operation is robust irrespective of gate delays and assuming that wire delays are negligible.

- Delay-insensitive circuit operation is robust assuming any arbitrary values for gate or wire delay.

In synchronous circuits, using the clock signal makes the design process easier, but the energy consumption of the circuit increases. Since the clock frequency is set for the longest delay path in the circuit, with perhaps an extra safety margin, an idle state is created at each clock cycle for the shorter delay paths in the circuit. This increases the leakage energy consumption of the circuit. Generating and maintaining the clock signal is another source of energy overhead in synchronous circuits. Avoid clocking the circuit by using asynchronous circuits is one of the approaches used to decrease the energy consumption of the system [54, 57, 58].

Typically, asynchronous circuits consume less energy compared to their synchronous counterparts. One of the reasons for this is that the asynchronous operation does not allow for an idle state in the circuit, and therefore the leakage energy consumption decreases dramatically. In asynchronous designs, a completion detection signal is generated at the end of circuit operation. Once the completion detection is issued, the circuit realizes the outputs and starts a new task and thus no idle state is created. A circuit with no idle mode has less time to leak.

Despite the advantages mentioned above, employing asynchronous circuits can create a number of challenges. For instance, designing a circuit which can produce a completion signal is not an easy task. Therefore, techniques such as bundled delay lines or dual-rail implementation are used which require extra logic. The extra logic added to these circuits usually increases the energy consumption overhead. Another challenge is that the asynchronous designs are not fully supported by commercial Electronic Design Automation (EDA) tools [57]. Therefore, asynchronous circuits are often implemented using custom-built tools.

#### 2.3.3 Dynamic voltage scaling (DVS)

It is well-known that the supply voltage  $(V_{dd})$  has a direct effect on the circuit energy consumption and operating speed [59]. An example of voltage scaling to achieve low-energy consumption is to operate at the subthreshold region below the transistor threshold [55, 60, 61]. In this region, which is also called weak inversion, the ratio of

( $I_{on}$  / $I_{off}$ ) decreases exponentially (in subthreshold) [60].  $I_{on}$  is defined as the drain-to-source current when the transistor is on and  $I_{off}$  is the current when the transistor is in the idle mode.

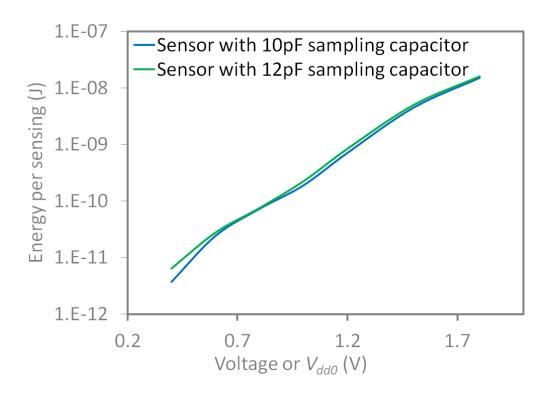

It is known that, if circuit supply voltage ( $V_{dd}$ ) is decreased, the gate propagation delay (T) will increase exponentially, [55] and therefore leakage (static) energy consumption ( $E_s$ ) increases exponentially. For values of  $V_{dd}$  greater than the threshold voltage, the dynamic energy consumption is dominant, and hence total energy consumption decreases while  $V_{dd}$  decreases. In the subthreshold region, the leakage grows exponentially when  $V_{dd}$  decreases. At a certain level of  $V_{dd}$ , the amount of leakage energy consumption will exceed the amount of dynamic energy consumption, and consequently the total energy consumption starts to increase with decreasing  $V_{dd}$ . At that level of  $V_{dd}$ , the circuit energy consumption per switching activity is at a minimum, and this is called the minimum energy point (MEP) [29]. As an example, the energy consumption of a simple asynchronous counter is plotted in Figure 2-18. This figure shows that the counter energy per count is at its minimum at 280mV. Research has shown that, by operating at the minimum energy point, more than 50% energy savings can be achieved [29].

Figure 2-18 Energy per transition for an 8-bit asynchronous counter.

For this simulation, energy consumption of the counter was measured under different fixed level of supply voltages.

## 2.3.4 Dynamic frequency scaling (DFS)

The frequency of the clock signal in a circuit is determined by the speed of operation in the circuit. On the other hand, the speed of operation in the circuit is determined by the supply voltage of the circuit. Therefore, the level of supply voltage is determined by the frequency of the clock signal of the circuit. In dynamic frequency scaling technique the frequency of clock signal is decreased, consequently, the required supply voltage can be decreased. Therefore, by decreasing the supply voltage the overall energy consumption of the circuit is decreased. This technique is often referred to as dynamic voltage/frequency scaling (DVFS) as the true energy saving comes from decreasing the supply voltage [62].

### 2.3.5 Voltage converters

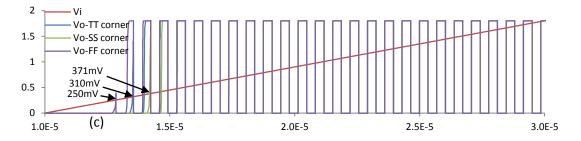

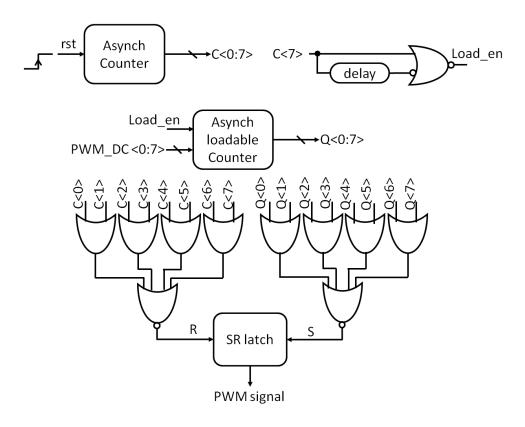

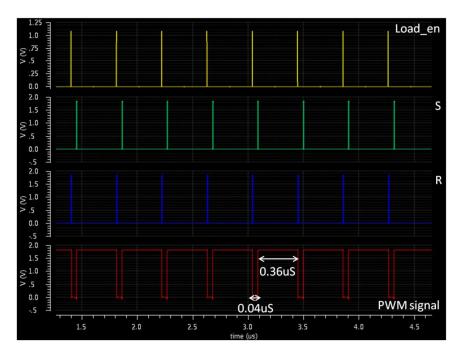

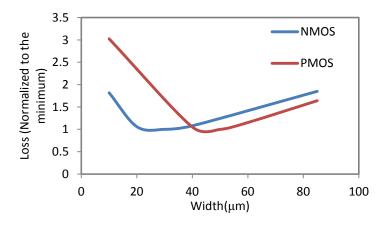

The key requirement of DVS is to design an efficient DC to DC converter which can scale the level of voltage according to the demand from the load circuit. A considerable