### **Newcastle University**

Faculty of Science, Agriculture and Engineering

# Power Delivery Mechanisms for Asynchronous Loads in Energy Harvesting Systems

## Xuefu Zhang

A thesis submitted for the degree of Doctor of Philosophy

May 2013

| 1. Reviewer:                           |

|----------------------------------------|

| 2. Reviewer:                           |

| Day of the defence:                    |

| Signature from head of Ph.D committee: |

|                                        |

# **Contents**

| List | of Figures                                                    | I    |

|------|---------------------------------------------------------------|------|

| List | of Tables                                                     | VIII |

| List | of Publications                                               | IX   |

| Abst | tract                                                         | XI   |

| Ackr | nowledgements                                                 | XIII |

| Acro | onyms                                                         | XV   |

| Intr | oduction                                                      | 1    |

| 1.1  | Motivation                                                    | 3    |

| 1.2  | Contributions                                                 | 9    |

| 1.3  | Organization                                                  | 10   |

| Bacl | kground                                                       | 13   |

| 2.1  | Energy Harvesting Methods for Micro-Scale Electronic Systems. | 13   |

| 2.2  | Energy Transducers                                            | 15   |

| 2.:  | 2.1 Piezoelectric Energy Harvesting                           | 16   |

| 2.3 | Ene   | ergy Storages                                                 | 19 |

|-----|-------|---------------------------------------------------------------|----|

| 2   | .3.1  | Non-rechargeable Vs Rechargeable Batteries                    | 19 |

| 2   | .3.2  | Supercapacitors Vs Rechargeable Batteries                     | 20 |

| 2.4 |       | nventional Power Delivery Method for Micro-Scale Energy Harve | _  |

| 2   | .4.1  | Power Delivery Method for Stage 1                             | 22 |

| 2   | .4.2  | Power Delivery Method for Stage 2                             | 23 |

| 2.5 | Sur   | nmary                                                         | 24 |

| Bas | elin  | ie Research                                                   | 26 |

| 3.1 | On-   | -Chip Power Delivery for Multi-components                     | 26 |

| 3   | .1.1  | Off-Chip Vs On-Chip Power Delivery for Multi-Components       | 27 |

| 3.2 | On-   | -Chip Power Delivery Units                                    | 29 |

| 3   | .2.1  | Linear Regulators                                             | 29 |

| 3   | .2.2  | Buck Converters                                               | 30 |

| 3   | 3.2.3 | Switched Capacitor DC/DC Convertors (SCC)                     | 33 |

| 3.3 | On-   | -Chip Voltage Sensing                                         | 48 |

| 3   | .3.1  | Traditional ADCs and Comparators                              | 49 |

| 3   | 3.3.2 | Power-on-Reset Circuits                                       | 50 |

| 3   | 3.3.3 | Reference-Free Voltage Sensors                                | 51 |

| 21  | C.,,, | nmary                                                         | 51 |

# **Switched Capacitor DC/DC Converter Investigation**

|         | 5!                                                                   |

|---------|----------------------------------------------------------------------|

| 4.1 Int | troduction55                                                         |

| 4.2 SC  | C Investigation Methodology56                                        |

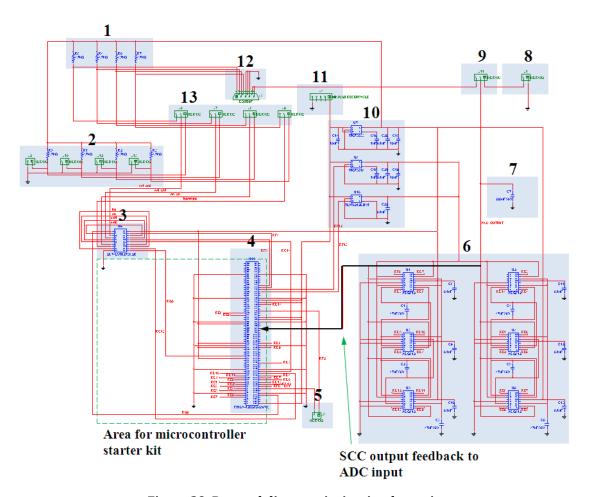

| 4.2.1   | SCC Based Asynchronous SRAM Chip Verification System57               |

| 4.2.2   | Microcontroller Application58                                        |

| 4.2.3   | Generating Six Various Output Voltage Levels59                       |

| 4.2.4   | D-Sub Connectors for Power and Signal Connection60                   |

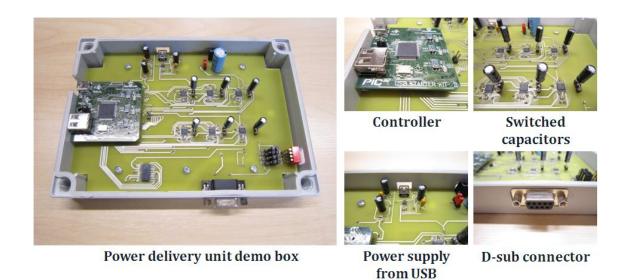

| 4.3 Ha  | ardware Implementation60                                             |

| 4.3.1   | Power Delivery Unit Circuit Schematic62                              |

| 4.4 Mi  | crocontroller Programming62                                          |

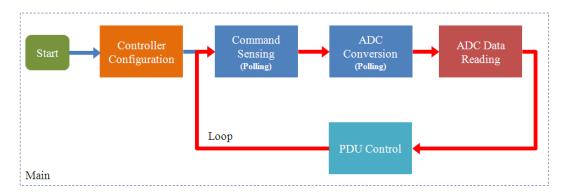

| 4.4.1   | Polling Method63                                                     |

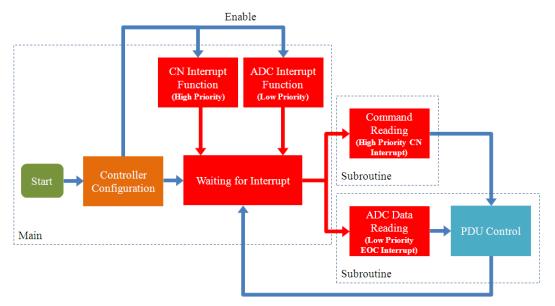

| 4.4.2   | Interrupt Method63                                                   |

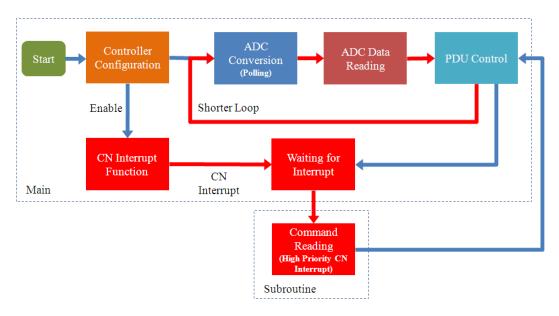

| 4.4.3   | Hybrid Method64                                                      |

| 4.4.4   | Sampling Performance65                                               |

| 4.5 SC  | C Hardware Investigation and Asynchronous SRAM Chip Verification .66 |

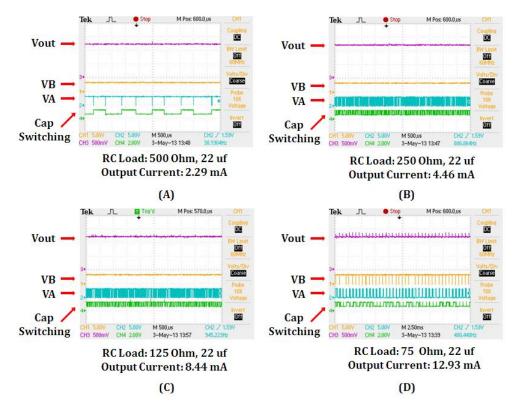

| 4.5.1   | SCC Hardware Investigated with a RC Load66                           |

| 4.5.2   | Test 1: Deliver 1.2 V to an Adjustable RC Load68                     |

| 4.5.3   | Test 2: Deliver Various Vdd to a Fixed RC Load70                     |

| 4.5.4   | Test 3: Deliver a Variable Vdd to an Asynchronous Chip72             |

|   | 4.6 | Sur | nmary and Conclusions                                | 73 |

|---|-----|-----|------------------------------------------------------|----|

| A | No  | ve  | l Power Delivery Method                              | 75 |

|   | 5.1 | Int | roduction                                            | 75 |

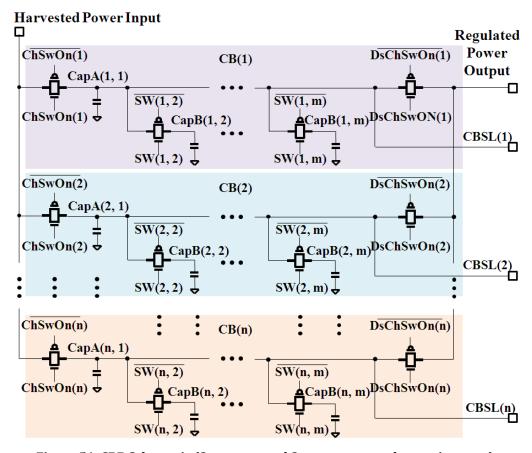

|   | 5.2 | Pro | pposed Capacitor Bank Block                          | 77 |

|   | 5.2 | 2.1 | Challenges of Using SCC in Energy Harvesting Systems | 77 |

|   | 5.2 | 2.2 | CBB Concept and Proposed CBB Structure               | 78 |

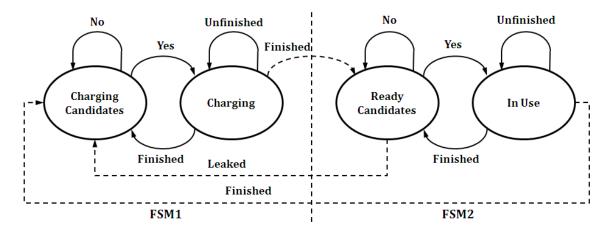

|   | 5.2 | 2.3 | Finite State Machines for CBB Control                | 80 |

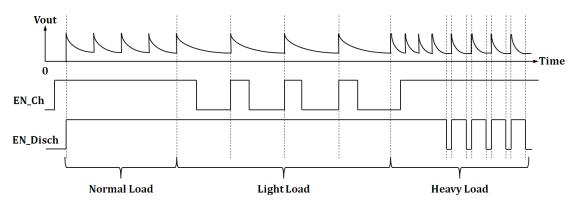

|   | 5.2 | 2.4 | CBB Behaviours with Different Loads                  | 80 |

|   | 5.3 | Cor | nparison Study System Design                         | 82 |

|   | 5.3 | 3.1 | Piezoelectric Energy Harvesting Circuit Model        | 82 |

|   | 5.3 | 3.2 | System for Comparative Studies                       | 83 |

|   | 5.4 | Ass | sumptions                                            | 85 |

|   | 5.4 | 4.1 | Asynchronous Load with SCC                           | 85 |

|   | 5.4 | 4.2 | Synchronous Load with SCC                            | 86 |

|   | 5.4 | 4.3 | Asynchronous Load with CBB                           | 86 |

|   | 5.4 | 4.4 | Synchronous Load with CBB                            | 86 |

|   | 5.5 | Loa | nd Performance Results                               | 87 |

|   | 5.5 | 5.1 | Computation Performances with Moderate Power Supply  | 88 |

|   | 5.5 | 5.2 | Computation Performances with Abundant Power Supply  | 95 |

|   | 5.5 | 5.3 | Computation Performances with Sparse Power Supply    | 98 |

| 5  | 5.6 | Sur | nmary and Conclusions                                      | 101 |

|----|-----|-----|------------------------------------------------------------|-----|

| As | yr  | ıch | ronous Controller Design                                   | 103 |

| 6  | 5.1 | Int | roduction                                                  | 103 |

| 6  | 5.2 | CBl | B PDU                                                      | 105 |

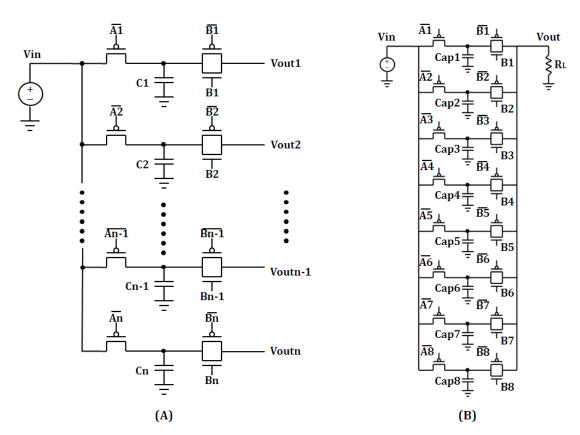

|    | 6.2 | 2.1 | CBB Schematic                                              | 105 |

|    | 6.2 | 2.2 | Schematic for Adjusting Capacitance Value                  | 106 |

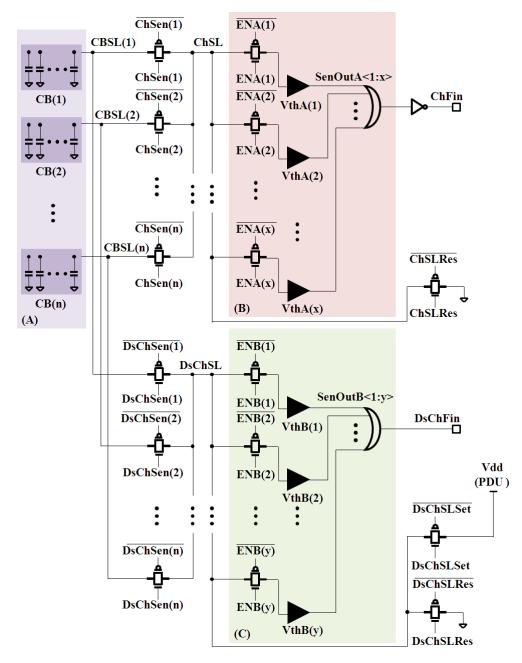

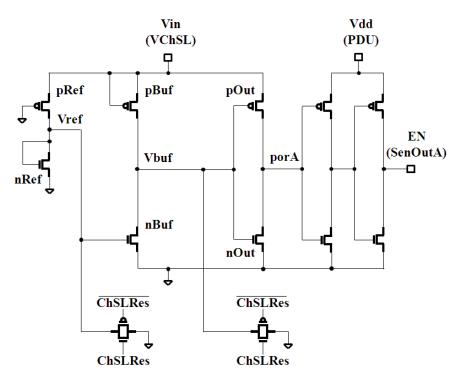

|    | 6.2 | 2.3 | Schematic for Voltage Sensing                              | 107 |

| 6  | 5.3 | Thi | reshold Voltage Sensing                                    | 109 |

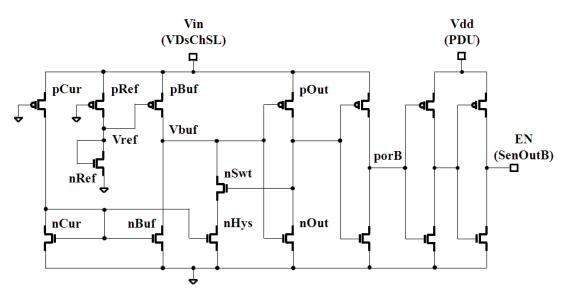

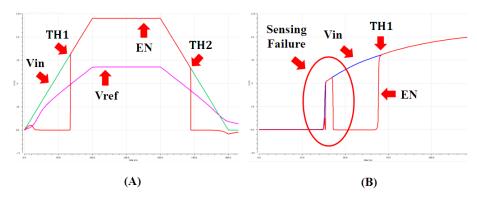

|    | 6.3 | 3.1 | Threshold Voltage Sensing for CBB PDU                      | 110 |

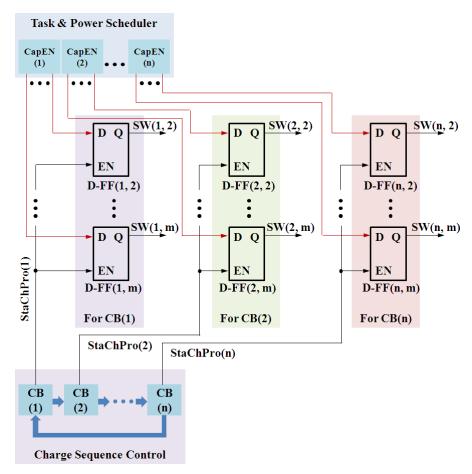

| 6  | 5.4 | Asy | nchronous Controller Cooperating with Tasks                | 112 |

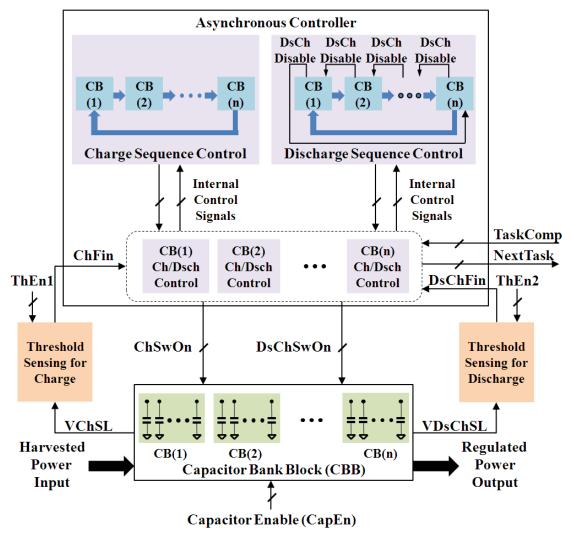

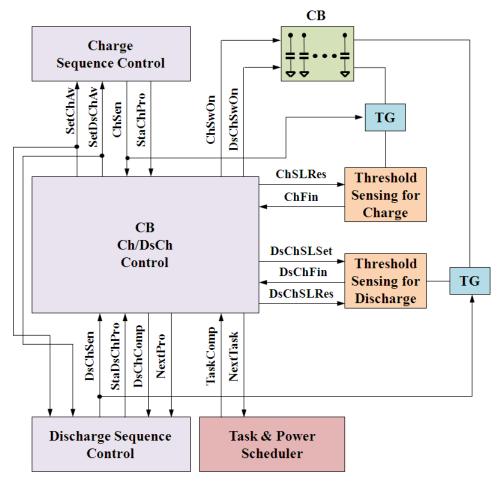

|    | 6.4 | 4.1 | General CBB PDU Structure                                  | 113 |

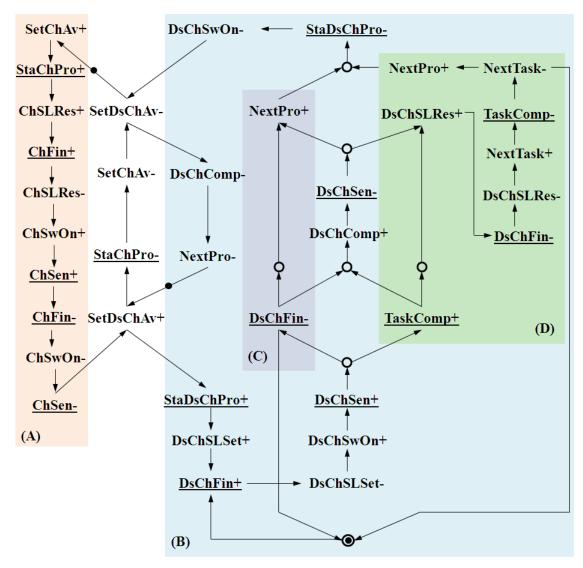

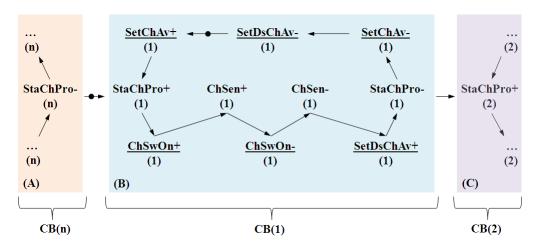

|    | 6.4 | 1.2 | Asynchronous Control                                       | 115 |

| 6  | 5.5 | CBl | B PDU Implementation and Analysis                          | 121 |

|    | 6.5 | 5.1 | Threshold Voltage Sensing                                  | 122 |

|    | 6.5 | 5.2 | Energy and Power Consumption of Threshold Voltage Sensing  | 123 |

|    | 6.5 | 5.3 | CBB PDU Working with Variable Vdd                          | 125 |

| 6  | 5.6 | CBl | B PDU Powered by a Primary Battery for EH Systems          | 127 |

|    | 6.6 | 5.1 | Power Consumption of CBB PDU                               | 127 |

|    | 6.6 | 6.2 | CBB PDU Powered by a Primary Battery                       | 128 |

| 6  | 5.7 | Loa | nd Performance Investigation for Task and Power Scheduling | 130 |

| 6.8  | Summary and Conclusions                                           | 135 |

|------|-------------------------------------------------------------------|-----|

| А Ну | brid Power Delivery Method                                        | 138 |

| 7.1  | Introduction                                                      | 138 |

| 7.2  | Task and Power Scheduling with SCC and CBB                        | 140 |

| 7.3  | Hybrid Capacitor Bank Blocks (HCBB)                               | 141 |

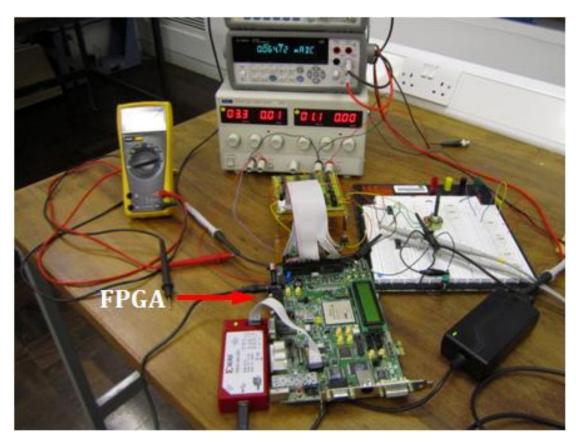

| 7.4  | Hardware Implementation                                           | 144 |

| 7.   | 4.1 HCBB Controller Implemented on FPGA                           | 145 |

| 7.5  | Testing and Verification                                          | 148 |

| 7.6  | Summary and Conclusions                                           | 154 |

| Con  | clusions and Future Work                                          | 156 |

| 8.1  | Conclusions                                                       | 156 |

| 8.2  | Future Work                                                       | 158 |

| Bibl | iography                                                          | 161 |

| Appe | endix A: Photos & Pictures                                        | 178 |

| Appe | endix B: Program Flowcharts                                       | 184 |

| Appe | endix C: EQN Files for CBB Asynchronous Controller Models         | 190 |

| Appe | endix D: Recently Published SCC Specifications                    | 193 |

| Appe | endix E: Discharge Ranges of CBs with Different Capacitance Value | 194 |

# **List of Figures**

| Figure 1. Managy micro-system overview                                                                        | 4  |

|---------------------------------------------------------------------------------------------------------------|----|

| Figure 2. Normal and new power delivery paths for energy harvesting systems                                   | 8  |

| Figure 3. Block diagram of a micro-scale energy harvesting system                                             | 14 |

| Figure 4. Commercial piezoelectric film transducer and an example of using a piezoelectric energy transducer. | 17 |

| Figure 5. Piezoelectric energy harvesting circuit model                                                       | 17 |

| Figure 6. Specific energy comparison of secondary and primary batteries                                       | 19 |

| Figure 7. Typical micro-scale energy harvesting system                                                        | 22 |

| Figure 8. Conventional power delivery method for Stage 1                                                      | 23 |

| Figure 9. Conventional power delivery method for Stage 2                                                      | 23 |

| Figure 10. Architecture of a power delivery network to implement dynamic volta                                |    |

| Figure 11. Lumped Vs. distributed on chip DC/DC converters                                                    | 28 |

| Figure 12. Schematic representation of a series linear regulator and its model                                | 29 |

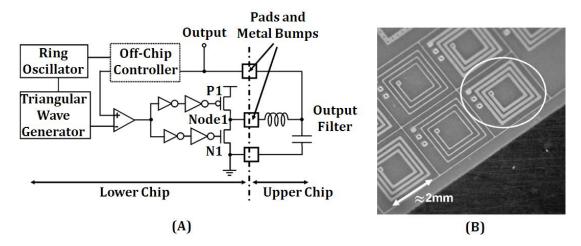

| Figure 13. Stacked-chip implementation of buck converter and 2x2 mm on-chip Loutput filter                    |    |

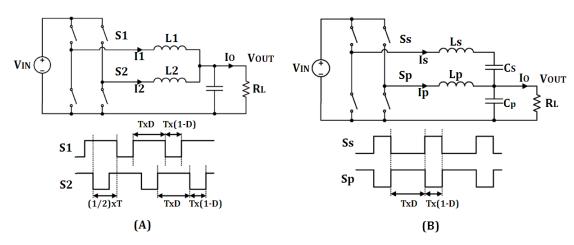

| Figure 14. Two-phase standard interleaved topology and timing diagram and                                     |    |

| stacked interleaved topology and timing diagram                                                               | 32 |

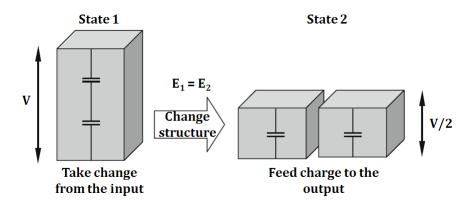

| Figure 15. The concept of capacitive conversion, from a charge point of view35                                          |

|-------------------------------------------------------------------------------------------------------------------------|

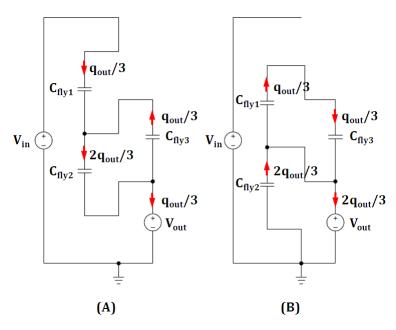

| Figure 16. A 1/3 ladder DC/DC converter topology, including networks in state 1 and state 236                           |

| Figure 17. Capacitor charge flows in ladder converter, state 1 and state 237                                            |

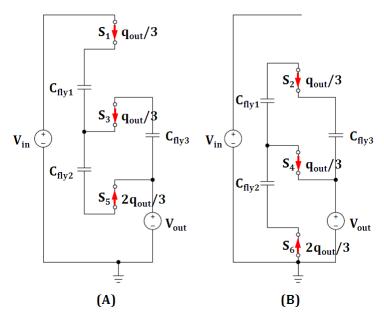

| Figure 18. Switch charge flow in ladder converter, state 1 and state 239                                                |

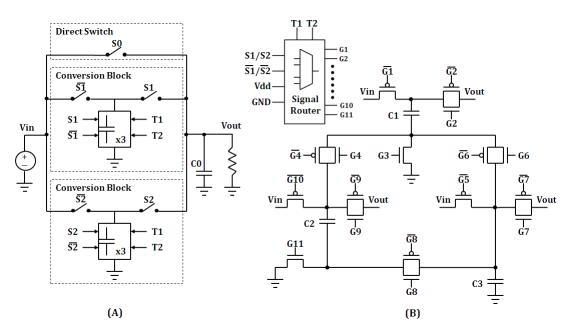

| Figure 19. Idealized 2-port SCC model40                                                                                 |

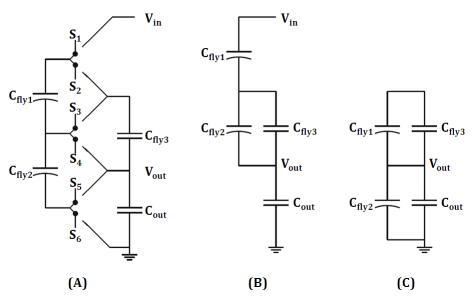

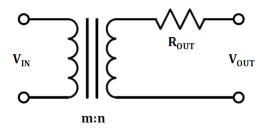

| Figure 20. Simplified architecture of SCC circuit and switches and capacitors inside conversion block and signal router |

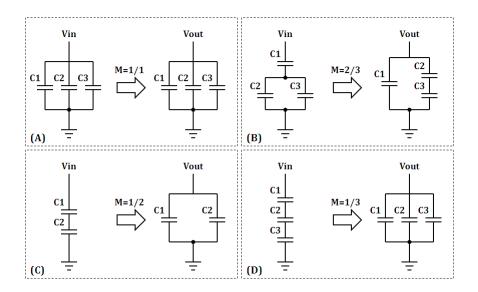

| Figure 21. Capacitor connection topologies for the different conversion ratios46                                        |

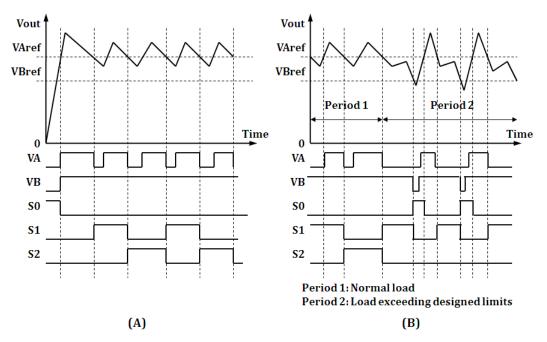

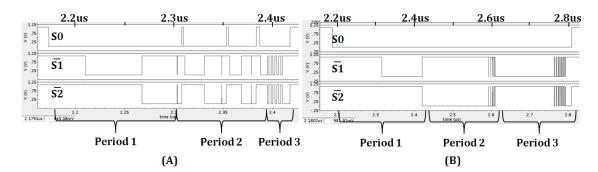

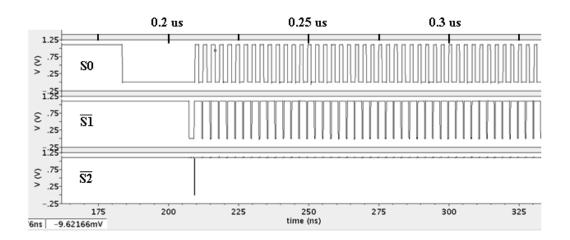

| Figure 22. Timing diagram when SCC works under: normal load and load exceeding design limit                             |

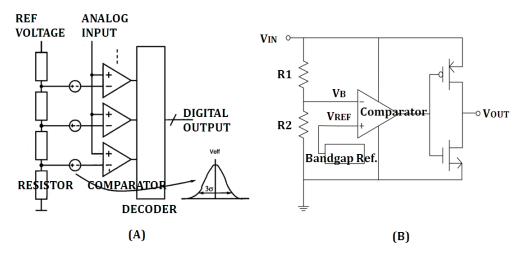

| Figure 23. Comparators used for voltage sensing: high speed CMOS ADC and voltage sensor architecture49                  |

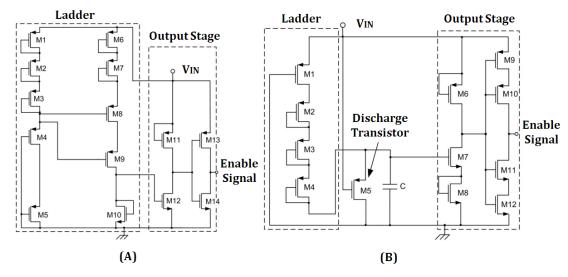

| Figure 24. Adjustable voltage sensor: Voltage Levels and Charge Capacitor50                                             |

| Figure 25. Configuration for the detection of the onset of the oscillation52                                            |

| Figure 26. General architecture of the reference-free voltage sensor and schematic of a dual-threshold POR circuit52    |

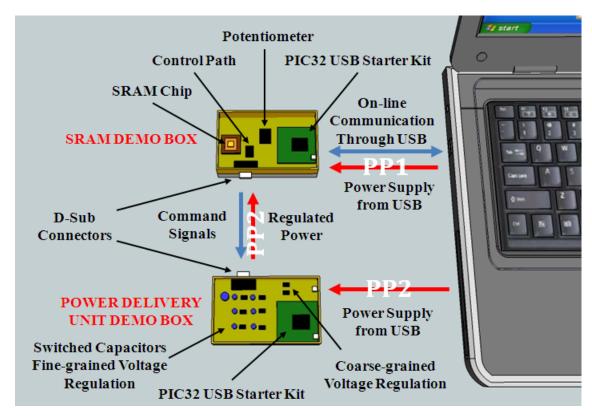

| Figure 27. Portable, user-friendly SCC based power delivery unit investigation system diagram                           |

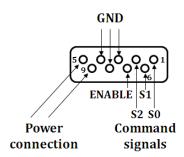

| Figure 28. Pin specification of female D-sub connecter on power delivery board60                                        |

| Figure 29. Power delivery unit circuit schematic61                                                                      |

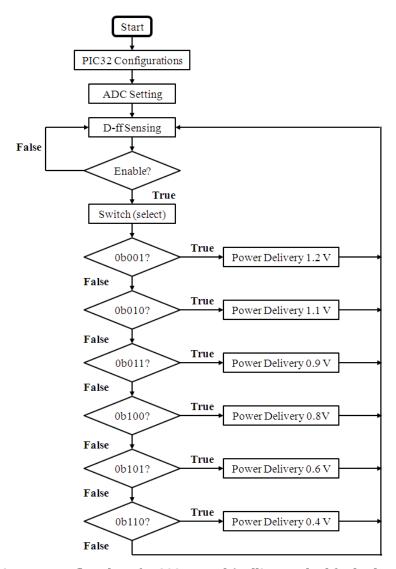

| Figure 30. Concise program flowchart for SCC control (polling method for both command and ADC sampling).                |

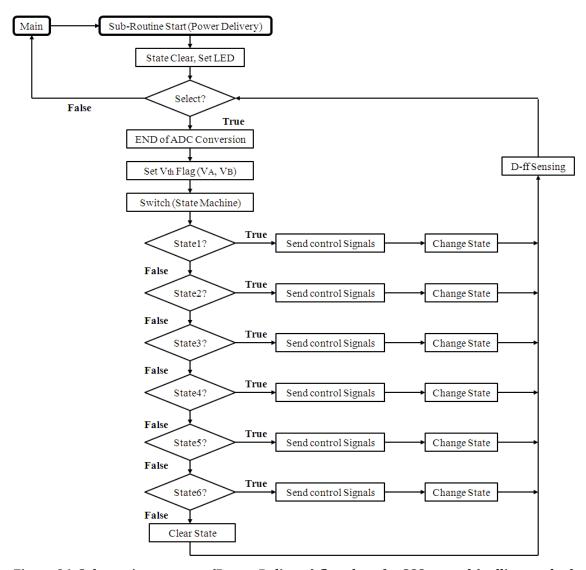

| Figure 31. Concise program flowchart for SCC control (interrupt method for both  |

|----------------------------------------------------------------------------------|

| command and ADC sampling)64                                                      |

| Figure 32. Concise program flowchart for SCC control (interrupt method for       |

| command sampling and polling method for ADC sampling)65                          |

|                                                                                  |

| Figure 33. SCC hardware investigated with a RC load67                            |

| Figure 34. 1.2 V regulated power delivered to an adjustable RC load68            |

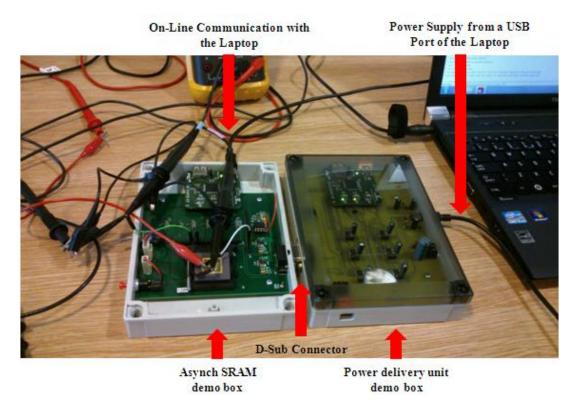

| Figure 35. Power Delivery Unit demo box powering asynchronous self-timed SRAM    |

| demo box71                                                                       |

|                                                                                  |

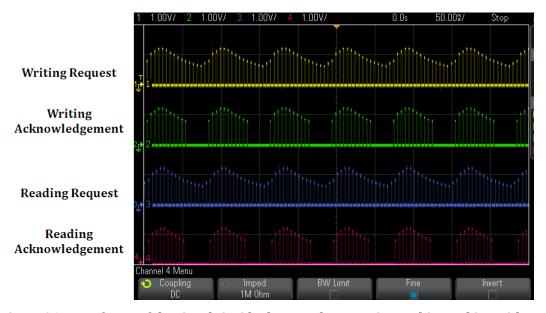

| Figure 36. Waveforms of the signals inside the asynchronous SRAM chip working    |

| with a variable Vdd generated by the power delivery unit demo board72            |

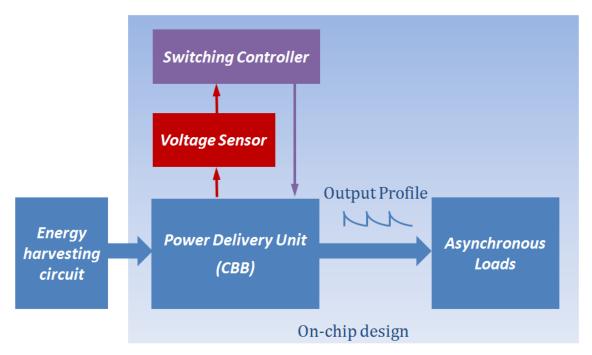

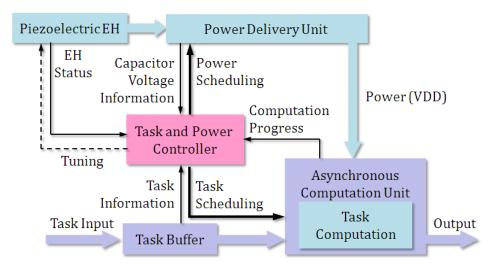

| Figure 37. Energy harvesting system employing proposed CBB for power delivery.   |

|                                                                                  |

|                                                                                  |

| Figure 38. CBB concept and proposed CBB structure79                              |

| Figure 39. FSMs for CBB control80                                                |

| Figure 40. Charge and discharge behaviours of CBB powering with medium load,     |

| small load, and large load81                                                     |

|                                                                                  |

| Figure 41. CBB charging control and discharging control cooperating with voltage |

| sensors81                                                                        |

| Figure 42. System architecture for comparative studies83                         |

|                                                                                  |

| Figure 43. Testing system with SCC and CBB respectively84                        |

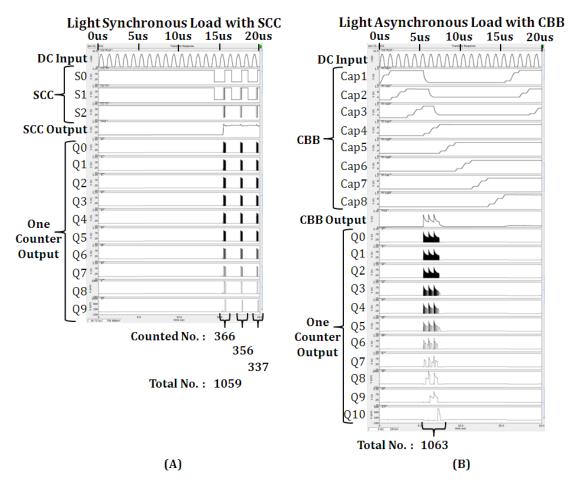

| Figure 44. Computation performances of SCC powering small and large              |

| synchronous loads88                                                              |

| 0,1011 0110 40 104401                                                            |

| Figure 45. Behaviours of SCC with large synchronous load and with small          |

| synchronous load89                                                               |

| Figure 46. Computation performances of SCC powering small and large                      |

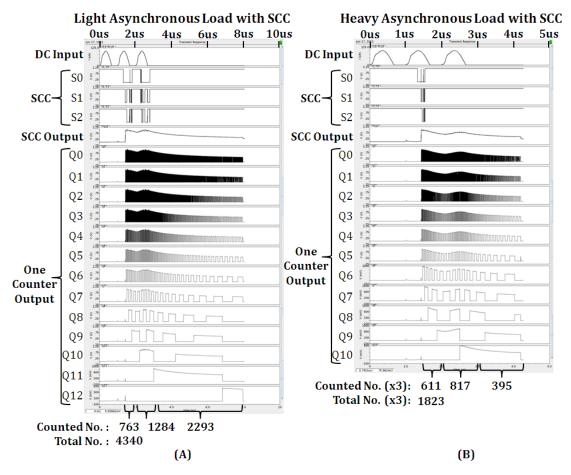

|------------------------------------------------------------------------------------------|

| asynchronous loads91                                                                     |

| Figure 47. Computation performances of CBB powering small and large asynchronous loads92 |

| usy nem onous rougs                                                                      |

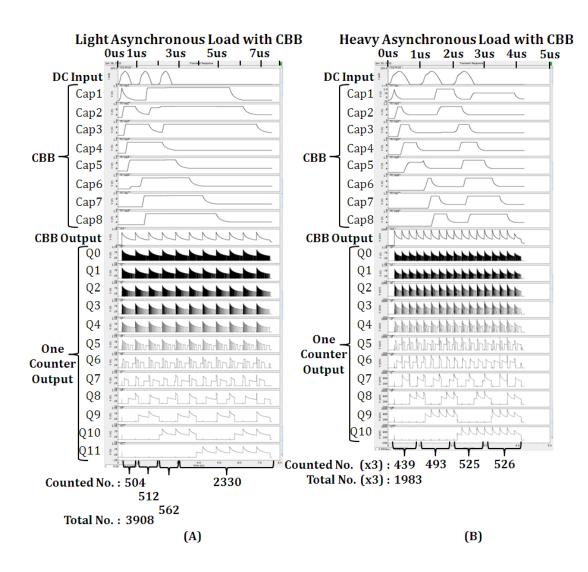

| Figure 48. Computation performances of SCC powering ultra-large synchronous              |

| load and CBB powering ultra-large asynchronous load95                                    |

| Figure 49. Behaviours of SCC powering ultra-large synchronous load96                     |

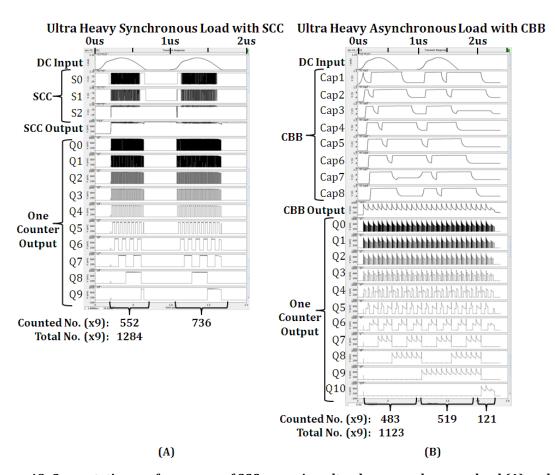

| Figure 50. Computation performances of SCC powering small synchronous load               |

| and CBB powering small asynchronous load99                                               |

| Figure 51. CBB Schematic105                                                              |

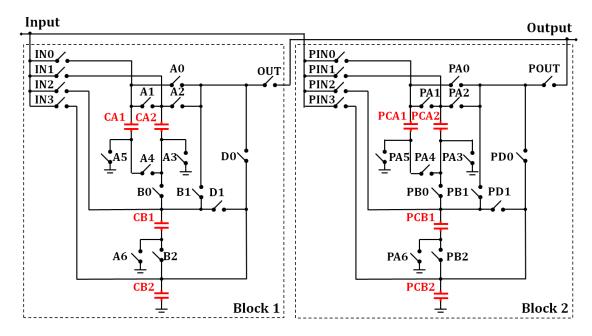

| Figure 52. Schematic for adjusting capacitance value                                     |

| Figure 53. Schematic for voltage sensing                                                 |

| Figure 54. Threshold sensing circuit employed for sensing falling voltage 110            |

| Figure 55. Threshold sensing behaviours                                                  |

| Figure 56. Threshold sensing circuit employed for sensing rising voltage                 |

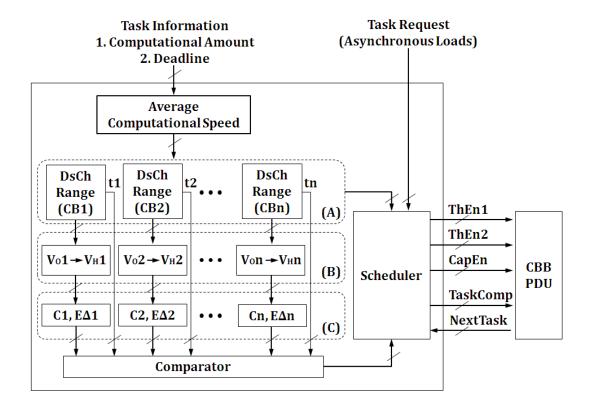

| Figure 57. Proposed asynchronous controller working with tasks113                        |

| Figure 58. Control signals employed for CBB power delivery unit115                       |

| Figure 59. STG of CB Ch/DsCh control model116                                            |

| Figure 60. STG of charge sequence control model117                                       |

| Figure 61. MUTEX for input signal DsChFin and TaskComp and MUTEX possible implementation |

| Figure 62. STG of discharge sequence control model                                       |

| Figure 63. Threshold voltage sensing for capacitor bank charge                     |

|------------------------------------------------------------------------------------|

| Figure 64. Threshold voltage sensing for capacitor bank discharge                  |

| Figure 65. Power Consumption of threshold voltage sensing circuits for charge and  |

| discharge versus different voltage levels                                          |

| Figure 66. CBB PDU working with global Vdd (Vdd variation range higher than CBB    |

| discharge range)125                                                                |

| Figure 67. CBB PDU working with global Vdd (Vdd variation range overlapping        |

| CBB discharge range)                                                               |

| Figure 68. CBB PDU power consumption Vs CBB switching frequency working with       |

| 1 V Vdd                                                                            |

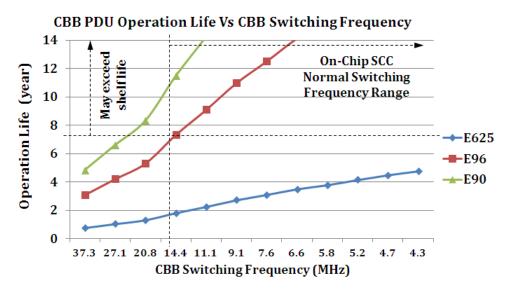

| Figure 69. CBB PDU operation life Vs CBB switching frequency                       |

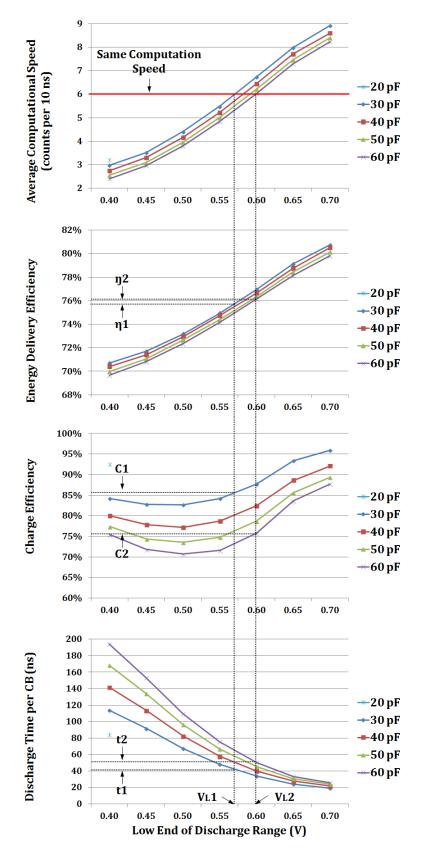

| Figure 70. Average computational speed of asynchronous load, proposed CBB PDU      |

| energy delivery efficiency, charge efficiency of capacitors employed by CB, and    |

| discharge time per CB versus discharge ranges releasing a standard energy packet.  |

| 133                                                                                |

| Figure 71. Task and power scheduler for CBB use                                    |

| Figure 72. System structure of task and power scheduling method for                |

| asynchronous loads in energy harvesting systems140                                 |

| Figure 73. Hybrid capacitor bank blocks structure                                  |

| Figure 74. Different connection topologies for CBB and SCC modes143                |

| Figure 75. Whole implementation system144                                          |

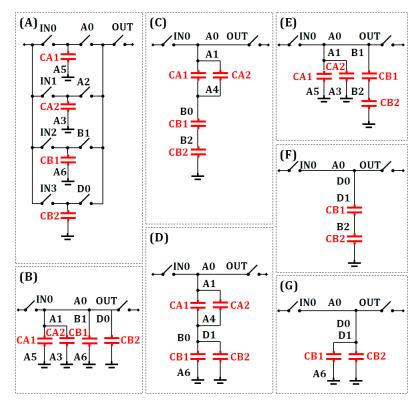

| Figure 76. Functional block diagram of hybrid capacitor bank blocks controller.146 |

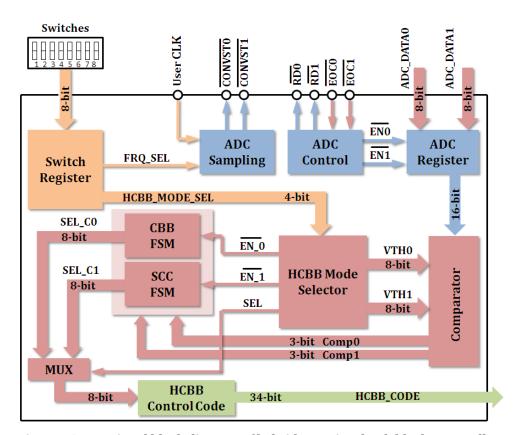

| Figure 77. Hardware verification by PCB and FPGA (A)                               |

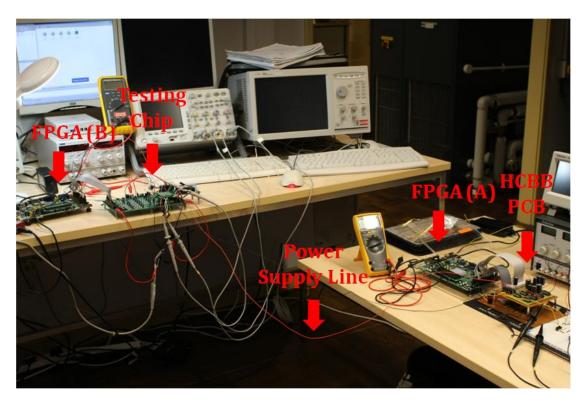

| Figure 78. Hardware verification by PCB and FPGA (B)149                                                                                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

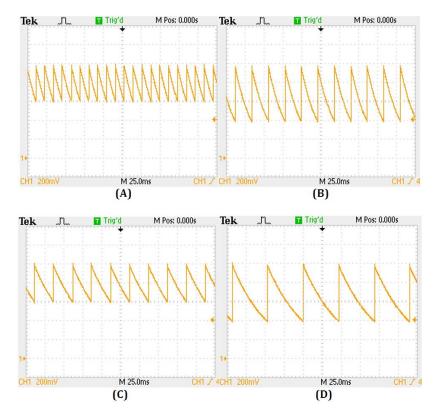

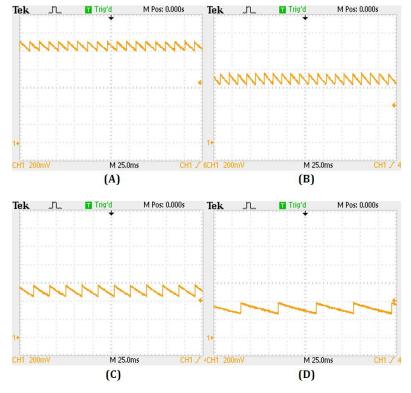

| Figure 79. Voltage waveforms at output of HCBB working in CBB mode150                                                                                                  |

| Figure 80. Voltage waveforms at output of HCBB working in SCC mode150                                                                                                  |

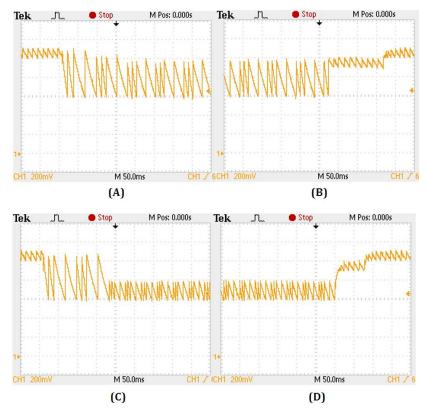

| Figure 81. Mode switching between SCC and CBB modes151                                                                                                                 |

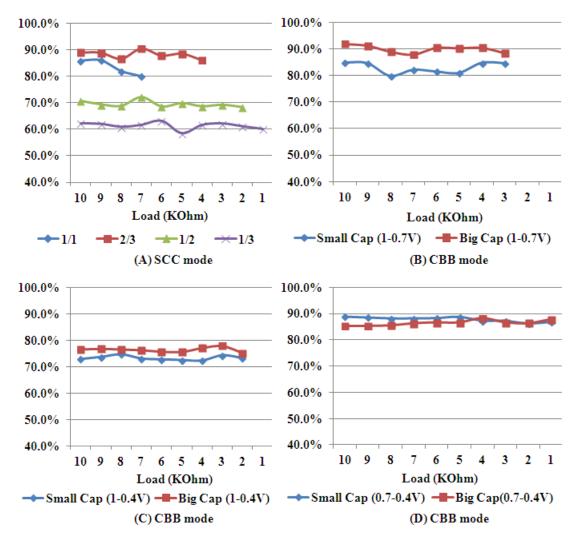

| Figure 82. Energy delivery efficiency of HCBB with RC load152                                                                                                          |

| Figure 83. HCBB powering a testing chip: asynchronous self-timed SRAM153                                                                                               |

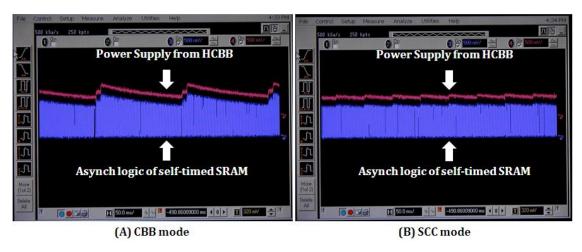

| Figure 84. Waveforms of HCBB powering an asynchronous self-timed SRAM chip in CBB mode                                                                                 |

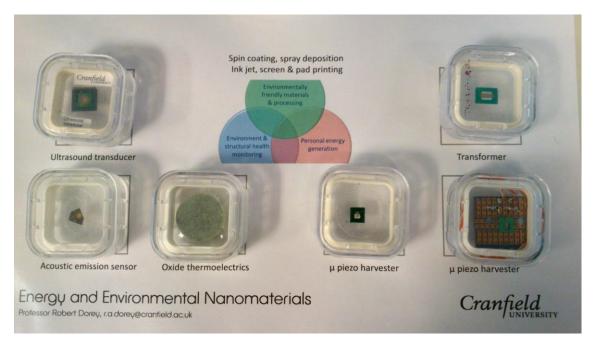

| Figure 85. Energy and environmental nano-material demonstration of Cranfield                                                                                           |

| University in Energy Harvesting 2013178                                                                                                                                |

| Figure 86. Switched capacitor based variable Vdd powered asynchronous self-timed SRAM demonstrators presented in Holistic Energy Harvesting project acceptance meeting |

| Figure 87. Switched capacitor based variable Vdd powered asynchronous self-                                                                                            |

| timed SRAM demonstrators presented in Holistic Energy Harvesting project acceptance meeting                                                                            |

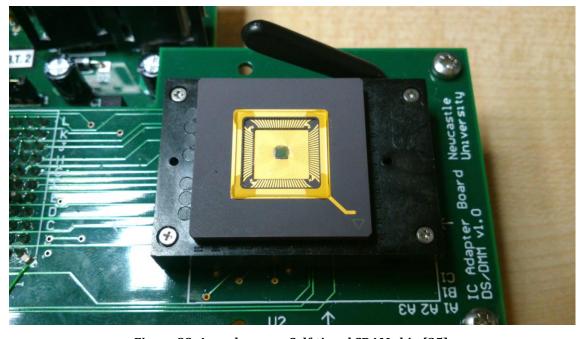

| Figure 88. Asynchronous Self-timed SRAM chip179                                                                                                                        |

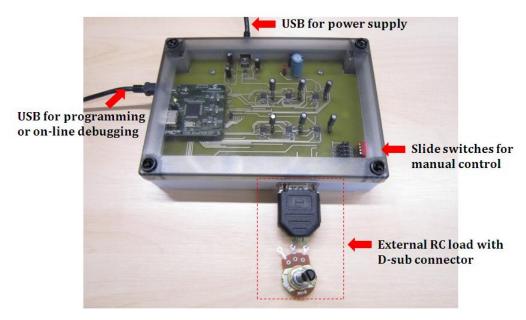

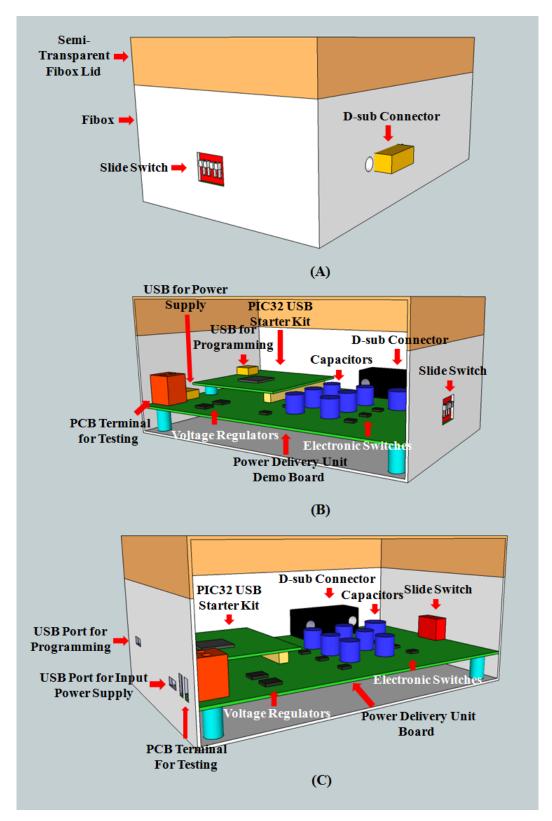

| Figure 89 Switched capacitor based power delivery unit demo box hardware implementation                                                                                |

| Figure 90. 3D graphs of power a delivery unit demo box                                                                                                                 |

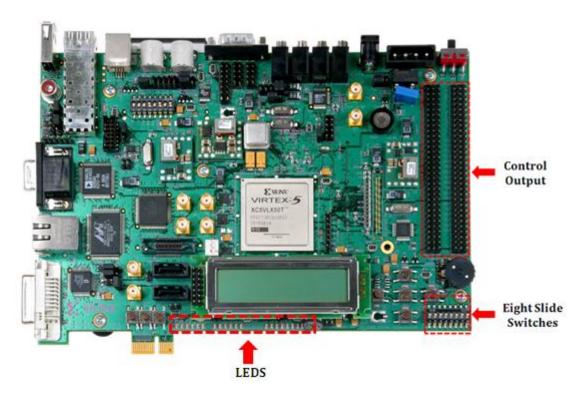

| Figure 91. FPGA development kit board Vertex 5 xc5vlx110t182                                                                                                           |

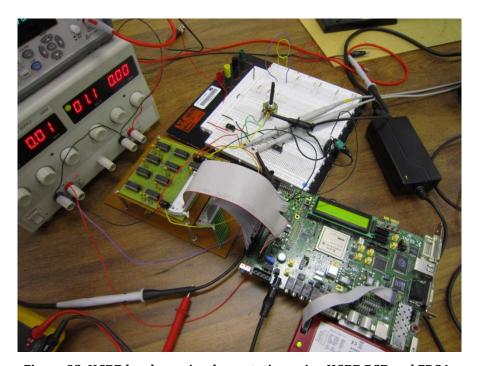

| Figure 92. HCBB hardware implementation using HCBB PCB and FPGA182                                                                                                     |

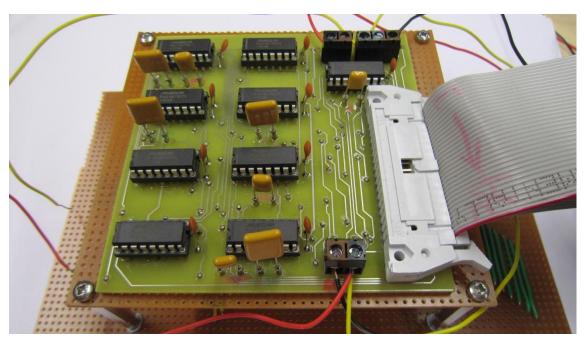

| Figure 93. HCBB circuit implemented on PCB                                                                                                                             |

| Figure 94. Two ADCs used by HCBB                                                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|

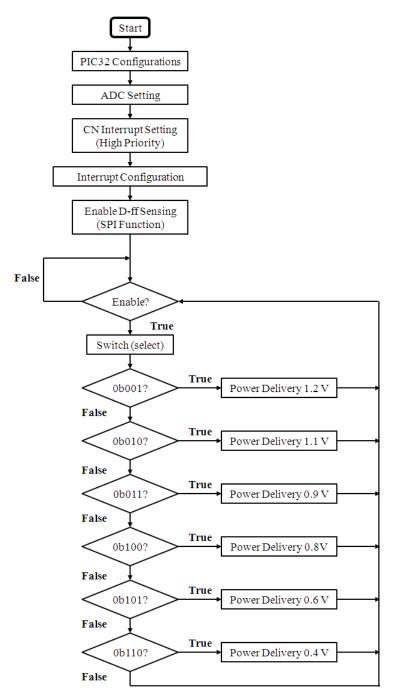

| Figure 95. Main program flowchart for SCC control (polling method for both command and ADC sensing)                                                      |

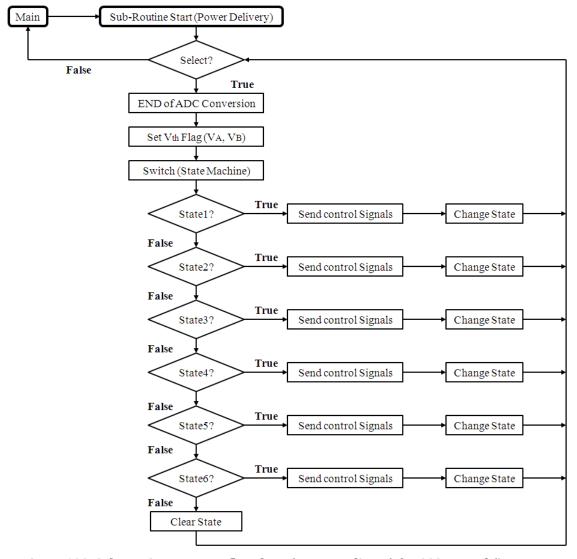

| Figure 96. Sub-routine program (Power Delivery) flowchart for SCC control (polling method for both command and ADC sensing)                              |

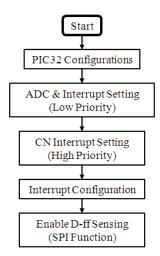

| Figure 97. Main program flowchart for SCC control (interrupt method for both command and ADC sensing)                                                    |

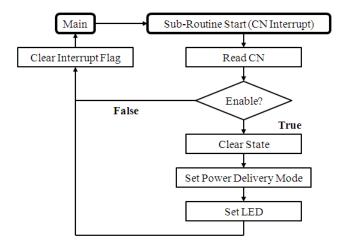

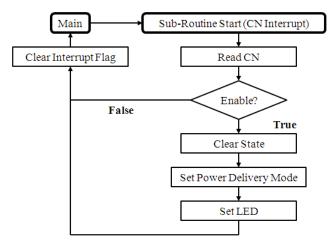

| Figure 98. Sub-routine program (CN Interrupt) flowchart for SCC control (interrupt method for both command and ADC sensing)                              |

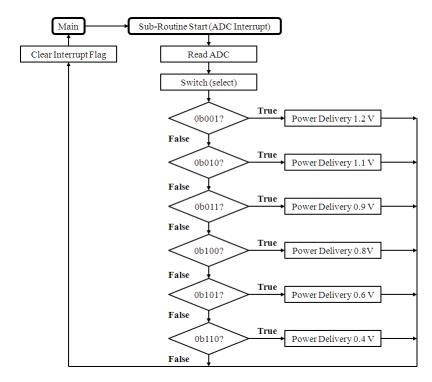

| Figure 99. Sub-routine program (ADC Interrupt) flowchart for SCC control (interrupt method for both command and ADC sensing)                             |

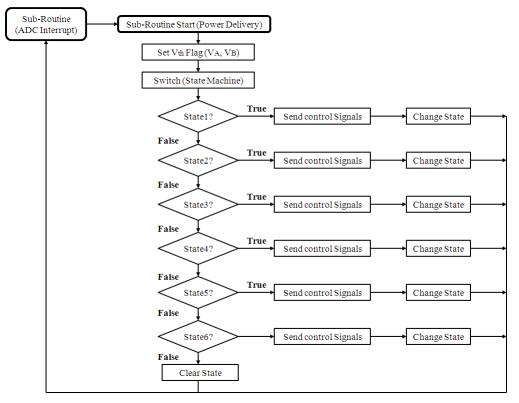

| Figure 100. Sub-routine program (Power Delivery) flowchart for SCC control (interrupt method for both command and ADC sensing)                           |

| Figure 101. Main program flowchart for SCC control (interrupt method for command sensing and polling method for ADC sensing)                             |

| Figure 102. Sub-routine program (CN Interrupt) flowchart for SCC control (interrupt method for command sensing and polling method for ADC sensing) 189   |

| Figure 103. Sub-routine program flowchart (Power Delivery) for SCC control (interrupt method for command sensing and polling method for ADC sensing) 189 |

# **List of Tables**

| Table I. Listing and characterization of energy sources                                  | 16  |

|------------------------------------------------------------------------------------------|-----|

| Table II. Performance comparison between supercapacitor and Li-ion                       | 21  |

| Table III. SCC generates six different output voltage levels for fine voltage regulation | 59  |

| Table IV. PDU microcontroller sampling performances based on three different methods     | 65  |

| Table V. Deliver various Vdd to a fixed RC load                                          | 70  |

| Table VI. Energy delivery efficiency of SCC and CBB with different load                  | 93  |

| Table VII. Energy consumed for switchings                                                | 94  |

| Table VIII. Energy delivery efficiency of SCC and CBB with different load                | 97  |

| Table IX. Energy consumed for switchings                                                 | 97  |

| Table X. Energy delivery efficiency of SCC and CBB with different load                   | 100 |

| Table XI. Energy consumed for switchings                                                 | 100 |

| Table XII. Miniature alkaline batteries from Energizer                                   | 129 |

### **List of Publications**

#### Journal

X. Zhang; D. Shang; F. Xia; A. Yakovlev; , "A Novel Power Delivery Method for Asynchronous Loads in Energy Harvesting Systems," Emerging Technologies in Computing Systems, ACM Journal on, JETC 7(4): 16 (2011).

#### Conference

Zhang, Xuefu; Shang, Delong; Xia, Fei; Low, Hock Soon; Yakovlev, Alex; , "A hybrid power delivery method for asynchronous loads in energy harvesting systems," New Circuits and Systems Conference (NEWCAS), 2012 IEEE 10th International, vol., no., pp.413-416, 17-20 June 2012.

Xuefu Zhang; Delong Shang; Fei Xia; Yakovlev, A.; , "A Novel Power Delivery Method for Asynchronous Loads in Energy Harvesting Systems," Asynchronous Circuits and Systems (ASYNC), 2011 17th IEEE International Symposium on, vol., no., pp.89-98, 27-29 April 2011.

### • Technical Report

Xuefu Zhang, Delong Shang, Fei Xia, Alex Yakovlev; , "A Novel Power Delivery Method for Asynchronous Loads in Energy Harvesting Systems," NCL-EECE-MSD-TR-2010-166, Microelectronic System Design Group, School of EECE, Newcastle University, December 2010.

X. Zhang; D. Shang; F. Xia; A. Yakovlev; , "Characteristic of Gated Diode Based DRAM under Low Voltage," NCL-EECE-MSD-TR-2010-157, Microelectronic System Design Group, School of EECE, Newcastle University, September 2010.

### Demonstration

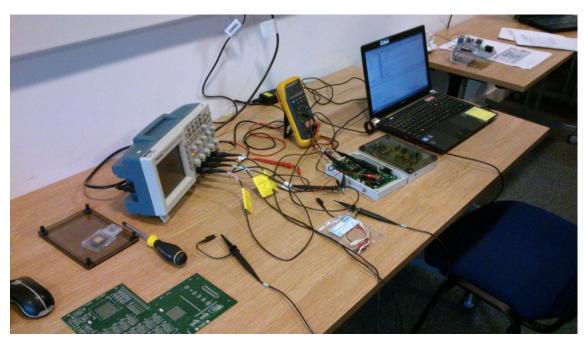

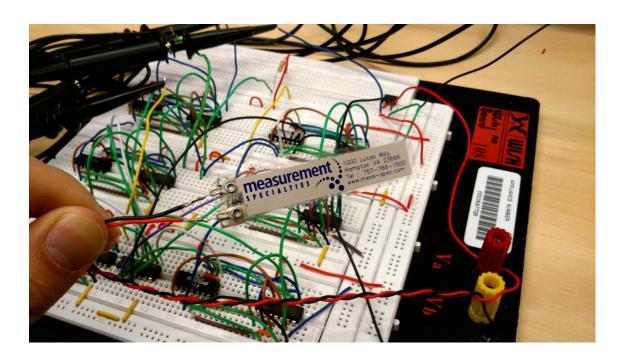

Southampton University, July, 2012: Portable, Switched Capacitor DC/DC Converter Based Variable Vdd Powered Asynchronous Self-Timed SRAM Demonstrator (System controlled by microcontrollers).

Newcastle University, November, 2011: Energy Proportional Computing Based Hybrid Power Delivery Method Hardware Implementation and Verification for Asynchronous Loads in Energy Harvesting Systems (System controlled by FPGAs).

Async 2013: Energy-modulated Computing: First Samples of Self-powered Life on a Die. Reza Ramezani, Maxim Rykunov, Abdullah Baz, Xuefu Zhang, Delong Shang, Andrey Mokhov, Danil Sokolov, Fei Xia and Alex Yakovlev.

### **Abstract**

For systems depending on *Energy Harvesting (EH)* methods, a fundamental contradiction in the power delivery chain has existed between conventional synchronous loads requiring a relatively stable Vdd and energy transducers unable to supply it. DC/DC conversion (e.g. *Switched Capacitor DC/DC Converter (SCC)*) has therefore been an integral part of such systems to resolve this contradiction. Asynchronous loads, in addition to their potential power-saving capabilities, can be made tolerant to a much wider range of Vdd variance. This may open up opportunities for much more energy efficient methods of power delivery.

This work firstly presents in-depth investigations into behaviour and performance of different power delivery mechanisms driving both asynchronous and synchronous loads directly from a harvester source bypassing bulky energy buffering devices for extremely compact EH systems. A novel power delivery method, which employs a *Capacitor Bank Block (CBB)* for adaptively storing the energy from a EH circuit depending on load and source conditions, is developed. Its advantages, especially when driving asynchronous loads, are demonstrated through comprehensive comparative analysis.

Based on the novel CBB power delivery method, an asynchronous controller is developed for a modified CBB, incorporating low-power threshold voltage sensing circuits to work with tasks. The successful asynchronous control design drives a case study that is meant to explore relations between power path and task path. Then a fundamental task and power scheduling method is developed.

To deal with different tasks with variable harvested power, systems may have a range of operation conditions and thus dynamically call for CBB or SCC type power delivery. Therefore, a new *Hybrid Capacitor Bank Blocks (HCBB)* using the same set of capacitors to form CBB or SCC is implemented with economic system size.

This work presents an unconventional way of designing a compact-size, quick-response, both task- and energy-aware EH system. In addition, asynchronous-logic circuit design and Energy-Modulated Computing method are employed to overcome large voltage variation in EH systems and implement smart power

management for harsh EH environment. The power delivery mechanisms (SCC, CBB, and HCBB) is not only investigated and verified by simulations, but also by hardware implementations that are currently employed to help asynchronous-logic-based chip testing and micro-scale EH system demonstrations.

# **Acknowledgements**

Firstly, I would like to thank my dear family, my parents, and my wife. On the path of my life, no success can be achieved without their encouragement, concern, love, and unselfish support with expecting nothing in return.

My supervisor, Prof. Alex Yakovlev – a friendly, kind, and wise leader of the *Microelectronics System Design (MSD)* group of Newcastle University, introduced me to the world of *Energy Harvesting (EH)* systems with amazing asynchronous logic methods and gave me invaluable guidance during my Ph. D research. His Energy-Modulated Computing concept threw a bright light on my research road of power delivery and drove me to explore beauties of EH-powered asynchronous-logic-based systems.

Dr. Delong Shang, a "circuit wizard", is an intelligent researcher in digital circuit design domains from large-scale (PCBs) to micro-scale (chips), from synchronous logic to asynchronous logic, and from microcontroller to FPGA. He is my friend and also my teacher. He broadened my vision in microelectronics and has given me hundreds and thousands ideas and suggestions within recent four years.

Dr. Fei Xia, Dr. Danil Sokolov and Dr. Andrey Mokhov gave me lots of valuable help in learning asynchronous logic, doing Petri-net and STG modelling, and using Workcraft and Petrify tools. Fei as an important co-author of my published papers also gave me lots of help in paper writing. Without him, it is hard to clearly and logically describe my research methods and present investigation results.

Alexander Kushnerov of Ben Gurion University is an expert in power delivery research field. I learned lots of knowledge of DC/DC conversions from him through exciting and interesting discussions.

Reza Ramezani, Abdullah Baz, and Hock Soon Low, my best friends, contributed lots to my researches on power delivery mechanisms. In addition, Abdullah and Hock Soon gave me lots of suggestions on the hardware implementation of the power delivery mechanisms. I am really grateful to their generous help.

Last but not least, I would like to thank all my colleagues from our MSD group. Especially many thanks to my dear Arabic friends, such as Sami Hasan, Ahmed Alahmadi, Nizar Saadi, and Ammar Mahmood, they taught me lots of Arabic cultures and languages. I very much enjoy my study in the MSD group and my stay in Newcastle in the past four years.

# **Acronyms**

**ADC** Analogue to Digital Converter

**AMS** Analogue Mixed Signal

**CB** Capacitor Bank

**CBB** Capacitor Bank Block

**CBSL** Capacitor Bank Voltage Sense Line

CC Charge Capacitor

**CEN** Capacitor Enable

ChFin Charge FinishChSen Change Sense

**ChSL** Charge Sense Line

**ChSLRes** Charge Sense Line Reset

**ChSwOn** Charge Switch On

**CN** Change Notice

**DFF** D-type flip-flop

**DsChComp** Discharge Complete

**DsChFin** Discharge Finish

**DsChSen** Discharge Sense

**DsChSL** Discharge Sense Line

**DsChSLRes** Discharge Sense Line Reset

**DsChSLSet** Discharge Sense Line Set

**DsChSwOn** Discharge Switch On

**DVFS** Dynamic Voltage and Frequency Scaling

**EDA** Electronic Design Automation

**EDLC** Electric Double-layer Capacitor

**EH** Energy Harvesting

**EMC** Electro-Magnetic Compatibility

**EOC** End of Conversion

**EPSRC** Engineering and Physical Sciences Research Council

**FPGA** Field Programmable Gate Array

FSL Fast-Switching Limit

FSM Finite State Machine

**HCBB** Hybrid Capacitor Bank Block

**Ipwlf** Independent Piece-Wise Linear current Source Based on File

ITRS International Technology Roadmap for Semiconductors

**Li-ion** Lithium-ion

MEMS Micro-Electro-Mechanical Systems

MIM Metal Insulator Metal

MPP Maximum Power Point

MSD Microelectronics System Design

**MUTEX** Mutual Exclusion element

**NextPro** Next Process

**MSB**

NiCd Nickel Cadmium

**NiMH** Nickel Metal Hybrid

**OTA** Operational Trans-conductance Amplifier

Most Significant Bit

PC Personal Computer

PCB Printed Circuit Board

PDU Power Delivery Unit

**PEDOT** Poly (3, 4 – ethylenedioxy - thiophene)

**POR** Power-on-Reset

**PP** Power Path

PVDF Polyvinylindene Fluoride

PWM Pulse Width Modulation

**RF** Radio Frequency

**RFID** Radio Frequency Identification

SCC Switched Capacitor DC/DC Converter

SenOutASensed Output ASenOutBSensed Output B

**SetChAv** Set Change Available

**SetDsChAv** Set Discharge Charge Available

**SOC** System-on-Chip

**SPI** Serial Peripheral Interface

**SRAM** Static Random Access Memory

SSL Slow-Switching Limit

**StaChPro** Start Charge Process

**StaDsChPro** Start Discharge Process

**STG** Signal Transition Graph

**TaskComp** Task Complete

**TG** Transmission Gate

**UGI** User Guider Interface

**VChSL** Voltage at Charge Sensing Line

**VCR** Voltage-Conversion Ratio

**VDsChSL** Voltage at Discharge Sensing Line

VL Voltage Level

**VRM** Voltage Regulator Module

## Chapter 1

## Introduction

In conventional energy-constrained electronic devices such as wireless sensors, the lifetime of the sensors is an important performance indicator, as the sensors are normally powered by fixed energy supplies (e.g. non-rechargeable batteries) leading to a limited operational life [1]. Additionally, practical deployment of the above systems is usually limited by the need to change batteries, and remoteness of location and low frequency of maintenance [2].

Recently, *Energy Harvesting (EH)* with growing popularity has become an appealing solution to prolong the lifetime of electronic devices. For instance, EH begins to be employed in large-scale, sensor-based *Wireless Sensor Networks (WSNs)* for structural health monitoring and human health monitoring [3]. Unlike non-rechargeable battery powered WSNs, EH WSNs potentially have an unlimited energy supply by harvesting environment energy from a variety of natural and man-made sources [4], such as solar, wind, heat, vibration, and *Radio Frequency (RF)* energy.

However, in EH systems, output voltage of EH transducers (e.g. piezoelectric energy transducers [5] [6]) typically depends on the designs of devices and conditions of the environment from which energy is harvested, and may be AC. It usually does not coincide with the correct Vdd level for load electronics. Therefore, DC/DC conversion units are normally needed to convert unstable Vdd from EH transducers to suitable Vdd levels for load electronics.

To meet requirements of EH system miniaturization, a *Micro-Electro Mechanical System (MEMS)* method has become a trend to design and manufacture micro-scale EH transducers to step over physical scaling barriers [7]. RF [8] and Piezoelectric [5] MEMS EH devices are the most popular choices. On the other hand, a *System-on-Chip (SoC)* method, which effectively shrinks system size, improves system performance, and reduces total energy consumption, has emerged as a promising solution for miniaturizing mixed-signal electronic devices, such as wireless network systems [9].

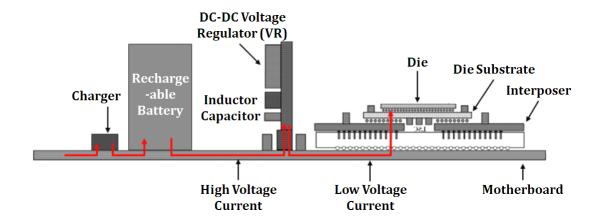

Thanks to research achievements in realms of MEMS and SoC, micro-scale EH systems have recently drawn a great deal of research attention [10] [11] [12] [13]. Following this trend, in order to further scale down the size of micro-scale EH systems, DC/DC conversion units, employed between MEMS EH transducers and load electronics (SoC), may be also constructed on the same chip where the load electronics is located, to meet the whole EH system miniaturization requirements. This is because off-chip DC/DC converting units normally employ bulky elements such as passive filtering devices – capacitors and inductors that may consume large board area. Additionally, employing an off-chip DC/DC conversion method leads to a mass of decoupling capacitors on power delivery paths, which may increase difficulty of power-path design and board area [14].

To replace off-chip DC/DC conversion units, the best existing solution is *Switched Capacitor DC/DC Converters* (SCC), which may have high conversion efficiency and can be fabricated on a chip [15]. Due to the constant improvement of on-chip capacitor fabrication technologies – achieving high Q and high energy density [16] [17], SCCs are predicted to be more and more popular for on-chip DC/DC conversion applications in the future.

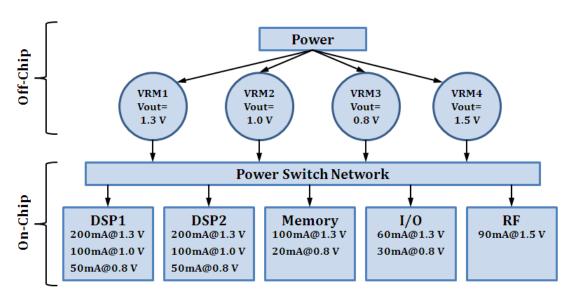

For load electronics with SoC methods, more and more workloads may be placed on the same die and the system may have ability to perform multiple task computations in parallel. However, the power demands of various workloads on the same die may be different and may change with time, depending on the task (e.g. priority, deadline, or both of them) that they may run.

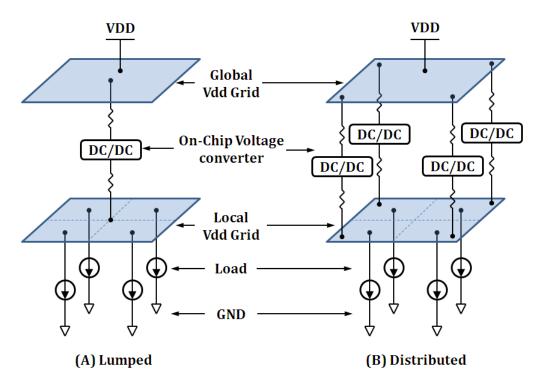

Therefore, fully integrating DC/DC conversion units distributed on-chip to implement *Dynamic Voltage Scaling (DVS)* for each power domain may improve load regulation and eliminate load-transient spikes caused by inductances from package and global power grid [18].

Moreover incorporating distributed on-chip DC/DC conversion units may decrease IR drop and achieve better power management compared to the lumped *Power Delivery Unit (PDU)* design (employing an on-chip large central DC/DC conversion unit) [19]. Besides, locating PDUs as close as possible to workloads may increase their power delivery efficiency as well.

### 1.1 Motivation

### • Possible to Bypass Energy Storage Devices

Generally in EH systems, harvested energy needs to be buffered in bulky off-chip energy storage devices (e.g. rechargeable batteries or supercapacitors), as the harvested energy is mainly influenced by EH targets – energy sources (e.g. solar and wind) that may be uncontrollable and hard to be accurately predicted. Therefore it is usually considered to be much challenging or even impractical to directly connect EH transducers to load electronics.

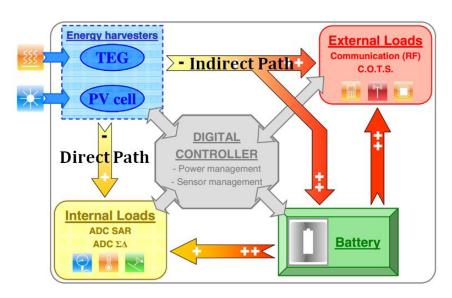

However, the EH power delivery method presented in [20] may provide an opportunity to directly power load electronics with EH transducers. In this work, an energy-autonomous wireless multi-source and multi-sensor node (called Managy) is introduced and its system diagram is shown in Figure 1. The Managy integrates on the same chip with a power harvesting and management platform, an internal sensor unit using ADC interfaces, a rechargeable battery layer deposited on the micro-system IC, and a global asynchronous digital controller.

In order to increase the overall efficiency, the Managy provides a direct power path from the energy harvesters to internal loads bypassing the rechargeable battery when obtained energy is enough to supply the loads. If not enough power has been scavenged, the indirect power path through the rechargeable battery will be used to supply the internal loads. On the other hand, employing direct power path also can save charge and discharge cycles of the rechargeable battery.

However, the indirect path presented in Figure 1 may be not energy efficient and it may suffer energy loss in energy delivery and storage processes, such as energy loss of battery charging and discharging, and electrochemical reactions inside the battery. In addition, such system also needs to consume extra energy for management of battery charge and discharge. Therefore, the output of the indirect path is always smaller than its input due to the energy loss and additional energy consumption.

Figure 1. Managy micro-system overview [20].

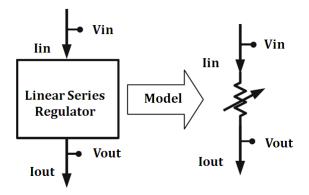

Although this work has thrown light on the method of employing direct path to connect EH transducers to load electronics bypassing energy storage devices, incorporating *Low Drop Out (LDO)* linear regulators for the direct path may be not a sophisticated choice. Compared to LDOs, on-chip switching DC/DC conversion units (e.g. SCC) may achieve obvious higher power delivery efficiency and more flexibility in *Dynamic Voltage Scaling (DVS)* [21]. However, the performance and problems of employing the switching DC/DC conversion units for such a direct

power path are still waiting to be investigated and crystallized. Besides, a corresponding task and power scheduling method aiming for such a direct power path have not been developed.

#### • Energy-Modulated Computing

Energy-aware computations and energy-efficient systems have become popular topics of research, especially in EH systems where energy supply is nondeterministic. EH and the reality that computation is becoming more energy-bounded are some of the inspirations for the concept of energy-modulated computing [22].

EH and other energy sources employed in energy-modulated computing systems can be fundamentally different from conventional power supply method. Energy-modulated computing treats both energy availability and data/task requirements as system design variables and design objectives can span the entire range between finding the optimal task scheduling to spend a given energy profile and finding the best energy supply scheduling to best fulfil a task requirement.

For instance, in these systems the available energy may be viewed as infinite, with newer energy always available during system lifetimes but instantaneous power often unpredictable and nondeterministic, depending on the environment [22]. This has motivated various techniques in trying to smooth the power flow, including temporarily buffering harvested energy in energy storage devices, such as off-chip rechargeable batteries and supercapacitors [23], which may have a number of disadvantages [24] (e.g. rechargeable batteries: damage caused by complete discharge, need of a great deal of "management", and poor compatibility between chargers and batteries; supercapacitors: low energy density, low voltage cells, and high self-discharge rate). On the other hand, directly delivering energy generated by harvesters to computational loads might be an alternative in some applications [25].

Energy-modulated computing aims to find better synergies between power supply and computational loads to achieve greater total energy efficiency. New ways of power supply and load design should both support more robust operation

of the load under variable Vdd and allow the load to "scavenge" more computation from the energy provided by the power supply.

For synchronous loads, relatively stable power supplies are needed with minimum (5% to 10%) voltage variation allowed [26]. DC/DC conversion units may pass on instability in the EH voltage when an off-chip intermediate storage is not used, potentially leading to the load needing to be switched off or into sleep mode. On the other hand, to increase power output stability under the variable power supply, switching-mode DC/DC conversion unit (e.g. SCC) designs usually employ the method of using controllable or self-adaptive frequency to implement the switching operations. For example, when the output power from the supply drops largely, this case may cause frequent switching operations inside the SCC accordingly [27].

However, although the existing DC/DC conversion unit (e.g. SCC) may have an ability to regulate power from a variable power supply, this ability may be very limited. Indeed, usually existing DC/DC conversion units are originally designed for regulating power from a stable power supply that may only have slight voltage variation (e.g. slight output voltage drop in a non-rechargeable battery with use time) to synchronous load electronics.

In EH systems, especially when bypassing energy storage devices and choosing the existing DC/DC conversion unit to directly regulate harvested power that may have large voltage variation or even have power-off gaps (for a very short time), the DC/DC conversion unit may not work efficiently and its performance and problems are still waiting to be explored and analyzed.

#### Asynchronous Circuits

Asynchronous circuits are fundamentally different from synchronous circuits. Although asynchronous circuits assume binary signals, there is no common and discrete time. The circuits incorporate handshaking between their components in order to perform the necessary synchronization, communication, and sequencing of operations.

Compared with synchronous circuit design, there are some challenges existing in asynchronous circuit design. It may suffer large area overhead (due to addition of completion detection and design-for-test circuits) and incompatibility with commercial EDA tools. Besides, it may be more difficult in circuit testing and debugging [28].

However, the advantages of the asynchronous circuit design are also obvious and cannot be ignored [28] [29]. Except lower power consumption [30], higher operating speed [31], less emission of electro-magnetic noise [32], better composability and modularity [33], and no global clock distribution & clock skew problems [28], the asynchronous circuits also have satisfactory robustness towards variations in supply voltage [34] [35], temperature, and fabrication process parameters [36].

Therefore, computational loads with asynchronous logic being capable of tolerating wide voltage variations may make them good candidates for use in conventional EH systems (having energy storage devices) where the DC/DC converters may deliver regulated power but with a degree of voltage variation. However, bypassing energy storage devices and directly employing asynchronous loads to cooperate with EH transducer and DC/DC converters (without energy storage devices) has not been investigated so far. Therefore, performance of the asynchronous loads running under such conditions is still unknown. Besides, problems arising from such a power delivery path have not been crystallized. Additionally, a new power delivery method, especially aiming for asynchronous loads in the EH systems (bypassing energy storage devices), is still waiting to be investigated and developed.

#### • Power Delivery Path for Concise Energy Harvesting Systems

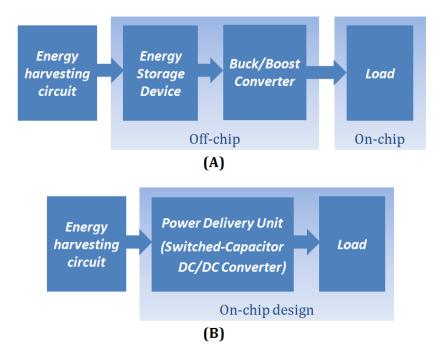

In EH systems, energy can be scavenged by harvesting circuits from ambient and supplied to loads through power delivery paths. Figure 2 (A) shows a normal power delivery path and (B) shows a new power delivery path for EH systems.

For (A), the power delivery path is normally implemented off-chip with very mature manufacturing techniques, employing a bulky energy storage device to store harvested energy and a buck/boost converter to deliver energy from the storage device to a load (integrated on-chip). In the path, before enabling the converter to deliver energy, the voltage at the storage device needs to be charged to a preset level [220] (e.g. charge supercapacitors to 2.5 V [100]). In addition, the buck/boost converter usually can adjust different Vdds at least in Microseconds [111]. The concept shown in (A) has been prevalently employed in lots of EH applications.

Compared with the normal power delivery path shown in (A), the new path shown in (B) is more compact. A *Power Delivery Unit (PDU)* (usually employing switched-capacitor DC/DC converter) and a load are both integrated on chip. The PDU is not used to store harvested energy, but to temporarily buffer the coming energy according to task requirements. Once energy is buffered much enough, it will be delivered to the load to finish the task. Since the PDU is integrated on-chip, it may be able to adjust different Vdds in Nanoseconds.

Figure 2. Normal (A) and new (B) power delivery paths for energy harvesting systems.

However, the concept introduced in (B) is stil waiting for further investigation. The performance of the new power delivery path is based on simulation results and approximate estimation. Additionally, from high-level, algorisms for power path control and power delivery management are waiting to be developed. On the

other hand, from low-level, specific circuit design and verification are also waiting to be implemented.

### 1.2 Contributions

Based on the problems and potentials discussed in above, this research concentrates on the power delivery mechanisms that deliver power directly from EH transducers via on-chip *Power Delivery Units (PDU)*, bypassing energy storage devices, to asynchronous computational loads in order to meet the more and more popular trend of micro-scale EH systems and implement intelligent task and power scheduling according to the novel energy modulated computing concept.

Firstly, the most popular on-chip fully integrated DC/DC conversion unit – SCC is investigated in-depth by means of a hardware implementation powering an asynchronous chip with a large output voltage range. In the investigation, the asynchronous chip shows satisfactory robustness against power supply (output of the SCC) voltage variations. It throws light on the possibility of powering asynchronous loads with controllable voltage ranges rather than stable voltage levels. Additionally, microcontrollers are employed in the SCC investigation. For microcontroller programming, different control and parameter sampling methods are studied to improve the SCC performance.

Secondly, a new power delivery method, based on an on-chip *Capacitor Bank Block (CBB)*, is proposed. It is aimed at providing a degree of programmability in the power delivery control so that power can be intelligently delivered under different EH source and load conditions for performance or efficiency goals. This method is comparatively investigated with a conventional SCC. The comprehensive analysis across the two different types of power delivery for synchronous and asynchronous loads represents the first attempt to systematically study the issue of on-chip power delivery directly from EH transducers to computational loads by passing bulky energy storage devices.

Thirdly, an asynchronous controller to support the CBB concept is designed. The asynchronous controller incorporating a modified CBB structure and improved low-power threshold voltage sensing circuits works with voltage-variation-robust

asynchronous loads, thereby allowing the whole system to get rid of global clocks and associated disadvantages. Employing asynchronous logic and threshold voltage sensing technique enables energy consumption of the whole PDU to stay at a satisfactory level. Additionally, the PDU is able to implement high quality power regulation powered by Vdd varying in a small range. A case study targeting at the interplay between power path and task path is performed based on the proposed PDU. A fundamental task and power scheduling method is developed. Incorporating the scheduling method, the EH system is able to finish tasks and achieve high efficient harvested energy use or low CBB PDU power consumption.

Fourthly, a new *Hybrid Power Delivery Method (HCBB)* is designed and is able to use the same set of capacitors to form both CBB and SCC configurations which can be switched in and out at run time, effectively realizing a kind of dynamic reconfiguration of power delivery to deal with different tasks with variable harvested power. The HCBB (sharing the same set of capacitors to form CBB or SCC) effectively decreases system size and control overheads, as on-chip capacitors for energy storage tending to be huge compared to logic. Additionally, the HCBB hardware implementation is realized. A HCBB controller is developed and verified by FPGA. The hardware is characterized with experiments using RC loads and then used as a power supply in our current variable VDD chip testing system.

The SCC, CBB, and more sophisticated HCBB concept are not only verified in simulation, but also verified by hardware implementation. The hardware implementation is used for on-chip DC/DC conversion and task and scheduling method investigation in this research. It is also employed as an asynchronous chip testing platform delivering power with required voltage profiles. Additionally, the achievements of this research in EH power delivery for asynchronous loads have been successfully demonstrated in Newcastle University Annual Research Conference, Holistic Energy Harvesting Advisory Board Meeting, and Energy Harvesting 2013 Forum.

### 1.3 Organization

The thesis is organised into eight Chapters and five Appendixes as follows:

- **Chapter 1 (Introduction)** motivates the necessity of developing an on-chip power delivery method for micro-EH systems to deliver harvested power directly to asynchronous loads bypassing bulky energy storage device. Contributions are also discussed in this chapter.

- **Chapter 2 (Background)** presents a detailed introduction regarding micro-scale EH systems including energy transducers, energy storage devices, and conventional power delivery method.

- **Chapter 3 (Baseline Research)** introduces the state-of-the-art on-chip power delivery methods for multi-core systems and compares with off-chip power delivery methods. Then on-chip DC/DC conversion units are reviewed, including linear regulators, buck converters and SCCs. Besides, on-chip voltage sensing technologies are introduced and discussed.

- **Chapter 4 (Switched Capacitor DC/DC Converter Investigation)** reports an investigation performed on SCC, including the SCC working principle, hardware implementation and verification with an RC load, and an asynchronous self-timed SRAM chip.

- Chapter 5 (A Novel Power Delivery Method) describes a novel on-chip power delivery method in a micro-scale EH system for directly powering asynchronous loads from an energy transducer bypassing traditional energy storage devices. Comparative studies have been performed by separately employing the proposed CBB and a traditional SCC as the PDU in such an EH system powering synchronous and asynchronous loads. The performance and behaviour of the PDUs and loads are compared and discussed.

- **Chapter 6 (Asynchronous Controller Design)** presents an asynchronous controller design cooperating with modified CBB and improved low-power threshold voltage sensing circuits in order to work with tasks. A case study has been performed to develop fundamental task and power scheduling method based on the proposed PDU.

- Chapter 7 (A Hybrid Power Delivery Method) introduces a design of a new HCBB using the same set of capacitors to behave like CBB or SCC for EH power delivery to implement task and power scheduling. The HCBB connection topology, control method, hardware implementation and verification are introduced. In addition, the HCBB performance and potential of implementing task and power scheduling are presented and discussed.

- **Chapter 8 (Conclusions and Future Work)** summarises the contributions of this thesis as presented in the previous chapters, and discusses areas of future work.

- **Appendix A (Photos & Pictures)** includes photos and pictures illustrating PDU hardware implementation and verification for demonstrations.

- **Appendix B (Program Flowcharts)** shows different programming methods expressed by program flowcharts for a microcontroller to implement different control for the SCC PDU.

- **Appendix C (EQN Files for CBB Asynchronous Controller Models)** lists EQN files used to implement an asynchronous controller to incorporate a modified CBB structure and threshold voltage sensing circuit to work with tasks.

- **Appendix D (Recently Published SCC Results)** reports specifications of recently published SCC work in a table.

- **Appendix E (Discharge Ranges of CBs with Different Capacitance Value)** includes investigated data of a case study for developing a task and power scheduling method based on the proposed CBB concept.

## Chapter 2

# **Background**

This chapter provides a fundamental introduction to the problem of incorporating *Energy Harvesting (EH)* methods in powering micro-scale electronic systems, in the first section. In the second section, various ambient energy sources and transducers are introduced. Details of micro-scale piezoelectric energy transducers used as examples are reviewed in the same section. Energy storage devices, popular and widely used in micro-scale EH systems, are introduced in the third section. In the last section, conventional power delivery methods for micro-scale EH systems are discussed.

# 2.1 Energy Harvesting Methods for Micro-Scale Electronic Systems

In recent years, micro-scale electronic systems have evolved significantly due to on-chip circuit research advancing forward in the direction of high frequency, high integration density and low power. However, due to the trend of further shrinking and minimizing system size, the lifetime of battery-powered systems may meet a fundamental limitation due to slower development of battery technology, limited

energy storage space and high cost of replacement [1]. Therefore, the EH technology, based on scavenging energy from the environment without generating any hazardous substances, has been explored to provide renewable energy for micro-scale electronic systems.

To meet the requirements of system miniaturisation, EH methods to power up a rechargeable battery or supercapacitor-powered micro-scale electronic devices such as mobile devices and wireless sensor nodes have attracted immense research interests [37] [38] [39]. The amount of power required for those applications may reach a few hundreds of milliwatts. Some wireless sensor nodes have been successfully powered by energy scavenged from ambient sources such as solar, heat, and vibrations, for example EH powered sensor nodes (Heliomote [40], Hydro Watch [41], Everlast [42], SolarBiscuit [43], Sunflower [44], Prometheus [45] and AmbiMax [46]).

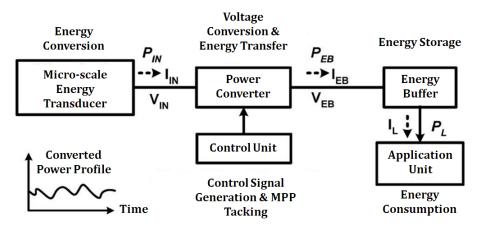

A general block diagram of a micro-scale EH system is shown in Figure 3 [47]. It contains five main blocks: micro-scale energy transducer, power converter, control unit, energy buffer, and application unit.

Figure 3. Block diagram of a micro-scale energy harvesting system [47].

With the help of the micro-scale energy transducer, it is possible to convert ambient energy to electrical energy. However, due to the change of environment, the converted power may not be stable and may vary in a large range with time. The converted power profile is shown in Figure 3. Besides, the micro-scale energy transducer block may be based on a single energy conversion mechanism [48] [49] or a hybrid mechanism [50] [51]. For example, a temperature sensor embedded in

a car may have both solar and vibration energy harvesters. When sunlight is not enough, vibration energy harvester is able to power the sensor when engine is running. On the other hand, when engine stops, the solar energy harvester may be able to supply required power for the sensor. However, although the hybrid mechanism for EH systems may obviously increase reliability and flexibility, increase of cost and system volume may not be ignored.

The power converter is used to draw maximum power from the energy transducer and deliver the conditioned power to the energy storage or directly to the application unit with minimum power loss. To achieve highly efficient power transfer and delivery, the control unit is employed to ensure *Maximum Power Point (MPP)* operation at all the times by running a tracking scheme, such as incorporating MPP tracking for electromagnetic energy transducers [52] and piezoelectric energy transducers [53]. Additionally, the control unit may have ability to tune the energy transducer as well. For example, tuneable piezoelectric EH system designs have been reported in [54] [55].

Usually, harvested energy will be buffered in energy storage devices such as supercapacitors or rechargeable batteries before delivered to the application unit. As output power of energy transducers may be unstable and change with time, most of electronic devices with synchronous logic may be unsuitable to work with such a variable power supply. It is normally considered to be very challenging or even impractical to directly use an energy transducer to power an application unit that is designed with synchronous logic.

## 2.2 Energy Transducers

The classification of EH can be organized on the basis of the form of energy. The various sources for EH are photovoltaic cells, wind turbines, thermoelectric generator and mechanical vibration devices, *Radio Frequency (RF)* electromagnetic antenna and so on [56] [57]

Table I shows some of the harvesting methods with their characterization [58]. For the listed harvesting methods, they can be categorized into two groups: 1)

109 μW [63]

ambient energy source such as solar, wind, vibration and RF energy, and 2) human power harvested from body movements.

For the ambient energy source, most of them may be uncontrollable but predictable such as solar and wind energy. They can only be harvested whenever available. If the energy source is predictable then a prediction model that forecasts its availability can be used to indicate the time of the next recharge cycle. For the human power, some of them may be fully controllable such as finger motion and foot falls. In this case, energy may be harvested whenever required without any prediction on the energy source.

**Amount of** Amount of Conversion **Harvesting Energy Source Energy** Energy **Technology Efficiency** Available Harvested Solar [40] Solar Cells 100 mW/cm<sup>2</sup> 15 %  $15 \text{ mW/cm}^2$ 1200 mWh/day -Wind [45] Anemometer Finger Motion [59] Piezoelectric 19 mW 11 % 2.1 mW Footfalls [60] 67 W 7.5 % 5 W Piezoelectric Vibration in Indoor Electromagnetic  $0.2 \text{ mW/cm}^2$ **Environments** [61] Induction 0.4 W Exhalation [59] **Breath Masks** 1 W 40 % Breathing [59] 0.42 W Ratchet-Flywheel 0.83 W 50 % **Blood Pressure [59]** 40 % Micro-Generator 0.93 W 0.37 W 60 µW [62] and **Electromagnetic wave** RF Antenna

Table I. Listing and characterization of energy sources [58].

#### 2.2.1 Piezoelectric Energy Harvesting

Mechanical EH may be the most promising of several EH techniques – mechanical, thermal, light, electromagnetic, human body and so on [64]. The Mechanical EH uses piezoelectric components that are deformed by different means. The deformations are directly converted to an electrical charge via a direct piezoelectric effect. This electrical charge can be subsequently regulated and stored before using by the electronic devices where the replacement of batteries is impractical, such as the wireless micro sensor networks, implantable medical electronics, and tire pressure sensor system [65].

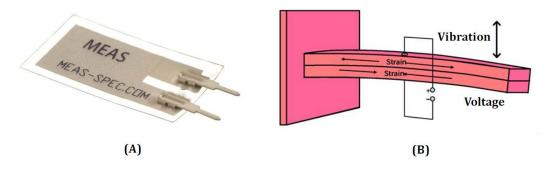

Figure 4 (A) shows a commercial piezoelectric film transducer. And an example of harvesting electrical energy from deformation of a piezoelectric energy transducer caused by vibrations is shown in (B).

The electrical energy at the output of the transducer is a strong and irregular function of time; hence, an AC-DC rectifier is needed to produce a DC supply source for the EH system. There are two types of conventional rectifiers: full bridge rectifier and voltage doubler. The limitations of the conventional piezoelectric EH architectures and replacements with higher power extraction efficiency are reported in [67] [68].

Figure 4. (A) Commercial piezoelectric film transducer [66] and (B) an example of using a piezoelectric energy transducer [67].

#### • Piezoelectric Energy Harvesting Circuit Model

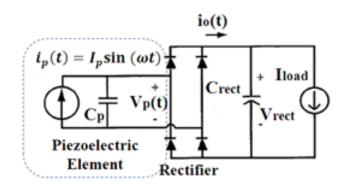

A simple model of a piezoelectric EH circuit [69] is shown in Figure 5. This model consists of a sinusoidal AC source and a four-diode rectifier (full bridge rectifier). Here ip(t) is the AC generated from the piezoelectric element, io(t) is the variable DC with an obvious power-off gap flowing through the load.

Figure 5. Piezoelectric energy harvesting circuit model.

#### • Working in Wide Range of Frequency

For the traditional piezoelectric energy transducers, the most common and widely employed piezoelectric material is Lead Zirconate titanate [70] [71]. It is usually brittle, thereby causing limitations in the applied strain. Additionally, when it is subjected to high-frequency motions, this material is susceptible to fatigue crack and can be easily damaged [72] [73].

To step over the limitation of the traditional piezoelectric energy transducers and improve their efficiency and flexibility, more flexible piezoelectric material such as *Polyvinylindene Fluoride (PVDF)* is developed and investigated in applications [74] [75]. Thanks to new piezoelectric materials, the piezoelectric energy transducer is able to work with vibration sources in a range from a few tens of Hz to tens of kHz [64] [76] [77] [78].

Furthermore, a PVDF film coated with *Poly (3, 4 - ethylenedioxy - thiophene)* (*PEDOT*) and *Poly (4 - styrenesulfonate)* (*PSS*) electrodes was investigated in [73] [79]. The results showed that the PEDOT/PSS film is able to work with a 1 MHz vibration source without damage to the film and electrodes. Consequently, the electrodes have an important influence on the behaviour of the piezoelectric material. The results also showed that a piezoelectric energy transducer can operate over a wide range of frequencies.

Besides, piezoelectric energy transducers have been widely employed to harvest energy not only from normal ambient vibrations and but also from aeroelastic vibrations [80]. Based on *Micro-Electro-Mechanical Systems (MEMS)* technologies, piezoelectric membranes [81] are employed for micro-scale EH transducers that can be fully integrated on ICs without traditional electrode connections thereby are able to work in a high frequency (up to MHz) [82].

Cranfield University, UK has reported a piezoelectric micro ultrasound transducer design working in MHz range is able to be used for EH applications [83]. The transducers was presented in Energy Harvesting 2013 [84] shown in Appendix A, Figure 85. Additionally, TIMA laboratory located at Grenoble, France [85] reports a fabrication of PZT/Si piezoelectric micro-machined ultrasonic

transducers first designed for ultrasonic imaging applications [86] that can be used as a mechanical to electrical energy transformer for EH. This design is able to convert acoustic energy in a large frequency range (a few tens of kHz to several tens of MHz) to electrical energy.

### 2.3 Energy Storages

For energy storage, there are mainly three types: non-rechargeable battery, rechargeable battery, and supercapacitor. This section comparatively introduces and discusses advantages and disadvantages of these energy storage devices.

#### 2.3.1 Non-rechargeable Vs Rechargeable Batteries

For modern commercial batteries, there are two main kinds of batteries, primary batteries (non-rechargeable, such as alkaline and lithium) [87] and secondary batteries (rechargeable, such as *Nickel Cadmium (NiCd)*, *Nickel Metal Hybrid (NiMH)*, and *Lithium-ion (Li-ion)*) [88].

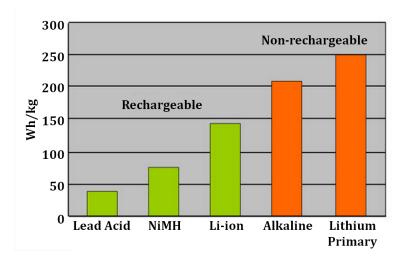

$Figure\ 6.\ Specific\ energy\ comparison\ of\ secondary\ and\ primary\ batteries\ [87].$

The primary battery is designed to be used once and discarded, and not recharged with electricity and reused. The electrochemical reaction occurring in the primary battery is not reversible. When the battery is in use, the electrochemical reaction uses the chemicals that generate the power. When the chemicals are exhausted, the battery stops producing electricity and the battery is useless and only recycled. For secondary battery, the electrochemical reaction can

be reversed by running a current into the battery with a battery charger to recharge it, regenerating the chemical reactants [89].

Compared with secondary batteries, the primary batteries usually have higher energy densities [90]. Although secondary batteries have been improved, a regular household alkaline provides 50 percent more energy than lithium-ion. Figure 6 compares the typical gravimetric energy densities of lead acid, NiMH, Li-ion, alkaline and lithium batteries. Additionally, the primary batteries also have lower self-discharge rate (alkaline 2-3 %per year, lithium 10% in five years) [91], much longer shelf life (alkaline 7-10 years and lithium 10-15 years) [92], and lower initial cost [93].

For primary batteries, compared with alkaline batteries, the lithium batteries are good at powering high drain devices [94]. On the other hand, alkaline batteries usually have a lower self-discharge rate in room temperature. In addition, powering low drain devices helps to maximize the longevity of the alkaline batteries.

#### 2.3.2 Supercapacitors Vs Rechargeable Batteries

Supercapacitors (also known as ultracapacitors or *Electric Double-layer Capacitors (EDLCs)*) utilize high surface area electrode materials and thin electrolytic dielectrics to achieve capacitances several orders of magnitude larger than conventional capacitors [95] [96]. They are widely employed to: 1) store harvested energy for many electronic devices such as wireless sensor nodes [4] [97], 2) work as low-maintenance memory backup to bridge short power interruptions [98], 3) deliver high current to drive hybrid vehicles [99], and so on.

Table II shows the performance comparison between supercapacitor and Li-ion rechargeable battery [100]. The supercapacitor has merit for applications where charging or discharging with high current rates is needed for only a few seconds [101]. Additionally, the supercapacitor has extremely long life cycles (without any memory effect compare with the rechargeable battery) and long service life as well. It also has excellent low-temperature charge and discharge performance.

However, the supercapacitor has poor volumetric and gravimetric energy density compared with the rechargeable battery. It suffers higher self-discharge than most batteries. It also has high cost per watt.

The supercapacitor is able to be charged to 2.3 to 2.75 V and can withstand higher volts. However, voltage higher than 2.8 V will reduce the service life of the supercapacitor. To achieve higher voltages, several supercapacitors can be connected in series but the series connection decreases the total capacitance.

Table II. Performance comparison between supercapacitor and Li-ion [100].

| Function                  | Supercapacitor        | Lithium-ion (general)          |

|---------------------------|-----------------------|--------------------------------|

| Charge time               | 1 - 10 seconds        | 10 - 60 minutes                |

| Cycle life                | 1 million or 30,000 h | 500 h and higher               |

| Cell voltage              | 2.3 to 2.75 V         | 3.6 to 3.7 V                   |

| Specific energy (Wh/kg)   | 5 (typical)           | 100 - 200                      |

| Specific power (W/kg)     | Up to 10,000          | 1,000 to 3,000                 |

| Cost per Wh               | \$20 (typical)        | \$0.50 - \$1.00 (large system) |

| Service life (in vehicle) | 10 to 15 years        | 5 to 10 years                  |

| Charge temperature        | -40 to 65 °C          | 0 to 45 °C                     |

| Discharge temperature     | -40 to 65 °C          | -20 to 60 °C                   |

The discharge curve may be a disadvantage to supercapacitors. For electrochemical batteries, they deliver a steady voltage in the usable power band. However, in the discharge process, the voltage of the supercapacitor decreases following an exponential curve from full to zero voltage. This curve starts at the initial voltage of the capacitor and diminishes quickly at first. Then, the slope becomes less and less while the voltage approaches zero [102]. This may reduce the usable power spectrum and much of the stored energy may be left behind, as the voltage level at the supercapacitor may be lower than the cut-off voltage level of loads.

# 2.4 Conventional Power Delivery Method for Micro-Scale Energy Harvesting Systems

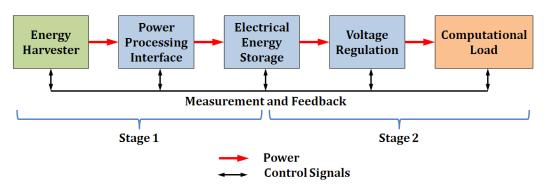

A typical micro-scale EH system is shown in Figure 7 [103]. The whole power delivery process is comprised of two stages. Stage 1 (energy accumulation) is from the energy harvester to the electrical energy storage and Stage 2 (energy use) is from the electrical energy storage to the computational load. For each block, voltage and current parameters will be measured and feedbacks will be employed as control references for the whole system.

Figure 7. Typical micro-scale EH system [103].

In the system, an EH unit is incorporated to convert ambient energy to electrical energy. A power processing interface is employed to condition the harvested electrical energy for attaining an appropriate DC voltage to charge an electrical energy storage unit and tune the EH unit in order to draw maximum input power [104]. The electrical energy storage unit is used to buffer the harvested energy, as the ambient energy source may be uncontrollable and unpredictable. When the energy is needed by a computational load, a voltage regulation unit will be enabled to deliver power with a proper voltage level to the computational load.

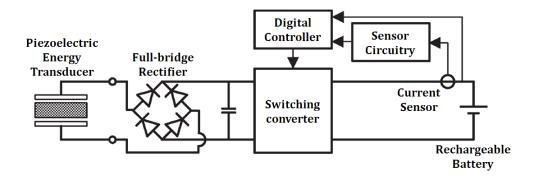

#### 2.4.1 Power Delivery Method for Stage 1

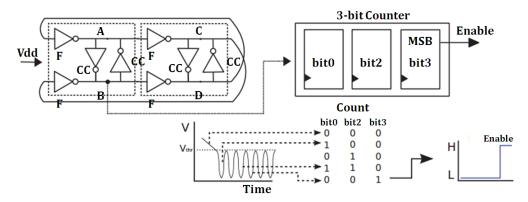

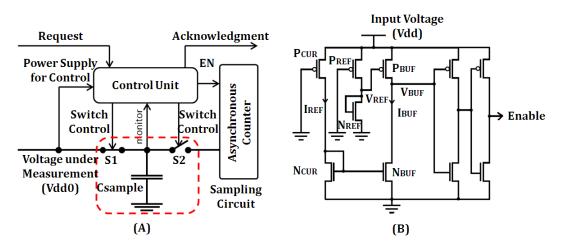

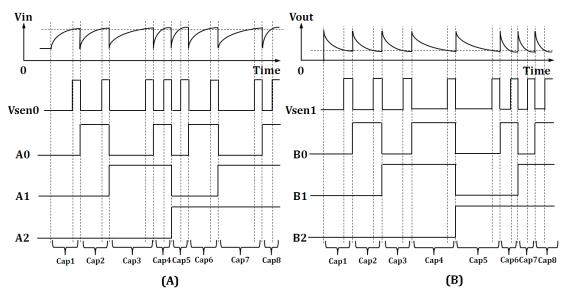

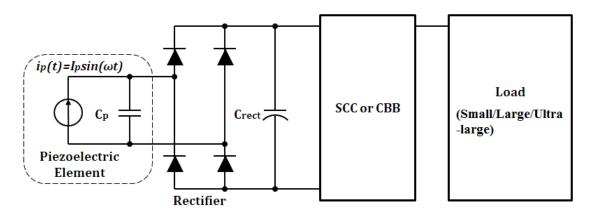

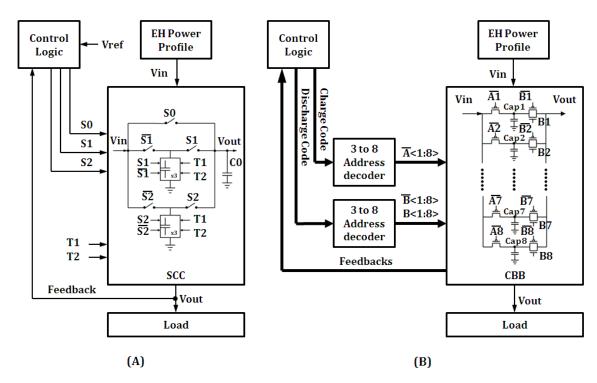

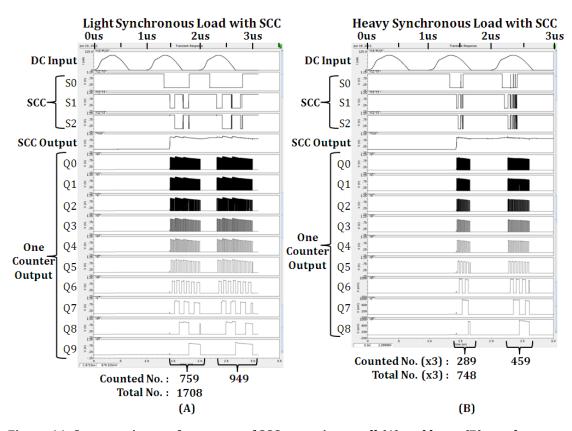

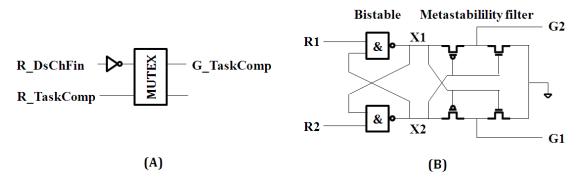

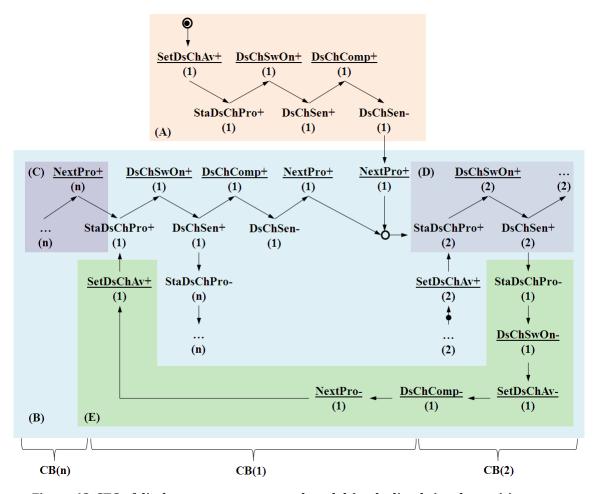

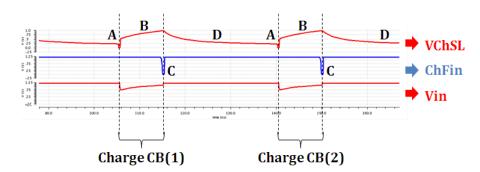

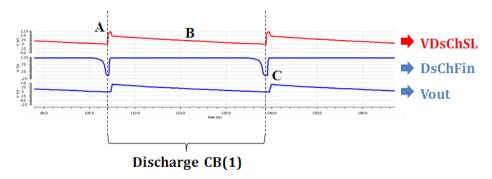

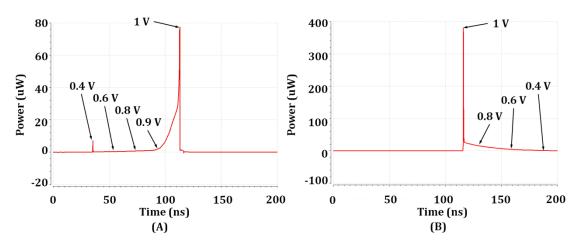

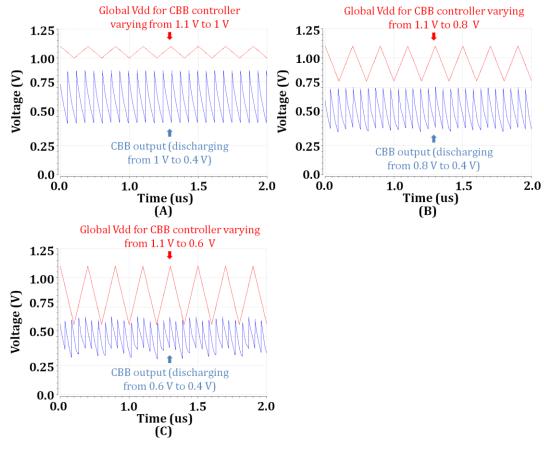

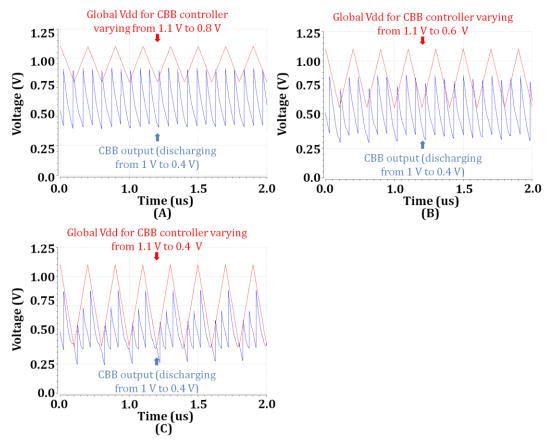

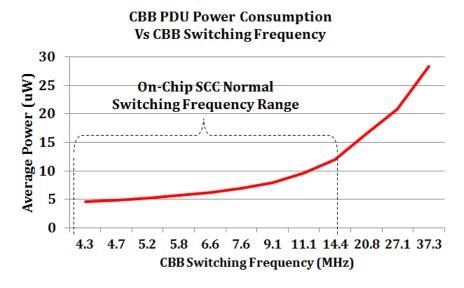

In Figure 8 [105], a traditional power delivery method for Stage 1 is presented. A piezoelectric energy transducer is employed. The harvested energy with AC characteristic will be rectified by a full-bridge rectifier. A capacitor located at the output of the rectifier is used to smooth the output voltage ripples varying in a large range. A switching converter is incorporated to regulate the harvested