| Voltage Equalis   | ation Techni     | gues for High  | Capacitance  | <b>Device Modules</b> |

|-------------------|------------------|----------------|--------------|-----------------------|

| , ortage Equation | CCIOII I COIIIII | ques ror ringi | Capacitanico |                       |

Simon Lambert

A thesis submitted for the degree of Doctor of Philosophy

School of Electrical and Electronic Engineering

Newcastle University

#### **Abstract**

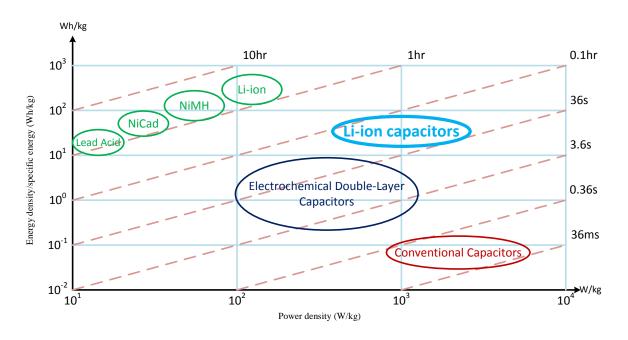

Traditionally, the electrochemical battery has been the prime medium by which electrical energy is stored for future use. Increasingly, the demands of modern systems such as electric vehicles, renewable energy, distributed generation, smart grid and others has stretched the development of new chemistries, materials and assembly techniques for electrochemical batteries. Additionally, some load profiles in these applications demand extremely high dynamic behaviour which is either undeliverable by conventional electrochemical batteries or is undesirably damaging to these technologies. As such, a family of electrochemical storage, known generally as supercapacitors or ultracapacitors, have been developed and implemented for such applications. In recent years advancements in electrochemical technology has led to hybridisation of high capacitance devices. Lithium-ion capacitors that are used in this work are, with their higher cell voltage and modern packaging, expected to be among the next emerging families of state-of-the-art electrical energy storage devices.

The relatively low cell voltage of high capacitance cells requires them to be connected in series to attain a system level voltage. During charging and discharging, manufacturing tolerances between the cells results in voltage mismatch across the stack. Mismatched voltages are an inefficient use of the energy storage medium and can lead to dangerous failures in the cells. Several techniques exist to limit the variance in cell voltages of supercapacitors across a series connected stack. These range from simple systems which discharge the cells at higher voltages through resistors to more complex active converter systems which equalise the cell voltages through charge redistribution via a power electronic converter. Whilst the simpler schemes are effective they are very inefficient and as such are not suitable for use in many applications.

A number of active converter voltage equalisation schemes have been proposed in literature, however, each of these equalisation schemes exhibit flaws which either makes them less desirable or less effective for a broad range of applications. Therefore, a new equalisation converter topology is proposed which is designed for greater equalisation effectiveness, modularity and size. The proposed equalisation converter differs from previously published equalisation schemes by allowing energy transfer between any pair of cells without the cumbersome multi-winding transformers employed in existing equalisation converters. The new equalisation scheme uses a bi-directional arrangement of MOSFET switches for galvanostatic isolation allowing the converter to be multiplexed to the stack. This arrangement allows the total size of the equalisation scheme to be reduced whilst maintaining performance.

# **Acknowledgements**

Working towards this point over the past four years has been an incredible experience for me; I've learned more than I'll ever remember and experienced more than I ever thought I would and there are a few people without whom I would never have made it here.

Firstly, my sincere gratitude to Volker for the opportunity to undertake this research in the first place. I'm also very grateful for his guidance and support and the advice about this work and more; I've been looked after. I have received excellent support in general from all of the academics in PEDM but particular thanks must go to Barrie and Matthew who have been especially supportive and happy to offer counsel. I look forward to remaining a colleague.

This work has only been possible because of the funding of EPSRC on the FRENS project. I would like to thank EPSRC and all the partners in the FRENS consortium for the chance to work in such a fascinating and diverse partnership. I would also like to acknowledge the assistance of The Centre for Process Innovation, Middlesbrough for their assistance with measurement and modelling of the cells and the late John Holden of HILTech for sourcing sample cells.

My time living in China was... an experience! But it's an experience I wouldn't change if I could. I owe a great debt of gratitude to Prof He and his team for their hospitality and friendship which made the time I spent in China a period which I remember fondly. Wuhua Li and the students in lab 211 became excellent friends and I hope I will have the opportunity to work with them in the future.

A lot of work in the department would not be possible without the technical and administrative support staff and I have benefited particularly from the technical support of the mechanical workshop team. Ian, Ian and Dave have been indispensable for all of my IT needs and are also great friends.

I had the good fortune to undertake my research in the UG lab at the same time as some great people some of who were invaluable in their support, advice and company. Special thanks must go to John for his technical support and guidance on a range of how-tos. Particular thanks to Daniel, Andy and Dave for their friendship and encouragement and for making the workplace a fun place be in.

Undertaking a PhD is a lot of hard work for the researcher but it is also a lot of hard work for their family. The hard work and sacrifices of my parents made it possible for me to go to university, for this and their belief in me, I am eternally grateful.

My most profound gratitude is to my wife, Jennifer, who has suffered a building site for a home during the first year of our marriage and has been the greatest source of encouragement. She has helped me more than she will ever know.

# **Table of contents**

| A] | BSTRAG  | CT                                                                   | 1   |

|----|---------|----------------------------------------------------------------------|-----|

| A  | CKNOW   | /LEDGEMENTS                                                          | II  |

| TA | ABLE O  | F CONTENTS                                                           | III |

| LI | ST OF I | FIGURES                                                              | VI  |

| LI | ST OF   | ΓABLES                                                               | X   |

| N  | OMENC   | LATURE                                                               | XI  |

| ΡŪ | JBLICA  | TIONS BY THE AUTHOR                                                  | XIV |

| 1  | INTI    | RODUCTION                                                            | 1   |

|    | 1.1     | OBJECTIVES AND CONTRIBUTION                                          | 1   |

|    | 1.2     | THESIS OVERVIEW                                                      | 2   |

|    | 1.3     | INTRODUCTION TO CAPACITANCE, DOUBLE LAYER EFFECTS AND ADVANCES IN LI | _   |

|    | ION TEC | HNOLOGY                                                              |     |

|    | 1.3.1   |                                                                      |     |

|    | 1.3.2   |                                                                      |     |

|    | 1.4     | APPLICATIONS OF HIGH CAPACITANCE DEVICES                             |     |

|    | •       | Transport                                                            | 7   |

|    | •       | Renewable generation                                                 |     |

|    | •       | Micro-grid                                                           |     |

|    | •       | Distribution                                                         |     |

|    | •       | Other applications                                                   |     |

|    | 1.5     | MULTIPLE CELL ASSEMBLIES                                             |     |

|    | 1.6     | VOLTAGE EQUALISATION – DEFINITION OF TECHNIQUES                      |     |

|    | 1.7     | POWER ELECTRONIC CONVERTERS FOR SUPERCAPACITOR APPLICATIONS          |     |

|    | 1.8     | DESIGN CONSIDERATIONS FOR ACTIVE ELECTRONIC SYSTEMS IN FLOATING      |     |

|    |         | NCE APPLICATIONS                                                     | 11  |

|    | 1.9     | MODELLING SINGLE CELLS                                               |     |

| 2  | CEL     | L MEASUREMENT AND MODELLING                                          | 13  |

|    | 2.1     | DESCRIPTIONS OF SAMPLE CELLS                                         | 13  |

|    | 2.1.1   | Maxwell PC2500, 2700F ultracapacitor                                 | 13  |

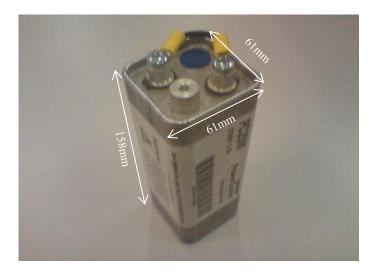

|    | 2.1.2   | JS Micro 2200F Lithium-ion capacitor                                 | 15  |

|    | 2.2     | INTRODUCTION TO MODELLING ELECTRICAL ENERGY STORAGE                  |     |

|    | 2.3     | REVIEW OF MODELLING TECHNIQUES                                       | 19  |

|    | 2.3.1   | Representation of double layer capacitance effect                    | 19  |

|    | 2.3.2   | Modelling cells as an energy storage component                       | 22  |

|    | 2 3 3   | Modelling cells as a complex impedance                               | 27  |

| SIMULATI                                                                                                             | ON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 35                                     |

|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

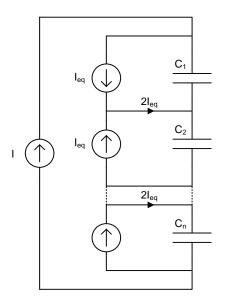

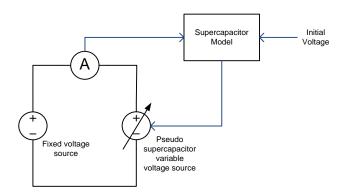

| 2.5 E                                                                                                                | DEVELOPMENT OF A MODELLING TECHNIQUE FOR DIRECT COMPARISON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 37                                     |

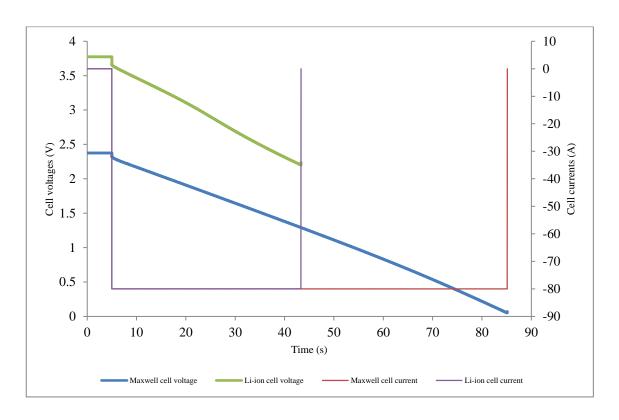

| 2.5.1                                                                                                                | Constant current charging response of sample cells                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 37                                     |

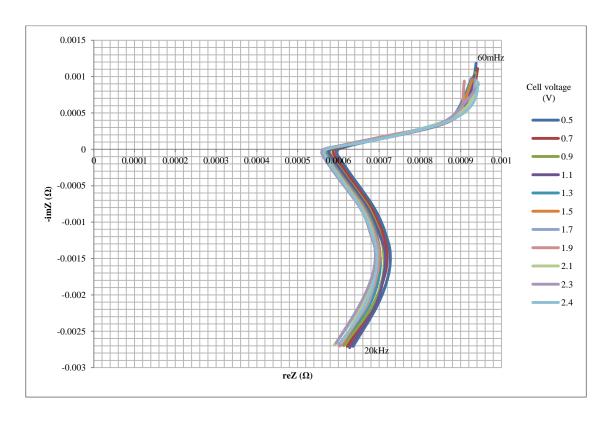

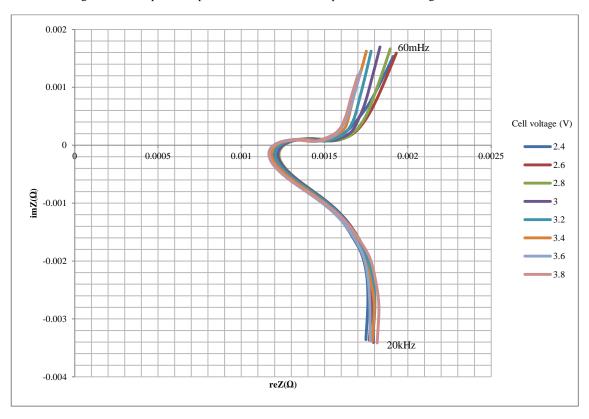

| 2.5.2                                                                                                                | Electrochemical impedance spectroscopy measurement of sample cells                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 38                                     |

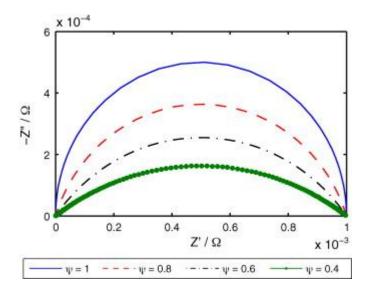

| 2.5.3                                                                                                                | Model development from measured impedance response                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 41                                     |

| 2.6 S                                                                                                                | SUMMARY – CELL MEASUREMENT AND MODELLING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 46                                     |

| 3 ASSES                                                                                                              | SSMENT OF EQUALISATION SCHEMES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 47                                     |

| 3.1                                                                                                                  | OVERVIEW OF ACTIVE EQUALISATION FAMILIES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 47                                     |

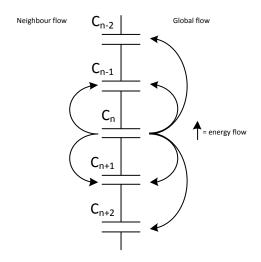

| 3.1.1                                                                                                                | Energy Flow Paths                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 48                                     |

| 3.1.2                                                                                                                | Constituent Component Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 50                                     |

| 3.1.3                                                                                                                | Transformers with distributed primaries/secondaries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 51                                     |

| 3.2 D                                                                                                                | DESCRIPTION AND ASSESSMENT OF EXISTING SCHEMES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 55                                     |

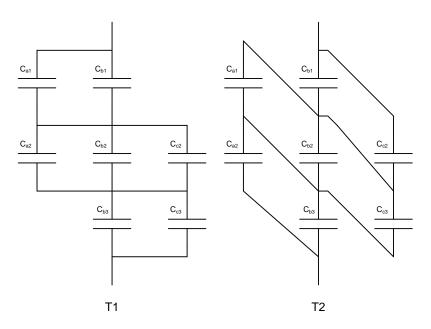

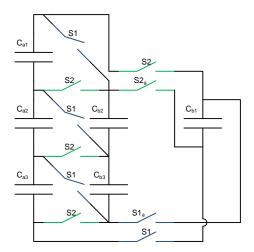

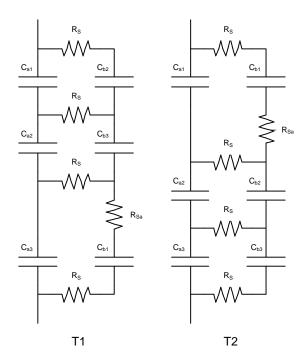

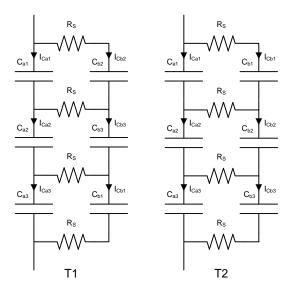

| 3.2.1                                                                                                                | Series-parallel connection equalisation scheme [72] (Figure 3-8)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 55                                     |

| 3.2.2                                                                                                                | Flying capacitor equalisation scheme [47] (Figure 3-19)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 62                                     |

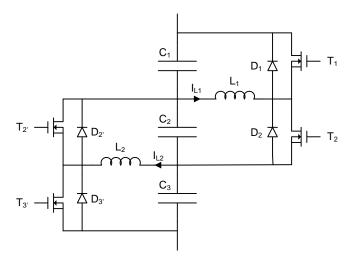

| 3.2.3                                                                                                                | Bi-directional buck-boost DC-DC converter equalisation scheme [48]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                        |

| (Figur                                                                                                               | e 3-3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 67                                     |

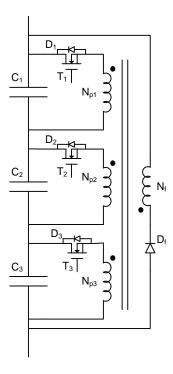

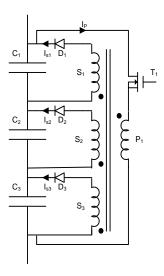

| 3.2.4                                                                                                                | Centralised flyback DC/DC converter with distributed secondary [48]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                        |

| (Figur                                                                                                               | e 3-5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 75                                     |

|                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0.2                                    |

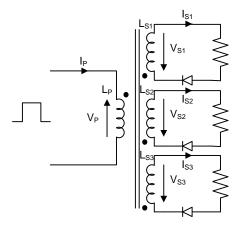

| 3.2.5                                                                                                                | Forward DC/DC Converter with Distributed Primary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 83                                     |

|                                                                                                                      | Forward DC/DC Converter with Distributed Primary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                        |

| 3.3 S                                                                                                                | SUMMARY OF EXISTING EQUALISATION SCHEMES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                        |

| 3.3 S<br>4 DEVE                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 88                                     |

| 3.3 S<br>4 DEVE<br>PRINCIPAI                                                                                         | LOPMENT OF AN EQUALISATION SCHEME FROM POWER FLOW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 88                                     |

| 3.3 S 4 DEVE PRINCIPAL 4.1 M                                                                                         | LOPMENT OF AN EQUALISATION SCHEME FROM POWER FLOW  S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 98<br>92                               |

| 3.3 S 4 DEVE PRINCIPAL 4.1 M 4.2 A                                                                                   | LOPMENT OF AN EQUALISATION SCHEME FROM POWER FLOW  S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 92<br>92<br>93                         |

| 3.3 S 4 DEVE PRINCIPAL 4.1 M 4.2 A 4.3 P                                                                             | LOPMENT OF AN EQUALISATION SCHEME FROM POWER FLOW  LS  MOTIVATION  ANALYSIS OF THE REQUIRED POWER FLOW FOR EQUALISATION  PROPOSED CONVERTER TOPOLOGY AND OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 92<br>92<br>93                         |

| 3.3 S 4 DEVE PRINCIPAL 4.1 M 4.2 A 4.3 P 4.3.1                                                                       | LOPMENT OF AN EQUALISATION SCHEME FROM POWER FLOW  LS  MOTIVATION  ANALYSIS OF THE REQUIRED POWER FLOW FOR EQUALISATION  PROPOSED CONVERTER TOPOLOGY AND OPERATION  Stack-converter interaction                                                                                                                                                                                                                                                                                                                                                                                                                           | 92<br>92<br>93<br>95                   |

| 3.3 S 4 DEVE PRINCIPAL 4.1 M 4.2 A 4.3 P 4.3.1 4.3.2                                                                 | LOPMENT OF AN EQUALISATION SCHEME FROM POWER FLOW  S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 92 92 93 95 95                         |

| 3.3 S 4 DEVE PRINCIPAL 4.1 M 4.2 A 4.3 P 4.3.1 4.3.2 4.3.3                                                           | LOPMENT OF AN EQUALISATION SCHEME FROM POWER FLOW  LS  MOTIVATION  ANALYSIS OF THE REQUIRED POWER FLOW FOR EQUALISATION  PROPOSED CONVERTER TOPOLOGY AND OPERATION  Stack-converter interaction  Bi-directional, multiplexed equalisation converter  Principles of operation                                                                                                                                                                                                                                                                                                                                              | 92 92 93 95 95 97                      |

| 3.3 S 4 DEVE PRINCIPAL 4.1 M 4.2 A 4.3 P 4.3.1 4.3.2 4.3.3 4.3.4                                                     | LOPMENT OF AN EQUALISATION SCHEME FROM POWER FLOW  LS  MOTIVATION  ANALYSIS OF THE REQUIRED POWER FLOW FOR EQUALISATION  PROPOSED CONVERTER TOPOLOGY AND OPERATION  Stack-converter interaction  Bi-directional, multiplexed equalisation converter  Principles of operation  Limitations of efficiency                                                                                                                                                                                                                                                                                                                   | 92 92 93 95 95 101 105                 |

| 3.3 S 4 DEVE PRINCIPAL 4.1 M 4.2 A 4.3 P 4.3.1 4.3.2 4.3.3 4.3.4 4.3.5                                               | LOPMENT OF AN EQUALISATION SCHEME FROM POWER FLOW  S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                        |

| 3.3 S 4 DEVE PRINCIPAL 4.1 M 4.2 A 4.3 P 4.3.1 4.3.2 4.3.3 4.3.4 4.3.5 4.4 P                                         | LOPMENT OF AN EQUALISATION SCHEME FROM POWER FLOW  LS  MOTIVATION  ANALYSIS OF THE REQUIRED POWER FLOW FOR EQUALISATION  PROPOSED CONVERTER TOPOLOGY AND OPERATION  Stack-converter interaction  Bi-directional, multiplexed equalisation converter  Principles of operation  Limitations of efficiency  Advantages of using li-ion capacitor for proposed topology                                                                                                                                                                                                                                                       | 9292959597101106                       |

| 3.3 S 4 DEVE PRINCIPAL 4.1 M 4.2 A 4.3 P 4.3.1 4.3.2 4.3.3 4.3.4 4.3.5 4.4 P 4.4.1                                   | LOPMENT OF AN EQUALISATION SCHEME FROM POWER FLOW  S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 9293959597101105106                    |

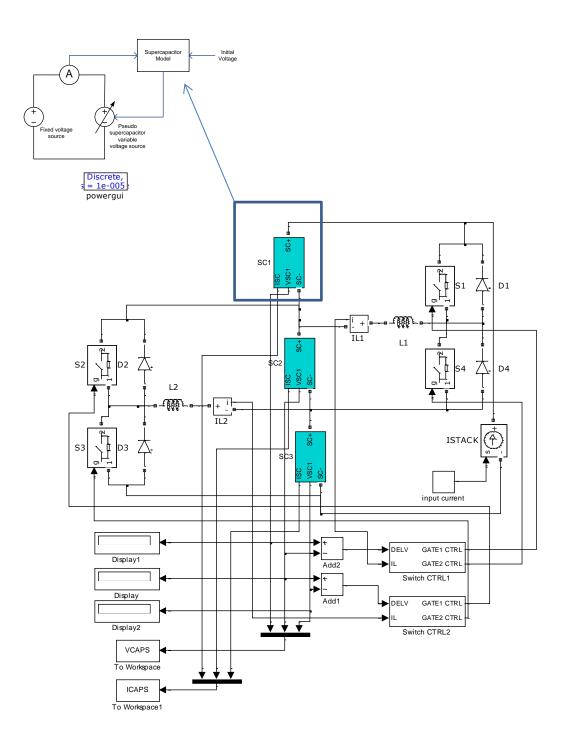

| 3.3 S 4 DEVE PRINCIPAL 4.1 M 4.2 A 4.3 P 4.3.1 4.3.2 4.3.3 4.3.4 4.3.5 4.4 P 4.4.1 4.4.2                             | LOPMENT OF AN EQUALISATION SCHEME FROM POWER FLOW  S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                        |

| 3.3 S 4 DEVE PRINCIPAL 4.1 M 4.2 A 4.3 P 4.3.1 4.3.2 4.3.3 4.3.4 4.3.5 4.4 P 4.4.1 4.4.2                             | LOPMENT OF AN EQUALISATION SCHEME FROM POWER FLOW  S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                        |

| 3.3 S 4 DEVE PRINCIPAL 4.1 M 4.2 A 4.3 P 4.3.1 4.3.2 4.3.3 4.3.4 4.3.5 4.4 P 4.4.1 4.4.2 4.5 S                       | LOPMENT OF AN EQUALISATION SCHEME FROM POWER FLOW  S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                        |

| 3.3 S 4 DEVE PRINCIPAL 4.1 M 4.2 A 4.3 P 4.3.1 4.3.2 4.3.3 4.3.4 4.3.5 4.4 P 4.4.1 4.4.2 4.5 S 5 EXPER               | LOPMENT OF AN EQUALISATION SCHEME FROM POWER FLOW  LS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 92 92 93 95 97 101 106 106 108 112     |

| 3.3 S 4 DEVE PRINCIPAL 4.1 M 4.2 A 4.3 P 4.3.1 4.3.2 4.3.3 4.3.4 4.3.5 4.4 P 4.4.1 4.4.2 4.5 S 5 EXPERMISSIVE EXPERT | LOPMENT OF AN EQUALISATION SCHEME FROM POWER FLOW  LS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                        |

| 3.3 S 4 DEVE PRINCIPAL 4.1 M 4.2 A 4.3 P 4.3.1 4.3.2 4.3.3 4.3.4 4.3.5 4.4 P 4.4.1 4.4.2 4.5 S 5 EXPERMISSIVE EXPERT | LOPMENT OF AN EQUALISATION SCHEME FROM POWER FLOW  LOPMENT OF AN EQUALISATION SCHEME FROM POWER FLOW  LOPMENT OF AN EQUALISATION SCHEME FROM POWER FLOW  MOTIVATION  ANALYSIS OF THE REQUIRED POWER FLOW FOR EQUALISATION  PROPOSED CONVERTER TOPOLOGY AND OPERATION  Stack-converter interaction  Bi-directional, multiplexed equalisation converter  Principles of operation  Limitations of efficiency  Advantages of using li-ion capacitor for proposed topology  PROPOSED CONVERTER SIMULATION  Open loop control  Simulated converter waveforms  SUMMARY  RIMENTAL ARRANGEMENT, HARDWARE CONSIDERATIONS AND  MENTS | 92 92 93 95 97 101 106 106 108 112 114 |

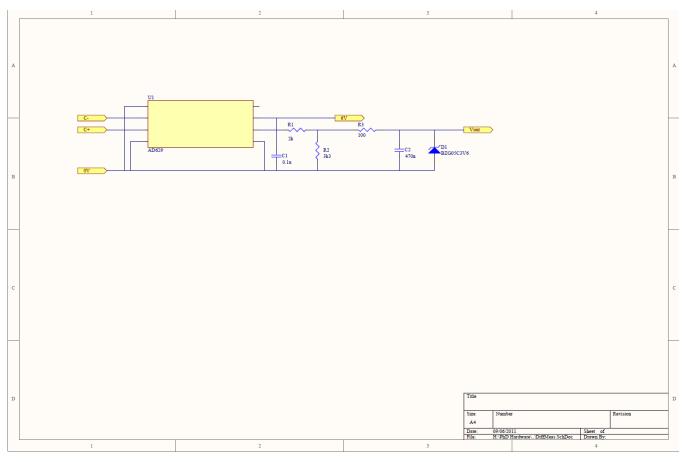

|   | 5.1.   | 3 Current measurement                                                | 115 |

|---|--------|----------------------------------------------------------------------|-----|

|   | 5.1.   | 4 Filtering considerations                                           | 116 |

|   | 5.2    | EXPERIMENT OVERVIEW                                                  | 116 |

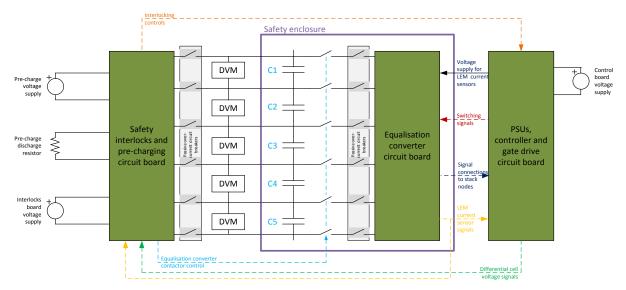

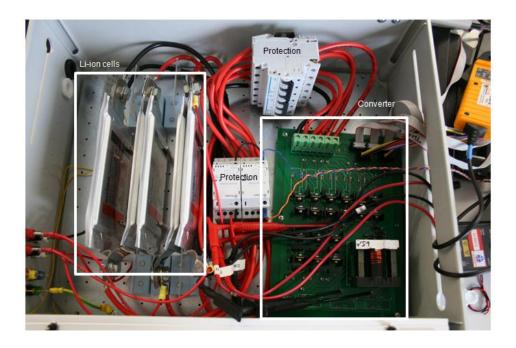

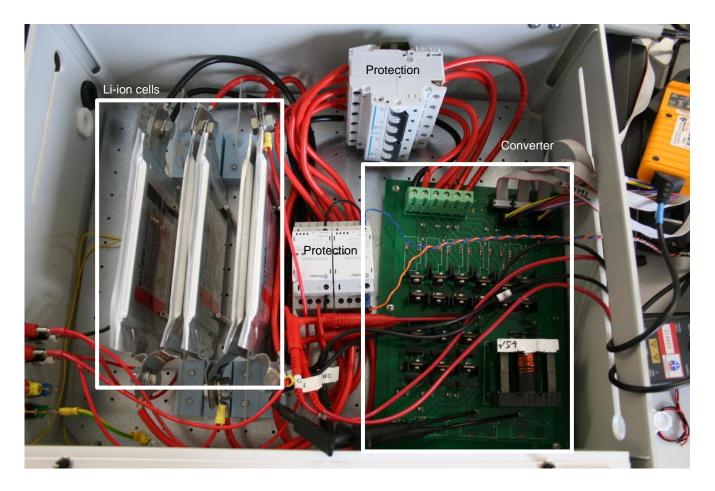

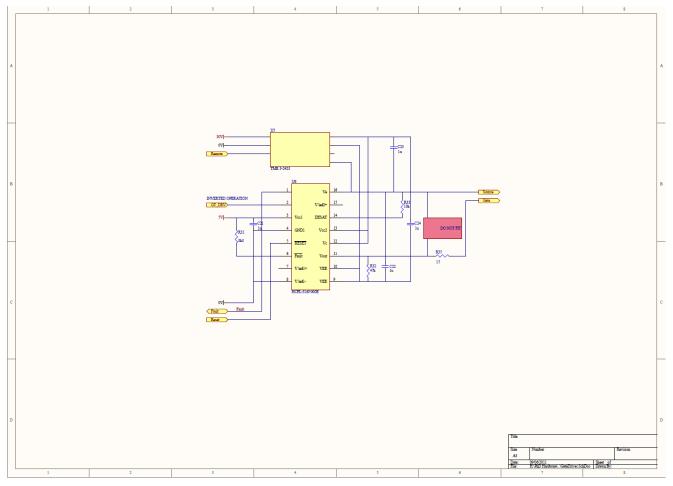

|   | 5.2.   | 1 Hardware topology 1 – stack of series connected cells              | 117 |

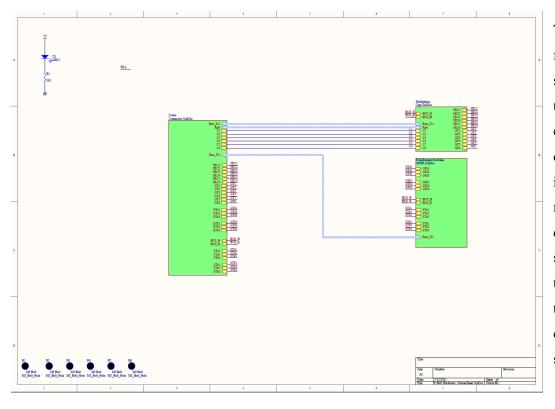

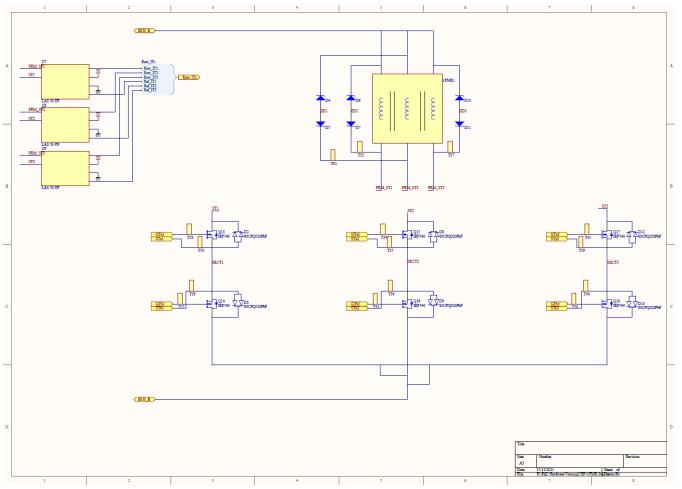

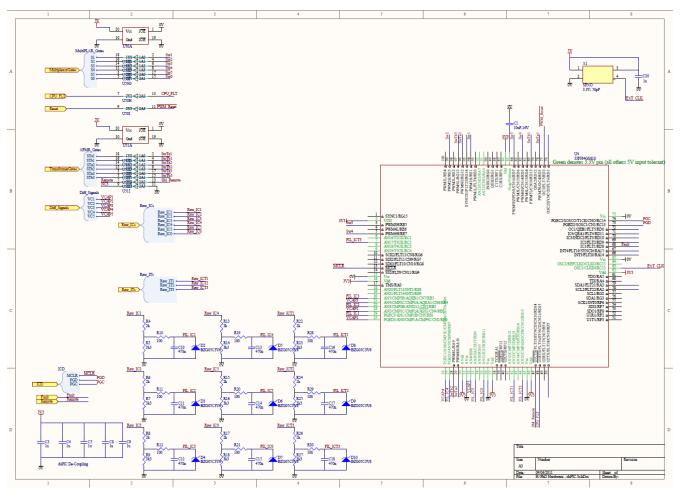

|   | 5.2.   | 2 Hardware topology 2 – equalisation converter                       | 118 |

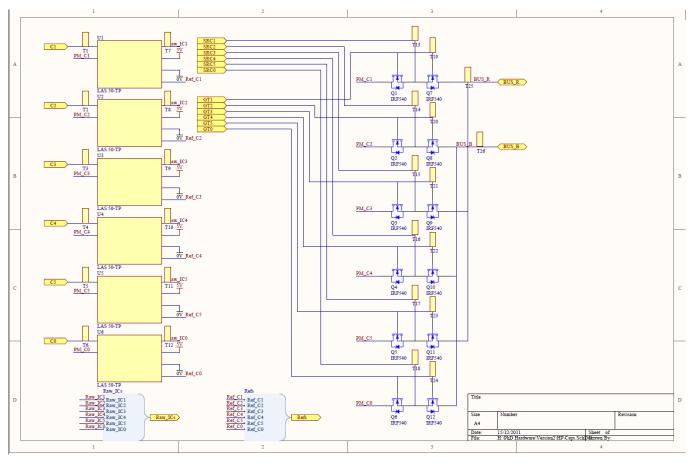

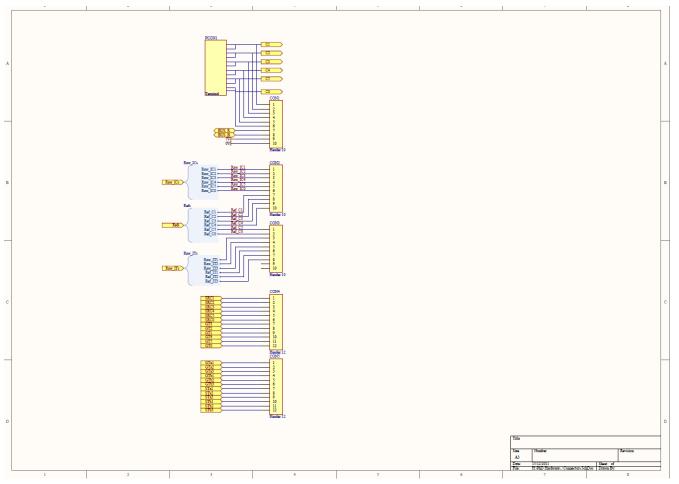

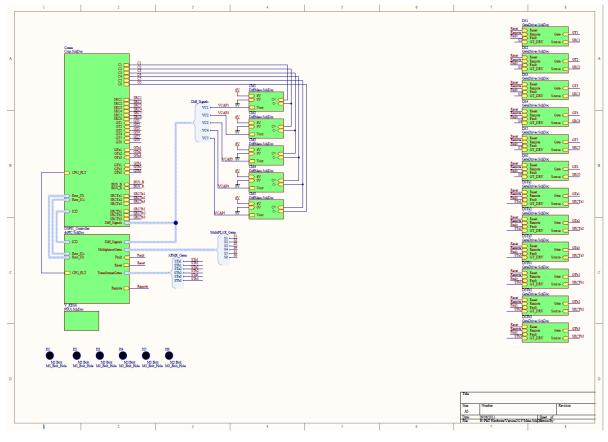

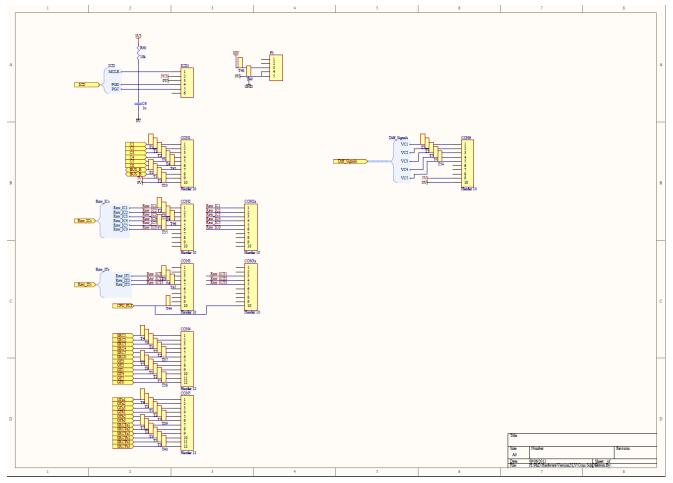

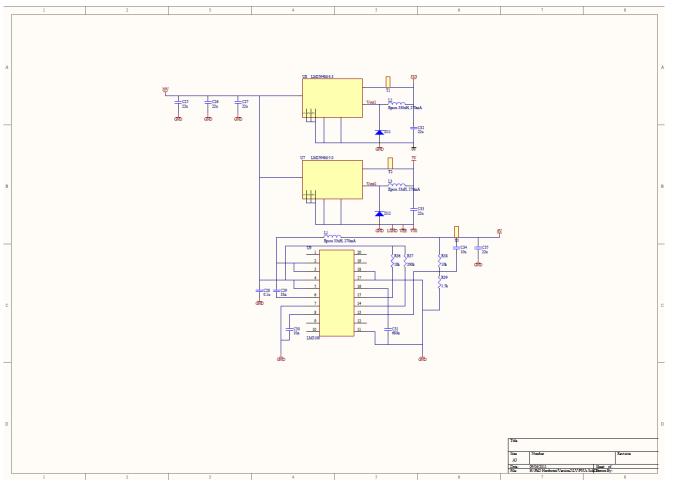

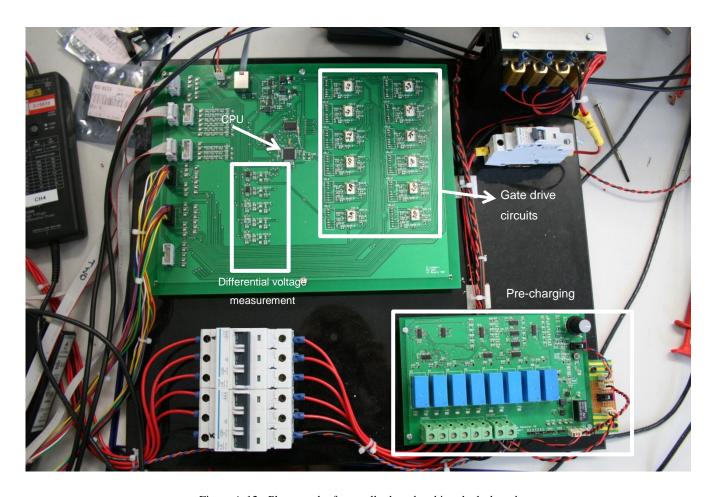

|   | 5.2.   | 3 Hardware topology 3 – converter controller and gate drive circuits | 119 |

|   | 5.2.   | 4 Hardware topology 4 – safety interlocks and pre-charging           | 122 |

|   | 5.3    | OPERATIONAL MEASUREMENTS                                             | 122 |

|   | 5.4    | LOSS ANALYSIS                                                        | 127 |

|   | 5.5    | EQUALISATION PERFORMANCE                                             | 128 |

|   | 5.6    | EXPERIMENTAL ARRANGEMENT SUMMARY                                     | 129 |

| ( | 6 CO   | NCLUSIONS                                                            | 130 |

|   | 6.1    | SUMMARY OF WORK                                                      | 130 |

|   | 6.2    | FUTURE WORK                                                          | 133 |

| I | REFERE | NCES                                                                 | 134 |

| , | A. API | PENDIX – HARDWARE SCHEMATICS                                         | A   |

# List of figures

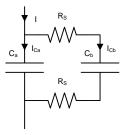

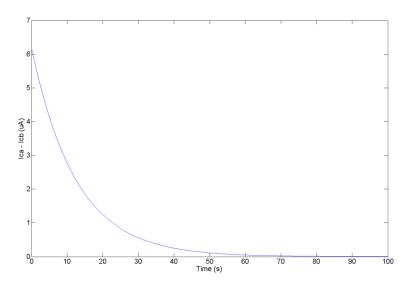

| Figure 3-15 - Difference in capacitor currents for parallel connected cells           | .60   |

|---------------------------------------------------------------------------------------|-------|

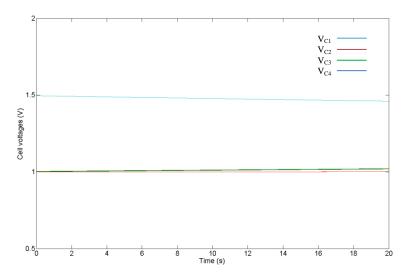

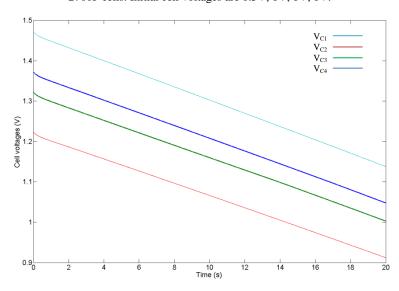

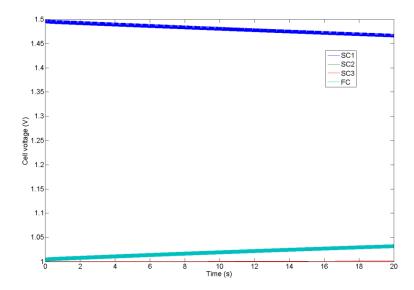

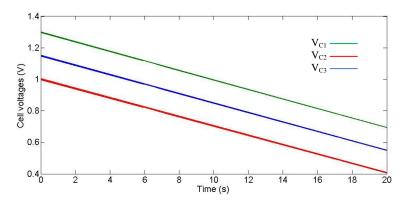

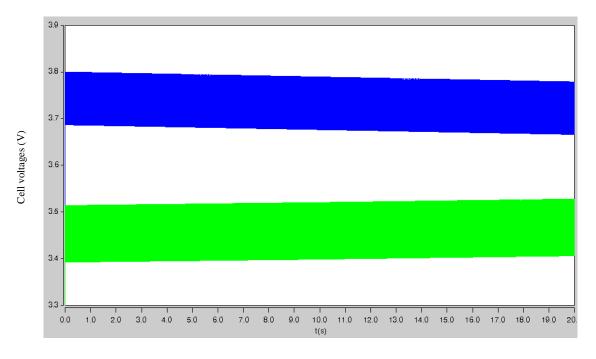

| Figure 3-16 - Cell voltages with series-parallel scheme operating at 100Hz over 20s   |       |

| with 0A stack current - four 2700F cells. Initial cell voltages are 1.5V, 1V, 1V, 1V  | .61   |

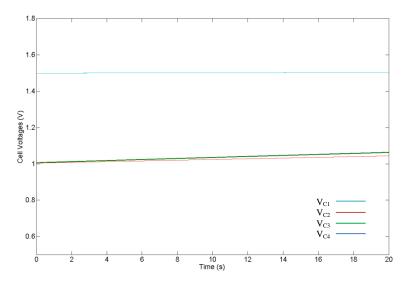

| Figure 3-17 - Cell voltages with series-parallel scheme operating at 100Hz over 20s   |       |

| with 10A charging current - four 2700F cells. Initial cell voltages are 1.5V, 1V,     |       |

| 1V, 1V                                                                                | .62   |

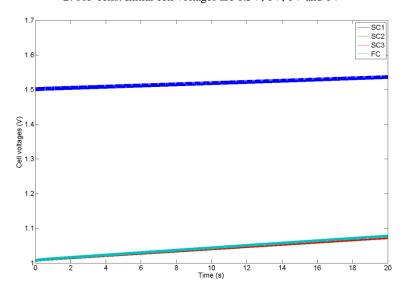

| Figure 3-18 - Cell voltages with series-parallel scheme operating at 100Hz over 20s   |       |

| with 80A discharging current – four 2700F cells. Initial cell voltages are 1.5V,      |       |

| 1.4V, 1.35V, 1.25V                                                                    | .62   |

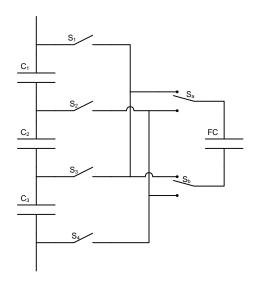

| Figure 3-19 - Flying capacitor equalisation scheme                                    | .63   |

| Figure 3-20 - Flying capacitor buss diagram                                           |       |

| Figure 3-21 - Equivalent circuit of flying capacitor scheme                           |       |

| Figure 3-22 - Switching sequence for sequential connection of flying capacitor        |       |

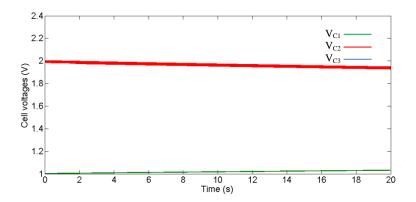

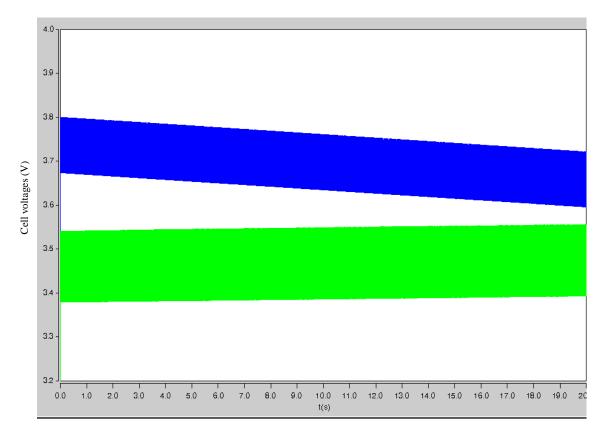

| Figure 3-23 - Cell voltages with flying capacitor scheme operating at 100Hz over      |       |

| 20s with 0A stack current - four 2700F cells. Initial cell voltages are 1.5V, 1V, 1V  |       |

| and 1V                                                                                | .66   |

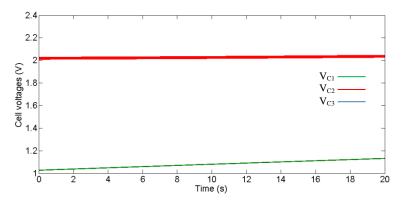

| Figure 3-24 - Cell voltages with flying capacitor scheme operating at 100Hz over      |       |

| 20s with 10A charging current - four 2700F cells. Initial cell voltages are 1.5V, 1V, |       |

| 1V and 1V                                                                             | 66    |

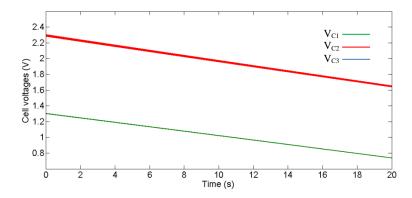

| Figure 3-25 - Cell voltages with flying capacitor scheme operating at 100Hz over      |       |

| 20s with 80A discharging current - four 2700F cells. Initial cell voltages are 1.5V,  |       |

| 1.4V, 1.35V and 1.25V                                                                 | 66    |

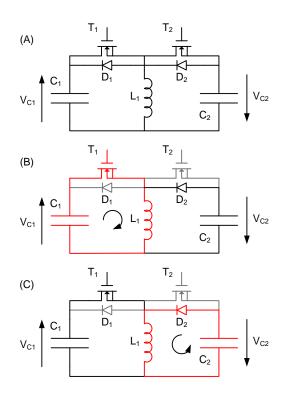

| Figure 3-26 - Operation of buck-boost voltage equalisation scheme                     |       |

| Figure 3-27 - Buck-boost equalisation converter waveforms for $V_{C1} > V_{C2}$       |       |

| Figure 3-28 - Representation of equalisation converters through deviation of stack    | .0)   |

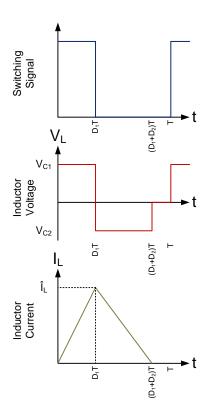

| current                                                                               | 70    |

| Figure 3-29 - Signal flow model/network model interface diagram                       |       |

| Figure 3-30 - Network model of buck-boost equalisation scheme                         |       |

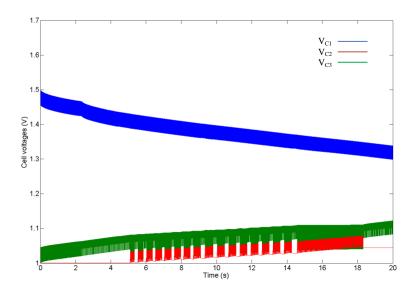

| Figure 3-31 - Cell voltages with buck-boost equalisation scheme operating over        | . 13  |

| 20s with 0A stack current – three 2700F cells. Initial cell voltages are 1.5V, 1V,    |       |

| 1V                                                                                    | 74    |

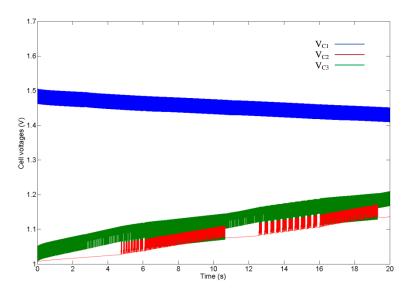

| Figure 3-32 - Cell voltages with buck-boost equalisation scheme operating over        | . , ¬ |

| 20s with 10A stack current – three 2500F cells. Initial cell voltages are 1.5V, 1V,   |       |

| 1V                                                                                    | 74    |

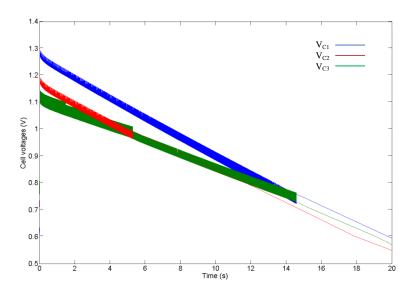

| Figure 3-33 - Cell voltages with buck-boost equalisation scheme operating over        | . / — |

| 20s with 80A discharging current – three 2500F cells. Initial cell voltages are 0.6V, |       |

| 0.7V, 0.75V                                                                           | 75    |

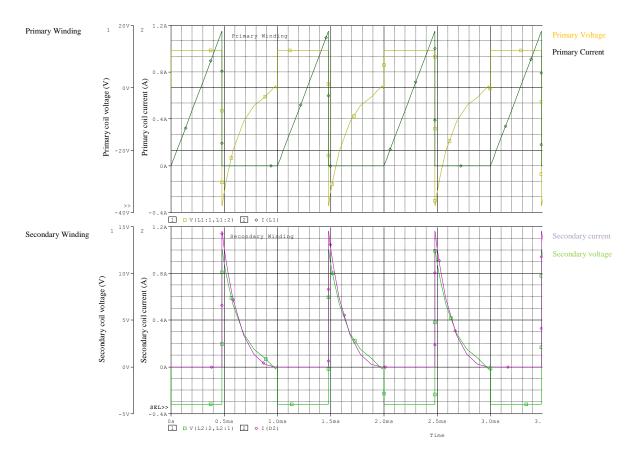

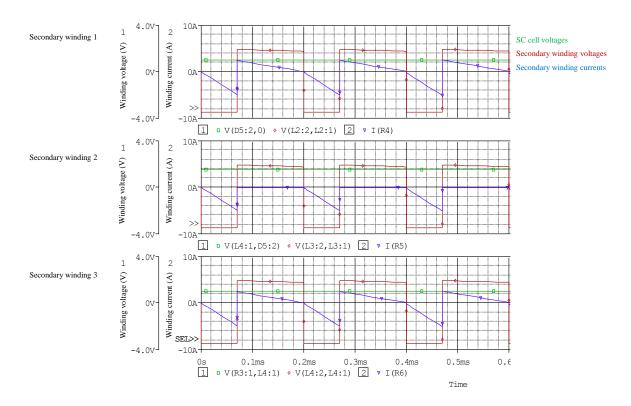

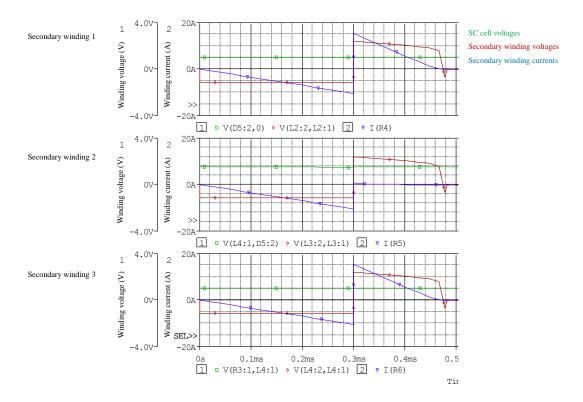

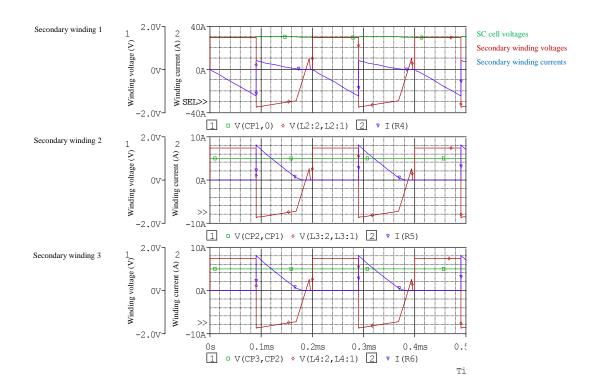

| Figure 3-35 - Voltage traces for secondary windings (red) and supercapacitor cells    | . 13  |

| (green) and supercapacitor current (blue) for the scheme shown in Figure 3-34         |       |

| operating discontinuously at frequency of 5 kHz. Initial cell voltages; 1V, 1.5V and  |       |

| 1V, stack current; 0A                                                                 | 77    |

|                                                                                       | . / / |

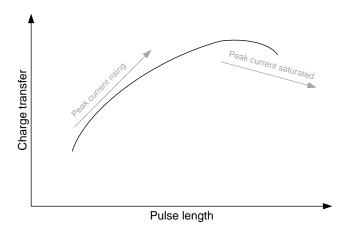

| Figure 3-36 – Design consideration for the effects on equalisation efficiency from    | 70    |

| primary pulse length for the distributed flyback equalisation scheme                  | . / 8 |

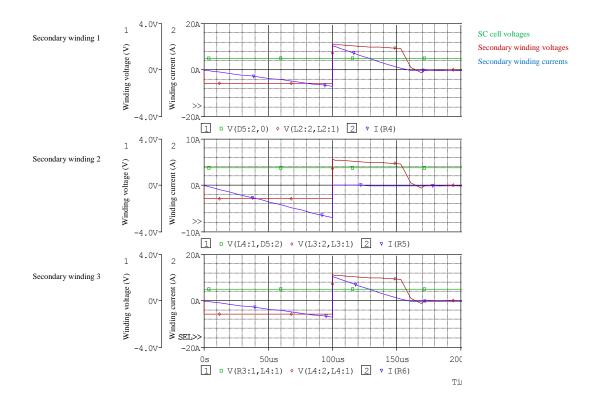

| Figure 3-37 - Voltage traces for secondary windings (red) and supercapacitor cells    |       |

| (green) and supercapacitor current (blue) for the scheme shown in figure 3-34.        |       |

| Optimised primary pulse time = 0.1ms. Initial cell voltages; 1V, 1.5V and 1V,         | 70    |

| stack current; 0A.                                                                    | . 19  |

| Figure 3-38 - Voltage traces for secondary windings (red) and supercapacitor cells    |       |

| (green) and supercapacitor current (blue) for the scheme shown in Figure 56.          |       |

| Optimised primary pulse time = 0.3ms. Initial cell voltages; 1V, 1.5V and 1V,                                                                                                                                                                 | 00  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| stack current; 0A.                                                                                                                                                                                                                            | 80  |

| Figure 3-39 - Voltage traces for secondary windings (red) and supercapacitor cells (green) and supercapacitor current (blue) for the scheme shown in Figure 56. Optimised primary pulse time = 0.9ms. Initial cell voltages; 1V, 1.5V and 1V, | 0.0 |

| stack current; 0A.                                                                                                                                                                                                                            | 80  |

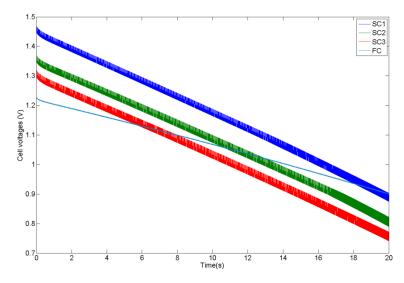

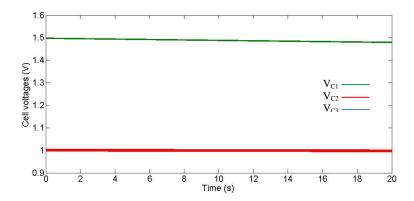

| Figure 3-40 - Cell voltages with distributed flyback equalisation scheme operating at 5 kHz over 20s with 0A stack current - three 2700F cells. Initial cell voltages are                                                                     |     |

| 1.5V, 1V and 1V                                                                                                                                                                                                                               | 82  |

| Figure 3-41 - Cell voltages with distributed flyback equalisation scheme operating at 5 kHz over 20s with 10A stack current - three 2700F cells. Initial cell voltages                                                                        | 0.2 |

| are 1.5V, 1V and 1V                                                                                                                                                                                                                           | 82  |

| Figure 3-42 - Cell voltages with distributed flyback equalisation scheme operating                                                                                                                                                            |     |

| at 5 kHz over 20s with -80A stack current - three 2700F cells. Initial cell voltages are 1.5V, 1V and 1V                                                                                                                                      | 82  |

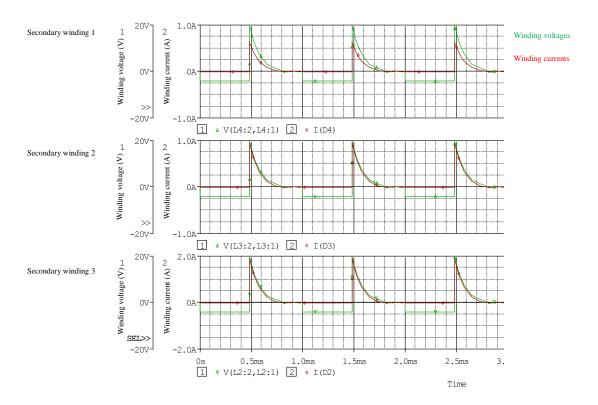

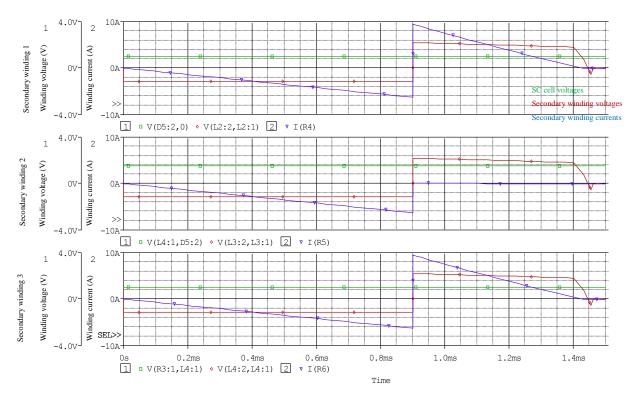

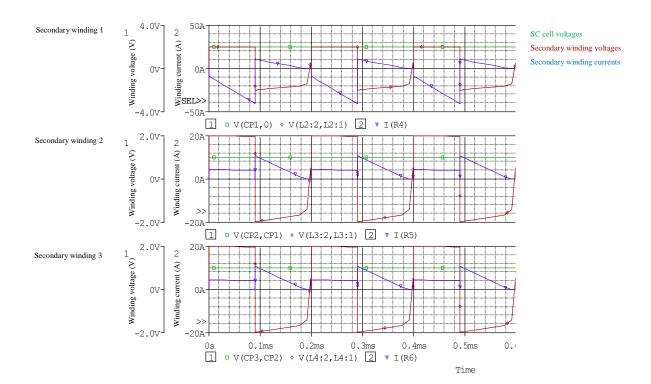

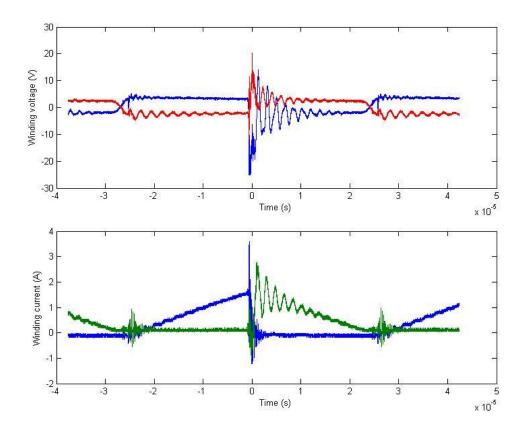

| Figure 3-43 – Voltage traces for primary windings (red) and supercapacitor cells (green) and supercapacitor current (blue) for circuit shown in with $C_1 = 1.5V$ and                                                                         |     |

| $C_2$ and $C_3 = 1V$ . $T_1$ switching at 5 kHz with a duty of 0.45                                                                                                                                                                           | 84  |

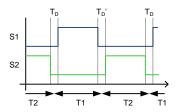

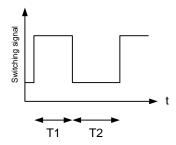

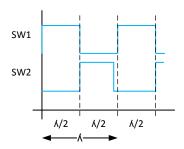

| Figure 3-44 - PWM switching period                                                                                                                                                                                                            | 84  |

| Figure 3-45 - Voltage traces for primary windings (red) and supercapacitor cells                                                                                                                                                              |     |

| (green) and supercapacitor current (blue) for circuit shown in Figure 66 with C1 =                                                                                                                                                            |     |

| 2V and C2 and C3 = 1V. T1 switching at 5 kHz with a duty of 0.45                                                                                                                                                                              | 85  |

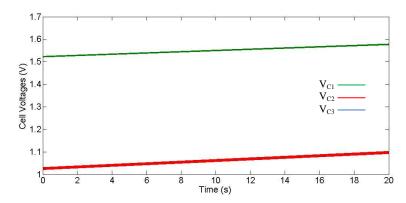

| Figure 3-46 - Cell voltages with distributed forward equalisation scheme operating                                                                                                                                                            |     |

| at 5 kHz over 20s with 0A stack current - three 2700F cells. Initial cell voltages are                                                                                                                                                        |     |

| 2V, 1V and 1V                                                                                                                                                                                                                                 | 86  |

| Figure 3-47 - Cell voltages with distributed forward equalisation scheme operating                                                                                                                                                            |     |

| at 5 kHz over 20s with 10A stack current - three 2700F cells. Initial cell voltages                                                                                                                                                           | 0.4 |

| are 2V, 1V and 1V                                                                                                                                                                                                                             | 86  |

| Figure 3-48 - Cell voltages with distributed forward equalisation scheme operating                                                                                                                                                            |     |

| at 5 kHz over 20s with -80A stack current - three 2700F cells. Initial cell voltages                                                                                                                                                          | 07  |

| are 2.3V, 1.3V and 1.3V                                                                                                                                                                                                                       | 8/  |

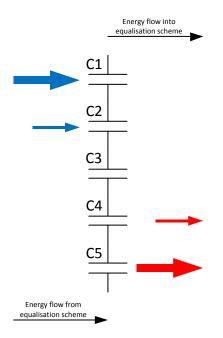

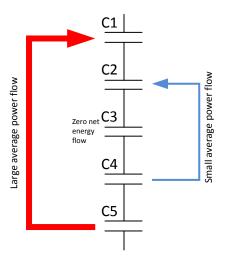

| Figure 4-2 - Average power flow to and from stack in idealised equalisation                                                                                                                                                                   | 0.4 |

| schemeFigure 4-3 - Average power flow between cells in idealised global equalisation                                                                                                                                                          | 94  |

| converter                                                                                                                                                                                                                                     | 95  |

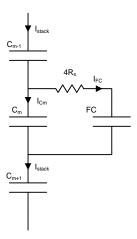

| Figure 4-4 - Interaction between equalisation converter and capacitor stack                                                                                                                                                                   |     |

| Figure 4-5 - Two MOSFET switches arranged in anti-series to form bi-directional                                                                                                                                                               | 70  |

| switch (Gate, Drain and Source indicated)                                                                                                                                                                                                     | 96  |

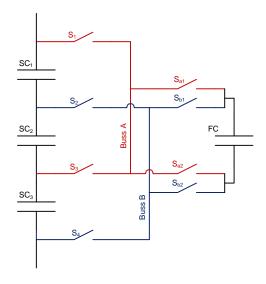

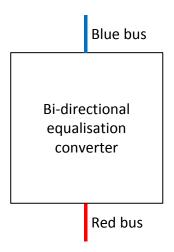

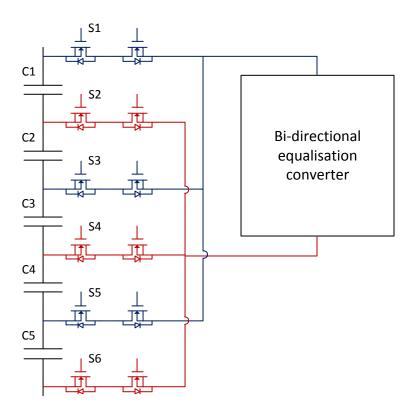

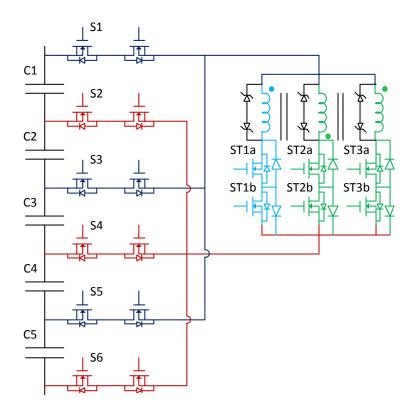

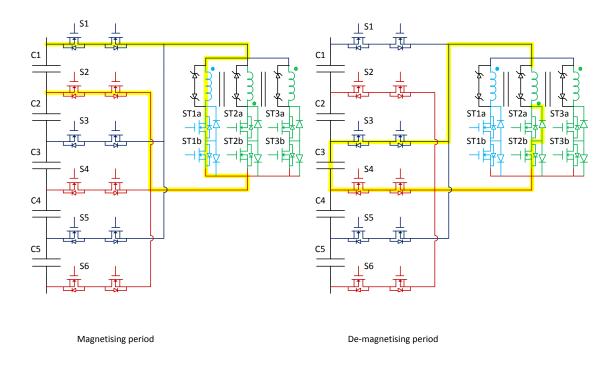

| Figure 4-6 - Bi-directional equalisation converter with red and blue energy busses                                                                                                                                                            |     |

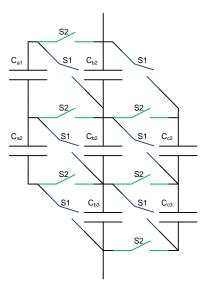

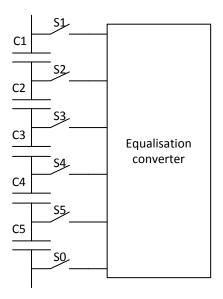

| Figure 4-7 - Multiplexed input/output to equalisation converter using bi-directional                                                                                                                                                          | ) 1 |

| switches and energy busses.                                                                                                                                                                                                                   | 98  |

| Figure 4-8 - Equalisation through multiplexed selected coil converter                                                                                                                                                                         |     |

| Figure 4-9 - Conduction paths relating to description of operation                                                                                                                                                                            |     |

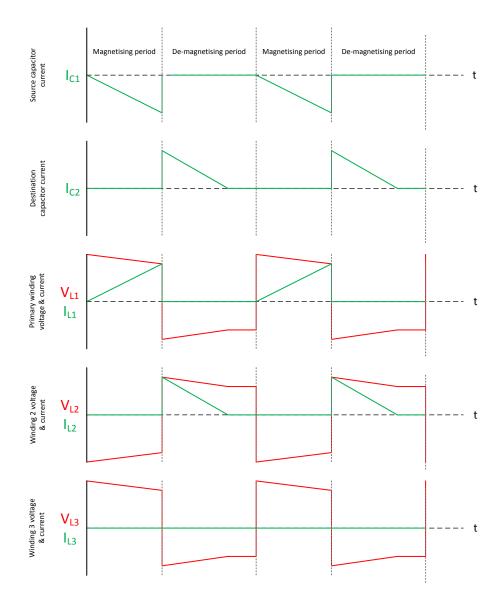

| Figure 4-10 – Predicted converter waveforms                                                                                                                                                                                                   |     |

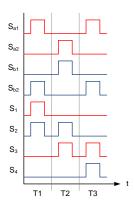

| Figure 4-11 - Switching sequence for proposed converter                                                                                                                                                                                       |     |

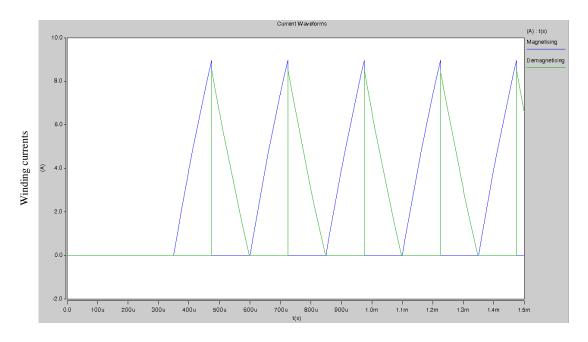

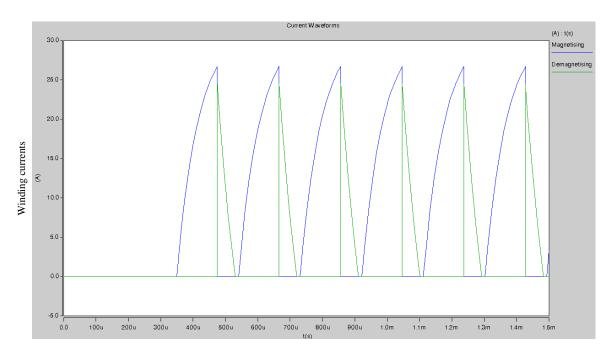

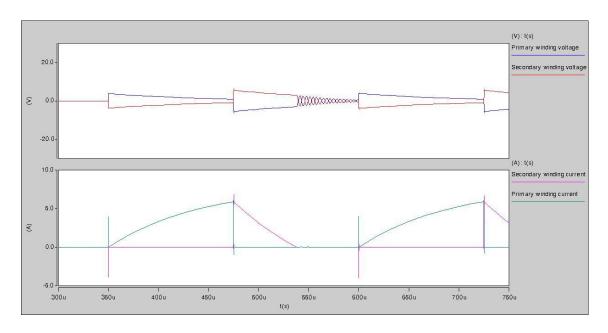

| Figure 4-13 - Converter current waveforms, $f = 4kHz$ , $Lp = 20\mu H$                                                                                                                                                                        |     |

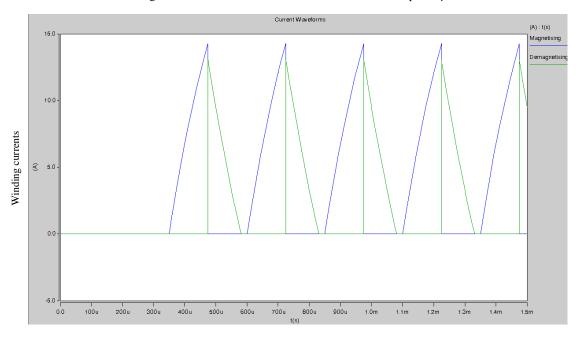

| Figure 4-14 - Converter current waveforms, f = 4kHz, Lp = 6µH                                                                                                                                                                                 |     |

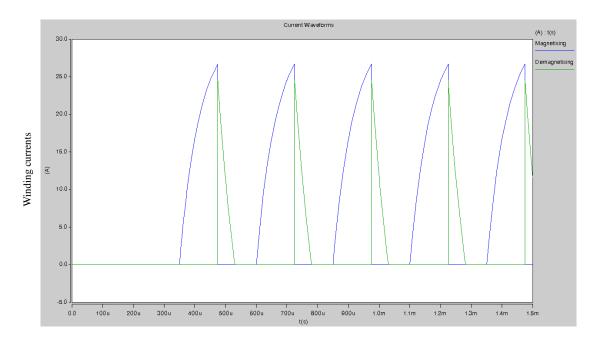

| Figure 4-15 - Converter current waveforms, f = 4kHz, Lp = 4µH                                                                                                                                                                                 |     |

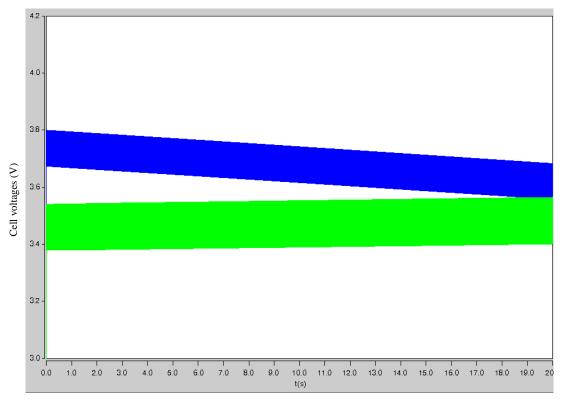

| Figure 4-16 - Cell voltages for C1 and C3 over 20s equalisation at limit of                                                                                                                                                                   |     |

| continuous conduction. Initial Voltages C1 = 3.8V and C3 = 3.4V                                                                                                                                                                               | 110 |

| Figure 4-17 - Cell voltages for C1 and C3 over 20s equalisation at $\in$ = 0.33. Initial |    |

|------------------------------------------------------------------------------------------|----|

| Voltages C1 = 3.8V and C3 = 3.4V                                                         | 11 |

| Figure 4-18 - Converter current waveforms with increased duty ratio∈ = 0.33, f =         |    |

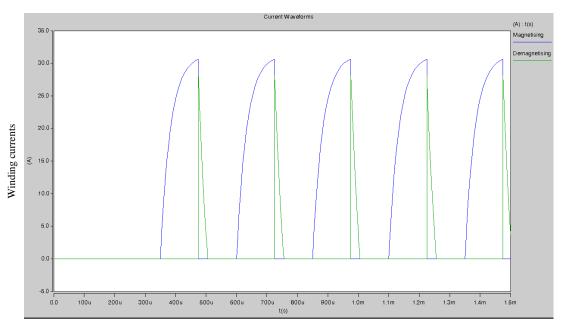

| $5.25$ kHz, $Lp = 6\mu$ H                                                                | 12 |

| Figure 4-19 - Cell voltages for C1 and C3 over 20s equalisation at increased             |    |

| frequency and duty cycle $\in$ = 0.33. Initial Voltages C1 = 3.8V and C3 = 3.4V1         | 12 |

| Figure 5-1- System level diagram of experimental apparatus1                              | 17 |

| Figure 5-2 - Arrangements of five cells in series connected stack, cells numbered in     |    |

| blue and nodes in black1                                                                 | 17 |

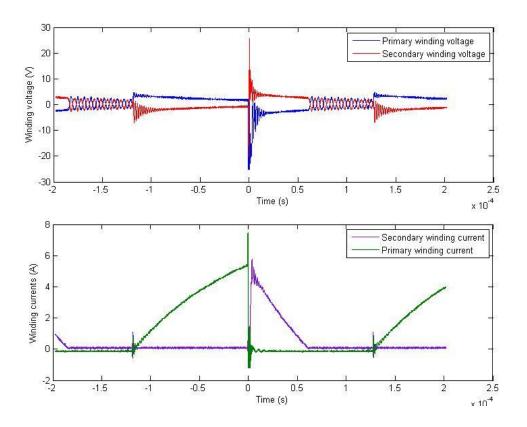

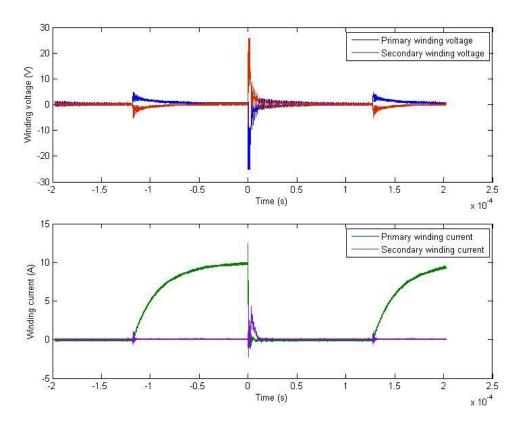

| Figure 5-4 - Voltage and current waveforms for converter operation. f = 4kHz, Lp         |    |

| = 44uH12                                                                                 | 23 |

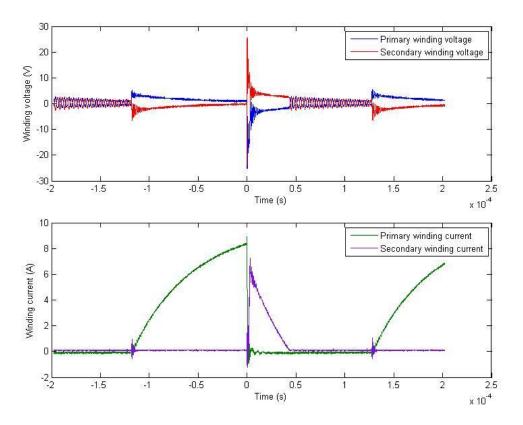

| Figure 5-5 - Voltage and current waveforms for converter operation. f = 4kHz, Lp         |    |

| = 20uH12                                                                                 | 23 |

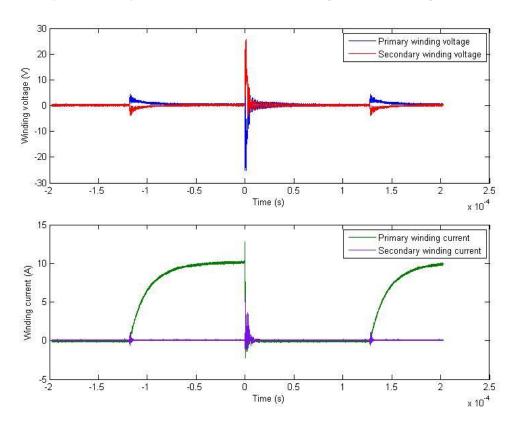

| Figure 5-6 - Voltage and current waveforms for converter operation. $f = 4kHz$ , Lp      |    |

| = 6.5uH                                                                                  | 24 |

| Figure 5-7 - Voltage and current waveforms for converter operation. $f = 4kHz$ , Lp      |    |

| = 3.5uH                                                                                  |    |

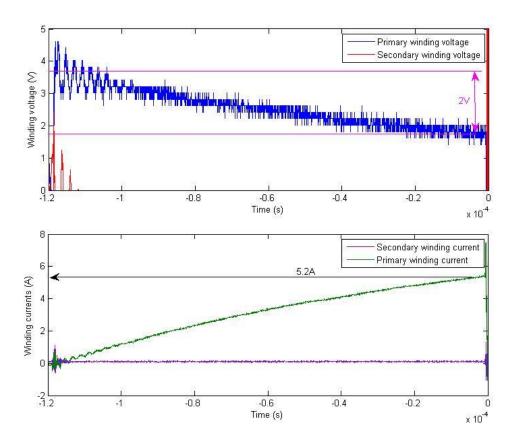

| Figure 5-8 - Analysis of voltage drop during magnetisation. $f = 4kHz$ , $Lp = 44uH12$   | 25 |

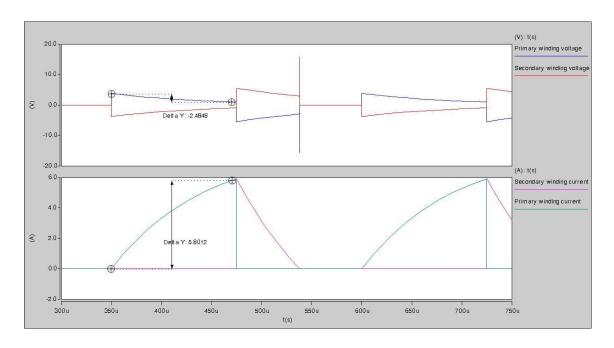

| Figure 5-9 - Adjusted simulation results for greater series resistance of conduction     |    |

| loop12                                                                                   | 26 |

| Figure 5-10 - Simulated voltage waveforms with lumped transformer winding                |    |

| capacitances to approximate ringing effect                                               | 26 |

| Figure 5-11 - Voltage and current waveforms for converter operation. f = 20kHz,          |    |

| Lp = 44uH12                                                                              |    |

| Figure A-2 – Converter board multiplexor subsystem schematic                             |    |

| Figure A-3 – Converter board converter subsystem schematic                               |    |

| Figure A-4 – Converter board connectors subsystem schematic                              |    |

| Figure A-5 - Photograph of converter board and Li-ion cell stack                         |    |

| Figure A-6 - Controller board top level schematic                                        |    |

| Figure A-7 – Controller board connectors subsystem schematic                             |    |

| Figure A-8 - Controller board differential measurement subsystem schematic               |    |

| Figure A-9 - Controller board microprocessor subsystem schematic                         |    |

| Figure A-10 - Controller board gate drive circuit subsystem schematic                    |    |

| Figure A-11 - Controller board power supplies subsystem schematic                        |    |

| Figure A-12 - Photograph of controller board and interlocks board                        | L  |

# List of tables

| Table 2-3 - Summary of EDLC advantages and disadvantages                   | 36  |

|----------------------------------------------------------------------------|-----|

| Table 3-1 - Grouping of families of existing equalisation schemes          | 51  |

| Table 3-3 - Simulated equalisation rates for existing converters           | 91  |

| Table 4-1 - Lookup table for bus polarity for five cells                   | 99  |

| Table 4-2 - Reduced look-up table for bus polarity                         | 99  |

| Table 4-4 - Simulated equalisation rates for existing converters           | 113 |

| Table 5-1- Range of absolute voltages for nodes in the stack of five cells | 118 |

| Table 5-2 - Equalisation rate for each winding inductance                  | 128 |

| Table 5-3 - Simulated equalisation rates for existing converters           | 129 |

#### Nomenclature

The terms supercapacitor, ultracapacitor and electrochemical-double-layer-capacitor (EDLC) are commonly used interchangeably in both academic literature and technical journalism. Where the context is that of a particular product the author has attempted, where possible, to use the commercial term for that particular product. Elsewhere the term employed usually relates directly to how it is presented in a referenced work or datasheet. For other purposes the terms can generally be considered interchangeable. A Lithium-ion capacitor is a separate technology.

#### Abbreviations

AC Alternating current

ADC Analogue to digital converter

DC Direct current

CAD Computer aided design

CMOS Complementary metal-oxide-semiconductor

EDLC Electric double-layer capacitor

EIS Electrochemical impedance spectroscopy

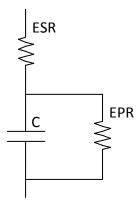

ESR Equivalent series resistance

EPR Equivalent parallel resistance

ESS Energy storage system

ICE Internal combustion engine

IEEE Institute of Electrical and Electronic Engineers

Li-ion Lithium-ion

MEMS Micro-electro-mechanical systems

MOSFET Metal oxide surface field effect transistor

MMF Magneto motive force

MIPS Mega instructions per second

PV Photovoltaic

PCB Printed circuit board

PWM Pulse width modulation

RC Resistor-capacitor

SOC State of charge

SOH State of health

UPS Uninterruptable power supply

VA Voltage-ampere rating

#### Symbols

A Area of plate in parallel plate capacitor

C Capacitance

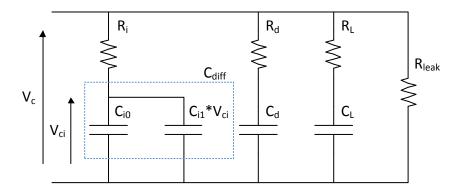

$C_d$  Delayed branch capacitance (3 branch model)

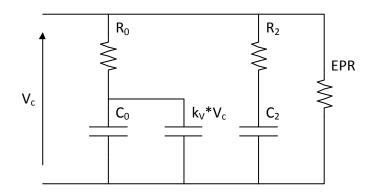

$C_{diff}$  Combination of  $C_{i0}$  and  $C_{i1}$

$C_{i0}$  Immediate branch fixed capacitance (3 branch model)  $C_{i1}$  Immediate branch variable capacitance (3 branch model)

$C_L$  Long term branch capacitance (3 branch model)

D Electric flux

d Distance between parallel plates

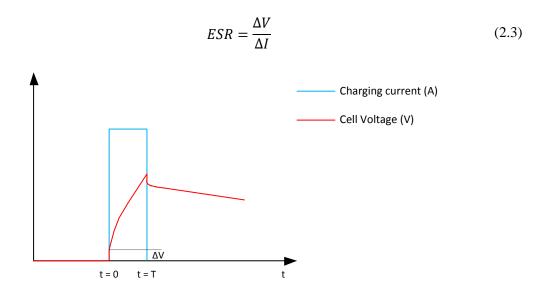

$\Delta V$  Step change in voltage  $\Delta I$  Step change in current  $\nabla$  Divergence function E Electric field strength

$E_c$  Energy stored in a capacitor

$\epsilon$  Equalisation efficiency  $\epsilon_0$  Permittivity of free space

$\varepsilon_r$  Relative permittivity

$f_c$  Filter corner frequency

I Current (constant)

*Î* Peak current

$I_{avg}$  Average current

$I_{eq}$  Equalisation current i Current (time variant)  $i_{Cn}$  Current in capacitor n

j Imaginary operator

$k_V$  Coefficient of variable capacitance (2 branch model)

L Inductance

$L_P$  Primary winding inductance  $L_S$  Secondary winding inductance

M Coupling coefficient

$N_P$  Number of primary turns  $N_S$  Number of secondary turns

P Polarisation

$\rho$  Surface charge density

$\phi$  Phase difference

Q Charge

$R_d$  Delayed branch resistance (3 branch model)  $R_i$  Immediate branch resistance (3 branch model)  $R_L$  Long term branch resistance (3 branch model)

$R_{Leak}$  Leakage resistance (3 branch model)

$R_S$  Switch resistance

$R_{ch}$  MOSFET channel resistance

S Reluctance

s Lapacian operator

t Time

$\tau_2$  Time constant of second branch (2 branches model)

V Voltage (constant)

Peak voltage

*V<sub>C</sub>* Capacitor voltage

$V_{Cn}$  Voltage of capacitor n in a capacitor stack

$V_{Ci}$  Coefficient of immediate branch variable capacitance (3-branches model)

$V_{Df}$  Diode forward voltage

v Voltage (time variant)

$\omega$  Angular velocity

$\varphi$  Depression factor

$X_L$  Reactance of an inductor

χ Dielectric material susceptibility

Z Complex impedance

$Z_{CPE}$  Impedance of constant phase element

$Z_{im}$  Imaginary impedance

$Z_{re}$  Real impedance

$Z_{Zarc}$  Impedance of a Zarc element

|Z| Impedance magnitude

$Z_p$  Porous electrode impedance

# Publications by the author

Lambert, S.M.; Pickert, V.; Holden, J.; He, X; Li, W; , "Comparison of supercapacitor and lithium-ion capacitor technologies for power electronics applications," *Power Electronics, Machines and Drives* (*PEMD 2010*), 5th IET International Conference on , vol., no., pp.1-5, 19-21 April 2010 doi:10.1049/cp.2010.0115

URL: <a href="http://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=5522509&isnumber=5522470">http://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=5522509&isnumber=5522470</a>

Lambert, S.; Pickert, V.; Holden, J.; Wuhua Li; Xiangning He; , "Overview of supercapacitor voltage equalisation circuits for an electric vehicle charging application," *Vehicle Power and Propulsion Conference (VPPC)*, 2010 IEEE, vol., no., pp.1-7, 1-3 Sept. 2010 doi:10.1109/VPPC.2010.5729226

URL: <a href="http://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=5729226&isnumber=5728974">http://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=5729226&isnumber=5728974</a>

Zhao, Yi; Li, Wuhua; Deng, Yan; He, Xiangning; Lambert, Simon; Pickert, Volker; , "High step-up boost converter with coupled inductor and switched capacitor," *Power Electronics, Machines and Drives* (*PEMD 2010*), 5th IET International Conference on , vol., no., pp.1-6, 19-21 April 2010 doi:10.1049/cp.2010.0009

URL: http://ieeexplore.ieee.org/stamp/stamp.isp?tp=&arnumber=5523809&isnumber=5522470

Li, Weichen; Li, Wuhua; He, Xiangning; Lambert, Simon; Pickert, Volker; , "Performance analysis of ZVT interleaved high step-up converter with built-in transformer," *Power Electronics, Machines and Drives (PEMD 2010), 5th IET International Conference on*, vol., no., pp.1-6, 19-21 April 2010 doi:10.1049/cp.2010.0010

URL: <a href="http://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=5523810&isnumber=5522470">http://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=5523810&isnumber=5522470</a>

Yang, Bo; Li, Wuhua; Deng, Yan; He, Xiangning; Lambert, Simon; Pickert, Volker; , "A novel single-phase transformerless photovoltaic inveter connected to grid," *Power Electronics, Machines and Drives* (*PEMD 2010*), 5th IET International Conference on , vol., no., pp.1-6, 19-21 April 2010 doi:10.1049/cp.2010.0129

URL: <a href="http://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=5522524&isnumber=5522470">http://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=5522524&isnumber=5522470</a>

Smith, D. J. B.; Lambert, S. M.; Mecrow, B. C.; Atkinson, G. J.; , "Interaction between PM rotor design and voltage fed inverter output," *Power Electronics, Machines and Drives (PEMD 2012), 6th IET International Conference on*, vol., no., pp.1-6, 27-29 March 2012 doi:10.1049/cp.2012.0274

URL: http://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=6242124&isnumber=6241991

# 1 Introduction

This chapter introduces the themes of this work; the technology and history of high capacitance electrical energy storage systems, the applications of such devices, the specific introduction of Lithium-ion capacitor devices, power electronic interaction and the requirements for voltage equalisation.

# 1.1 Objectives and contribution

The author's work contained in this thesis was carried out as part of an Engineering and Physical Sciences Research Council (EPSRC) funded project. The project (number EP/F06151X) is a UK-China partnership combining the work of seven UK and nine Chinese PhD studentships. The consortium consists of five UK universities with four industrial partners and four of China's key universities, one research institute, and three commercial organisations.

The objectives of the research project as a whole were to research increased reliability in renewable energy generation systems and networks. To that end, this work relates to essential safety and efficiency issues with electrical energy storage and its applicability to renewable generation but also many other applications.

Upon commencement of the project the objectives of this work were as follows;

- Study state of-the-art high capacitance technologies

- Establish safety critical, failure mode, lifetime and efficiency issues

- Develop progressive technology to positively contribute to one or more of the above identified issues

After review of the first two points, the voltage equalisation of high capacitance electrical energy storage systems was considered an area of interest as there was little published work on active converters for the purpose. The objectives of the project were then more closely specified as:

- Establish a family of electrical energy storage systems with a suitable requirement for voltage balancing when assembled into modules

- Study modelling techniques of these devices and establish a suitable modelling process for the study of equalisation schemes

- Carry out a critical review of published equalisation schemes including simulation of performance

- Establish weaknesses, if any, in the existing solutions and propose improvements or an enhanced design specification

- Develop from the above research an improved equalisation scheme and demonstrate its effectiveness

The contributions of this work, which the author believes to be previously unpublished, are as follows:

- Electrochemical impedance analysis of Lithium-ion capacitors (see section 1.3.2 for description of these devices) developed by the company JSR Micro

- Critical comparison between the JSR Micro Li-ion capacitor and a Maxwell carbon electrode double layer ultracapacitor

- Development of modelling technique for Li-ion capacitors which is analogous to a previously published method for traditional ultracapacitors

- Simulation of published equalisation schemes for critical analysis

- A unique method for grouping published equalisation schemes into families either based on constituent parts or energy flow paths – although the latter is a development of work which is referenced within

- A development of energy flow path concepts into power flow paths to demonstrate

wasted power overhead in equalisation schemes. This leads to the conclusion that an

equalisation scheme can be designed with lowered aggregate power rating but

maintained performance

- A new equalisation converter topology based on the ideas developed above designed to reduce wasted overhead in power rating and therefore mass and volume issues, whilst maintaining effective equalisation performance

Whilst this work was undertaken as part of a collaborative project the work contained herein is in no way a repetition or collaboration of other work within the FRENS programme.

#### 1.2 Thesis Overview

Chapter one introduces high capacitance technology; the historical background, applications and general principles of the double layer effect. An introduction into modules of cells and power electronic interface is given. A general overview of design considerations and modelling is shown.

Chapter two describes modelling techniques for high capacitance cells. Initially, a study is undertaken into the supercapacitor devices themselves comprising of a brief overview of the electrochemical processes followed by a review of modelling techniques. A new family of devices, the Li-ion capacitor, is presented. A new method to model this device which is analogous to a modelling method of more traditional devices, identified as a suitable method for modelling power electronic interface, is also developed.

Chapter three is a representative review of published equalisation schemes. Individual description of operation, critique and simulation is made. A method of grouping the existing solutions into families of equalisation schemes is proposed which allows conclusions about

equalisation scheme performance depending on topology types, constituent components and energy flow paths to be generalised. This leads to a specification of a more idealised equalisation scheme based on the advantages and failings of existing schemes.

Chapter four uses the ideas established in chapter three for an improved specification to develop a new equalisation scheme using an entirely new equalisation scheme converter topology which negates some of the failings in existing schemes. The development of the new topology through an understanding of the power flow requirements in an equalisation scheme is shown. Simulation of the proposed system is shown with discussion on control methods and expected efficiencies.

Chapter five outlines the experimental arrangements of the prototype hardware setup. An overview is made of the experimental setup describing the function of each section. The hardware issues and mitigations are described.

In chapter six it is concluded that the proposed system, as constructed, whilst showing significant advantages also shows potential for improvement both in the practical implementation of the prototype and in the control of the system.

# 1.3 Introduction to capacitance, double layer effects and advances in Li-ion technology

The ability to store energy is a fundamental building block in engineering. As uses for electricity grew throughout the nineteenth and twentieth centuries the facility to store electrical energy became essential. In modern times electrical energy storage is utilised in millions of devices and pieces of equipment and is vital to the running almost every industrialised system.

As applications and demands have evolved the demands and requirements for electrical energy storage systems (ESS) has grown and diversified greatly. Consequently, many families of electrical ESS exist today. These range from tiny batteries which power watches or small medical equipment to very large capacitor banks in electricity distribution systems. The progression of development of the many forms of electrical ESS has led to the growth of multiple, very large, industries to support the technology.

Initially, research centred on the development of electrochemical batteries such as lead-acid technology. The development of new battery chemistry carries on in a multi-billion pound industry as new more challenging demands are made of battery technology.

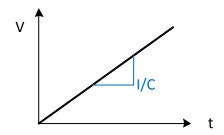

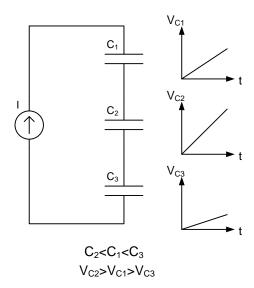

Electronic double layer capacitors (EDLCs) are commonly known as ultracapacitors, a term which was trademarked by NEC Tokin in 1975 [1], however other terms such as supercapacitors or power capacitors are in common use [2]. Early patents for the EDLC exist for General Electric in 1957 [3] and Standard Oil Company of Ohio (SOHIO) in 1970 [4]. Unlike

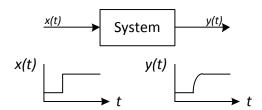

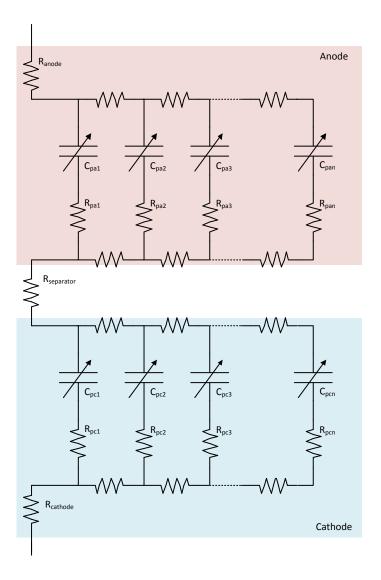

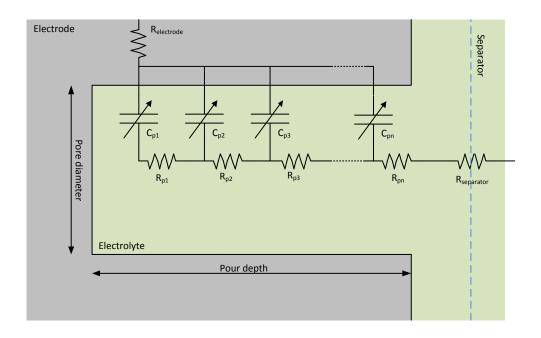

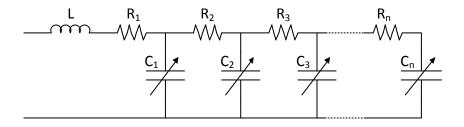

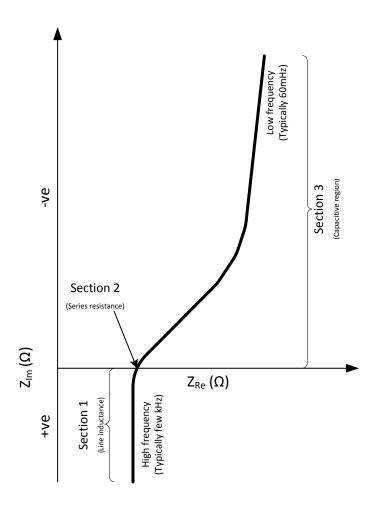

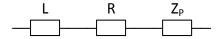

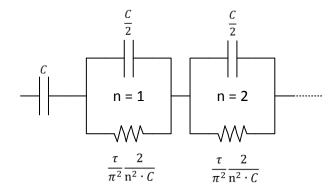

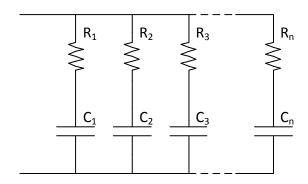

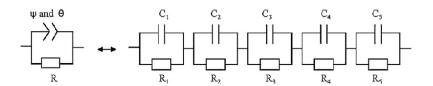

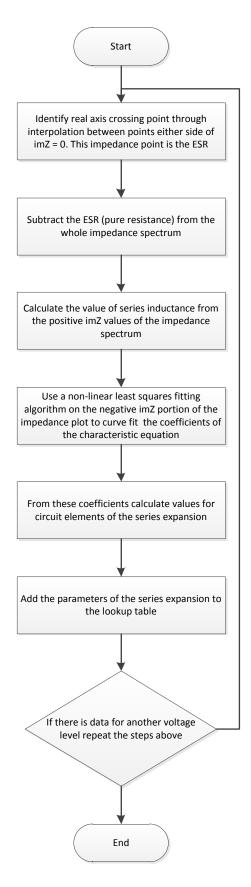

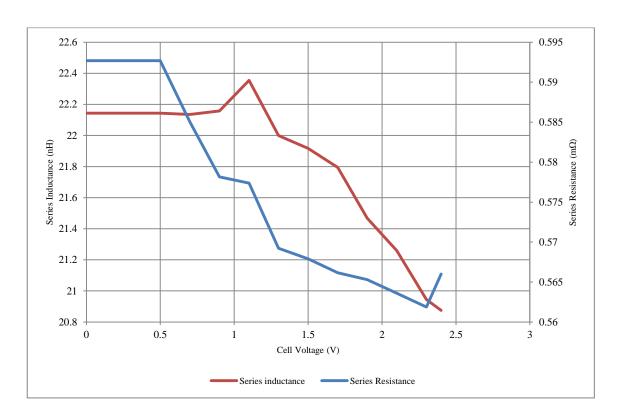

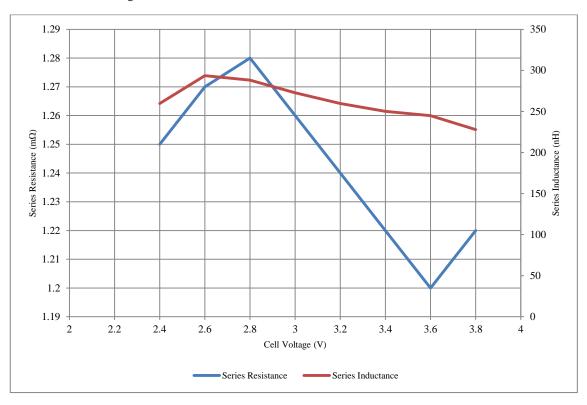

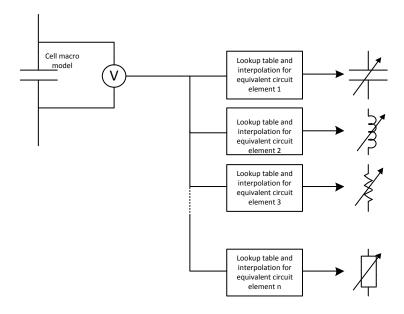

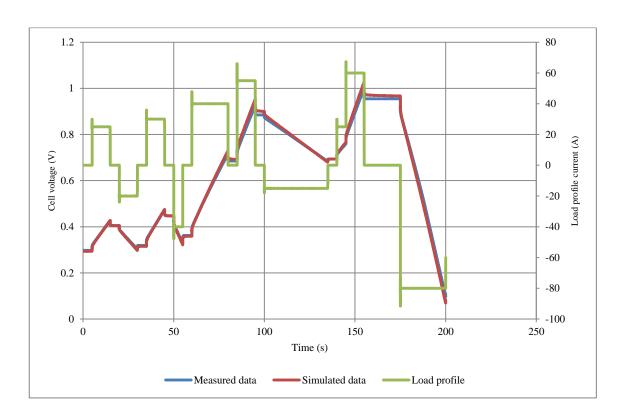

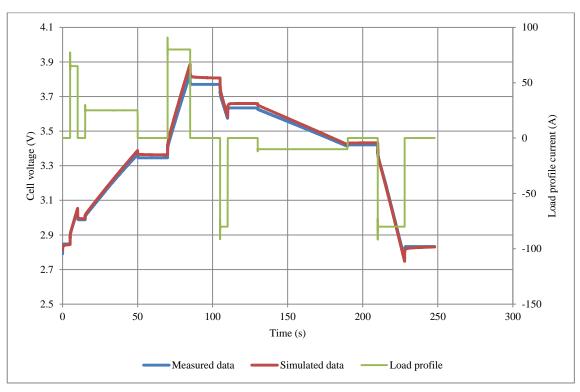

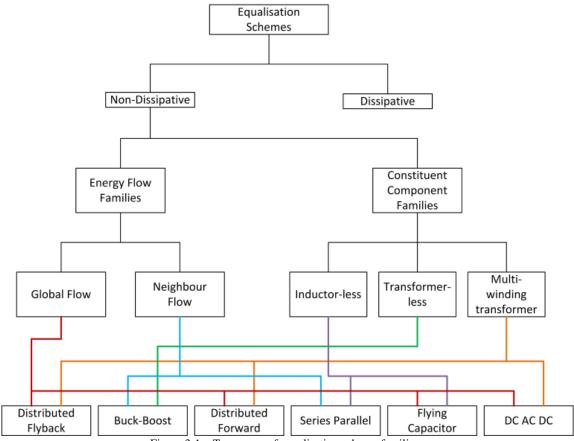

the electrochemical battery, which stores energy in chemical bonds that follow redox reactions in which occurs mass transfer, the EDLC effect is purely electrostatic where energy is stored in an electric field. Energy storage for capacitors does not involve mass transfer elevating the wear out failures associated with such reactions. The EDLC effect relates to the utilization of an electrostatic field across the interface boundary between an electron conductor and an ion conductor [1].